Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 80MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, SWPMI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                     |

| Number of I/O              | 26                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                              |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l431kcu6     |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | package mechanical data                                                            | . 175 |

|------------------|------------------------------------------------------------------------------------|-------|

| Table 93.        | UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid array |       |

| <b>T</b> 1 1 0 4 | package mechanical data                                                            |       |

| Table 94.        | UFBGA64 recommended PCB design rules (0.5 mm pitch BGA)                            | . 179 |

| Table 95.        | WLCSP64 - 64-ball, 3.141 x 3.127 mm, 0.35 mm pitch wafer level chip scale          |       |

|                  | package mechanical data                                                            | . 181 |

| Table 96.        | WLCSP64 recommended PCB design rules (0.35 mm pitch)                               | . 182 |

| Table 97.        | WLCSP49 - 49-ball, 3.141 x 3.127 mm, 0.4 mm pitch wafer level chip scale           |       |

|                  | package mechanical data                                                            | . 185 |

| Table 98.        | WLCSP49 recommended PCB design rules (0.4 mm pitch)                                | . 186 |

| Table 99.        | LQFP48 - 48-pin, 7 x 7 mm low-profile guad flat package                            |       |

|                  | mechanical data                                                                    | . 188 |

| Table 100.       | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat          |       |

|                  | package mechanical data                                                            | . 191 |

| Table 101.       | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat            |       |

|                  | package mechanical data                                                            | . 193 |

| Table 102.       | Package thermal characteristics                                                    |       |

| Table 103.       | STM32L431xx ordering information scheme                                            |       |

| Table 104.       | Document revision history                                                          |       |

|                  |                                                                                    | 00    |

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32L431xx microcontrollers.

This document should be read in conjunction with the STM32L4x1 reference manual (RM0392). The reference manual is available from the STMicroelectronics website *www.st.com*.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core, please refer to the Cortex<sup>®</sup>-M4 Technical Reference Manual, available from the www.arm.com website.

DocID028800 Rev 1

# 3.14 Interrupts and events

## 3.14.1 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 67 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\mathbb{B}}$ -M4.

The NVIC benefits are the following:

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

The NVIC hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.14.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 37 edge detector lines used to generate interrupt/event requests and wake-up the system from Stop mode. Each external line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently A pending register maintains the status of the interrupt requests. The internal lines are connected to peripherals with wakeup from Stop mode capability. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 83 GPIOs can be connected to the 16 external interrupt lines.

## 3.22.2 General-purpose timers (TIM2, TIM15, TIM16)

There are up to three synchronizable general-purpose timers embedded in the STM32L431xx (see *Table 9* for differences). Each general-purpose timer can be used to generate PWM outputs, or act as a simple time base.

• TIM2

It is a full-featured general-purpose timer:

TIM2 has a 32-bit auto-reload up/downcounter and 32-bit prescaler.

This timer features 4 independent channels for input capture/output compare, PWM or one-pulse mode output. It can work with the other general-purpose timers via the Timer Link feature for synchronization or event chaining.

The counter can be frozen in debug mode.

It has independent DMA request generation and support quadrature encoder.

• TIM15 and 16

They are general-purpose timers with mid-range features:

They have 16-bit auto-reload upcounters and 16-bit prescalers.

- TIM15 has 2 channels and 1 complementary channel

- TIM16 has 1 channel and 1 complementary channel

All channels can be used for input capture/output compare, PWM or one-pulse mode output.

The timers can work together via the Timer Link feature for synchronization or event chaining. The timers have independent DMA request generation.

The counters can be frozen in debug mode.

### 3.22.3 Basic timers (TIM6 and TIM7)

The basic timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit timebases.

### 3.22.4 Low-power timer (LPTIM1 and LPTIM2)

The devices embed two low-power timers. These timers have an independent clock and are running in Stop mode if they are clocked by LSE, LSI or an external clock. They are able to wakeup the system from Stop mode.

LPTIM1 is active in Stop 0, Stop 1 and Stop 2 modes.

LPTIM2 is active in Stop 0 and Stop 1 mode.

# 3.25 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32L431xx devices have three embedded universal synchronous receiver transmitters (USART1, USART2 and USART3).

These interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. They provide hardware management of the CTS and RTS signals, and RS485 Driver Enable. They are able to communicate at speeds of up to 10Mbit/s.

USART1, USART2 and USART3 also provide Smart Card mode (ISO 7816 compliant) and SPI-like communication capability.

All USART have a clock domain independent from the CPU clock, allowing the USARTx (x=1,2,3) to wake up the MCU from Stop mode using baudrates up to 200 Kbaud. The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

All USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>   | USART1 | USART2      | USART3    | LPUART1 |

|---------------------------------------|--------|-------------|-----------|---------|

| Hardware flow control for modem       | х      | Х           | Х         | Х       |

| Continuous communication using DMA    | X      | Х           | Х         | Х       |

| Multiprocessor communication          | Х      | Х           | Х         | Х       |

| Synchronous mode                      | Х      | Х           | Х         | -       |

| Smartcard mode                        | Х      | Х           | Х         | -       |

| Single-wire half-duplex communication | Х      | Х           | Х         | Х       |

| IrDA SIR ENDEC block                  | Х      | Х           | Х         | -       |

| LIN mode                              | Х      | Х           | Х         | -       |

| Dual clock domain                     | Х      | Х           | Х         | Х       |

| Wakeup from Stop 0 / Stop 1 modes     | Х      | Х           | Х         | Х       |

| Wakeup from Stop 2 mode               | -      | -           | -         | Х       |

| Receiver timeout interrupt            | Х      | Х           | Х         | -       |

| Modbus communication                  | Х      | Х           | Х         | -       |

| Auto baud rate detection              |        | X (4 modes) |           | -       |

| Driver Enable                         | Х      | Х           | Х         | Х       |

| LPUART/USART data length              |        | 7, 8 a      | nd 9 bits |         |

### Table 11. STM32L431xx USART/LPUART features

1. X = supported.

|   | 1                  | 2    | 3   | 4         | 5   | 6   | 7    | 8    | 9    | 10   | 11   | 12   |       |

|---|--------------------|------|-----|-----------|-----|-----|------|------|------|------|------|------|-------|

| А | PE3                | PE1  | PB8 | PH3/BOOT0 | PD7 | PD5 | PB4  | PB3  | PA15 | PA14 | PA13 | PA12 |       |

| в | PE4                | PE2  | PB9 | PB7       | PB6 | PD6 | PD4  | PD3  | PD1  | PC12 | PC10 | PA11 |       |

| с | PC13               | PE5  | PE0 | VDD       | PB5 |     | PC11 | VDD  | PA10 |      |      |      |       |

| D | PC14-<br>OSC32_IN  | PE6  | vss |           |     |     |      |      |      | PA9  | PA8  | PC9  |       |

| E | PC15-<br>OSC32_OUT | VBAT | VSS |           |     |     |      |      |      | PC8  | PC7  | PC6  |       |

| F | PH0-OSC_IN         | VSS  |     |           |     |     | VSS  | VSS  |      |      |      |      |       |

| G | PH1-<br>OSC_OUT    | VDD  |     |           |     |     | VDD  | VDD  |      |      |      |      |       |

| н | PC0                | NRST | VDD |           |     |     |      |      |      | PD15 | PD14 | PD13 |       |

| J | VSSA               | PC1  | PC2 |           |     |     |      |      |      | PD12 | PD11 | PD10 |       |

| к | VREF-              | PC3  | PA2 | PA5       | PC4 |     |      | PD9  | PD8  | PB15 | PB14 | PB13 |       |

| L | VREF+              | PA0  | PA3 | PA6       | PC5 | PB2 | PE8  | PE10 | PE12 | PB10 | PB11 | PB12 |       |

| м | VDDA               | PA1  | PA4 | PA7       | PB0 | PB1 | PE7  | PE9  | PE11 | PE13 | PE14 | PE15 |       |

|   |                    |      |     |           |     |     |      |      |      |      |      | MSv3 | 39213 |

Figure 6. STM32L431Vx UFBGA100 ballout<sup>(1)</sup>

1. The above figure shows the package top view.

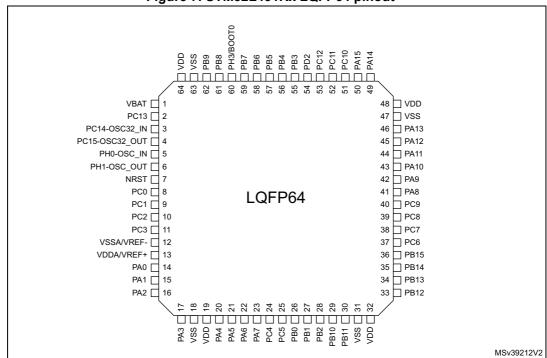

Figure 7. STM32L431Rx LQFP64 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

|                 |        |                 | Pi      | n Nu    | mbe    | ər      |         |          |                                          | -        | <u>A</u>      |       | Pin functions                                                                                                                                                 |                      |  |

|-----------------|--------|-----------------|---------|---------|--------|---------|---------|----------|------------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| <b>UFQFPN32</b> | LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                           | Additional functions |  |

| -               | -      | -               | -       | -       | -      | -       | 46      | M12      | PE15                                     | I/O      | FT            | -     | TIM1_BKIN,<br>TIM1_BKIN_COMP1,<br>SPI1_MOSI,<br>QUADSPI_BK1_IO3,<br>EVENTOUT                                                                                  | -                    |  |

| -               | 21     | 21              | E3      | H4      | 29     | G7      | 47      | L10      | PB10                                     | I/O      | FT_f          | -     | TIM2_CH3, I2C2_SCL,<br>SPI2_SCK, USART3_TX,<br>LPUART1_RX,<br>TSC_SYNC,<br>QUADSPI_CLK,<br>COMP1_OUT,<br>SAI1_SCK_A,<br>EVENTOUT                              | -                    |  |

| -               | 22     | 22              | F2      | H3      | 30     | H7      | 48      | L11      | PB11                                     | I/O      | FT_f          | -     | TIM2_CH4, I2C2_SDA,<br>USART3_RX,<br>LPUART1_TX,<br>QUADSPI_BK1_NCS,<br>COMP2_OUT,<br>EVENTOUT                                                                | -                    |  |

| 16              | 23     | 23              | G2      | H2      | 31     | D6      | 49      | F12      | VSS                                      | S        | -             | -     | -                                                                                                                                                             | -                    |  |

| 17              | 24     | 24              | G1      | H1      | 32     | E6      | 50      | G12      | VDD                                      | S        | -             | -     | -                                                                                                                                                             | -                    |  |

| -               | 25     | 25              | F1      | G3      | 33     | H8      | 51      | L12      | PB12                                     | I/O      | FT            | -     | TIM1_BKIN,<br>TIM1_BKIN_COMP2,<br>I2C2_SMBA, SPI2_NSS,<br>USART3_CK,<br>LPUART1_RTS_DE,<br>TSC_G1_IO1,<br>SWPMI1_IO,<br>SAI1_FS_A,<br>TIM15_BKIN,<br>EVENTOUT | -                    |  |

| -               | 26     | 26              | E2      | G2      | 34     | G8      | 52      | K12      | PB13                                     | I/O      | FT_f          | -     | TIM1_CH1N, I2C2_SCL,<br>SPI2_SCK,<br>USART3_CTS,<br>LPUART1_CTS,<br>TSC_G1_IO2,<br>SWPMI1_TX,<br>SAI1_SCK_A,<br>TIM15_CH1N,<br>EVENTOUT                       | -                    |  |

Table 14. STM32L431xx pin definitions (continued)

|                 |        |                 | Pi      | n Nu    | mbe    | ər      |         |          |                                          | •        |               |       | Pin function                                                                                                  | s                       |

|-----------------|--------|-----------------|---------|---------|--------|---------|---------|----------|------------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| <b>UFQFPN32</b> | LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                           | Additional<br>functions |

| -               | -      | -               | -       | F3      | 39     | E8      | 65      | E10      | PC8                                      | I/O      | FT            | -     | TSC_G4_IO3,<br>SDMMC1_D0,<br>EVENTOUT                                                                         | -                       |

| -               | -      | -               | -       | E2      | 40     | D8      | 66      | D12      | PC9                                      | I/O      | FT            | -     | TSC_G4_IO4,<br>SDMMC1_D1,<br>EVENTOUT                                                                         | -                       |

| 18              | 29     | 29              | D1      | E3      | 41     | D7      | 67      | D11      | PA8                                      | I/O      | FT            | -     | MCO, TIM1_CH1,<br>USART1_CK,<br>SWPMI1_IO,<br>SAI1_SCK_A,<br>LPTIM2_OUT,<br>EVENTOUT                          | -                       |

| 19              | 30     | 30              | D2      | D1      | 42     | C7      | 68      | D10      | PA9                                      | I/O      | FT_f          | -     | TIM1_CH2, I2C1_SCL,<br>USART1_TX,<br>SAI1_FS_A,<br>TIM15_BKIN,<br>EVENTOUT                                    | -                       |

| 20              | 31     | 31              | C2      | D2      | 43     | C6      | 69      | C12      | PA10                                     | I/O      | FT_f          | -     | TIM1_CH3, I2C1_SDA,<br>USART1_RX,<br>SAI1_SD_A, EVENTOUT                                                      | -                       |

| 21              | 32     | 32              | C1      | D3      | 44     | C8      | 70      | B12      | PA11                                     | I/O      | FT_u          | -     | TIM1_CH4, TIM1_BKIN2,<br>SPI1_MISO,<br>COMP1_OUT,<br>USART1_CTS,<br>CAN1_RX,<br>TIM1_BKIN2_COMP1,<br>EVENTOUT | -                       |

| 22              | 33     | 33              | C3      | C1      | 45     | B8      | 71      | A12      | PA12                                     | I/O      | FT_u          | -     | TIM1_ETR, SPI1_MOSI,<br>USART1_RTS_DE,<br>CAN1_TX, EVENTOUT                                                   | -                       |

| 23              | 34     | 34              | B2      | C2      | 46     | A8      | 72      | A11      | PA13<br>(JTMS-<br>SWDIO)                 | I/O      | FT            | (3)   | JTMS-SWDIO, IR_OUT,<br>SWPMI1_TX,<br>SAI1_SD_B, EVENTOUT                                                      | -                       |

| -               | 35     | 35              | B1      | B1      | 47     | D5      | -       | -        | VSS                                      | S        | -             | -     | -                                                                                                             | -                       |

| -               | 36     | 36              | A1      | A1      | 48     | E5      | 73      | C11      | VDD                                      | S        | -             | -     | -                                                                                                             | -                       |

| -               | -      | -               | -       | -       | -      | -       | 74      | F11      | VSS                                      | S        | -             | -     | -                                                                                                             | -                       |

| -               | -      | -               | -       | -       | -      | -       | 75      | G11      | VDD                                      | S        | -             | -     | -                                                                                                             | -                       |

| 24              | 37     | 37              | A2      | B2      | 49     | A7      | 76      | A10      | PA14<br>(JTCK-<br>SWCLK)                 | I/O      | FT            | (3)   | JTCK-SWCLK,<br>LPTIM1_OUT,<br>I2C1_SMBA,<br>SWPMI1_RX,<br>SAI1_FS_B, EVENTOUT                                 | -                       |

Table 14. STM32L431xx pin definitions (continued)

|        |      | AF8                | AF9        | AF10                | AF11 | AF12                                  | AF13        | AF14                        | AF15     |  |

|--------|------|--------------------|------------|---------------------|------|---------------------------------------|-------------|-----------------------------|----------|--|

| Po     | ort  | LPUART1            | CAN1/TSC   | QUADSPI             |      | SDMMC1/<br>COMP1/<br>COMP2/<br>SWPMI1 | SAI1        | TIM2/TIM15/<br>TIM16/LPTIM2 | EVENTOUT |  |

|        | PB0  | -                  | -          | QUADSPI_<br>BK1_IO1 |      | COMP1_OUT                             | SAI1_EXTCLK | -                           | EVENTOUT |  |

| ·      | PB1  | LPUART1_RTS<br>_DE | -          | QUADSPI_<br>BK1_IO0 |      | -                                     | -           | LPTIM2_IN1                  | EVENTOU  |  |

|        | PB2  | -                  | -          | -                   |      | -                                     | -           | -                           | EVENTOU" |  |

|        | PB3  | -                  | -          | -                   |      | -                                     | SAI1_SCK_B  | -                           | EVENTOU" |  |

|        | PB4  | -                  | TSC_G2_IO1 | -                   |      | -                                     | SAI1_MCLK_B | -                           | EVENTOU  |  |

|        | PB5  | -                  | TSC_G2_IO2 | -                   |      | COMP2_OUT                             | SAI1_SD_B   | TIM16_BKIN                  | EVENTOU  |  |

|        | PB6  | -                  | TSC_G2_IO3 | -                   | -    | -                                     | SAI1_FS_B   | TIM16_CH1N                  | EVENTOU  |  |

|        | PB7  | -                  | TSC_G2_IO4 | -                   |      | -                                     | -           | -                           | EVENTOU  |  |

| Port B | PB8  | -                  | CAN1_RX    | -                   |      | SDMMC1_D4                             | SAI1_MCLK_A | TIM16_CH1                   | EVENTOU" |  |

|        | PB9  | -                  | CAN1_TX    | -                   |      | SDMMC1_D5                             | SAI1_FS_A   | -                           | EVENTOU  |  |

|        | PB10 | LPUART1_RX         | TSC_SYNC   | QUADSPI_CLK         |      | COMP1_OUT                             | SAI1_SCK_A  | -                           | EVENTOU  |  |

|        | PB11 | LPUART1_TX         | -          | QUADSPI_<br>BK1_NCS |      | COMP2_OUT                             | -           | -                           | EVENTOU  |  |

| ·      | PB12 | LPUART1_RTS<br>_DE | TSC_G1_IO1 | -                   |      | SWPMI1_IO                             | SAI1_FS_A   | TIM15_BKIN                  | EVENTOU  |  |

|        | PB13 | LPUART1_CTS        | TSC_G1_IO2 | -                   |      | SWPMI1_TX                             | SAI1_SCK_A  | TIM15_CH1N                  | EVENTOU  |  |

|        | PB14 | -                  | TSC_G1_IO3 | -                   |      | SWPMI1_RX                             | SAI1_MCLK_A | TIM15_CH1                   | EVENTOU  |  |

|        | PB15 | -                  | TSC_G1_IO4 | -                   |      | SWPMI1_<br>SUSPEND                    | SAI1_SD_A   | TIM15_CH2                   | EVENTOU  |  |

DocID028800 Rev 1

5

70/200

STM32L431xx

Pinouts and pin description

| Bus  | Boundary address          | Size(bytes) | Peripheral |

|------|---------------------------|-------------|------------|

|      | 0x4001 3000 - 0x4001 33FF | 1 KB        | SPI1       |

|      | 0x4001 2C00 - 0x4001 2FFF | 1 KB        | TIM1       |

|      | 0x4001 2800 - 0x4001 2BFF | 1 KB        | SDMMC1     |

|      | 0x4001 2000 - 0x4001 27FF | 2 KB        | Reserved   |

| 4002 | 0x4001 1C00 - 0x4001 1FFF | 1 KB        | FIREWALL   |

| APB2 | 0x4001 0800- 0x4001 1BFF  | 5 KB        | Reserved   |

|      | 0x4001 0400 - 0x4001 07FF | 1 KB        | EXTI       |

|      | 0x4001 0200 - 0x4001 03FF |             | COMP       |

|      | 0x4001 0030 - 0x4001 01FF | 1 KB        | VREFBUF    |

|      | 0x4001 0000 - 0x4001 002F |             | SYSCFG     |

|      | 0x4000 9800 - 0x4000 FFFF | 26 KB       | Reserved   |

|      | 0x4000 9400 - 0x4000 97FF | 1 KB        | LPTIM2     |

|      | 0x4000 8C00 - 0x4000 93FF | 2 KB        | Reserved   |

|      | 0x4000 8800 - 0x4000 8BFF | 1 KB        | SWPMI1     |

|      | 0x4000 8400 - 0x4000 87FF | 1 KB        | Reserved   |

|      | 0x4000 8000 - 0x4000 83FF | 1 KB        | LPUART1    |

|      | 0x4000 7C00 - 0x4000 7FFF | 1 KB        | LPTIM1     |

|      | 0x4000 7800 - 0x4000 7BFF | 1 KB        | OPAMP      |

|      | 0x4000 7400 - 0x4000 77FF | 1 KB        | DAC        |

|      | 0x4000 7000 - 0x4000 73FF | 1 KB        | PWR        |

|      | 0x4000 6800 - 0x4000 6FFF | 2 KB        | Reserved   |

| APB1 | 0x4000 6400 - 0x4000 67FF | 1 KB        | CAN1       |

| APDI | 0x4000 6000 - 0x4000 63FF | 1 KB        | CRS        |

|      | 0x4000 5C00- 0x4000 5FFF  | 1 KB        | I2C3       |

|      | 0x4000 5800 - 0x4000 5BFF | 1 KB        | I2C2       |

|      | 0x4000 5400 - 0x4000 57FF | 1 KB        | I2C1       |

|      | 0x4000 4C00 - 0x4000 53FF | 2 KB        | Reserved   |

|      | 0x4000 4800 - 0x4000 4BFF | 1 KB        | USART3     |

|      | 0x4000 4400 - 0x4000 47FF | 1 KB        | USART2     |

|      | 0x4000 4000 - 0x4000 43FF | 1 KB        | Reserved   |

|      | 0x4000 3C00 - 0x4000 3FFF | 1 KB        | SPI3       |

|      | 0x4000 3800 - 0x4000 3BFF | 1 KB        | SPI2       |

|      | 0x4000 3400 - 0x4000 37FF | 1 KB        | Reserved   |

|      | 0x4000 3000 - 0x4000 33FF | 1 KB        | IWDG       |

| Table 17. STM32L431xx memory map and peripheral register boundary addresses | Table 17. STM32L | .431xx memory ma | p and p | peripheral re | eqister b | oundary | addresses |

|-----------------------------------------------------------------------------|------------------|------------------|---------|---------------|-----------|---------|-----------|

|-----------------------------------------------------------------------------|------------------|------------------|---------|---------------|-----------|---------|-----------|

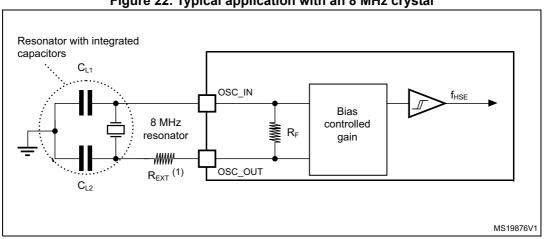

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 22. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 46*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                | Conditions <sup>(2)</sup>                        | Min | Тур | Max  | Unit |  |

|-------------------------------------|--------------------------|--------------------------------------------------|-----|-----|------|------|--|

|                                     |                          | LSEDRV[1:0] = 00<br>Low drive capability         | -   | 250 | -    |      |  |

|                                     |                          | LSEDRV[1:0] = 01<br>Medium low drive capability  | -   | 315 | -    | nA   |  |

| IDD(LSE)                            | LSE current consumption  | LSEDRV[1:0] = 10<br>Medium high drive capability | -   | 500 | -    | ПА   |  |

|                                     |                          | LSEDRV[1:0] = 11<br>High drive capability        | -   | 630 | -    |      |  |

|                                     |                          | LSEDRV[1:0] = 00<br>Low drive capability         | -   | -   | 0.5  |      |  |

| Gm                                  | Maximum critical crystal | LSEDRV[1:0] = 01<br>Medium low drive capability  | -   | -   | 0.75 | μΑ/V |  |

| Gm <sub>critmax</sub>               | gm                       | LSEDRV[1:0] = 10<br>Medium high drive capability | -   | -   | 1.7  | μΑνν |  |

|                                     |                          | LSEDRV[1:0] = 11<br>High drive capability        | -   | -   | 2.7  |      |  |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time             | V <sub>DD</sub> is stabilized                    | -   | 2   | -    | s    |  |

| Table 46. LSE oscillator characteristics | $(f_{LSE} = 32.768 \text{ kHz})^{(1)}$ |

|------------------------------------------|----------------------------------------|

|------------------------------------------|----------------------------------------|

| -                                   | Tun                                            | ne of . Abo accuracy - III            |                          |                          | nava | /   |     |  |  |  |

|-------------------------------------|------------------------------------------------|---------------------------------------|--------------------------|--------------------------|------|-----|-----|--|--|--|

| Sym-<br>bol                         | Parameter                                      | Conditions <sup>(4)</sup> Min Typ Max |                          |                          |      |     |     |  |  |  |

|                                     |                                                | ADC clock frequency ≤                 | Single                   | Fast channel (max speed) | -    | -74 | -65 |  |  |  |

| Total<br>THD harmonic<br>distortion | al 80 MHz,<br>monic Sampling rate ≤ 5.33 Msps, | ended                                 | Slow channel (max speed) | -                        | -74  | -67 | dB  |  |  |  |

|                                     |                                                | Differential                          | Fast channel (max speed) | -                        | -79  | -70 |     |  |  |  |

|                                     |                                                | $2 V \leq V_{DDA}$                    | Dinerential              | Slow channel (max speed) | -    | -79 | -71 |  |  |  |

Table 67. ADC accuracy - limited test conditions  $2^{(1)(2)(3)}$  (continued)

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

| Symbol             | Parameter                                            | Conditions                                                         | Min | Тур  | Max  | Unit |  |

|--------------------|------------------------------------------------------|--------------------------------------------------------------------|-----|------|------|------|--|

| Coin               | Gain error <sup>(5)</sup>                            | DAC output buffer ON<br>CL $\leq$ 50 pF, RL $\geq$ 5 k $\Omega$    | -   | -    | ±0.5 | %    |  |

| Gain               |                                                      | DAC output buffer OFF<br>CL ≤ 50 pF, no RL                         | -   | -    | ±0.5 | %    |  |

| TUE                | Total<br>unadjusted                                  | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ                      | -   | -    | ±30  |      |  |

| TUE                | error                                                | DAC output buffer OFF<br>CL ≤ 50 pF, no RL                         | -   | -    | ±12  | LSB  |  |

| TUECal             | Total<br>unadjusted<br>error after<br>calibration    | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ                      | -   | -    | ±23  | LSB  |  |

| SINK               | Signal-to-noise<br>ratio                             | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ<br>1 kHz, BW 500 kHz | -   | 71.2 | -    | dB   |  |

|                    |                                                      | DAC output buffer OFF<br>CL ≤ 50 pF, no RL, 1 kHz<br>BW 500 kHz    | -   | 71.6 | -    | uр   |  |

| THD Total harmonic | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ, 1 kHz | -                                                                  | -78 | -    | dB   |      |  |

| IIID               | distortion                                           | DAC output buffer OFF<br>CL ≤ 50 pF, no RL, 1 kHz                  | -   | -79  | -    | UB   |  |

| SINAD              | Signal-to-noise<br>and distortion<br>ratio           | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ, 1 kHz               | -   | 70.4 | -    | dB   |  |

|                    |                                                      | DAC output buffer OFF<br>CL ≤ 50 pF, no RL, 1 kHz                  | -   | 71   | -    | UD   |  |

| ENOB               | Effective number of bits                             | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ, 1 kHz               | -   | 11.4 | -    | bits |  |

| LINOD              |                                                      | DAC output buffer OFF<br>CL ≤ 50 pF, no RL, 1 kHz                  | -   | 11.5 | -    | DILS |  |

| Table 71. | DAC | accuracy | y <sup>(1)</sup> | (continued) | ) |

|-----------|-----|----------|------------------|-------------|---|

|-----------|-----|----------|------------------|-------------|---|

1. Guaranteed by design.

2. Difference between two consecutive codes - 1 LSB.

3. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

4. Difference between the value measured at Code (0x001) and the ideal value.

5. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{REF+} - 0.2$ ) V when buffer is ON.

| package mechanical data (continued) |             |        |       |                       |        |        |

|-------------------------------------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol                              | millimeters |        |       | inches <sup>(1)</sup> |        |        |

| Symbol                              | Min         | Тур    | Мах   | Min                   | Тур    | Max    |

| b <sup>(3)</sup>                    | 0.190       | 0.220  | 0.250 | 0.0075                | 0.0087 | 0.0098 |

| D                                   | 3.106       | 3.141  | 3.176 | 0.1223                | 0.1237 | 0.1250 |

| E                                   | 3.092       | 3.127  | 3.162 | 0.1217                | 0.1231 | 0.1245 |

| е                                   | -           | 0.350  | -     | -                     | 0.0138 | -      |

| e1                                  | -           | 2.450  | -     | -                     | 0.0965 | -      |

| e2                                  | -           | 2.450  | -     | -                     | 0.0965 | -      |

| F                                   | -           | 0.3455 | -     | -                     | 0.0136 | -      |

| G                                   | -           | 0.3385 | -     | -                     | 0.0133 | -      |

| aaa                                 | -           | -      | 0.100 | -                     | -      | 0.0039 |

| bbb                                 | -           | -      | 0.100 | -                     | -      | 0.0039 |

| ссс                                 | -           | -      | 0.100 | -                     | -      | 0.0039 |

| ddd                                 | -           | -      | 0.050 | -                     | -      | 0.0020 |

| eee                                 | -           | -      | 0.050 | -                     | -      | 0.0020 |

# Table 95. WLCSP64 - 64-ball, 3.141 x 3.127 mm, 0.35 mm pitch wafer level chip scale package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

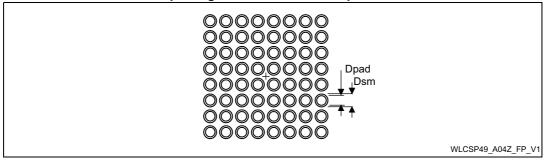

# Figure 55. WLCSP64 - 64-ball, 3.141 x 3.127 mm, 0.35 mm pitch wafer level chip scale package recommended footprint

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.35 mm                                                          |

| Dpad              | 0.210 mm                                                         |

| Dsm               | 0.275 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.235 mm                                                         |

| Stencil thickness | 0.100 mm                                                         |

DocID028800 Rev 1

| package mechanical data |             |       |       |                       |        |        |

|-------------------------|-------------|-------|-------|-----------------------|--------|--------|

| O week at               | millimeters |       |       | inches <sup>(1)</sup> |        |        |

| Symbol                  | Min         | Тур   | Max   | Min                   | Тур    | Мах    |

| А                       | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |

| A1                      | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |

| D                       | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| Е                       | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| D2                      | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| E2                      | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| L                       | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| Т                       | -           | 0.152 | -     | -                     | 0.0060 | -      |

| b                       | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |

| е                       | -           | 0.500 | -     | -                     | 0.0197 | -      |

| ddd                     | -           | -     | 0.080 | -                     | -      | 0.0031 |

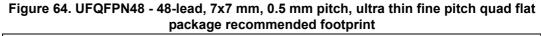

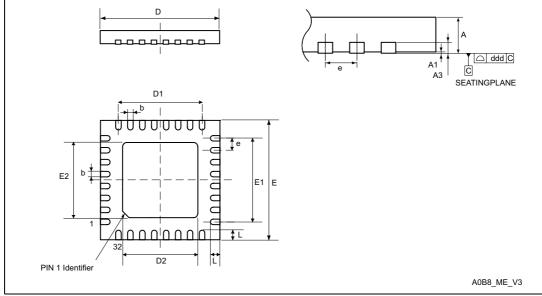

# Table 100. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

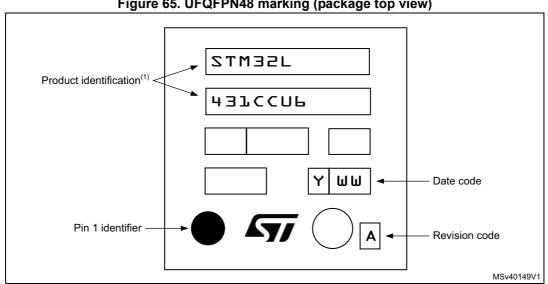

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 65. UFQFPN48 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering 1. samples to run qualification activity.

#### 7.9 **UFQFPN32** package information

- 1. Drawing is not to scale.

- There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this backside pad to PCB ground. 2.

### 7.10.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Part numbering*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32L431xx at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 82$  °C (measured according to JESD51-2), I<sub>DDmax</sub> = 50 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V and maximum 8 I/Os used at the same time in output at low level with I<sub>OL</sub> = 20 mA, V<sub>OL</sub>= 1.3 V

P<sub>INTmax</sub> = 50 mA × 3.5 V= 175 mW

P<sub>IOmax</sub> = 20 × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives:  $P_{INTmax}$  = 175 mW and  $P_{IOmax}$  = 272 mW:

P<sub>Dmax</sub> = 175 + 272 = 447 mW

Using the values obtained in *Table 102* T<sub>Jmax</sub> is calculated as follows:

For LQFP64, 46 °C/W

T<sub>Jmax</sub> = 82 °C + (46 °C/W × 447 mW) = 82 °C + 20.562 °C = 102.562 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105$  °C) see Section 8: Part numbering.

In this case, parts must be ordered at least with the temperature range suffix 6 (see Part numbering).

Note: With this given  $P_{Dmax}$  we can find the  $T_{Amax}$  allowed for a given device temperature range (order code suffix 6 or 7).

Suffix 6:  $T_{Amax} = T_{Jmax} - (46^{\circ}C/W \times 447 \text{ mW}) = 105-20.562 = 84.438^{\circ}C$ Suffix 7:  $T_{Amax} = T_{Jmax} - (46^{\circ}C/W \times 447 \text{ mW}) = 125-20.562 = 104.438^{\circ}C$

### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

# 9 Revision history

| Table 10 | 4. Documen | t revision | history |

|----------|------------|------------|---------|

|----------|------------|------------|---------|

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 31-May-2016 | 1        | Initial release. |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID028800 Rev 1