Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                             |

| Number of I/O              | 52                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-UFBGA                                                                          |

| Supplier Device Package    | 64-UFBGA (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l431rbi6tr           |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Per                                                                                                                                                                                                                                                       | ipheral                                        | STM32L431Vx         | STM32L431Rx                                                | STM32L431Cx                                                 | STM32L431Kx                    |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------|------------------------------------------------------------|-------------------------------------------------------------|--------------------------------|--|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                           | Advanced control                               |                     | 1                                                          | (16-bit)                                                    |                                |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                           | General<br>purpose                             |                     |                                                            | ? (16-bit)<br>(32-bit)                                      |                                |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                           | Basic                                          |                     | 2                                                          | ? (16-bit)                                                  |                                |  |  |  |  |  |  |  |  |

| Timers                                                                                                                                                                                                                                                    | Low -power                                     |                     | 2                                                          | ? (16-bit)                                                  |                                |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                           | SysTick timer                                  |                     |                                                            | 1                                                           |                                |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                           | Watchdog<br>timers<br>(independent,<br>window) |                     |                                                            | 2                                                           |                                |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                           | SPI                                            |                     | 3                                                          |                                                             | 2                              |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                           | l <sup>2</sup> C                               |                     | 3                                                          |                                                             | 2                              |  |  |  |  |  |  |  |  |

| 0                                                                                                                                                                                                                                                         | USART<br>LPUART<br>SAI<br>CAN                  |                     | 3<br>1                                                     |                                                             | 2<br>1                         |  |  |  |  |  |  |  |  |

| interfaces                                                                                                                                                                                                                                                | SAI                                            | 1                   |                                                            |                                                             |                                |  |  |  |  |  |  |  |  |

| -                                                                                                                                                                                                                                                         | CAN                                            | 1                   |                                                            |                                                             |                                |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                           | SDMMC                                          | Yes No              |                                                            |                                                             |                                |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                           | SWPMI                                          |                     |                                                            | Yes                                                         |                                |  |  |  |  |  |  |  |  |

| RTC                                                                                                                                                                                                                                                       | ·                                              |                     |                                                            | Yes                                                         |                                |  |  |  |  |  |  |  |  |

| Tamper pins                                                                                                                                                                                                                                               |                                                | 3                   | 2                                                          | 2                                                           | 1                              |  |  |  |  |  |  |  |  |

| Random ger                                                                                                                                                                                                                                                | nerator                                        |                     |                                                            | Yes                                                         |                                |  |  |  |  |  |  |  |  |

| Timers Timers Comm. nterfaces CartC Tamper pins Capacitive ser Vakeup pins Capacitive ser Vakeup pins Capacitive ser Vamber of cha 12-bit ADCs Number of cha 12-bit DAC ch nternal voltag ouffer Analog compa Operational ar Max. CPU free Operating volt | 3                                              | 83 52<br>5 4        |                                                            | 38 or 39 <sup>(1)</sup><br>3                                | 26<br>2                        |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                           |                                                | 21                  | 12                                                         | 6                                                           | 3                              |  |  |  |  |  |  |  |  |

| 12-bit ADCs<br>Number of c                                                                                                                                                                                                                                |                                                | 1<br>16             | 1<br>16                                                    | 1<br>10                                                     | 1<br>10                        |  |  |  |  |  |  |  |  |

| 12-bit DAC o                                                                                                                                                                                                                                              | channels                                       |                     |                                                            | 2                                                           |                                |  |  |  |  |  |  |  |  |

| Internal volta<br>buffer                                                                                                                                                                                                                                  | age reference                                  | Yes                 |                                                            | No                                                          |                                |  |  |  |  |  |  |  |  |

| Analog com                                                                                                                                                                                                                                                | parator                                        |                     |                                                            | 2                                                           |                                |  |  |  |  |  |  |  |  |

| Operational                                                                                                                                                                                                                                               | amplifiers                                     |                     |                                                            | 1                                                           |                                |  |  |  |  |  |  |  |  |

| Max. CPU fr                                                                                                                                                                                                                                               | equency                                        |                     | 8                                                          | 80 MHz                                                      |                                |  |  |  |  |  |  |  |  |

| Operating vo                                                                                                                                                                                                                                              | oltage                                         |                     | 1.7                                                        | '1 to 3.6 V                                                 |                                |  |  |  |  |  |  |  |  |

| Operating te                                                                                                                                                                                                                                              | mperature                                      | Ambient<br>Jun      | t operating temperature: -4<br>ction temperature: -40 to 1 | 40 to 85 °C / -40 to 105 °C<br>105 °C / -40 to 125 °C / -40 | / -40 to 125 °C<br>) to 130 °C |  |  |  |  |  |  |  |  |

| Packages                                                                                                                                                                                                                                                  |                                                | LQFP100<br>UFBGA100 | WLCSP64<br>LQFP64<br>UFBGA64                               | WLCSP49<br>LQFP48<br>UFQFPN48                               | UFQFPN32                       |  |  |  |  |  |  |  |  |

Table 2. STM32L431xx family device features and peripheral counts (continued)

1. For WLCSP49 package.

### 3.7 Boot modes

At startup, BOOT0 pin or nSWBOOT0 option bit, and BOOT1 option bit are used to select one of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

BOOT0 value may come from the PH3-BOOT0 pin or from an option bit depending on the value of a user option bit to free the GPIO pad if needed.

A Flash empty check mechanism is implemented to force the boot from system flash if the first flash memory location is not programmed and if the boot selection is configured to boot from main flash.

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART, I2C, SPI and CAN in Device mode through DFU (device firmware upgrade).

## 3.8 Cyclic redundancy check calculation unit (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 3.9 Power supply management

### 3.9.1 Power supply schemes

- V<sub>DD</sub> = 1.71 to 3.6 V: external power supply for I/Os (V<sub>DDIO1</sub>), the internal regulator and the system analog such as reset, power management and internal clocks. It is provided externally through V<sub>DD</sub> pins.

- V<sub>DDA</sub> = 1.62 V (ADCs/COMPs) / 1.8 (DACs/OPAMP) to 3.6 V: external analog power supply for ADCs, DACs, OPAMP, Comparators and Voltage reference buffer. The V<sub>DDA</sub> voltage level is independent from the V<sub>DD</sub> voltage.

- V<sub>BAT</sub> = 1.55 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

- Note: When the functions supplied by  $V_{DDA}$  are not used, this supply should preferably be shorted to  $V_{DD}$ .

- Note: If these supplies are tied to ground, the I/Os supplied by these power supplies are not 5 V tolerant (refer to Table 18: Voltage characteristics).

- Note:  $V_{DDIOx}$  is the I/Os general purpose digital functions supply.  $V_{DDIOx}$  represents  $V_{DDIO1}$ , with  $V_{DDIO1} = V_{DD}$ .

RC, the HSI16 RC and the HSE crystal oscillators are disabled. The LSE or LSI is still running.

The RTC can remain active (Stop mode with RTC, Stop mode without RTC).

Some peripherals with wakeup capability can enable the HSI16 RC during Stop mode to detect their wakeup condition.

Three Stop modes are available: Stop 0, Stop 1 and Stop 2 modes. In Stop 2 mode, most of the VCORE domain is put in a lower leakage mode.

Stop 1 offers the largest number of active peripherals and wakeup sources, a smaller wakeup time but a higher consumption than Stop 2. In Stop 0 mode, the main regulator remains ON, allowing a very fast wakeup time but with much higher consumption.

The system clock when exiting from Stop 0, Stop1 or Stop2 modes can be either MSI up to 48 MHz or HSI16, depending on software configuration.

### • Standby mode

The Standby mode is used to achieve the lowest power consumption with BOR. The internal regulator is switched off so that the VCORE domain is powered off. The PLL, the MSI RC, the HSI16 RC and the HSE crystal oscillators are also switched off.

The RTC can remain active (Standby mode with RTC, Standby mode without RTC).

The brown-out reset (BOR) always remains active in Standby mode.

The state of each I/O during standby mode can be selected by software: I/O with internal pull-up, internal pull-down or floating.

After entering Standby mode, SRAM1 and register contents are lost except for registers in the Backup domain and Standby circuitry. Optionally, SRAM2 can be retained in Standby mode, supplied by the low-power Regulator (Standby with RAM2 retention mode).

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper) or a failure is detected on LSE (CSS on LSE).

The system clock after wakeup is MSI up to 8 MHz.

### Shutdown mode

The Shutdown mode allows to achieve the lowest power consumption. The internal regulator is switched off so that the VCORE domain is powered off. The PLL, the HSI16, the MSI, the LSI and the HSE oscillators are also switched off.

The RTC can remain active (Shutdown mode with RTC, Shutdown mode without RTC).

The BOR is not available in Shutdown mode. No power voltage monitoring is possible in this mode, therefore the switch to Backup domain is not supported.

SRAM1, SRAM2 and register contents are lost except for registers in the Backup domain.

The device exits Shutdown mode when an external reset (NRST pin), a WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper).

The system clock after wakeup is MSI at 4 MHz.

|                      |     |       | -                    | -                      |      |                   | -   |                   |     |                   | -    |                   |      |

|----------------------|-----|-------|----------------------|------------------------|------|-------------------|-----|-------------------|-----|-------------------|------|-------------------|------|

|                      |     |       |                      |                        | Stop | o 0/1             | Sto | op 2              | Sta | ndby              | Shut | down              |      |

| Peripheral           | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | -    | Wakeup capability | -   | Wakeup capability | -   | Wakeup capability | -    | Wakeup capability | VBAT |

| CRC calculation unit | 0   | 0     | 0                    | 0                      | -    | -                 | -   | -                 | -   | -                 | -    | -                 | -    |

| GPIOs                | 0   | 0     | 0                    | 0                      | 0    | 0                 | 0   | 0                 | (9) | 5<br>pins<br>(10) | (11) | 5<br>pins<br>(10) | -    |

### Table 4. Functionalities depending on the working mode<sup>(1)</sup> (continued)

1. Legend: Y = Yes (Enable). O = Optional (Disable by default. Can be enabled by software). - = Not available.

2. The Flash can be configured in power-down mode. By default, it is not in power-down mode.

- 3. The SRAM clock can be gated on or off.

- 4. SRAM2 content is preserved when the bit RRS is set in PWR\_CR3 register.

- Some peripherals with wakeup from Stop capability can request HSI16 to be enabled. In this case, HSI16 is woken up by the peripheral, and only feeds the peripheral which requested it. HSI16 is automatically put off when the peripheral does not need it anymore.

- 6. UART and LPUART reception is functional in Stop mode, and generates a wakeup interrupt on Start, address match or received frame event.

- 7. I2C address detection is functional in Stop mode, and generates a wakeup interrupt in case of address match.

- 8. Voltage scaling Range 1 only.

- 9. I/Os can be configured with internal pull-up, pull-down or floating in Standby mode.

- 10. The I/Os with wakeup from Standby/Shutdown capability are: PA0, PC13, PE6, PA2, PC5.

- 11. I/Os can be configured with internal pull-up, pull-down or floating in Shutdown mode but the configuration is lost when exiting the Shutdown mode.

### 3.9.5 Reset mode

In order to improve the consumption under reset, the I/Os state under and after reset is "analog state" (the I/O schmitt trigger is disable). In addition, the internal reset pull-up is deactivated when the reset source is internal.

### 3.9.6 VBAT operation

The VBAT pin allows to power the device VBAT domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present. The VBAT pin supplies the RTC with LSE and the backup registers. Three anti-tamper detection pins are available in VBAT mode.

VBAT operation is automatically activated when V<sub>DD</sub> is not present.

An internal VBAT battery charging circuit is embedded and can be activated when  $\mathsf{V}_{\mathsf{DD}}$  is present.

*Note:* When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from VBAT operation.

DocID028800 Rev 1

## 3.15 Analog to digital converter (ADC)

The device embeds a successive approximation analog-to-digital converter with the following features:

- 12-bit native resolution, with built-in calibration

- 5.33 Msps maximum conversion rate with full resolution

- Down to 18.75 ns sampling time

- Increased conversion rate for lower resolution (up to 8.88 Msps for 6-bit resolution)

- Up to 16 external channels.

- 5 internal channels: internal reference voltage, temperature sensor, VBAT/3, DAC1 and DAC2 outputs.

- One external reference pin is available on some package, allowing the input voltage range to be independent from the power supply

- Single-ended and differential mode inputs

- Low-power design

- Capable of low-current operation at low conversion rate (consumption decreases linearly with speed)

- Dual clock domain architecture: ADC speed independent from CPU frequency

- Highly versatile digital interface

- Single-shot or continuous/discontinuous sequencer-based scan mode: 2 groups of analog signals conversions can be programmed to differentiate background and high-priority real-time conversions

- ADC supports multiple trigger inputs for synchronization with on-chip timers and external signals

- Results stored into data register or in RAM with DMA controller support

- Data pre-processing: left/right alignment and per channel offset compensation

- Built-in oversampling unit for enhanced SNR

- Channel-wise programmable sampling time

- Three analog watchdog for automatic voltage monitoring, generating interrupts and trigger for selected timers

- Hardware assistant to prepare the context of the injected channels to allow fast context switching

### 3.15.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{TS}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC1\_IN17 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

## 3.22 Timers and watchdogs

The STM32L431xx includes one advanced control timers, up to five general-purpose timers, two basic timers, two low-power timers, two watchdog timers and a SysTick timer. The table below compares the features of the advanced control, general purpose and basic timers.

| Timer type          | Timer      | Counter resolution | Counter<br>type      | Prescaler<br>factor                       | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>outputs |  |  |  |  |  |  |

|---------------------|------------|--------------------|----------------------|-------------------------------------------|------------------------------|---------------------------------|--------------------------|--|--|--|--|--|--|

| Advanced control    | TIM1       | 16-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536     | Yes                          | 4                               | 3                        |  |  |  |  |  |  |

| General-<br>purpose | TIM2       | 32-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536     | Yes                          | 4                               | No                       |  |  |  |  |  |  |

| General-<br>purpose | TIM15      | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536     | Yes                          | 2                               | 1                        |  |  |  |  |  |  |

| General-<br>purpose | TIM16      | 16-bit             | Up                   | Any integer<br>between 1 Yes<br>and 65536 |                              | 1                               | 1                        |  |  |  |  |  |  |

| Basic               | TIM6, TIM7 | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536     | Yes                          | 0                               | No                       |  |  |  |  |  |  |

Table 9. Timer feature comparison

### 3.22.1 Advanced-control timer (TIM1)

The advanced-control timer can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as complete general-purpose timers. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

Many features are shared with those of the general-purpose TIMx timers (described in *Section 3.22.2*) using the same architecture, so the advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

## 3.24 Inter-integrated circuit interface (I2C)

The device embeds 3 I2C. Refer to *Table 10: I2C implementation* for the features implementation.

The I<sup>2</sup>C bus interface handles communications between the microcontroller and the serial I<sup>2</sup>C bus. It controls all I<sup>2</sup>C bus-specific sequencing, protocol, arbitration and timing.

The I2C peripheral supports:

- I<sup>2</sup>C-bus specification and user manual rev. 5 compatibility:

- Slave and master modes, multimaster capability

- Standard-mode (Sm), with a bitrate up to 100 kbit/s

- Fast-mode (Fm), with a bitrate up to 400 kbit/s

- Fast-mode Plus (Fm+), with a bitrate up to 1 Mbit/s and 20 mA output drive I/Os

- 7-bit and 10-bit addressing mode, multiple 7-bit slave addresses

- Programmable setup and hold times

- Optional clock stretching

- System Management Bus (SMBus) specification rev 2.0 compatibility:

- Hardware PEC (Packet Error Checking) generation and verification with ACK control

- Address resolution protocol (ARP) support

- SMBus alert

- Power System Management Protocol (PMBus<sup>TM</sup>) specification rev 1.1 compatibility

- Independent clock: a choice of independent clock sources allowing the I2C communication speed to be independent from the PCLK reprogramming. Refer to Figure 3: Clock tree.

- Wakeup from Stop mode on address match

- Programmable analog and digital noise filters

- 1-byte buffer with DMA capability

### Table 10. I2C implementation

| I2C features <sup>(1)</sup>                                 | I2C1 | I2C2 | I2C3 |

|-------------------------------------------------------------|------|------|------|

| Standard-mode (up to 100 kbit/s)                            | Х    | Х    | Х    |

| Fast-mode (up to 400 kbit/s)                                | Х    | Х    | Х    |

| Fast-mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) | Х    | Х    | Х    |

| Programmable analog and digital noise filters               | Х    | Х    | Х    |

| SMBus/PMBus hardware support                                | Х    | Х    | Х    |

| Independent clock                                           | Х    | Х    | Х    |

| Wakeup from Stop 0 / Stop 1 mode on address match           | Х    | Х    | Х    |

| Wakeup from Stop 2 mode on address match                    | -    | -    | Х    |

1. X: supported

# 3.25 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32L431xx devices have three embedded universal synchronous receiver transmitters (USART1, USART2 and USART3).

These interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. They provide hardware management of the CTS and RTS signals, and RS485 Driver Enable. They are able to communicate at speeds of up to 10Mbit/s.

USART1, USART2 and USART3 also provide Smart Card mode (ISO 7816 compliant) and SPI-like communication capability.

All USART have a clock domain independent from the CPU clock, allowing the USARTx (x=1,2,3) to wake up the MCU from Stop mode using baudrates up to 200 Kbaud. The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

All USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>   | USART1 | USART2      | USART3    | LPUART1 |

|---------------------------------------|--------|-------------|-----------|---------|

| Hardware flow control for modem       | х      | Х           | Х         | Х       |

| Continuous communication using DMA    | X      | Х           | Х         | Х       |

| Multiprocessor communication          | Х      | Х           | Х         | Х       |

| Synchronous mode                      | Х      | Х           | Х         | -       |

| Smartcard mode                        | Х      | Х           | Х         | -       |

| Single-wire half-duplex communication | Х      | Х           | Х         | Х       |

| IrDA SIR ENDEC block                  | Х      | Х           | Х         | -       |

| LIN mode                              | Х      | Х           | Х         | -       |

| Dual clock domain                     | Х      | Х           | Х         | Х       |

| Wakeup from Stop 0 / Stop 1 modes     | Х      | Х           | Х         | Х       |

| Wakeup from Stop 2 mode               | -      | -           | -         | Х       |

| Receiver timeout interrupt            | Х      | Х           | Х         | -       |

| Modbus communication                  | Х      | Х           | Х         | -       |

| Auto baud rate detection              |        | X (4 modes) |           | -       |

| Driver Enable                         | Х      | Х           | Х         | Х       |

| LPUART/USART data length              |        | 7, 8 a      | nd 9 bits |         |

### Table 11. STM32L431xx USART/LPUART features

1. X = supported.

## 4 Pinouts and pin description

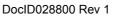

Figure 5. STM32L431Vx LQFP100 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

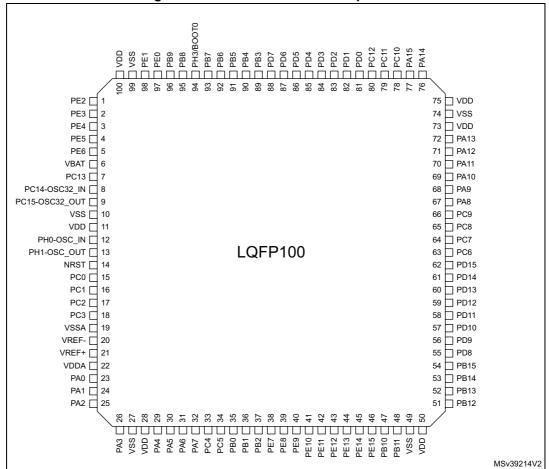

### Figure 13. STM32L431Kx UFQFPN32 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

| Na        | me                     | Abbreviation                                                                                    | Definition                                                                      |  |  |  |  |  |  |

|-----------|------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin r     | name                   | Unless otherwise specified ir<br>reset is the same as the actu                                  | h brackets below the pin name, the pin function during and after<br>al pin name |  |  |  |  |  |  |

|           |                        | S                                                                                               | Supply pin                                                                      |  |  |  |  |  |  |

| Pin       | type                   | I                                                                                               | Input only pin                                                                  |  |  |  |  |  |  |

|           |                        | I/O                                                                                             | Input / output pin                                                              |  |  |  |  |  |  |

|           |                        | FT                                                                                              | 5 V tolerant I/O                                                                |  |  |  |  |  |  |

|           |                        | TT                                                                                              | 3.6 V tolerant I/O                                                              |  |  |  |  |  |  |

|           |                        | RST                                                                                             | Bidirectional reset pin with embedded weak pull-up resistor                     |  |  |  |  |  |  |

| I/O str   | ructure                |                                                                                                 | Option for TT or FT I/Os                                                        |  |  |  |  |  |  |

|           |                        | _f <sup>(1)</sup>                                                                               | I/O, Fm+ capable                                                                |  |  |  |  |  |  |

|           |                        | _a <sup>(2)</sup>                                                                               | I/O, with Analog switch function supplied by $V_{DDA}$                          |  |  |  |  |  |  |

| No        | otes                   | Unless otherwise specified by a note, all I/Os are set as analog inputs during and after reset. |                                                                                 |  |  |  |  |  |  |

| Pin       | Alternate<br>functions | Functions selected through GPIOx_AFR registers                                                  |                                                                                 |  |  |  |  |  |  |

| functions | Additional functions   | Functions directly selected/enabled through peripheral registers                                |                                                                                 |  |  |  |  |  |  |

### Table 13. Legend/abbreviations used in the pinout table

1. The related I/O structures in *Table 14* are: FT\_f, FT\_fa.

2. The related I/O structures in Table 14 are: FT\_a, FT\_fa, TT\_a.

|                 |        |                 | Pi      | n Nu    | mbe    | ər      |         |          |                                          | _                         | 0             |                                                    | Pin function                                                                                                                      | IS                                                  |

|-----------------|--------|-----------------|---------|---------|--------|---------|---------|----------|------------------------------------------|---------------------------|---------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| <b>UFQFPN32</b> | LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type                  | I/O structure | Notes                                              | Alternate functions                                                                                                               | Additional functions                                |

| 8               | 12     | 12              | E5      | F6      | 16     | F3      | 25      | K3       | PA2                                      | I/O                       | FT_a          | -                                                  | TIM2_CH3, USART2_TX,<br>LPUART1_TX,<br>QUADSPI_BK1_NCS,<br>COMP2_OUT,<br>TIM15_CH1, EVENTOUT                                      | COMP2_INM,<br>ADC1_IN7,<br>WKUP4,<br>LSCO           |

| 9               | 13     | 13              | E4      | G6      | 17     | G3      | 26      | L3       | PA3 I/C                                  |                           | /0 TT_a -     |                                                    | TIM2_CH4, USART2_RX,<br>LPUART1_RX,<br>QUADSPI_CLK,<br>SAI1_MCLK_A,<br>TIM15_CH2, EVENTOUT                                        | OPAMP1_<br>VOUT,<br>COMP2_INP,<br>ADC1_IN8          |

| -               | -      | -               | -       | H8      | 18     | C2      | 27      | E3       | VSS                                      | S                         | -             | -                                                  | -                                                                                                                                 | -                                                   |

| -               | -      | -               | -       | H7      | 19     | D2      | 28      | H3       | VDD                                      | S                         | -             | -                                                  | -                                                                                                                                 | -                                                   |

| 10              | 14     | 14              | G6      | E5      | 20     | H3      | 29      | М3       | PA4                                      | PA4 I/O TT_a - SAI1_FS_B, |               | COMP1_INM,<br>COMP2_INM,<br>ADC1_IN9,<br>DAC1_OUT1 |                                                                                                                                   |                                                     |

| 11              | 15     | 15              | F5      | F5      | 21     | F4      | 30      | K4       | PA5                                      | I/O                       | TT_a          | -                                                  | TIM2_CH1, TIM2_ETR,<br>SPI1_SCK,<br>LPTIM2_ETR,<br>EVENTOUT                                                                       | COMP1_INM,<br>COMP2_INM,<br>ADC1_IN10,<br>DAC1_OUT2 |

| 12              | 16     | 16              | F4      | G5      | 22     | G4      | 31      | L4       | PA6                                      | I/O                       | FT_a          | -                                                  | TIM1_BKIN, SPI1_MISO,<br>COMP1_OUT,<br>USART3_CTS,<br>LPUART1_CTS,<br>QUADSPI_BK1_IO3,<br>TIM1_BKIN_COMP2,<br>TIM16_CH1, EVENTOUT | ADC1_IN11                                           |

| 13              | 17     | 17              | F3      | H6      | 23     | H4      | 32      | M4       | PA7                                      | I/O                       | FT_fa         | -                                                  | TIM1_CH1N, I2C3_SCL,<br>SPI1_MOSI,<br>QUADSPI_BK1_IO2,<br>COMP2_OUT,<br>EVENTOUT                                                  | ADC1_IN12                                           |

| -               | -      | -               | -       | D4      | 24     | H5      | 33      | K5       | PC4                                      | I/O                       | FT_a          | -                                                  | USART3_TX,<br>EVENTOUT                                                                                                            | COMP1_INM,<br>ADC1_IN13                             |

| -               | -      | -               | -       | E4      | 25     | H6      | 34      | L5       | PC5                                      | I/O                       | FT_a          | -                                                  | USART3_RX,<br>EVENTOUT                                                                                                            | COMP1_INP,<br>ADC1_IN14,<br>WKUP5                   |

Table 14. STM32L431xx pin definitions (continued)

|                 |        |                 | Pi      | n Nu    | mbe    | ər      |         |          |                                          | •                     |               |       | Pin function                                                                                                  | s                       |

|-----------------|--------|-----------------|---------|---------|--------|---------|---------|----------|------------------------------------------|-----------------------|---------------|-------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| <b>UFQFPN32</b> | LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type              | I/O structure | Notes | Alternate functions                                                                                           | Additional<br>functions |

| -               | -      | -               | -       | F3      | 39     | E8      | 65      | E10      | PC8                                      | I/O                   | FT            | -     | TSC_G4_IO3,<br>SDMMC1_D0,<br>EVENTOUT                                                                         | -                       |

| -               | -      | -               | -       | E2      | 40     | D8      | 66      | D12      | PC9                                      | I/O                   | FT            | -     | TSC_G4_IO4,<br>SDMMC1_D1,<br>EVENTOUT                                                                         | -                       |

| 18              | 29     | 29              | D1      | E3      | 41     | D7      | 67      | D11      | PA8                                      | I/O                   | FT            | -     | MCO, TIM1_CH1,<br>USART1_CK,<br>SWPMI1_IO,<br>SAI1_SCK_A,<br>LPTIM2_OUT,<br>EVENTOUT                          | -                       |

| 19              | 30     | 30              | D2      | D1      | 42     | C7      | 68      | D10      | PA9                                      | I/O                   | FT_f          | -     | TIM1_CH2, I2C1_SCL,<br>USART1_TX,<br>SAI1_FS_A,<br>TIM15_BKIN,<br>EVENTOUT                                    | -                       |

| 20              | 31     | 31              | C2      | D2      | 43     | C6      | 69      | C12      | PA10                                     | I/O                   | FT_f          | -     | TIM1_CH3, I2C1_SDA,<br>USART1_RX,<br>SAI1_SD_A, EVENTOUT                                                      | -                       |

| 21              | 32     | 32              | C1      | D3      | 44     | C8      | 70      | B12      | PA11                                     | I/O                   | FT_u          | -     | TIM1_CH4, TIM1_BKIN2,<br>SPI1_MISO,<br>COMP1_OUT,<br>USART1_CTS,<br>CAN1_RX,<br>TIM1_BKIN2_COMP1,<br>EVENTOUT | -                       |

| 22              | 33     | 33              | C3      | C1      | 45     | B8      | 71      | A12      | PA12                                     | I/O                   | FT_u          | -     | TIM1_ETR, SPI1_MOSI,<br>USART1_RTS_DE,<br>CAN1_TX, EVENTOUT                                                   | -                       |

| 23              | 34     | 34              | B2      | C2      | 46     | A8      | 72      | A11      | PA13<br>(JTMS-<br>SWDIO)                 | I/O FT <sup>(3)</sup> |               | (3)   | JTMS-SWDIO, IR_OUT,<br>SWPMI1_TX,<br>SAI1_SD_B, EVENTOUT                                                      | -                       |

| -               | 35     | 35              | B1      | B1      | 47     | D5      | -       | -        | VSS                                      | S                     |               |       | -                                                                                                             | -                       |

| -               | 36     | 36              | A1      | A1      | 48     | E5      | 73      | C11      | VDD                                      | S                     | S             |       | -                                                                                                             | -                       |

| -               | -      | -               | -       | -       | -      | -       | 74      | F11      | VSS                                      | S -                   |               | -     | -                                                                                                             | -                       |

| -               | -      | -               | -       | -       | -      | -       | 75      | G11      | VDD                                      | S - ·                 |               | -     | -                                                                                                             | -                       |

| 24              | 37     | 37              | A2      | B2      | 49     | A7      | 76      | A10      | PA14<br>(JTCK-<br>SWCLK)                 | I/O FT                |               | (3)   | JTCK-SWCLK,<br>LPTIM1_OUT,<br>I2C1_SMBA,<br>SWPMI1_RX,<br>SAI1_FS_B, EVENTOUT                                 | -                       |

Table 14. STM32L431xx pin definitions (continued)

| Elec  |  |

|-------|--|

| tric  |  |

| al ch |  |

| arac  |  |

| teri  |  |

| stics |  |

|  | Т          | able 32. Cur                         | rent cons          | sumption          | in Lov | v-powe | er sleep | modes  | , Flash | in powe            | e <mark>r-dow</mark> r | า     |        |        |      |

|--|------------|--------------------------------------|--------------------|-------------------|--------|--------|----------|--------|---------|--------------------|------------------------|-------|--------|--------|------|

|  | Parameter  | Co                                   |                    |                   | ТҮР    |        |          |        |         | MAX <sup>(1)</sup> |                        |       |        |        |      |

|  |            | -                                    | Voltage<br>scaling | f <sub>HCLK</sub> | 25 °C  | 55 °C  | 85 °C    | 105 °C | 125 °C  | 25 °C              | 55 °C                  | 85 °C | 105 °C | 125 °C | Unit |

|  |            |                                      |                    | 2 MHz             | 58.7   | 70.7   | 103.2    | 153.7  | 248.5   | 80                 | 113                    | 180   | 330    | 641    |      |

|  |            | f <sub>HCLK</sub> = f <sub>MSI</sub> |                    | 1 MHz             | 39.4   | 47.2   | 79.3     | 129.6  | 224.8   | 53                 | 86                     | 154   | 304    | 616    | μA   |

|  | sleep mode | all peripherals                      | s disable          | 400 kHz           | 20.8   | 30.8   | 62.1     | 112.5  | 207.8   | 35                 | 67                     | 137   | 286    | 597    | μΛ   |

|  | ·          |                                      |                    | 100 kHz           | 14.3   | 23.1   | 55.1     | 105.7  | 201.5   | 27                 | 58                     | 130   | 279    | 590    |      |

1. Guaranteed by characterization results, unless otherwise specified.

| 0                        | Demonster                      | Conditions                               |                 |       |       | TYP   |        |        |       |       | MAX <sup>(1)</sup> |        |        |    |

|--------------------------|--------------------------------|------------------------------------------|-----------------|-------|-------|-------|--------|--------|-------|-------|--------------------|--------|--------|----|

| Symbol                   | Parameter                      | -                                        | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C | Un |

|                          |                                |                                          | 1.8 V           | 1     | 2.54  | 8.74  | 19.8   | 43.4   | 2.0   | 5.6   | 21.1               | 50.8   | 116.0  |    |

| I <sub>DD</sub> (Stop 2) | Supply current in Stop 2 mode, | _                                        | 2.4 V           | 1.02  | 2.59  | 8.89  | 20.2   | 44.3   | 2.1   | 5.8   | 21.6               | 52.3   | 119.6  | u/ |

| IDD (Stop 2)             | RTC disabled                   | -                                        | 3 V             | 1.06  | 2.67  | 9.11  | 20.7   | 45.5   | 2.1   | 5.9   | 22.2               | 53.7   | 123.2  | μ/ |

|                          |                                |                                          | 3.6 V           | 1.23  | 2.88  | 9.56  | 21.6   | 47.3   | 2.3   | 6.1   | 23.0               | 55.8   | 127.9  |    |

|                          |                                |                                          | 1.8 V           | 1.3   | 2.82  | 9.02  | 20.1   | 43.6   | 2.5   | 6.2   | 21.6               | 51.3   | 116.3  |    |

|                          |                                | RTC clocked by LSI                       | 2.4 V           | 1.39  | 2.95  | 9.24  | 20.5   | 44.6   | 2.8   | 6.4   | 22.3               | 52.8   | 120.0  |    |

|                          |                                |                                          | 3 V             | 1.5   | 3.11  | 9.55  | 21.1   | 45.8   | 3.0   | 6.8   | 23.0               | 54.5   | 123.8  |    |

|                          |                                |                                          | 3.6 V           | 1.76  | 3.42  | 10.1  | 22.1   | 47.8   | 3.3   | 7.2   | 24.1               | 56.7   | 128.7  |    |

|                          |                                |                                          | 1.8 V           | 1.36  | 2.9   | 9.1   | 20.1   | 43.7   | -     | -     | -                  | -      | -      |    |

| I <sub>DD</sub> (Stop 2  | Supply current in Stop 2 mode, | RTC clocked by LSE                       | 2.4 V           | 1.48  | 3.09  | 9.44  | 20.8   | 45     | -     | -     | -                  | -      | -      | μA |

| with RTC)                | RTC enabled                    | bypassed at 32768 Hz                     | 3 V             | 1.83  | 3.67  | 10.4  | 22.3   | 47.3   | -     | -     | -                  | -      | -      | μ, |

|                          |                                |                                          | 3.6 V           | 3.58  | 6.17  | 13.9  | 26.6   | 53     | -     | -     | -                  | -      | -      |    |

|                          |                                |                                          | 1.8 V           | 1.28  | 2.81  | 9.13  | 20.8   | -      | -     | -     | -                  | -      | -      |    |

|                          |                                | RTC clocked by LSE quartz <sup>(2)</sup> | 2.4 V           | 1.39  | 2.93  | 9.34  | 21.3   | -      | -     | -     | -                  | -      | -      |    |

|                          |                                | in low drive mode                        | 3 V             | 1.59  | 3.1   | 9.64  | 21.8   | -      | -     | -     | -                  | -      | -      |    |

|                          |                                |                                          | 3.6 V           | 1.86  | 3.45  | 10.2  | 22.8   | -      | -     | -     | -                  | -      | -      |    |

### Table 33. Current consumption in Stop 2 mode

94/200

DocID028800 Rev 1

Symbol

I<sub>DD</sub>(LPSleep

)

| Symbol                                            | Parameter                                                 |                                         | Conditions                    |                                     | Min  | Тур  | Max    | Unit |   |  |

|---------------------------------------------------|-----------------------------------------------------------|-----------------------------------------|-------------------------------|-------------------------------------|------|------|--------|------|---|--|

|                                                   |                                                           |                                         | Range 0 to 3                  | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -1.2 | -    | 0.5    |      |   |  |

|                                                   |                                                           |                                         |                               | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -0.5 | -    |        |      |   |  |

| ∆ <sub>VDD</sub> (MSI) <sup>(2)</sup>             | MSI oscillator<br>frequency drift                         |                                         | Range 4 to 7                  | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -2.5 | -    | 0.7    | %    |   |  |

|                                                   | over V <sub>DD</sub><br>(reference is 3 V)                | MSI mode                                |                               | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -0.8 | -    | 0.7    | 70   |   |  |

|                                                   |                                                           |                                         | Pange 8 to 11                 | V <sub>DD</sub> =1.62 V<br>to 3.6 V | -5   | -    | 1      |      |   |  |

|                                                   |                                                           |                                         | Range 8 to 11                 | V <sub>DD</sub> =2.4 V<br>to 3.6 V  | -1.6 | -    |        |      |   |  |

|                                                   | Frequency<br>variation in<br>sampling mode <sup>(3)</sup> | MOL                                     | T <sub>A</sub> = -40 to 85 °C |                                     | -    | 1    | 2<br>4 | %    |   |  |

| ∆F <sub>SAMPLING</sub><br>(MSI) <sup>(2)(4)</sup> |                                                           | MSI mode T <sub>A</sub> = -40 to 125 °C |                               | °C                                  | -    | 2    |        |      |   |  |

| CC jitter(MSI) <sup>(4)</sup>                     | RMS cycle-to-<br>cycle jitter                             | PLL mode Range 11                       |                               | -                                   | -    | 60   | -      | ps   |   |  |

| P jitter(MSI) <sup>(4)</sup>                      | RMS Period jitter                                         | PLL mode Range 11                       |                               | -                                   | -    | 50   | -      | ps   |   |  |

|                                                   |                                                           | Range 0                                 |                               | -                                   | -    | 10   | 20     | -    |   |  |

|                                                   |                                                           | Range 1                                 |                               | -                                   | -    | 5    | 10     |      |   |  |

| t <sub>SU</sub> (MSI) <sup>(4)</sup>              | MSI oscillator                                            | Range 2                                 | -                             |                                     | -    | 4    | 8      |      |   |  |

|                                                   | start-up time                                             | Range 3                                 |                               | -                                   | -    | 3    | 7      | us   |   |  |

|                                                   |                                                           | Range 4 to 7                            |                               | -                                   | -    | 3    | 6      |      |   |  |

|                                                   |                                                           | Range 8 to 11                           |                               | Range 8 to 11 -                     |      | -    | -      | 2.5  | 6 |  |

| t <sub>STAB</sub> (MSI) <sup>(4)</sup>            |                                                           | PLL mode<br>Range 11                    | 10 % of final frequency       | -                                   | -    | 0.25 | 0.5    |      |   |  |

|                                                   |                                                           |                                         | 5 % of final<br>frequency     | -                                   | -    | 0.5  | 1.25   | ms   |   |  |

|                                                   |                                                           |                                         | 1 % of final<br>frequency     | -                                   | -    | -    | 2.5    |      |   |  |

Table 48. MSI oscillator characteristics<sup>(1)</sup> (continued)

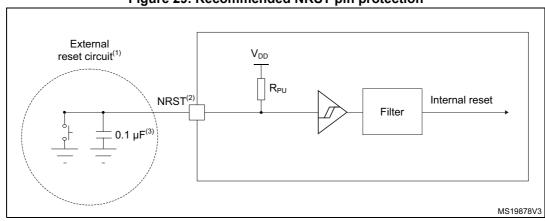

Figure 29. Recommended NRST pin protection

- 1. The reset network protects the device against parasitic resets.

- 2. The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in *Table 62: NRST pin characteristics*. Otherwise the reset will not be taken into account by the device.

- 3. The external capacitor on NRST must be placed as close as possible to the device.

### 6.3.16 Analog switches booster

| Symbol                 | Parameter                                                                             | Min  | Тур | Max | Unit |  |

|------------------------|---------------------------------------------------------------------------------------|------|-----|-----|------|--|

| V <sub>DD</sub>        | Supply voltage                                                                        | 1.62 | -   | 3.6 | V    |  |

| t <sub>SU(BOOST)</sub> | Booster startup time                                                                  | -    | -   | 240 | μs   |  |

| I <sub>DD(BOOST)</sub> | Booster consumption for $1.62 \text{ V} \leq \text{V}_{\text{DD}} \leq 2.0 \text{ V}$ | -    | -   | 250 |      |  |

|                        | Booster consumption for $2.0 \vee \leq V_{DD} \leq 2.7 \vee$                          | -    | -   | 500 | μA   |  |

|                        | Booster consumption for 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                     | -    | -   | 900 |      |  |

Table 63. Analog switches booster characteristics<sup>(1)</sup>

1. Guaranteed by design.

### **Quad SPI characteristics**

Unless otherwise specified, the parameters given in *Table 83* and *Table 84* for Quad SPI are derived from tests performed under the ambient temperature,  $f_{AHB}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 21: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 15 or 20 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics.

| Symbol              | Parameter                | Conditions                                                                   | Min                    | Тур | Max                    | Unit |  |

|---------------------|--------------------------|------------------------------------------------------------------------------|------------------------|-----|------------------------|------|--|

|                     |                          | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 20 pF<br>Voltage Range 1 | -                      | -   | 40                     |      |  |

| F <sub>CK</sub>     |                          | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 15 pF<br>Voltage Range 1 | -                      | -   | 48                     | MHz  |  |

| 1/t <sub>(CK)</sub> | Quad SPI clock frequency | $2.7 < V_{DD} < 3.6 V$ , $C_{LOAD} = 15 pF$<br>Voltage Range 1               | -                      | -   | 60                     |      |  |

|                     |                          | $1.71 < V_{DD} < 3.6 V C_{LOAD} = 20 pF$<br>Voltage Range 2                  | -                      | -   | 26                     |      |  |

| t <sub>w(CKH)</sub> | Quad SPI clock high and  | f <sub>AHBCLK</sub> = 48 MHz, presc=0                                        | t <sub>(CK)</sub> /2-2 | -   | t <sub>(CK)</sub> /2   |      |  |

| t <sub>w(CKL)</sub> | low time                 | AHBCLK- 40 Min 12, prese-0                                                   | t <sub>(СК)</sub> /2   | -   | t <sub>(CK)</sub> /2+2 |      |  |

| <b>t</b>            |                          | Voltage Range 1                                                              | 2                      | -   | -                      |      |  |

| t <sub>s(IN)</sub>  | Data input setup time    | Voltage Range 2                                                              | 3.5                    | -   | -                      |      |  |

| +                   | Data input hold time     | Voltage Range 1                                                              | 5                      | -   | -                      | ns   |  |

| t <sub>h(IN)</sub>  |                          | Voltage Range 2                                                              | 6.5                    | -   | -                      | 115  |  |

| +                   | Data autaut valid tima   | Voltage Range 1                                                              | -                      | 1   | 5                      |      |  |

| t <sub>v(OUT)</sub> | Data output valid time   | Voltage Range 2                                                              | -                      | 3   | 5                      |      |  |

| +                   | Data output hold time    | Voltage Range 1                                                              | 0                      | -   | -                      |      |  |

| t <sub>h(OUT)</sub> | Data output hold time    | Voltage Range 2                                                              | 0                      | -   | -                      |      |  |

| Table 83. Qua | ad SPI characteristics | in | SDR | mode <sup>(1)</sup> |

|---------------|------------------------|----|-----|---------------------|

|---------------|------------------------|----|-----|---------------------|

1. Guaranteed by characterization results.

## CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

### **SWPMI** characteristics

The Single Wire Protocol Master Interface (SWPMI) and the associated SWPMI\_IO transceiver are compliant with the ETSI TS 102 613 technical specification.

| Symbol                | Parameter                    | Conditions                                    | Min | Тур | Max | Unit |

|-----------------------|------------------------------|-----------------------------------------------|-----|-----|-----|------|

| t <sub>SWPSTART</sub> | SWPMI regulator startup time | SWP Class B<br>2.7 V ≤ V <sub>DD</sub> ≤ 3,3V | -   | -   | 300 | μs   |

| t <sub>SWPBIT</sub>   | SWP bit duration             | V <sub>CORE</sub> voltage range 1             | 500 | -   | -   | ns   |

|                       |                              | V <sub>CORE</sub> voltage range 2             | 620 | -   | -   | 115  |

Table 88. SWPMI electrical characteristics

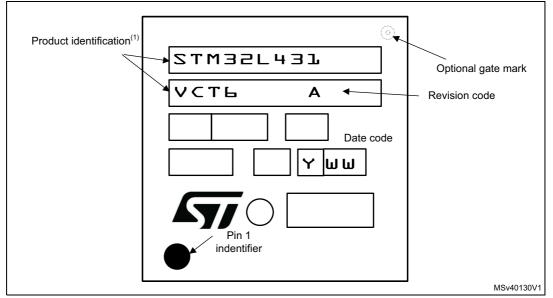

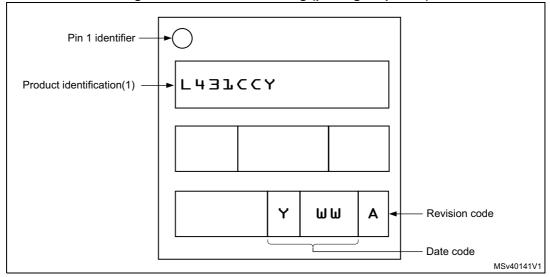

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

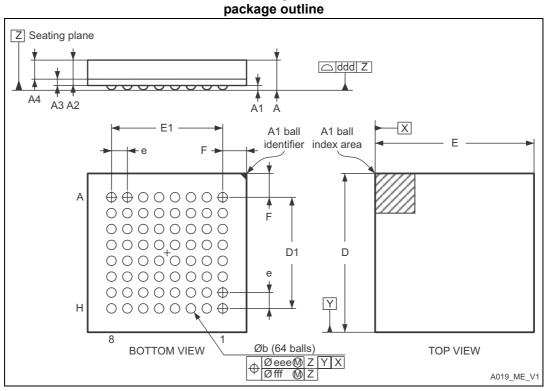

## 7.4 UFBGA64 package information

Figure 51. UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid array

1. Drawing is not to scale.

## Table 93. UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid array package mechanical data

| Symbol | millimeters |       |       |        |        |        |

|--------|-------------|-------|-------|--------|--------|--------|

| Symbol | Min Typ     |       | Мах   | Min    | Тур    | Мах    |

| А      | 0.460       | 0.530 | 0.600 | 0.0181 | 0.0209 | 0.0236 |

| A1     | 0.050       | 0.080 | 0.110 | 0.0020 | 0.0031 | 0.0043 |

| A2     | 0.400       | 0.450 | 0.500 | 0.0157 | 0.0177 | 0.0197 |

| A3     | 0.080       | 0.130 | 0.180 | 0.0031 | 0.0051 | 0.0071 |

| A4     | 0.270       | 0.320 | 0.370 | 0.0106 | 0.0126 | 0.0146 |

| b      | 0.170       | 0.280 | 0.330 | 0.0067 | 0.0110 | 0.0130 |

| D      | 4.850       | 5.000 | 5.150 | 0.1909 | 0.1969 | 0.2028 |

| D1     | 3.450       | 3.500 | 3.550 | 0.1358 | 0.1378 | 0.1398 |

| E      | 4.850       | 5.000 | 5.150 | 0.1909 | 0.1969 | 0.2028 |

| E1     | 3.450       | 3.500 | 3.550 | 0.1358 | 0.1378 | 0.1398 |

| е      | -           | 0.500 | -     | -      | 0.0197 | -      |

| ······································ |                                                                  |  |  |  |

|----------------------------------------|------------------------------------------------------------------|--|--|--|

| Dimension                              | Recommended values                                               |  |  |  |

| Pitch                                  | 0.4                                                              |  |  |  |

| Dpad                                   | 0.225 mm                                                         |  |  |  |

| Dsm                                    | 0.290 mm typ. (depends on the soldermask registration tolerance) |  |  |  |

| Stencil opening                        | 0.250 mm                                                         |  |  |  |

| Stencil thickness                      | 0.100 mm                                                         |  |  |  |

Table 98. WLCSP49 recommended PCB design rules (0.4 mm pitch)

### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 59. WLCSP49 marking (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.