# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                             |

| Number of I/O              | 83                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-LQFP                                                                          |

| Supplier Device Package    | 100-LQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l431vct6             |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.23 Real-time clock (RTC) and backup registers

The RTC is an independent BCD timer/counter. It supports the following features:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28, 29 (leap year), 30, and 31 days of the month.

- Two programmable alarms.

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 0.95 ppm resolution, to compensate for quartz crystal inaccuracy.

- Three anti-tamper detection pins with programmable filter.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event, or by a switch to VBAT mode.

- 17-bit auto-reload wakeup timer (WUT) for periodic events with programmable resolution and period.

The RTC and the 32 backup registers are supplied through a switch that takes power either from the  $V_{DD}$  supply when present or from the VBAT pin.

The backup registers are 32-bit registers used to store 128 bytes of user application data when VDD power is not present. They are not reset by a system or power reset, or when the device wakes up from Standby or Shutdown mode.

The RTC clock sources can be:

- A 32.768 kHz external crystal (LSE)

- An external resonator or oscillator (LSE)

- The internal low power RC oscillator (LSI, with typical frequency of 32 kHz)

- The high-speed external clock (HSE) divided by 32.

The RTC is functional in VBAT mode and in all low-power modes when it is clocked by the LSE. When clocked by the LSI, the RTC is not functional in VBAT mode, but is functional in all low-power modes except Shutdown mode.

All RTC events (Alarm, WakeUp Timer, Timestamp or Tamper) can generate an interrupt and wakeup the device from the low-power modes.

|   | 1                  | 2    | 3   | 4         | 5               | 6   | 7   | 8    | 9    | 10   | 11   | 12   |       |

|---|--------------------|------|-----|-----------|-----------------|-----|-----|------|------|------|------|------|-------|

| А | PE3                | PE1  | PB8 | PH3/BOOT0 | PD7             | PD5 | PB4 | PB3  | PA15 | PA14 | PA13 | PA12 |       |

| в | PE4                | PE2  | PB9 | PB7       | PB6             | PD6 | PD4 | PD3  | PD1  | PC12 | PC10 | PA11 |       |

| с | PC13               | PE5  | PE0 | VDD       | VDD PB5 PD2 PD0 |     |     |      |      |      | VDD  | PA10 |       |

| D | PC14-<br>OSC32_IN  | PE6  | vss |           |                 |     |     |      |      | PA9  | PA8  | PC9  |       |

| E | PC15-<br>OSC32_OUT | VBAT | VSS |           | PC8             |     |     |      |      |      | PC7  | PC6  |       |

| F | PH0-OSC_IN         | VSS  |     |           | UFBGA100        |     |     |      |      |      | VSS  | VSS  |       |

| G | PH1-<br>OSC_OUT    | VDD  |     |           |                 |     |     | )    |      |      | VDD  | VDD  |       |

| н | PC0                | NRST | VDD |           |                 |     |     |      |      | PD15 | PD14 | PD13 |       |

| J | VSSA               | PC1  | PC2 |           |                 |     |     |      |      | PD12 | PD11 | PD10 |       |

| к | VREF-              | PC3  | PA2 | PA5       | PC4             |     |     | PD9  | PD8  | PB15 | PB14 | PB13 |       |

| L | VREF+              | PA0  | PA3 | PA6       | PC5             | PB2 | PE8 | PE10 | PE12 | PB10 | PB11 | PB12 |       |

| м | VDDA               | PA1  | PA4 | PA7       | PB0             | PB1 | PE7 | PE9  | PE11 | PE13 | PE14 | PE15 |       |

|   |                    |      |     |           |                 |     |     |      |      |      |      | MSv3 | 39213 |

Figure 6. STM32L431Vx UFBGA100 ballout<sup>(1)</sup>

1. The above figure shows the package top view.

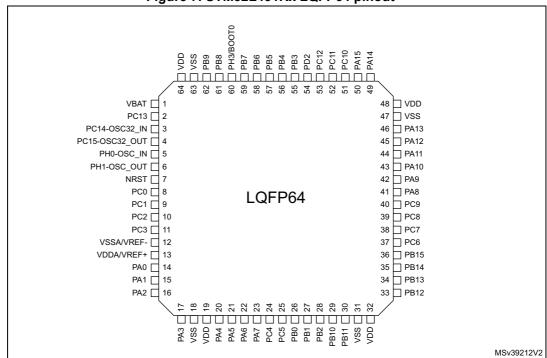

Figure 7. STM32L431Rx LQFP64 pinout<sup>(1)</sup>

1. The above figure shows the package top view.

|                 |        |                 | Pi      | n Nu    | mbe    | ər      |         |          | Diaman                                   |          | ¢)            |       | Pin function        | s                    |

|-----------------|--------|-----------------|---------|---------|--------|---------|---------|----------|------------------------------------------|----------|---------------|-------|---------------------|----------------------|

| <b>UFQFPN32</b> | LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions | Additional functions |

| -               | -      | -               | -       | -       | -      | -       | 97      | C3       | PE0                                      | I/O      | FT            | -     | TIM16_CH1, EVENTOUT | -                    |

| -               | -      | -               | -       | -       | -      | -       | 98      | A2       | PE1                                      | I/O      | FT            | -     | EVENTOUT            | -                    |

| 32              | 47     | 47              | A6      | A7      | 63     | D4      | 99      | D3       | VSS                                      | S        | -             | -     | -                   | -                    |

| 1               | 48     | 48              | A7      | A8      | 64     | E4      | 100     | C4       | VDD                                      | S        | -             | -     | -                   | -                    |

Table 14. STM32L431xx pin definitions (continued)

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF

These GPIOs must not be used as current sources (e.g. to drive an LED).

After a Backup domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the RTC registers which are not reset by the system reset. For details on how to manage these GPIOs, refer to the Backup domain and RTC register descriptions in the RM0392 reference manual.

3. After reset, these pins are configured as JTAG/SW debug alternate functions, and the internal pull-up on PA15, PA13, PB4 pins and the internal pull-down on PA14 pin are activated.

STM32L431xx

Pinouts and pin description

|        | Table 15. Alternate function AF0 to AF7 (for AF8 to AF15 see Table 16) (continued) |        |                      |           |        |                |           |      |                              |  |  |  |

|--------|------------------------------------------------------------------------------------|--------|----------------------|-----------|--------|----------------|-----------|------|------------------------------|--|--|--|

|        |                                                                                    | AF0    | AF1                  | AF2       | AF3    | AF4            | AF5       | AF6  | AF7                          |  |  |  |

| P      | ort                                                                                | SYS_AF | TIM1/TIM2/<br>LPTIM1 | TIM1/TIM2 | USART2 | 12C1/12C2/12C3 | SPI1/SPI2 | SPI3 | USART1/<br>USART2/<br>USART3 |  |  |  |

|        | PD0                                                                                | -      | -                    | -         | -      | -              | SPI2_NSS  | -    | -                            |  |  |  |

|        | PD1                                                                                | -      | -                    | -         | -      | -              | SPI2_SCK  | -    | -                            |  |  |  |

|        | PD2                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART3_RTS_<br>DE            |  |  |  |

|        | PD3                                                                                | -      | -                    | -         | -      | -              | SPI2_MISO | -    | USART2_CTS                   |  |  |  |

|        | PD4                                                                                | -      | -                    | -         | -      | -              | SPI2_MOSI | -    | USART2_RTS_<br>DE            |  |  |  |

|        | PD5                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART2_TX                    |  |  |  |

|        | PD6                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART2_RX                    |  |  |  |

| Port D | PD7                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART2_CK                    |  |  |  |

|        | PD8                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART3_TX                    |  |  |  |

|        | PD9                                                                                | -      | -                    | -         | -      | -              | -         | -    | USART3_RX                    |  |  |  |

|        | PD10                                                                               | -      | -                    | -         | -      | -              | -         | -    | USART3_CK                    |  |  |  |

|        | PD11                                                                               | -      | -                    | -         | -      | -              | -         | -    | USART3_CTS                   |  |  |  |

|        | PD12                                                                               | -      | -                    | -         | -      | -              | -         | -    | USART3_RTS_<br>DE            |  |  |  |

|        | PD13                                                                               | -      | -                    | -         | -      | -              | -         | -    | -                            |  |  |  |

|        | PD14                                                                               | -      | -                    | -         | -      | -              | -         | -    | -                            |  |  |  |

|        | PD15                                                                               | -      | -                    | -         | -      | -              | -         | -    | -                            |  |  |  |

| Port E | PE0                                                                                | -      | -                    | -         | -      | -              | -         | -    | -                            |  |  |  |

DocID028800 Rev 1

5

67/200

#### 5

# Memory mapping

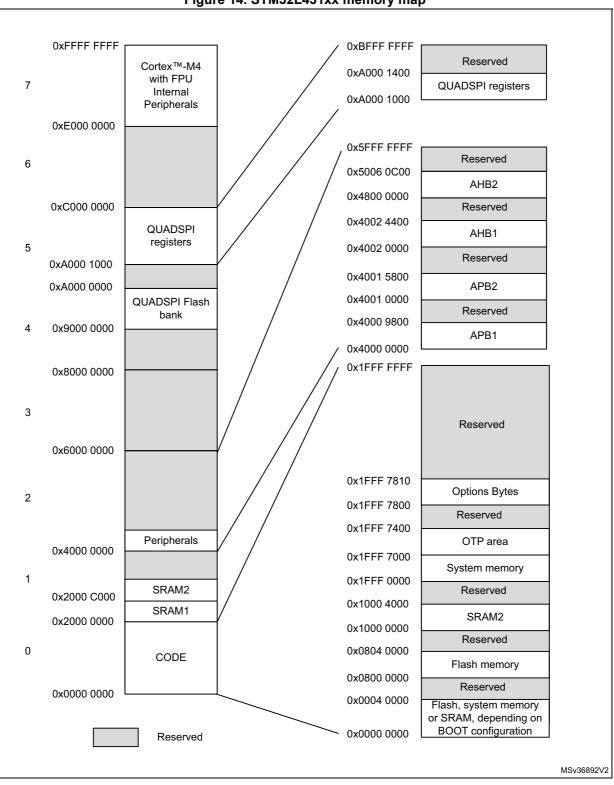

Figure 14. STM32L431xx memory map

DocID028800 Rev 1

| Symbol               | Parameter                                                          |                            | Conditions                  | Тур   | Мах   | Unit |  |  |

|----------------------|--------------------------------------------------------------------|----------------------------|-----------------------------|-------|-------|------|--|--|

|                      |                                                                    | Range 1                    | Wakeup clock MSI = 48 MHz   | 3.8   | 5.7   |      |  |  |

|                      | Wake up time from Stop 0                                           | Range                      | Wakeup clock HSI16 = 16 MHz | 4.1   | 6.9   |      |  |  |

|                      | mode to Run mode in                                                |                            | Wakeup clock MSI = 24 MHz   | 4.07  | 6.2   |      |  |  |

|                      | Flash                                                              | Range 2                    | Wakeup clock HSI16 = 16 MHz | 4.1   | 6.8   |      |  |  |

| +                    |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 8.45  | 11.8  |      |  |  |

| twustop0             |                                                                    | Range 1                    | Wakeup clock MSI = 48 MHz   | 1.5   | 2.9   | μs   |  |  |

|                      | Wake up time from Stop 0                                           | Range                      | Wakeup clock HSI16 = 16 MHz | 2.4   | 2.76  |      |  |  |

|                      | mode to Run mode in                                                |                            | Wakeup clock MSI = 24 MHz   | 2.4   | 3.48  |      |  |  |

|                      | SRAM1                                                              | Range 2                    | Wakeup clock HSI16 = 16 MHz | 2.4   | 2.76  |      |  |  |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 8.16  | 10.94 |      |  |  |

|                      |                                                                    | Dongo 1                    | Wakeup clock MSI = 48 MHz   | 6.34  | 7.86  |      |  |  |

|                      |                                                                    | Range 1                    | Wakeup clock HSI16 = 16 MHz | 6.84  | 8.23  |      |  |  |

|                      | Wake up time from Stop 1 mode to Run in Flash                      | Range 2                    | Wakeup clock MSI = 24 MHz   | 6.74  | 8.1   |      |  |  |

|                      |                                                                    |                            | Wakeup clock HSI16 = 16 MHz | 6.89  | 8.21  | -    |  |  |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 10.47 | 12.1  |      |  |  |

|                      |                                                                    | Range 1                    | Wakeup clock MSI = 48 MHz   | 4.7   | 5.97  |      |  |  |

|                      | Wake up time from Stop 1                                           | Range                      | Wakeup clock HSI16 = 16 MHz | 5.9   | 6.92  |      |  |  |

| t <sub>WUSTOP1</sub> | mode to Run mode in                                                |                            | Wakeup clock MSI = 24 MHz   | 5.4   | 6.51  | μs   |  |  |

|                      | SRAM1                                                              | Range 2                    | Wakeup clock HSI16 = 16 MHz | 5.9   | 6.92  |      |  |  |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 11.1  | 12.2  |      |  |  |

|                      | Wake up time from Stop 1<br>mode to Low-power run<br>mode in Flash | Regulator in<br>low-power  | Makaun alaak MOL = 2 ML     | 16.4  | 17.73 |      |  |  |

|                      | Wake up time from Stop 1<br>mode to Low-power run<br>mode in SRAM1 | mode (LPR=1<br>in PWR_CR1) | Wakeup clock MSI = 2 MHz    | 17.3  | 18.82 |      |  |  |

Table 40. Low-power mode wakeup timings<sup>(1)</sup> (continued)

| Symbol                               | Parameter                              |                     | Conditions |   | Min | Тур  | Мах | Unit |

|--------------------------------------|----------------------------------------|---------------------|------------|---|-----|------|-----|------|

|                                      |                                        |                     | Range 0    | - | -   | 0.6  | 1   |      |

|                                      |                                        |                     | Range 1    | - | -   | 0.8  | 1.2 |      |

|                                      |                                        |                     | Range 2    | - | -   | 1.2  | 1.7 |      |

|                                      |                                        |                     | Range 3    | - | -   | 1.9  | 2.5 |      |

|                                      |                                        |                     | Range 4    | - | -   | 4.7  | 6   |      |

| I <sub>DD</sub> (MSI) <sup>(4)</sup> | MSI oscillator<br>power<br>consumption | MSI and<br>PLL mode | Range 5    | - | -   | 6.5  | 9   | Αμ - |

|                                      |                                        |                     | Range 6    | - | -   | 11   | 15  |      |

|                                      |                                        |                     | Range 7    | - | -   | 18.5 | 25  |      |

|                                      |                                        |                     | Range 8    | - | -   | 62   | 80  |      |

|                                      |                                        |                     | Range 9    | - | -   | 85   | 110 |      |

|                                      |                                        |                     | Range 10   | - | -   | 110  | 130 |      |

|                                      |                                        |                     | Range 11   | - | -   | 155  | 190 |      |

### Table 48. MSI oscillator characteristics<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

2. This is a deviation for an individual part once the initial frequency has been measured.

3. Sampling mode means Low-power run/Low-power sleep modes with Temperature sensor disable.

4. Guaranteed by design.

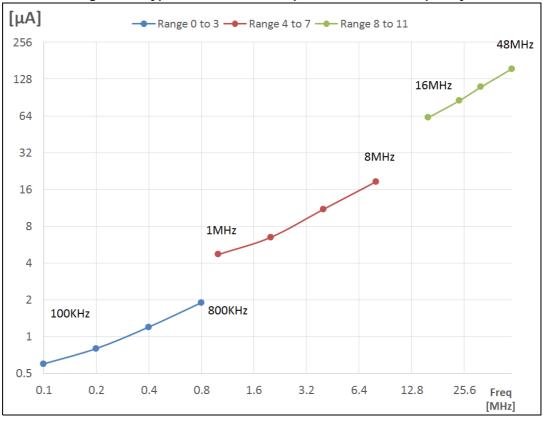

#### Figure 25. Typical current consumption versus MSI frequency

DocID028800 Rev 1

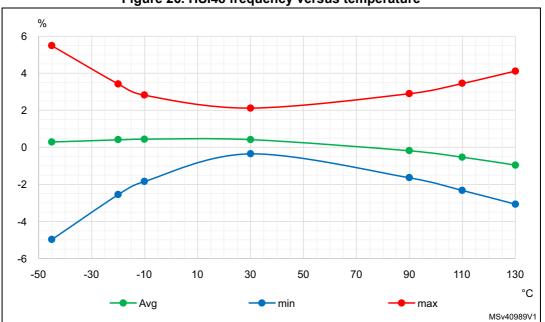

Figure 26. HSI48 frequency versus temperature

### Low-speed internal (LSI) RC oscillator

| Table 50. L | SI oscillator | characteristics <sup>(1)</sup> |

|-------------|---------------|--------------------------------|

|-------------|---------------|--------------------------------|

| Symbol                                 | Parameter                            | Conditions                                      |       | Тур | Max   | Unit |  |  |

|----------------------------------------|--------------------------------------|-------------------------------------------------|-------|-----|-------|------|--|--|

| f                                      | LSI Frequency                        | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 30 °C | 31.04 | -   | 32.96 | kHz  |  |  |

| f <sub>LSI</sub>                       |                                      | $V_{DD}$ = 1.62 to 3.6 V, TA = -40 to 125 °C    | 29.5  | -   | 34    |      |  |  |

| t <sub>SU</sub> (LSI) <sup>(2)</sup>   | LSI oscillator start-<br>up time     | -                                               | -     | 80  | 130   | μs   |  |  |

| t <sub>STAB</sub> (LSI) <sup>(2)</sup> | LSI oscillator<br>stabilization time | 5% of final frequency                           | -     | 125 | 180   | μs   |  |  |

| I <sub>DD</sub> (LSI) <sup>(2)</sup>   | LSI oscillator power consumption     | -                                               | -     | 110 | 180   | nA   |  |  |

1. Guaranteed by characterization results.

2. Guaranteed by design.

## 6.3.9 PLL characteristics

The parameters given in *Table 51* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 21: General operating conditions*.

| Symbol              | Parameter                      | Conditions | Min | Тур | Max | Unit |

|---------------------|--------------------------------|------------|-----|-----|-----|------|

| f                   | PLL input clock <sup>(2)</sup> | -          | 4   | -   | 16  | MHz  |

| <sup>I</sup> PLL_IN | PLL input clock duty cycle     | -          | 45  | -   | 55  | %    |

Table 51. PLL, PLLSAI1 characteristics<sup>(1)</sup>

## 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 54*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                    | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD} = 3.3 \text{ V}, T_A = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 80 MHz,<br>conforming to IEC 61000-4-2 | 3B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, $T_A$ = +25 °C,<br>f <sub>HCLK</sub> = 80 MHz,<br>conforming to IEC 61000-4-4               | 5A              |

Table 54. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

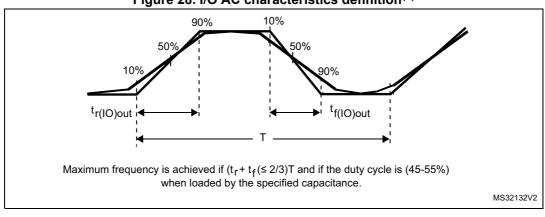

1. Refer to Table 61: I/O AC characteristics.

# 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

| Symbol                 | Parameter                                          | Conditions                        | Min                                 | Тур | Мах                                 | Unit |

|------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------|-----|-------------------------------------|------|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                       | -                                 | -                                   | -   | 0.3 <sub>x</sub> V <sub>DDIOx</sub> | v    |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                      | -                                 | 0.7 <sub>x</sub> V <sub>DDIOx</sub> | -   | -                                   | v    |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis            | -                                 | -                                   | 200 | -                                   | mV   |

| R <sub>PU</sub>        | Weak pull-up<br>equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                  | 40  | 55                                  | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered<br>pulse                       | -                                 | -                                   | -   | 70                                  | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                      | 1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V  | 350                                 | -   | -                                   | ns   |

Table 62. NRST pin characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

# 6.3.17 Analog-to-Digital converter characteristics

Unless otherwise specified, the parameters given in *Table 64* are preliminary values derived from tests performed under ambient temperature,  $f_{PCLK}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 21: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                          | Parameter                          | Conditions                                        | Min                                                     | Тур                                           | Max                                                     | Unit               |  |

|---------------------------------|------------------------------------|---------------------------------------------------|---------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------|--------------------|--|

| V <sub>DDA</sub>                | Analog supply voltage              | -                                                 | 1.62                                                    | -                                             | 3.6                                                     | V                  |  |

| M                               |                                    | V <sub>DDA</sub> ≥ 2 V                            | 2                                                       | -                                             | V <sub>DDA</sub>                                        | V                  |  |

| $V_{REF^+}$                     | Positive reference voltage         | V <sub>DDA</sub> < 2 V                            |                                                         | V <sub>DDA</sub>                              |                                                         | V                  |  |

| V <sub>REF-</sub>               | Negative reference voltage         | -                                                 |                                                         | $V_{SSA}$                                     |                                                         | V                  |  |

| f                               | ADC clock frequency                | Range 1                                           | -                                                       | -                                             | 80                                                      | MHz                |  |

| f <sub>ADC</sub>                | ADC clock frequency                | Range 2                                           | -                                                       | -                                             | 26                                                      | WIHZ               |  |

|                                 |                                    | Resolution = 12 bits                              | -                                                       | -                                             | 5.33                                                    |                    |  |

|                                 | Sampling rate for FAST             | Resolution = 10 bits                              | -                                                       | -                                             | 6.15                                                    |                    |  |

|                                 | channels                           | Resolution = 8 bits                               | -                                                       | -                                             | 7.27                                                    | -                  |  |

| f                               |                                    | Resolution = 6 bits                               | -                                                       | -                                             | 8.88                                                    | Msps               |  |

| f <sub>s</sub>                  | Sampling rate for SLOW             | Resolution = 12 bits                              | -                                                       | -                                             | 4.21                                                    | ivisps             |  |

|                                 |                                    | Resolution = 10 bits                              | -                                                       | -                                             | 4.71                                                    | -                  |  |

|                                 | channels                           | Resolution = 8 bits                               | -                                                       | -                                             | 5.33                                                    | -                  |  |

|                                 |                                    | Resolution = 6 bits                               | -                                                       | -                                             | 6.15                                                    | -                  |  |

| f <sub>TRIG</sub>               | External trigger frequency         | f <sub>ADC</sub> = 80 MHz<br>Resolution = 12 bits | -                                                       | -                                             | 5.33                                                    | MHz                |  |

|                                 |                                    | Resolution = 12 bits                              | -                                                       | -                                             | 15                                                      | 1/f <sub>ADC</sub> |  |

| V <sub>CMIN</sub>               | Input common mode                  | Differential mode                                 | (V <sub>REF+</sub> +<br>V <sub>REF-</sub> )/2<br>- 0.18 | (V <sub>REF+</sub> +<br>V <sub>REF-</sub> )/2 | (V <sub>REF+</sub> +<br>V <sub>REF-</sub> )/2<br>+ 0.18 | V                  |  |

| V <sub>AIN</sub> <sup>(3)</sup> | Conversion voltage range(2)        | -                                                 | 0                                                       | -                                             | V <sub>REF+</sub>                                       | V                  |  |

| R <sub>AIN</sub>                | External input impedance           | -                                                 | -                                                       | -                                             | 50                                                      | kΩ                 |  |

| C <sub>ADC</sub>                | Internal sample and hold capacitor | -                                                 | -                                                       | 5                                             | -                                                       | pF                 |  |

| t <sub>STAB</sub>               | Power-up time                      | -                                                 |                                                         | 1                                             |                                                         |                    |  |

| tau                             | Calibration time                   | f <sub>ADC</sub> = 80 MHz                         |                                                         | 1.45                                          |                                                         |                    |  |

| t <sub>CAL</sub>                |                                    | -                                                 |                                                         | 116                                           |                                                         | 1/f <sub>ADC</sub> |  |

| Table 6 |        | characteristics | (1) (2) |

|---------|--------|-----------------|---------|

| Table 6 | 4. ADC | characteristics | s(1) (2 |

| Sym-<br>bol | Parameter               | (                               | Conditions <sup>(4)</sup> |                          |      |      |     | Unit                 |  |

|-------------|-------------------------|---------------------------------|---------------------------|--------------------------|------|------|-----|----------------------|--|

|             |                         |                                 | Single                    | Fast channel (max speed) | -    | 4    | 6.5 |                      |  |

| ET          | Total                   |                                 | ended                     | Slow channel (max speed) | -    | 4    | 6.5 |                      |  |

|             | unadjusted<br>error     |                                 | Differential              | Fast channel (max speed) | -    | 3.5  | 5.5 |                      |  |

|             |                         |                                 | Dillerential              | Slow channel (max speed) | -    | 3.5  | 5.5 |                      |  |

|             |                         |                                 | Single                    | Fast channel (max speed) | -    | 1    | 4.5 |                      |  |

| EO          | Offset                  |                                 | ended                     | Slow channel (max speed) | -    | 1    | 5   |                      |  |

| EU          | error                   |                                 | Differential              | Fast channel (max speed) | -    | 1.5  | 3   |                      |  |

|             |                         |                                 | Dillerential              | Slow channel (max speed) | -    | 1.5  | 3   |                      |  |

|             |                         |                                 | Single                    | Fast channel (max speed) | -    | 2.5  | 6   |                      |  |

| EG          | Coin orror              |                                 | ended                     | Slow channel (max speed) | -    | 2.5  | 6   |                      |  |

| EG          | G Gain error            |                                 | Differential              | Fast channel (max speed) | -    | 2.5  | 3.5 | - LSB<br>-<br>-<br>- |  |

|             |                         |                                 | Dillerential              | Slow channel (max speed) | -    | 2.5  | 3.5 |                      |  |

|             |                         | earity                          | Single<br>ended           | Fast channel (max speed) | -    | 1    | 1.5 |                      |  |

| ED          | Differential            |                                 |                           | Slow channel (max speed) | -    | 1    | 1.5 |                      |  |

| ED          | error                   |                                 | Differential              | Fast channel (max speed) | -    | 1    | 1.2 |                      |  |

|             |                         |                                 |                           | Slow channel (max speed) | -    | 1    | 1.2 |                      |  |

|             |                         | Sampling rate $\leq 5.33$ Msps, | Single<br>ended           | Fast channel (max speed) | -    | 1.5  | 3.5 |                      |  |

| EL          | Integral                |                                 |                           | Slow channel (max speed) | -    | 1.5  | 3.5 | -                    |  |

| EL          | linearity<br>error      |                                 | D'fferentiet              | Fast channel (max speed) | -    | 1    | 3   |                      |  |

|             |                         |                                 | Differential              | Slow channel (max speed) | -    | 1    | 2.5 |                      |  |

|             |                         |                                 | Single                    | Fast channel (max speed) | 10   | 10.5 | -   |                      |  |

| ENOB        | Effective number of     |                                 | ended                     | Slow channel (max speed) | 10   | 10.5 | -   | bits                 |  |

| ENOD        | bits                    |                                 | Differential              | Fast channel (max speed) | 10.7 | 10.9 | -   | DILS                 |  |

|             |                         |                                 | Dillerential              | Slow channel (max speed) | 10.7 | 10.9 | -   |                      |  |

|             | Cignal to               |                                 | Single                    | Fast channel (max speed) | 62   | 65   | -   |                      |  |

| SINAD       | Signal-to-<br>noise and |                                 | ended                     | Slow channel (max speed) | 62   | 65   | -   | dB                   |  |

| SINAD       | distortion<br>ratio     |                                 | Differential              | Fast channel (max speed) | 66   | 67.4 | -   |                      |  |

|             | Tallo                   |                                 | Differential              | Slow channel (max speed) | 66   | 67.4 | -   |                      |  |

|             |                         |                                 | Single                    | Fast channel (max speed) | 64   | 66   | -   |                      |  |

|             | Signal-to-              |                                 | ended                     | Slow channel (max speed) | 64   | 66   | -   | 1                    |  |

| SNR         | noise ratio             |                                 | Differential              | Fast channel (max speed) | 66.5 | 68   | -   |                      |  |

|             |                         |                                 | Differential              | Slow channel (max speed) | 66.5 | 68   | -   |                      |  |

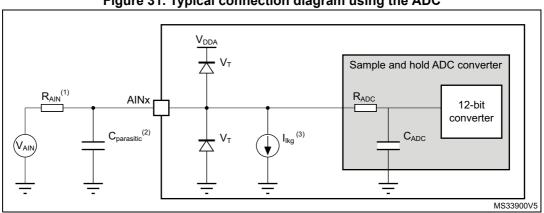

Figure 31. Typical connection diagram using the ADC

- Refer to Table 64: ADC characteristics for the values of  $\mathsf{R}_{AIN},\,\mathsf{R}_{ADC}$  and  $\mathsf{C}_{ADC}$ 1.

- $C_{\text{parasitic}}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (refer to *Table 59: I/O static characteristics* for the value of the pad capacitance). A high  $C_{\text{parasitic}}$  value will downgrade conversion accuracy. To remedy this,  $f_{\text{ADC}}$  should be reduced. 2.

- 3. Refer to Table 59: I/O static characteristics for the values of Ilkg.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in Figure 17: Power supply scheme. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

#### Voltage reference buffer characteristics 6.3.19

|                       |                                                                                                 | Table 72. VRE                     | BUF characte               | eristics <sup>(1)</sup>  |       | -                                       |         |

|-----------------------|-------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|--------------------------|-------|-----------------------------------------|---------|

| Symbol                | Parameter                                                                                       | Conditio                          | ons                        | Min                      | Тур   | Max                                     | Unit    |

|                       |                                                                                                 | Normal mode                       | V <sub>RS</sub> = 0        | 2.4                      | -     | 3.6                                     |         |

| V                     | Analog supply                                                                                   | Normal mode                       | V <sub>RS</sub> = 1        | 2.8                      | -     | 3.6                                     |         |

| $V_{DDA}$             | voltage                                                                                         | Degraded mode <sup>(2)</sup>      | V <sub>RS</sub> = 0        | 1.65                     | -     | 2.4                                     |         |

|                       |                                                                                                 |                                   | V <sub>RS</sub> = 1        | 1.65                     | -     | 2.8                                     | V       |

|                       |                                                                                                 | Normal mode                       | V <sub>RS</sub> = 0        | 2.046 <sup>(3)</sup>     | 2.048 | 2.049 <sup>(3)</sup>                    | v       |

| V <sub>REFBUF</sub> _ | Voltage reference                                                                               | Normarmode                        | V <sub>RS</sub> = 1        | 2.498 <sup>(3)</sup>     | 2.5   | 2.502 <sup>(3)</sup>                    |         |

| OUT                   | output                                                                                          | Degraded mode <sup>(2)</sup>      | V <sub>RS</sub> = 0        | V <sub>DDA</sub> -150 mV | -     | V <sub>DDA</sub>                        |         |

|                       |                                                                                                 |                                   | V <sub>RS</sub> = 1        | V <sub>DDA</sub> -150 mV | -     | V <sub>DDA</sub>                        |         |

| TRIM                  | Trim step resolution                                                                            | -                                 | -                          | -                        | ±0.05 | ±0.1                                    | %       |

| CL                    | Load capacitor                                                                                  | -                                 | -                          | 0.5                      | 1     | 1.5                                     | μF      |

| esr                   | Equivalent<br>Serial Resistor<br>of Cload                                                       | -                                 | -                          | -                        | -     | 2                                       | Ω       |

| I <sub>load</sub>     | Static load current                                                                             | -                                 | -                          | -                        | -     | 4                                       | mA      |

| 1                     | Line regulation                                                                                 | 2.8 V ≤ V <sub>DDA</sub> ≤ 3.6 V  | I <sub>load</sub> = 500 μA | -                        | 200   | 1000                                    | ppm/V   |

| I <sub>line_reg</sub> |                                                                                                 |                                   | I <sub>load</sub> = 4 mA   | -                        | 100   | 500                                     | phu/v   |

| I <sub>load_reg</sub> | Load<br>regulation                                                                              | 500 µA ≤ I <sub>load</sub> ≤4 mA  | Normal mode                | -                        | 50    | 500                                     | ppm/mA  |

| Т                     | Temperature                                                                                     | -40 °C < T <sub>J</sub> < +125 °C |                            | -                        | -     | T <sub>coeff</sub> _<br>vrefint +<br>50 | ppm/ °C |

| T <sub>Coeff</sub>    | coefficient                                                                                     | 0 °C < T <sub>J</sub> < +50 °C    |                            | -                        | -     | T <sub>coeff</sub> _<br>vrefint +<br>50 | ppm/ C  |

| PSRR                  | Power supply                                                                                    | DC                                |                            | 40                       | 60    | -                                       | dB      |

| TORK                  | rejection                                                                                       | 100 kHz                           |                            | 25                       | 40    | -                                       | ЧD      |

|                       |                                                                                                 | $CL = 0.5 \ \mu F^{(4)}$          |                            | -                        | 300   | 350                                     |         |

| t <sub>START</sub>    | Start-up time                                                                                   | $CL = 1.1 \ \mu F^{(4)}$          |                            | -                        | 500   | 650                                     | μs      |

|                       |                                                                                                 | $CL = 1.5 \ \mu F^{(4)}$          |                            | -                        | 650   | 800                                     |         |

| I <sub>INRUSH</sub>   | Control of<br>maximum DC<br>current drive<br>on VREFBUF_<br>OUT during<br>start-up phase<br>(5) | -                                 | -                          | -                        | 8     | -                                       | mA      |

# (1)

### **Quad SPI characteristics**

Unless otherwise specified, the parameters given in *Table 83* and *Table 84* for Quad SPI are derived from tests performed under the ambient temperature,  $f_{AHB}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 21: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 15 or 20 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics.

| Symbol              | Parameter                | Conditions                                                                   | Min                    | Тур | Max                    | Unit    |  |

|---------------------|--------------------------|------------------------------------------------------------------------------|------------------------|-----|------------------------|---------|--|

|                     |                          | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 20 pF<br>Voltage Range 1 | -                      | -   | 40                     |         |  |

| F <sub>CK</sub>     | Quad SPI clock frequency | $1.71 < V_{DD} < 3.6 V$ , $C_{LOAD} = 15 pF$<br>Voltage Range 1              | -                      | -   | 48                     | MHz     |  |

| 1/t <sub>(CK)</sub> |                          | $2.7 < V_{DD} < 3.6 V$ , $C_{LOAD} = 15 pF$<br>Voltage Range 1               | -                      | -   | 60                     | 1011 12 |  |

|                     |                          | 1.71 < V <sub>DD</sub> < 3.6 V C <sub>LOAD</sub> = 20 pF<br>Voltage Range 2  |                        | -   | 26                     |         |  |

| t <sub>w(CKH)</sub> | Quad SPI clock high and  | f <sub>AHBCLK</sub> = 48 MHz, presc=0                                        | t <sub>(CK)</sub> /2-2 | -   | t <sub>(CK)</sub> /2   |         |  |

| t <sub>w(CKL)</sub> | low time                 | AHBCLK - 40 Minz, prese-0                                                    |                        | -   | t <sub>(CK)</sub> /2+2 |         |  |

| t ann               | Data input setup time    | Voltage Range 1                                                              | 2                      | -   | -                      |         |  |

| t <sub>s(IN)</sub>  |                          | Voltage Range 2                                                              | 3.5                    | -   | -                      |         |  |

| +                   | Data input hold time     | Voltage Range 1                                                              | 5                      | -   | -                      | ns      |  |

| t <sub>h(IN)</sub>  |                          | Voltage Range 2 6.5 -                                                        |                        | -   | -                      | 115     |  |

| +                   | Data autaut valid tima   | Voltage Range 1                                                              | -                      | 1   | 5                      | -       |  |

| t <sub>v(OUT)</sub> | Data output valid time   | Voltage Range 2                                                              | -                      | 3   | 5                      |         |  |

| +                   | Data output hold time    | Voltage Range 1                                                              | 0                      | -   | -                      |         |  |

| t <sub>h(OUT)</sub> | Data output hold time    | Voltage Range 2                                                              | 0                      | -   | -                      |         |  |

| Table 83. Qua | ad SPI characteristics | in | SDR | mode <sup>(1)</sup> |

|---------------|------------------------|----|-----|---------------------|

|---------------|------------------------|----|-----|---------------------|

1. Guaranteed by characterization results.

# CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

#### **SWPMI** characteristics

The Single Wire Protocol Master Interface (SWPMI) and the associated SWPMI\_IO transceiver are compliant with the ETSI TS 102 613 technical specification.

| Symbol                | Parameter Conditions         |                                               | Min | Тур | Max | Unit |

|-----------------------|------------------------------|-----------------------------------------------|-----|-----|-----|------|

| t <sub>SWPSTART</sub> | SWPMI regulator startup time | SWP Class B<br>2.7 V ≤ V <sub>DD</sub> ≤ 3,3V | -   | -   | 300 | μs   |

| towner                | SWP bit duration             | V <sub>CORE</sub> voltage range 1             | 500 | -   | -   | ns   |

| ISWPBIT               |                              | V <sub>CORE</sub> voltage range 2             | 620 | -   | -   | 115  |

Table 88. SWPMI electrical characteristics

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

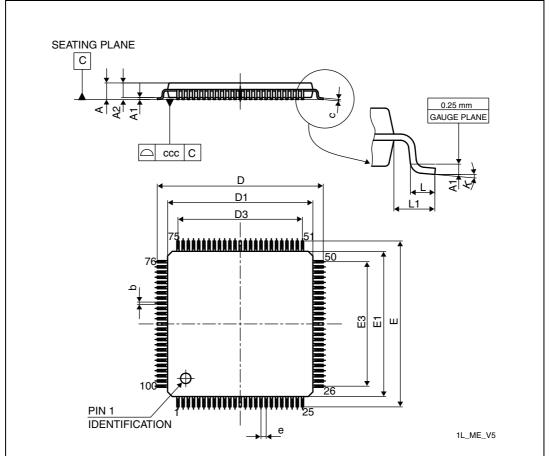

# 7.1 LQFP100 package information

Figure 42. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 89. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

| Symbol | millimeters |     |       | inches <sup>(1)</sup> |     |        |

|--------|-------------|-----|-------|-----------------------|-----|--------|

| Symbol | Min         | Тур | Мах   | Min                   | Тур | Max    |

| А      | -           | -   | 1.600 | -                     | -   | 0.0630 |

| A1     | 0.050       | -   | 0.150 | 0.0020                | -   | 0.0059 |

|                   |       |             | ge mechanic |        | (1)                   |        |  |

|-------------------|-------|-------------|-------------|--------|-----------------------|--------|--|

| Symbol            |       | millimeters |             |        | inches <sup>(1)</sup> |        |  |

| Cymbol            | Min   | Тур         | Max         | Min    | Тур                   | Max    |  |

| А                 | 0.525 | 0.555       | 0.585       | 0.0207 | 0.0219                | 0.0230 |  |

| A1                | -     | 0.175       | -           | -      | 0.0069                | -      |  |

| A2                | -     | 0.380       | -           | -      | 0.0150                | -      |  |

| A3 <sup>(2)</sup> | -     | 0.025       | -           | -      | 0.0010                | -      |  |

| b <sup>(3)</sup>  | 0.220 | 0.250       | 0.280       | 0.0087 | 0.0098                | 0.0110 |  |

| D                 | 3.106 | 3.141       | 3.176       | 0.1223 | 0.1237                | 0.1250 |  |

| Е                 | 3.092 | 3.127       | 3.162       | 0.1217 | 0.1231                | 0.1245 |  |

| е                 | -     | 0.400       | -           | -      | 0.0157                | -      |  |

| e1                | -     | 2.400       | -           | -      | 0.0945                | -      |  |

| e2                | -     | 2.400       | -           | -      | 0.0945                | -      |  |

| F                 | -     | 0.3705      | -           | -      | 0.0146                | -      |  |

| G                 | -     | 0.3635      | -           | -      | 0.0143                | -      |  |

| ааа               | -     | -           | 0.100       | -      | -                     | 0.0039 |  |

| bbb               | -     | -           | 0.100       | -      | -                     | 0.0039 |  |

| CCC               | -     | -           | 0.100       | -      | -                     | 0.0039 |  |

| ddd               | -     | -           | 0.050       | -      | -                     | 0.0020 |  |

| eee               | -     | -           | 0.050       | -      | -                     | 0.0020 |  |

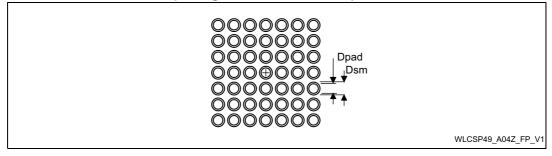

# Table 97. WLCSP49 - 49-ball, 3.141 x 3.127 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

# Figure 58. WLCSP49 - 49-ball, 3.141 x 3.127 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |  |

| А      | -     | -           | 1.600 | -      | -                     | 0.0630 |  |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |  |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |  |

| b      | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |  |

| с      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |

| D      | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |  |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |  |

| D3     | -     | 5.500       | -     | -      | 0.2165                | -      |  |

| E      | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |  |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |  |

| E3     | -     | 5.500       | -     | -      | 0.2165                | -      |  |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |  |

| L1     | -     | 1.000       | -     | -      | 0.0394                | -      |  |

| k      | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |  |

| CCC    | -     | -           | 0.080 | -      | -                     | 0.0031 |  |

| Table 99. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 7.10 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 21: General operating conditions*.

The maximum chip-junction temperature,  $\mathsf{T}_{\mathsf{J}}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma \; ((\mathsf{V}_{\mathsf{DDIOx}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                         | Value | Unit |

|-----------------|-----------------------------------------------------------------------------------|-------|------|

| Θ <sub>JA</sub> | <b>Thermal resistance junction-ambient</b><br>UFQFPN48 - 7 × 7 mm / 0.5 mm pitch  | 33    | °C/W |

|                 | <b>Thermal resistance junction-ambient</b><br>LQFP48 - 7 × 7 mm / 0.5 mm pitch    | 57    |      |

|                 | Thermal resistance junction-ambient<br>WLCSP49 3.141 x 3.127 / 0.4 mm pitch       | 48    |      |

|                 | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch         | 46    |      |

|                 | <b>Thermal resistance junction-ambient</b><br>UFBGA64 - 5 × 5 mm / 0.5 mm pitch   | 65    |      |

|                 | Thermal resistance junction-ambient<br>WLCSP64 3.141 x 3.127 / 0.35 mm pitch      | 46    |      |

|                 | <b>Thermal resistance junction-ambient</b><br>LQFP100 - 14 × 14 mm / 0.5 mm pitch | 42    |      |

|                 | <b>Thermal resistance junction-ambient</b><br>UFBGA100 - 7 × 7 mm / 0.5 mm pitch  | 57    |      |

Table 102. Package thermal characteristics

## 7.10.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org