Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | EBI/EMI, UART/USART                                                     |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-DIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p87c51rc-4n-112 |

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33 MHz) 8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

#### DESCRIPTION

Three different Single-Chip 8-Bit Microcontroller families are presented in this datasheet:

- 8XC54/8XC58

- 80C51FA/8XC51FA/8XC51FB/8XC51FC

- 80C51RA+/8XC51RA+/8XC51RB+/8XC51RC+/8XC51RD+

For applications requiring 4K ROM/EPROM, see the 8XC51/80C31 8-bit CMOS (low voltage, low power, and high speed) microcontroller families datasheet.

All the families are Single-Chip 8-Bit Microcontrollers manufactured in advanced CMOS process and are derivatives of the 80C51 microcontroller family. All the devices have the same instruction set as the 80C51.

These devices provide architectural enhancements that make them applicable in a variety of applications for general control systems.

| ROM/EPROM<br>Memory Size<br>(X by 8) | RAM Size<br>(X by 8) | Programmable<br>Timer Counter<br>(PCA) | Hardware<br>Watch Dog<br>Timer |

|--------------------------------------|----------------------|----------------------------------------|--------------------------------|

| 80C31/8XC51                          |                      |                                        |                                |

| 0K/4K                                | 128                  | No                                     | No                             |

| 8XC54/58                             |                      |                                        |                                |

| 0K/8K/16K/32K                        | 256                  | No                                     | No                             |

| 80C51FA/8XC51                        | FA/FB/FC             |                                        |                                |

| 0K/8K/16K/32K                        | 256                  | Yes                                    | No                             |

| 80C51RA+/8XC5                        | 1RA+/RB+/RC          | +                                      |                                |

| 0K/8K/16K/32K                        | 512                  | Yes                                    | Yes                            |

| 8XC51RD+                             |                      |                                        |                                |

| 64K                                  | 1024                 | Yes                                    | Yes                            |

The ROMless devices, 80C51FA, and 80C51RA+ can address up to 64K of external memory. All the devices have four 8-bit I/O ports, three 16-bit timer/event counters, a multi-source, four-priority-level, nested interrupt structure, an enhanced UART and on-chip oscillator and timing circuits. For systems that require extra memory capability up to 64k bytes, each can be expanded using standard TTL-compatible memories and logic.

Its added features make it an even more powerful microcontroller for applications that require pulse width modulation, high-speed I/O and up/down counting capabilities such as motor control. It also has a more versatile serial channel that facilitates multiprocessor communications.

#### **FEATURES**

- 80C51 Central Processing Unit

- Speed up to 33 MHz

- Full static operation

- Operating voltage range: 2.7 V to 5.5 V @ 16 MHz

- Security bits:

- ROM 2 bits

- OTP-EPROM 3 bits

- Encryption array 64 bytes

- RAM expandable to 64K bytes

- 4 level priority interrupt

- 6 or7 interrupt sources, depending on device

- Four 8-bit I/O ports

- Full-duplex enhanced UART

- Framing error detection

- Automatic address recognition

- Power control modes

- Clock can be stopped and resumed

- Idle mode

- Power down mode

- Programmable clock out

- Second DPTR register

- Asynchronous port reset

- Low EMI (inhibit ALE)

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33 MHz)

8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

## **PIN DESCRIPTIONS**

|                 | PII        | PIN NUMBER   |               |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|------------|--------------|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC        | DIP        | LCC          | QFP           | TYPE       | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>SS</sub> | 20         | 22           | 16            | I          | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>CC</sub> | 40         | 44           | 38            | ı          | Power Supply: This is the power supply voltage for normal, idle, and power-down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P0.0-0.7        | 39–32      | 43–36        | 37–30         | I/O        | <b>Port 0:</b> Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s. Port 0 also outputs the code bytes during program verification and received code bytes during EPROM programming. External pull-ups are required during program verification.                                                                                                                                                                                                                                                                                                                                   |

| P1.0-P1.7       | 1–8        | 2–9          | 40–44,<br>1–3 | I/O        | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 1 also receives the low-order address byte during program memory verification.                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |            |              |               |            | Alternate functions for 8XC51FX and 8XC51RX+ Port 1 include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 1          | 2            | 40            | I/O        | T2 (P1.0): Timer/Counter 2 external count input/Clockout (see Programmable Clock-Out)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 | 2          | 3            | 41            | 1          | T2EX (P1.1): Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 3          | 4            | 42            | 1          | ECI (P1.2): External Clock Input to the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 | 4          | 5            | 43            | I/O        | CEX0 (P1.3): Capture/Compare External I/O for PCA module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                 | 5          | 6            | 44            | 1/0        | CEX1 (P1.4): Capture/Compare External I/O for PCA module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                 | 6          | 7            | 1             | 1/0        | CEX2 (P1.5): Capture/Compare External I/O for PCA module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                 | 7          | 8            | 2             | I/O<br>I/O | CEX3 (P1.6): Capture/Compare External I/O for PCA module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P2.0-P2.7       | 8<br>21–28 | 9<br>24–31   | 18–25         | 1/0        | CEX4 (P1.7): Capture/Compare External I/O for PCA module 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1 2.0 1 2.7     | 21 20      | 24 01        | 10 20         | 1/0        | <b>Port 2:</b> Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV @Ri), port 2 emits the contents of the P2 special function register. Some Port 2 pins receive the high order address bits during EPROM programming and verification. |

| P3.0-P3.7       | 10–17      | 11,<br>13–19 | 5,<br>7–13    | I/O        | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 3 also serves the special features of the 80C51 family, as listed below:                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 | 10         | 11           | 5             | 1          | RxD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 11         | 13           | 7             | 0          | TxD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 12         | 14           | 8             | l !        | INTO (P3.2): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 | 13         | 15           | 9             | l :        | INT1 (P3.4): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 | 14<br>15   | 16<br>17     | 10<br>11      | l ¦        | T0 (P3.4): Timer 0 external input T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | 16         | 18           | 12            | 0          | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 17         | 19           | 13            | 0          | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RST             | 9          | 10           | 4             | ı          | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to V <sub>SS</sub> permits a power-on reset using only an external capacitor to V <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ALE/PROG        | 30         | 33           | 27            | 0          | Address Latch Enable/Program Pulse: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during EPROM programming. ALE can be disabled by setting SFR auxiliary.0. With this bit set, ALE will be active only during a MOVX instruction.                                                                                                                                                                                                                                                                                                             |

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33 MHz)

8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

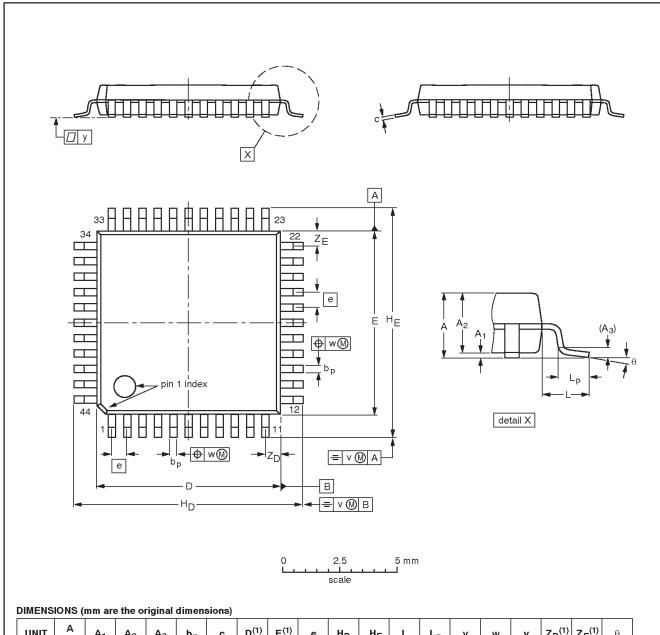

## **8XC54/58 ORDERING INFORMATION**

|     | MEMORY SIZE<br>16K×8 | MEMORY SIZE<br>32K×8 | TEMPERATURE RANGE °C<br>AND PACKAGE        | VOLTAGE<br>RANGE | FREQ.<br>(MHz) | DWG.<br># |

|-----|----------------------|----------------------|--------------------------------------------|------------------|----------------|-----------|

| ROM | P80C54SBPN           | P80C58SBPN           | 0 to +70, Plastic Dual In-line Package     | 2.7 V to         | 0 to 16        | SOT129-1  |

| OTP | P87C54SBPN           | P87C58SBPN           | 0 to +70, Flastic Dual III-lille Fackage   | 5.5 V            | 0 10 10        | 301129-1  |

| ROM | P80C54SBAA           | P80C58SBAA           | 0 to +70, Plastic Leaded Chip Carrier      | 2.7 V to         | 0 to 16        | SOT187-2  |

| OTP | P87C54SBAA           | P87C58SBAA           | 0 to +70, Plastic Leaded Chip Carrier      | 5.5 V            | 0 10 16        | 301107-2  |

| ROM | P80C54SBBB           | P80C58SBBB           | 0 to +70, Plastic Quad Flat Pack           | 2.7 V to         | 0 to 16        | SOT307-2  |

| OTP | P87C54SBBB           | P87C58SBBB           | 0 to +70, Flastic Quad Flat Fack           | 5.5 V            | 0 10 10        | 301301-2  |

| ROM | P80C54SFPN           | P80C58SFPN           | -40 to +85, Plastic Dual In-line Package   | 2.7 V to         | 0 to 16        | SOT129-1  |

| OTP | P87C54SFPN           | P87C58SFPN           | -40 to +65, Flastic Dual III-lille Fackage | 5.5 V            | 0 10 10        | 301129-1  |

| ROM | P80C54SFA A          | P80C58SFA A          | -40 to +85, Plastic Leaded Chip Carrier    | 2.7 V to         | 0 to 16        | SOT187-2  |

| OTP | P87C54SFA A          | P87C58SFA A          | -40 to +65, Flastic Leaded Chip Camer      | 5.5 V            | 0 10 10        | 301107-2  |

| ROM | P80C54SFBB           | P80C58SFBB           | –40 to +85, Plastic Quad Flat Pack         | 2.7 V to         | 0 to 16        | SOT307-2  |

| OTP | P87C54SFBB           | P87C58SFBB           | -40 to 703, Flastic Quad Flat Fack         | 5.5 V            | 0 10 10        | 301301-2  |

| ROM | P80C54UBAA           | P80C58UBAA           | 0 to +70, Plastic Leaded Chip Carrier      | 5 V              | 0 to 33        | SOT187-2  |

| OTP | P87C54UBAA           | P87C58UBAA           | 0 to +70, Plastic Leaded Chip Carrier      | 5 V              | 0 10 33        | 301107-2  |

| ROM | P80C54UBPN           | P80C58UBPN           | 0 to +70, Plastic Dual In-line Package     | 5 V              | 0 to 33        | SOT129-1  |

| OTP | P87C54UBPN           | P87C58UBPN           | 0 to +70, Flastic Dual III-IIIIe Fackage   | J V              | 0 10 33        | 301129-1  |

| ROM | P80C54UBBB           | P80C58UBBB           | 0 to +70, Plastic Quad Flat Pack           | 5 V              | 0 to 33        | SOT307-2  |

| OTP | P87C54UBBB           | P87C58UBBB           | 0 to +70, Flastic Quad Flat Fack           | J V              | 0 10 33        | 301301-2  |

| ROM | P80C54UFAA           | P80C58UFA A          | -40 to +85, Plastic Leaded Chip Carrier    | 5 V              | 0 to 33        | SOT187-2  |

| OTP | P87C54UFAA           | P87C58UFA A          | -40 to 405, Flastic Leaded Chip Camel      | J 5 V            | 0 10 33        | 301107-2  |

| ROM | P80C54UFPN           | P80C58UFPN           | -40 to +85, Plastic Dual In-line Package   | 5 V              | 0 to 33        | SOT129-1  |

| OTP | P87C54UFPN           | P87C58UFPN           | -40 to 700, Flastic Dual III-IIIIe Package | 5 v              | 0 10 33        | 301129-1  |

| ROM | P80C54UFBB           | P80C58UFBB           | –40 to +85, Plastic Quad Flat Pack         | 5 V              | 0 to 33        | SOT307-2  |

| OTP | P87C54UFBB           | P87C58UFBB           | -40 to 400, Flastic Quau Flat Pack         | 5 V              | 0 10 33        | 301307-2  |

Note: For Multi Time Programmable devices, See P89C51RX+

Flash datasheet.

## 87C51RA+/RB+/RC+/RD+ AND 80C51RA+ ORDERING INFORMATION

|     | MEMORY SIZE<br>8K×8 | MEMORY SIZE<br>16K×8 | MEMORY SIZE 32K × 8 | MEMORY SIZE<br>64K×8 | ROMIess                  | TEMPERATURE RANGE °C<br>AND PACKAGE | VOLTAGE<br>RANGE | FREQ.<br>(MHz) | DWG.<br># |

|-----|---------------------|----------------------|---------------------|----------------------|--------------------------|-------------------------------------|------------------|----------------|-----------|

| ROM | P83C51RA+4N         | P83C51RB+4N          | P83C51RC+4N         | P83C51RD+4N          | P80C51RA+4N              | 0 to +70,                           | 2.7V to 5.5V     | 0 to 16        | SOT129-1  |

| OTP | P87C51RA+4N         | P87C51RB+4N          | P87C51RC+4N         | P87C51RD+4N          | 1 000311(A+41)           | 40-Pin Plastic Dual In-line Pkg.    | 2.7 V 10 3.3 V   | 0 10 10        | 301129-1  |

| ROM | P83C51RA+4A         | P83C51RB+4A          | P83C51RC+4A         | P83C51RD+4A          | P80C51RA+4A              | 0 to +70,                           | 2.7V to 5.5V     | 0 to 16        | SOT187-2  |

| OTP | P87C51RA+4A         | P87C51RB+4A          | P87C51RC+4A         | P87C51RD+4A          | F00C3TRA <del>T4</del> A | 44-Pin Plastic Leaded Chip Carrier  | 2.7 V 10 3.3 V   | 0 10 10        | 301107-2  |

| ROM | P83C51RA+4B         | P83C51RB+4B          | P83C51RC+4B         | P83C51RD+4B          | P80C51RA+4B              | 0 to +70,                           | 2.7V to 5.5V     | 0 to 16        | SOT307-2  |

| OTP | P87C51RA+4B         | P87C51RB+4B          | P87C51RC+4B         | P87C51RD+4B          | POUCSTRA+4B              | 44-Pin Plastic Quad Flat Pack       | 2.7 V 10 5.5 V   | 0 10 16        | 301307-2  |

| ROM | P83C51RA+5N         | P83C51RB+5N          | P83C51RC+5N         | P83C51RD+5N          | DOOCEADA JEN             | -40 to +85,                         | 0.7\/ to F.E\/   | 0 to 16        | SOT129-1  |

| OTP | P87C51RA+5N         | P87C51RB+5N          | P87C51RC+5N         | P87C51RD+5N          | P80C51RA+5N              | 40-Pin Plastic Dual In-line Pkg.    | 2.7V to 5.5V     | 0 to 16        | 301129-1  |

| ROM | P83C51RA+5A         | P83C51RB+5A          | P83C51RC+5A         | P83C51RD+5A          | DOOCEADA LEA             | -40 to +85,                         | 0.7\/ to F.E\/   | 0 to 16        | SOT187-2  |

| OTP | P87C51RA+5A         | P87C51RB+5A          | P87C51RC+5A         | P87C51RD+5A          | P80C51RA+5A              | 44-Pin Plastic Leaded Chip Carrier  | 2.7V to 5.5V     | 0 to 16        | 301107-2  |

| ROM | P83C51RA+5B         | P83C51RB+5B          | P83C51RC+5B         | P83C51RD+5B          | DOOCEADA . ED            | -40 to +85,                         | 2.7V to 5.5V     | 0 += 40        | COT207.0  |

| OTP | P87C51RA+5B         | P87C51RB+5B          | P87C51RC+5B         | P87C51RD+5B          | P80C51RA+5B              | 44-Pin Plastic Quad Flat Pack       | 2.7 V 10 5.5 V   | 0 to 16        | SOT307-2  |

| ROM | P83C51RA+IN         | P83C51RB+IN          | P83C51RC+IN         | P83C51RD+IN          | DOOCEADA JIN             | 0 to +70,                           | 5V               | 0.4 00         | COT400.4  |

| OTP | P87C51RA+IN         | P87C51RB+IN          | P87C51RC+IN         | P87C51RD+IN          | P80C51RA+IN              | 40-Pin Plastic Dual In-line Pkg.    | ον               | 0 to 33        | SOT129-1  |

| ROM | P83C51RA+IA         | P83C51RB+IA          | P83C51RC+IA         | P83C51RD+IA          | P80C51RA+IA              | 0 to +70,                           | 5V               | 0 to 33        | SOT187-2  |

| OTP | P87C51RA+IA         | P87C51RB+IA          | P87C51RC+IA         | P87C51RD+IA          | 1 0003 INATIA            | 44-Pin Plastic Leaded Chip Carrier  | 3 V              | 0 10 33        | 301107-2  |

| ROM | P83C51RA+IB         | P83C51RB+IB          | P83C51RC+IB         | P83C51RD+IB          | P80C51RA+IB              | 0 to +70,                           | 5V               | 0 to 33        | SOT307-2  |

| OTP | P87C51RA+IB         | P87C51RB+IB          | P87C51RC+IB         | P87C51RD+IB          | FOUCSTRAFIB              | 44-Pin Plastic Quad Flat Pack       | 3 V              | 0 10 33        | 301307-2  |

| ROM | P83C51RA+JN         | P83C51RB+JN          | P83C51RC+JN         | P83C51RD+JN          | P80C51RA+JN              | -40 to +85,                         | 5V               | 0 to 33        | SOT129-1  |

| OTP | P87C51RA+JN         | P87C51RB+JN          | P87C51RC+JN         | P87C51RD+JN          | POUCSTRA+JIN             | 40-Pin Plastic Dual In-line Pkg.    | 3 0              | 0 10 33        | 301129-1  |

| ROM | P83C51RA+JA         | P83C51RB+JA          | P83C51RC+JA         | P83C51RD+JA          | P80C51RA+JA              | -40 to +85,                         | 5V               | 0 40 22        | SOT187-2  |

| OTP | P87C51RA+JA         | P87C51RB+JA          | P87C51RC+JA         | P87C51RD+JA          | PouCotra+JA              | 44-Pin Plastic Leaded Chip Carrier  | ον               | 0 to 33        | 301187-2  |

| ROM | P83C51RA+JB         | P83C51RB+JB          | P83C51RC+JB         | P83C51RD+JB          | P80C51RA+JB              | -40 to +85,                         | 5V               | 0 to 33        | SOT307-2  |

| OTP | P87C51RA+JB         | P87C51RB+JB          | P87C51RC+JB         | P87C51RD+JB          | 1 00001KATJB             | 44-Pin Plastic Quad Flat Pack       | 3 v              | 0 10 33        | 301301-2  |

Note: For Multi Time Programmable devices, See P89C51RX+ Flash datasheet.

8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

Product specification

Philips Semiconductors

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMIess, low voltage (2.7V-5.5V),

low power, high speed (33MHz)

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33MHz)

8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

Table 2. 8XC51FA/FB/FC, 8XC51RA+/RB+/RC+/RD+ Special Function Registers

| SYMBOL              | DESCRIPTION                                                     | DIRECT<br>ADDRESS | BIT A   | ADDRESS   | , SYMBO   | L, OR AL          | TERNATIV  | E PORT    | FUNCTIO              | N<br>LSB  | RESET<br>VALUE |

|---------------------|-----------------------------------------------------------------|-------------------|---------|-----------|-----------|-------------------|-----------|-----------|----------------------|-----------|----------------|

| ACC*                | Accumulator                                                     | E0H               | E7      | E6        | E5        | E4                | E3        | E2        | E1                   | E0        | 00H            |

| AUXR#               | Auxiliary                                                       | 8EH               | -       | -         | -         | -                 | -         | -         | EXTRAM<br>(RX+ only) | AO        | xxxxxx00B      |

| AUXR1#              | Auxiliary 1                                                     | A2H               | -       | -         | -         | LPEP <sup>3</sup> | GF3       | 0         | -                    | DPS       | xxx0xxx0B      |

| B*                  | B register                                                      | F0H               | F7      | F6        | F5        | F4                | F3        | F2        | F1                   | F0        | 00H            |

| CCAP0H#             | Module 0 Capture High                                           | FAH               |         |           |           |                   |           |           |                      |           | xxxxxxxxB      |

| CCAP1H#             | Module 1 Capture High                                           | FBH               |         |           |           |                   |           |           |                      |           | xxxxxxxxB      |

| CCAP2H#             | Module 2 Capture High                                           | FCH               |         |           |           |                   |           |           |                      |           | xxxxxxxxB      |

| CCAP3H#             | Module 3 Capture High                                           | FDH               |         |           |           |                   |           |           |                      |           | xxxxxxxxB      |

| CCAP4H#             | Module 4 Capture High                                           | FEH               |         |           |           |                   |           |           |                      |           | xxxxxxxxB      |

| CCAP0L#             | Module 0 Capture Low                                            | EAH               |         |           |           |                   |           |           |                      |           | xxxxxxxxB      |

| CCAP1L#             | Module 1 Capture Low                                            | EBH               |         |           |           |                   |           |           |                      |           | xxxxxxxxB      |

| CCAP2L#             | Module 2 Capture Low                                            | ECH               |         |           |           |                   |           |           |                      |           | xxxxxxxxB      |

| CCAP3L#             | Module 3 Capture Low                                            | EDH               |         |           |           |                   |           |           |                      |           | xxxxxxxxB      |

| CCAP4L#             | Module 4 Capture Low                                            | EEH               |         |           |           |                   |           |           |                      |           | xxxxxxxxB      |

| CCAPM0#             | Module 0 Mode                                                   | DAH               | _       | ECOM      | CAPP      | CAPN              | MAT       | TOG       | PWM                  | ECCF      | x0000000B      |

| CCAPM1#             | Module 1 Mode                                                   | DBH               | -       | ECOM      | CAPP      | CAPN              | MAT       | TOG       | PWM                  | ECCF      | x0000000B      |

| CCAPM2#             | Module 2 Mode                                                   | DCH               | _       | ECOM      | CAPP      | CAPN              | MAT       | TOG       | PWM                  | ECCF      | x0000000B      |

| CCAPM3#             | Module 3 Mode                                                   | DDH               | -       | ECOM      | CAPP      | CAPN              | MAT       | TOG       | PWM                  | ECCF      | x0000000B      |

| CCAPM4#             | Module 4 Mode                                                   | DEH               | -       | ECOM      | CAPP      | CAPN              | MAT       | TOG       | PWM                  | ECCF      | x0000000B      |

|                     |                                                                 |                   | DF      | DE        | DD        | DC                | DB        | DA        | D9                   | D8        |                |

| CCON*#              | PCA Counter Control                                             | D8H               | CF      | CR        | _         | CCF4              | CCF3      | CCF2      | CCF1                 | CCF0      | 00x00000B      |

| CH#                 | PCA Counter High                                                | F9H               |         |           |           |                   |           |           |                      |           | 00H            |

| CL#                 | PCA Counter Low                                                 | E9H               |         |           |           |                   |           |           |                      |           | 00H            |

| CMOD#               | PCA Counter Mode                                                | D9H               | CIDL    | WDTE      | _         | _                 | _         | CPS1      | CPS0                 | ECF       | 00xxx000B      |

| DPTR:<br>DPH<br>DPL | Data Pointer (2 bytes)<br>Data Pointer High<br>Data Pointer Low | 83H<br>82H        | AF      | AE        | AD        | AC                | AB        | AA        | A9                   | A8        | 00H<br>00H     |

| IE*                 | Interrupt Fachle                                                | A8H               | EA      | EC        | ET2       | ES                | ET1       | EX1       | ET0                  | EX0       | 00H            |

| IE                  | Interrupt Enable                                                | АОП               | BF      |           |           | I                 |           | <u> </u>  |                      |           | 000            |

| IP*                 | latamunt Driavitu                                               | DOLL              |         | BE        | BD        | BC                | BB        | BA        | B9                   | B8        | 00000000       |

| IP                  | Interrupt Priority                                              | B8H               | –<br>В7 | PPC<br>B6 | PT2<br>B5 | PS<br>B4          | PT1<br>B3 | PX1<br>B2 | PT0<br>B1            | PX0<br>B0 | x0000000B      |

| IPH#                | Interrupt Priority High                                         | B7H               |         | PPCH      | PT2H      | PSH               | PT1H      | PX1H      | PT0H                 | PX0H      | x0000000B      |

| IFN#                | interrupt Phonty High                                           | В/П               | _       | РРСП      | РІДП      | РЭП               | FIII      | PAIN      | FIUH                 | РЛОП      | XUUUUUUUD      |

|                     |                                                                 |                   | 87      | 86        | 85        | 84                | 83        | 82        | 81                   | 80        |                |

| P0*                 | Port 0                                                          | 80H               | AD7     | AD6       | AD5       | AD4               | AD3       | AD2       | AD1                  | AD0       | FFH            |

|                     |                                                                 |                   | 97      | 96        | 95        | 94                | 93        | 92        | 91                   | 90        | 1              |

| P1*                 | Port 1                                                          | 90H               | CEX4    | CEX3      | CEX2      | CEX1              | CEX0      | ECI       | T2EX                 | T2        | FFH            |

|                     |                                                                 |                   | A7      | A6        | A5        | A4                | А3        | A2        | A1                   | A0        |                |

| P2*                 | Port 2                                                          | A0H               | AD15    | AD14      | AD13      | AD12              | AD11      | AD10      | AD9                  | AD8       | FFH            |

|                     |                                                                 |                   | B7      | B6        | B5        | B4                | В3        | B2        | B1                   | B0        |                |

| P3*                 | Port 3                                                          | вон               | RD      | WR        | T1        | T0                | INT1      | ĪNT0      | TxD                  | RxD       | FFH            |

| PCON# <sup>1</sup>  | Power Control                                                   | 87H               | SMOD1   | SMOD0     | _         | POF <sup>2</sup>  | GF1       | GF0       | PD                   | IDL       | 00xx0000B      |

|                     |                                                                 | -                 |         |           |           | -                 | -         |           |                      |           |                |

<sup>\*</sup> SFRs are bit addressable.

<sup>#</sup> SFRs are modified from or added to the 80C51 SFRs.

<sup>-</sup> Reserved bits.

<sup>1.</sup> Reset value depends on reset source.

Bit will not be affected by Reset.

<sup>3.</sup> LPEP – Low Power OTP–EPROM only operation.

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33MHz)

8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

**Table 4. Timer 2 Operating Modes**

| RCLK + TCLK | CP/RL2 | TR2 | MODE                |

|-------------|--------|-----|---------------------|

| 0           | 0      | 1   | 16-bit Auto-reload  |

| 0           | 1      | 1   | 16-bit Capture      |

| 1           | X      | 1   | Baud rate generator |

| Х           | Х      | 0   | (off)               |

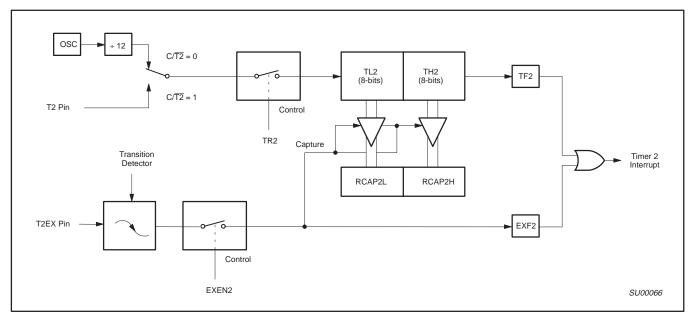

Figure 2. Timer 2 in Capture Mode

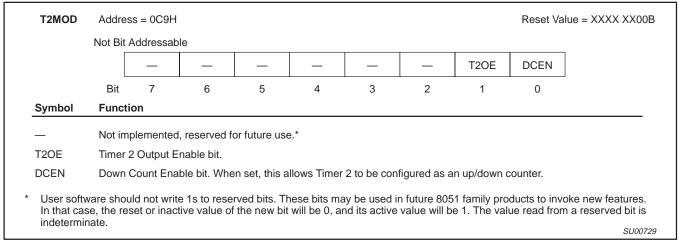

Figure 3. Timer 2 Mode (T2MOD) Control Register

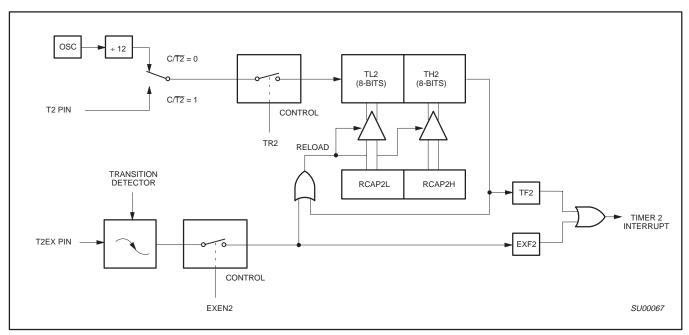

Figure 4. Timer 2 in Auto-Reload Mode (DCEN = 0)

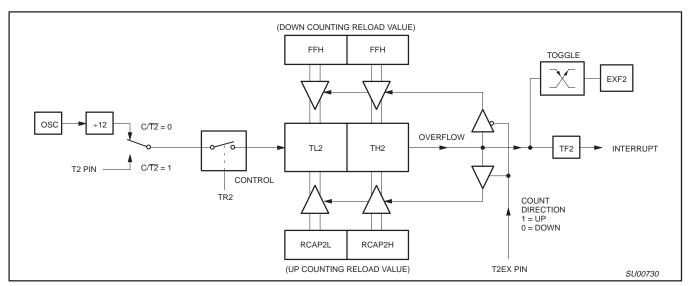

Figure 5. Timer 2 Auto Reload Mode (DCEN = 1)

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33MHz) 8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

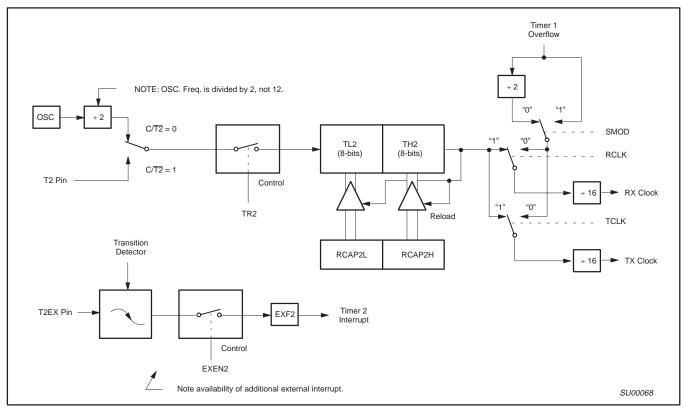

Figure 6. Timer 2 in Baud Rate Generator Mode

Table 5. Timer 2 Generated Commonly Used Baud Rates

| Baud Rate | Oce From | Timer 2 |        |  |  |  |  |  |  |  |

|-----------|----------|---------|--------|--|--|--|--|--|--|--|

| Baud Rate | Osc Freq | RCAP2H  | RCAP2L |  |  |  |  |  |  |  |

| 375K      | 12MHz    | FF      | FF     |  |  |  |  |  |  |  |

| 9.6K      | 12MHz    | FF      | D9     |  |  |  |  |  |  |  |

| 2.8K      | 12MHz    | FF      | B2     |  |  |  |  |  |  |  |

| 2.4K      | 12MHz    | FF      | 64     |  |  |  |  |  |  |  |

| 1.2K      | 12MHz    | FE      | C8     |  |  |  |  |  |  |  |

| 300       | 12MHz    | FB      | 1E     |  |  |  |  |  |  |  |

| 110       | 12MHz    | F2      | AF     |  |  |  |  |  |  |  |

| 300       | 6MHz     | FD      | 8F     |  |  |  |  |  |  |  |

| 110       | 6MHz     | F9      | 57     |  |  |  |  |  |  |  |

#### **Baud Rate Generator Mode**

Bits TCLK and/or RCLK in T2CON (Table 5) allow the serial port transmit and receive baud rates to be derived from either Timer 1 or Timer 2. When TCLK= 0, Timer 1 is used as the serial port transmit baud rate generator. When TCLK= 1, Timer 2 is used as the serial port transmit baud rate generator. RCLK has the same effect for the serial port receive baud rate. With these two bits, the serial port can have different receive and transmit baud rates – one generated by Timer 1, the other by Timer 2.

Figure 6 shows the Timer 2 in baud rate generation mode. The baud rate generation mode is like the auto-reload mode,in that a rollover in TH2 causes the Timer 2 registers to be reloaded with the 16-bit value in registers RCAP2H and RCAP2L, which are preset by software.

The baud rates in modes 1 and 3 are determined by Timer 2's overflow rate given below:

Modes 1 and 3 Baud Rates =

$$\frac{\text{Timer 2 Overflow Rate}}{16}$$

The timer can be configured for either "timer" or "counter" operation. In many applications, it is configured for "timer" operation ( $C/\overline{T}2^*=0$ ). Timer operation is different for Timer 2 when it is being used as a baud rate generator.

Usually, as a timer it would increment every machine cycle (i.e., 1/12 the oscillator frequency). As a baud rate generator, it increments every state time (i.e., 1/2 the oscillator frequency). Thus the baud rate formula is as follows:

Modes 1 and 3 Baud Rates =

$$\frac{\text{Oscillator Frequency}}{[32 \times [65536 - (\text{RCAP2H}, \text{RCAP2L})]]}$$

Where: (RCAP2H, RCAP2L)= The content of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

The Timer 2 as a baud rate generator mode shown in Figure 6, is valid only if RCLK and/or TCLK = 1 in T2CON register. Note that a rollover in TH2 does not set TF2, and will not generate an interrupt. Thus, the Timer 2 interrupt does not have to be disabled when Timer 2 is in the baud rate generator mode. Also if the EXEN2 (T2 external enable flag) is set, a 1-to-0 transition in T2EX (Timer/counter 2 trigger input) will set EXF2 (T2 external flag) but will not cause a reload from (RCAP2H, RCAP2L) to (TH2,TL2). Therefore when Timer 2 is in use as a baud rate generator, T2EX can be used as an additional external interrupt, if needed.

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33MHz)

8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

|        | SC                | ON Addr                     | ess = 98H             |                    |                            |                                  |               |              | ļ           | Reset Value = 0000 0000B                                   |

|--------|-------------------|-----------------------------|-----------------------|--------------------|----------------------------|----------------------------------|---------------|--------------|-------------|------------------------------------------------------------|

|        | Bit Addressable   |                             |                       |                    |                            |                                  |               |              | T           |                                                            |

|        |                   | SM0/FE                      | SM1                   | SM2                | REN                        | TB8                              | RB8           | TI           | RI          |                                                            |

|        | Bit:              | 7                           | 6                     | 5                  | 4                          | 3                                | 2             | 1            | 0           |                                                            |

|        | (8                | SMOD0 = 0                   | /1)*                  |                    |                            |                                  |               |              |             |                                                            |

| Symbol | Funct             | on                          |                       |                    |                            |                                  |               |              |             |                                                            |

| FE     |                   |                             |                       |                    |                            | hen an inva                      |               |              |             | t is not cleared by valid<br>e FE bit.                     |

| SM0    | Serial            | Port Mode                   | Bit 0, (SMC           | DD0 must :         | = 0 to acce                | ss bit SM0)                      |               |              |             |                                                            |

| SM1    | Serial            | Port Mode                   | Bit 1                 |                    |                            |                                  |               |              |             |                                                            |

|        | SM0               | SM1                         | Mode                  | Descr              | iption                     | Baud Rate                        | **            |              |             |                                                            |

|        | 0                 | 0                           | 0                     | shift re           | 0                          | f <sub>OSC</sub> /12             |               |              |             |                                                            |

|        | 0                 | 1<br>0                      | 1<br>2                | 8-bit U<br>9-bit U |                            | variable f <sub>OSC</sub> /64 or | food/32       |              |             |                                                            |

|        | 1                 | 1                           | 3                     | 9-bit U            |                            | variable                         | 1050/32       |              |             |                                                            |

| SM2    | receive<br>In Mod | ed 9th data<br>le 1, if SM2 | bit (RB8) i           | s 1, indicat       | ting an add<br>e activated | ress, and th<br>I unless a va    | e received l  | byte is a G  | iven or Bro | ot be set unless the padcast Address. e received byte is a |

| REN    | Enable            | es serial red               | ception. Se           | t by softwa        | are to enab                | le reception                     | . Clear by so | oftware to   | disable red | eption.                                                    |

| ГВ8    | The 9t            | h data bit th               | hat will be t         | ransmitted         | I in Modes                 | 2 and 3. Se                      | t or clear by | software a   | as desired. |                                                            |

| RB8    |                   |                             | the 9th das not used. |                    | was receiv                 | ed. In Mode                      | e 1, if SM2 = | 0, RB8 is    | the stop bi | t that was received.                                       |

| П      |                   |                             |                       |                    |                            | d of the 8th<br>cleared by s     |               | 1ode 0, or a | at the begi | nning of the stop bit in the                               |

|        |                   |                             |                       |                    |                            | d of the 8th bee SM2). M         |               |              |             | ough the stop bit time in                                  |

| RI     | the oth           | ici illoucs,                | , ,                   |                    | (                          | ,                                |               | ,            |             |                                                            |

Figure 7. SCON: Serial Port Control Register

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33MHz)

8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

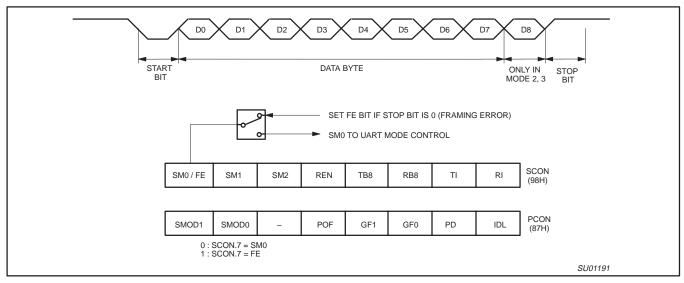

Figure 8. UART Framing Error Detection

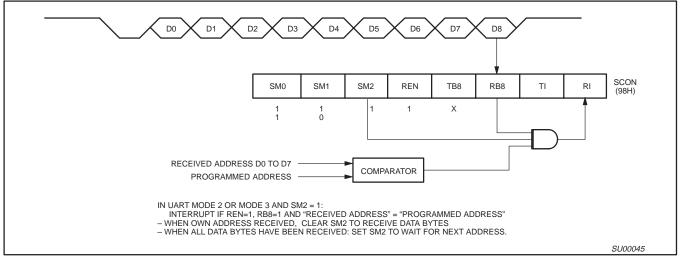

Figure 9. UART Multiprocessor Communication, Automatic Address Recognition

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33MHz)

8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

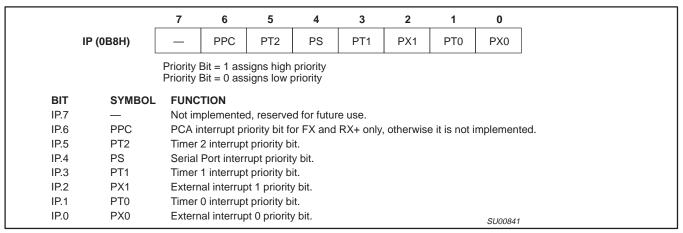

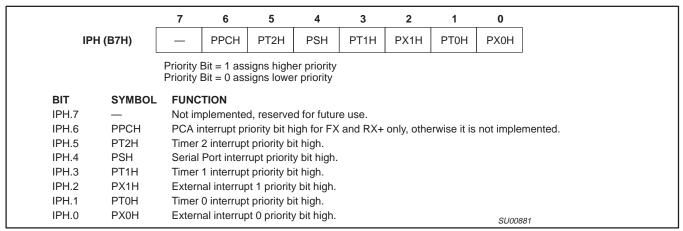

Figure 11. IP Registers

Figure 12. IPH Registers

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33MHz)

8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

## (8XC51FX and 8XC51RX+ ONLY)

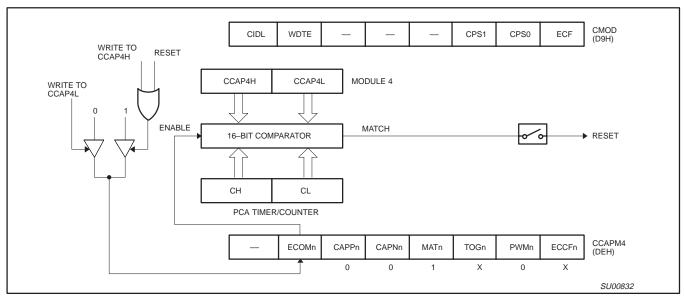

Figure 25. PCA Watchdog Timer m(Module 4 only)

#### **PCA Watchdog Timer**

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed.

Figure 25 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- periodically change the compare value so it will never match the PCA timer

- 2. periodically change the PCA timer value so it will never match the compare values, or

- disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for **all** modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

Figure 26 shows the code for initializing the watchdog timer. Module 4 can be configured in either compare mode, and the WDTE bit in CMOD must also be set. The user's software then must periodically change (CCAP4H,CCAP4L) to keep a match from occurring with the PCA timer (CH,CL). This code is given in the WATCHDOG routine in Figure 26.

This routine should not be part of an interrupt service routine, because if the program counter goes astray and gets stuck in an infinite loop, interrupts will still be serviced and the watchdog will keep getting reset. Thus, the purpose of the watchdog would be defeated. Instead, call this subroutine from the main program within  $2^{16}$  count of the PCA timer.

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33MHz)

8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

## (8XC51FX and 8XC51RX+ ONLY)

```

INIT_WATCHDOG:

MOV CCAPM4, #4CH ; Module 4 in compare mode

MOV CCAP4L, #0FFH ; Write to low byte first

MOV CCAP4H, #0FFH

; Before PCA timer counts up to

; FFFF Hex, these compare values

; must be changed

ORL CMOD, #40H

; Set the WDTE bit to enable the

; watchdog timer without changing

; the other bits in CMOD

; Main program goes here, but CALL WATCHDOG periodically.

; ***********************

WATCHDOG:

CLR EA ; Hold off interrupts

MOV CCAP4L, #00 ; Next compare value is within

MOV CCAP4H, CH

; 255 counts of the current PCA

SETB EA

; timer value

RET

```

Figure 26. PCA Watchdog Timer Initialization Code

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33MHz)

8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

## (8XC51RX+ ONLY)

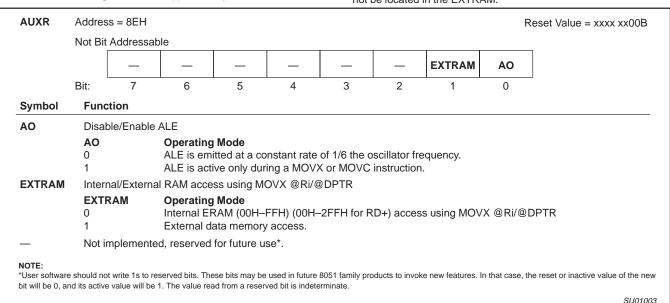

# Expanded Data RAM Addressing (8XC51RX+ ONLY)

The 8XC51RX+ have internal data memory that is mapped into four separate segments: the lower 128 bytes of RAM, upper 128 bytes of RAM, 128 bytes Special Function Register (SFR), and 256 bytes (768 for RD+) expanded RAM (EXTRAM).

The four segments are:

- The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only.

- The 256-bytes (768 for RD+) expanded RAM ((EXTRAM (256-bytes) 00H–FFH)) and ((EXTRAM (768-bytes for RD+) 00H – 2FFH)) are indirectly accessed by move external instruction, MOVX, and with the EXTRAM bit cleared, see Figure 27.

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction. Instructions that use direct addressing access SFR space. For example:

#### MOV 0A0H,#data

accesses the SFR at location 0A0H (which is P2). Instructions that use indirect addressing access the Upper 128 bytes of data RAM.

## For example:

MOV @R0,#data

where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

The EXTRAM can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory is physically located on-chip, logically occupies the first 256-bytes (768 for RD+) of external data memory.

With EXTRAM = 0, the EXTRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to EXTRAM will not affect ports P0, P3.6 (WR#) and P3.7 (RD#). P2 SFR is output during external addressing. For example, with EXTRAM = 0,

#### MOVX @R0,#data

where R0 contains 0A0H, access the EXTRAM at address 0A0H rather than external memory. An access to external data memory locations higher than FFH (2FF for RD+) (i.e., 0100H to FFFFH) will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, so with P0 and P2 as data/address bus, and P3.6 and P3.7 as write and read timing signals. Refer to Figure 28.

With EXTRAM = 1, MOVX @Ri and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an 8-bit address multiplexed with data on Port 0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a 16-bit address. Port 2 outputs the high-order eight address bits (the contents of DPH) while Port 0 multiplexes the low-order eight address bits (DPL) with data. MOVX @Ri and MOVX @DPTR will generate either read or write signals on P3.6 (#WR) and P3.7 (#RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the EXTRAM.

Figure 27. AUXR: Auxiliary Register (RX+ only)

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33MHz) 8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

## **ABSOLUTE MAXIMUM RATINGS**1, 2, 3

| PARAMETER                                                                                    | RATING                 | UNIT |

|----------------------------------------------------------------------------------------------|------------------------|------|

| Operating temperature under bias                                                             | 0 to +70 or -40 to +85 | °C   |

| Storage temperature range                                                                    | -65 to +150            | °C   |

| Voltage on EA/V <sub>PP</sub> pin to V <sub>SS</sub>                                         | 0 to +13.0             | V    |

| Voltage on any other pin to V <sub>SS</sub>                                                  | -0.5 to +6.5           | V    |

| Maximum I <sub>OL</sub> per I/O pin                                                          | 15                     | mA   |

| Power dissipation (based on package heat transfer limitations, not device power consumption) | 1.5                    | W    |

#### NOTES:

- 1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

- This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise

- Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

## **AC ELECTRICAL CHARACTERISTICS**

$T_{amb} = 0$ °C to +70°C or -40°C to +85°C

|                     |        |                                                                        | CLOCK FR<br>RANG |     |            |

|---------------------|--------|------------------------------------------------------------------------|------------------|-----|------------|

| SYMBOL              | FIGURE | PARAMETER                                                              | MIN              | MAX | UNIT       |

| 1/t <sub>CLCL</sub> | 33     | Oscillator frequency<br>Speed versions: 4:5:S (16MHz)<br>I:J:U (33MHz) | 0                |     | MHz<br>MHz |

80C51 8-bit microcontroller family 8K-64K/256-1K OTP/ROM/ROMless, low voltage (2.7V-5.5V), low power, high speed (33MHz)

8XC54/58 8XC51FA/FB/FC/80C51FA 8XC51RA+/RB+/RC+/RD+/80C51RA+

## **AC ELECTRICAL CHARACTERISTICS**

$v_{ab} = 0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  or  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $V_{CC} = +2.7\text{V}$  to +5.5V.  $V_{SS} = 0\text{V}^{1, 2, 3}$

|                     |        |                                                          | 16MHz    | CLOCK | VARIABL                  | E CLOCK                              |      |

|---------------------|--------|----------------------------------------------------------|----------|-------|--------------------------|--------------------------------------|------|

| SYMBOL              | FIGURE | PARAMETER                                                | MIN      | MAX   | MIN                      | MAX                                  | UNIT |

| 1/t <sub>CLCL</sub> | 29     | Oscillator frequency <sup>5</sup> Speed versions: 4; 5;S |          |       | 3.5                      | 16                                   | MHz  |

| t <sub>LHLL</sub>   | 29     | ALE pulse width                                          | 85       |       | 2t <sub>CLCL</sub> -40   |                                      | ns   |

| t <sub>AVLL</sub>   | 29     | Address valid to ALE low                                 | 22       |       | t <sub>CLCL</sub> -40    |                                      | ns   |

| t <sub>LLAX</sub>   | 29     | Address hold after ALE low                               | 32       |       | t <sub>CLCL</sub> -30    |                                      | ns   |

| t <sub>LLIV</sub>   | 29     | ALE low to valid instruction in                          |          | 150   |                          | 4t <sub>CLCL</sub> -100              | ns   |

| t <sub>LLPL</sub>   | 29     | ALE low to PSEN low                                      | 32       |       | t <sub>CLCL</sub> -30    |                                      | ns   |

| t <sub>PLPH</sub>   | 29     | PSEN pulse width                                         | 142      |       | 3t <sub>CLCL</sub> -45   |                                      | ns   |

| t <sub>PLIV</sub>   | 29     | PSEN low to valid instruction in                         |          | 82    |                          | 3t <sub>CLCL</sub> -105              | ns   |

| t <sub>PXIX</sub>   | 29     | Input instruction hold after PSEN                        | 0        |       | 0                        |                                      | ns   |

| t <sub>PXIZ</sub>   | 29     | Input instruction float after PSEN                       |          | 37    |                          | t <sub>CLCL</sub> -25                | ns   |

| t <sub>AVIV</sub> 5 | 29     | Address to valid instruction in                          |          | 207   |                          | 5t <sub>CLCL</sub> -105              | ns   |

| t <sub>PLAZ</sub>   | 29     | PSEN low to address float                                |          | 10    |                          | 10                                   | ns   |

| Data Memo           | ry     |                                                          | <u> </u> |       |                          | •                                    | •    |

| t <sub>RLRH</sub>   | 30, 31 | RD pulse width                                           | 275      |       | 6t <sub>CLCL</sub> -100  |                                      | ns   |

| t <sub>WLWH</sub>   | 30, 31 | WR pulse width                                           | 275      |       | 6t <sub>CLCL</sub> -100  |                                      | ns   |

| t <sub>RLDV</sub>   | 30, 31 | RD low to valid data in                                  |          | 147   |                          | 5t <sub>CLCL</sub> -165              | ns   |

| t <sub>RHDX</sub>   | 30, 31 | Data hold after RD                                       | 0        |       | 0                        |                                      | ns   |

| t <sub>RHDZ</sub>   | 30, 31 | Data float after RD                                      |          | 65    |                          | 2t <sub>CLCL</sub> -60               | ns   |

| t <sub>LLDV</sub>   | 30, 31 | ALE low to valid data in                                 |          | 350   |                          | 8t <sub>CLCL</sub> -150              | ns   |

| t <sub>AVDV</sub>   | 30, 31 | Address to valid data in                                 |          | 397   |                          | 9t <sub>CLCL</sub> -165              | ns   |

| t <sub>LLWL</sub>   | 30, 31 | ALE low to RD or WR low                                  | 137      | 239   | 3t <sub>CLCL</sub> -50   | 3t <sub>CLCL</sub> +50               | ns   |