Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                       |

|----------------------------|----------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                              |

| Core Size                  | 32-Bit Single-Core                                                                           |

| Speed                      | 100MHz                                                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                                           |

| Program Memory Size        | 1MB (1M x 8)                                                                                 |

| Program Memory Type        | FLASH                                                                                        |

| EEPROM Size                |                                                                                              |

| RAM Size                   | 256K x 8                                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                  |

| Data Converters            | A/D 10x12b                                                                                   |

| Oscillator Type            | Internal                                                                                     |

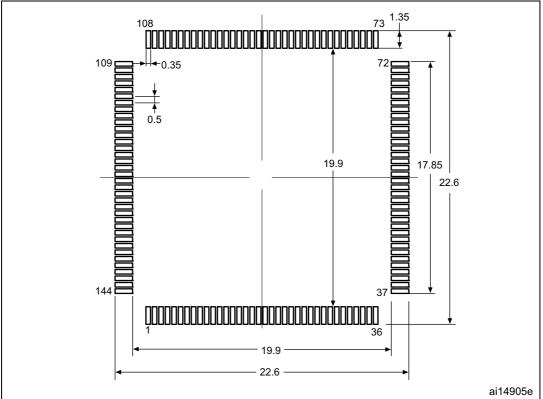

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                            |

| Mounting Type              | Surface Mount                                                                                |

| Package / Case             | 48-UFQFN Exposed Pad                                                                         |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f412cgu6tr                      |

|                            |                                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

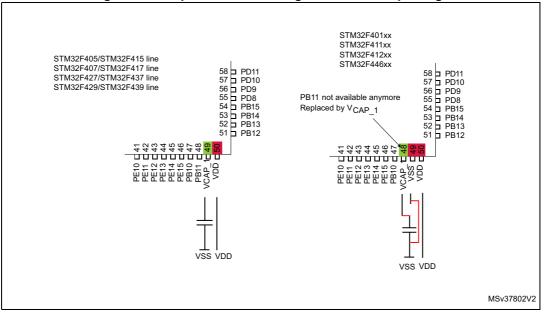

### 2.1 Compatibility with STM32F4 series

The STM32F412xE/G are fully software and feature compatible with the STM32F4 series (STM32F42x, STM32F401, STM32F43x, STM32F41x, STM32F405 and STM32F407)

The STM32F412xE/G can be used as drop-in replacement of the other STM32F4 products but some slight changes have to be done on the PCB board.

#### Figure 1. Compatible board design for LQFP100 package

### 3.16 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash memory

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using one of the interface listed in the *Table 3* or the USB OTG FS in device mode through DFU (device firmware upgrade).

| Package  | USART1<br>PA9/<br>PA10 | USART2<br>PD6/<br>PD5 | USART3<br>PB11/<br>PB10 | I2C1<br>PB6/<br>PB7 | I2C2<br>PF0/<br>PF1 | 12C3<br>PA8/<br>PB4 | I2C<br>FMP1<br>PB14/<br>PB15 | SPI1<br>PA4/<br>PA5/<br>PA6/<br>PA7 | SPI3<br>PA15/<br>PC10/<br>PC11/<br>PC12 | SPI4<br>PE11/<br>PE12/<br>PE13/<br>PE14 | CAN2<br>PB5/<br>PB13 | USB<br>PA11<br>/P12 |

|----------|------------------------|-----------------------|-------------------------|---------------------|---------------------|---------------------|------------------------------|-------------------------------------|-----------------------------------------|-----------------------------------------|----------------------|---------------------|

| UFQFPN48 | Y                      | -                     | -                       | Y                   | -                   | Y                   | Y                            | Y                                   | -                                       | -                                       | Y                    | Y                   |

| WLCSP64  | Y                      | -                     | -                       | Y                   | -                   | Y                   | Y                            | Y                                   | Y                                       | -                                       | Y                    | Y                   |

| LQFP64   | Y                      | -                     | -                       | Y                   | -                   | Y                   | Y                            | Y                                   | Y                                       | -                                       | Y                    | Y                   |

| LQFP100  | Y                      | Y                     | -                       | Y                   | -                   | Y                   | Y                            | Y                                   | Y                                       | Y                                       | Y                    | Y                   |

| LQFP144  | Y                      | Y                     | Y                       | Y                   | Y                   | Y                   | Y                            | Y                                   | Y                                       | Y                                       | Y                    | Y                   |

| UFBGA100 | Y                      | Y                     | Y                       | Y                   | -                   | Y                   | Y                            | Y                                   | Y                                       | Y                                       | Y                    | Y                   |

| UFBGA144 | Y                      | Y                     | Y                       | Y                   | Y                   | Y                   | Y                            | Y                                   | Y                                       | Y                                       | Y                    | Y                   |

Table 3. Embedded bootloader interfaces

For more detailed information on the bootloader, refer to Application Note: AN2606, *STM32™ microcontroller system memory boot mode*.

### 3.17 **Power supply schemes**

- V<sub>DD</sub> = 1.7 to 3.6 V: external power supply for I/Os with the internal supervisor (POR/PDR) disabled, provided externally through V<sub>DD</sub> pins. Requires the use of an external power supply supervisor connected to the V<sub>DD</sub> and NRST pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively, with decoupling technique.

Note:

The V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 3.18.2: Internal reset OFF). Refer to Table 4: Regulator ON/OFF and internal power supply supervisor availability to identify the packages supporting this option.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

- V<sub>DDUSB</sub> can be connected either to VDD or an external independent power supply (3.0 to 3.6 V) for USB transceivers.

For example, when device is powered at 1.8 V, an independent power supply 3.3V can

For example, when device is powered at 1.8 V, an independent power supply 3.3V can be connected to  $V_{DDUSB}$ . When the  $V_{DDUSB}$  is connected to a separated power supply,

Additional 32-bit registers contain the programmable alarm subseconds, seconds, minutes, hours, day, and date.

The RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or from the  $V_{BAT}$  pin.

### 3.21 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

To further reduce the power consumption, the Flash memory can be switched off before entering in Sleep mode. Note that this requires a code execution from the RAM.

### • Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm/ wakeup/ tamper/ time stamp events).

### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on one of the WKUP pins, or an RTC alarm/ wakeup/ tamper/time stamp event occurs.

Standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

### 3.22 V<sub>BAT</sub> operation

The VBAT pin allows to power the device  $V_{BAT}$  domain from an external battery, an external super-capacitor, or from  $V_{DD}$  when no external battery and an external super-capacitor are present.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The VBAT pin supplies the RTC and the backup registers.

Note: When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation. When PDR\_ON pin is not connected to  $V_{DD}$  (internal Reset OFF), the  $V_{BAT}$  functionality is no more available and VBAT pin should be connected to  $V_{DD}$ .

### 3.23.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1/8) can be seen as three-phase PWM generator multiplexed on 4 independent channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as a 16-bit PWM generator, they have full modulation capability (0-100%).

The advanced-control timers can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 and TIM8 support independent DMA request generation.

### 3.23.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F412xE/G (see *Table 5* for differences).

#### • TIM2, TIM3, TIM4, TIM5

The STM32F412xE/G devices include 4 full-featured general-purpose timers: TIM2. TIM3, TIM4 and TIM5. TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler while TIM3 and TIM4 timers are based on a 16bit auto-reload up/downcounter plus a 16-bit prescaler. They all features four independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 15 input capture/output compare/PWMs

TIM2. TIM3, TIM4 and TIM5 general-purpose timers can operate together or in conjunction with the other general-purpose timers and TIM1 advanced-control timer via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM output.

TIM2. TIM3, TIM4 and TIM5 channels have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

### • TIM9, TIM10, TIM11, TIM12, TIM13 and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13 and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or onepulse mode output. They can be synchronized with TIM2. TIM3, TIM4 and TIM5 fullfeatured general-purpose timers or used as simple time bases.

### 3.23.3 Basic timer (TIM6, TIM7)

TIM6 and TIM7 timers are basic 16-bit timers. They support independent DMA request generation.

DocID028087 Rev 4

|   |                    |      | <u> </u> |     |                |      |        | -    |        |      |        |        |

|---|--------------------|------|----------|-----|----------------|------|--------|------|--------|------|--------|--------|

|   | 1                  | 2    | 3        | 4   | 5              | 6    | 7      | 8    | 9      | 10   | 11     | 12     |

| Α | PC13               | PE3  | PE2      | PE1 | PE0            | PB4  | PB3    | PD6  | PD7    | PA15 | PA14   | PA13   |

| в | PC14-<br>OSC32_IN  | PE4  | PE5      | PE6 | PB9            | PB5  | PG15   | PG12 | PD5    | PC11 | PC10   | PA12   |

| с | PC15-<br>OSC32_OUT | VBAT | PF0      | PF1 | PB8            | PB6  | PG14   | PG11 | PD4    | PC12 | VDDUSB | PA11   |

| D | PH0 -<br>OSC_IN    | vss  | VDD      | PF2 | BOOTO          | PB7  | PG13   | PG10 | PD3    | PD1  | PA10   | PA9    |

| E | PH1 -<br>OSC_OUT   | PF3  | PF4      | PF5 | PDR_ON         | VSS  | vss    | PG9  | PD2    | PD0  | PC9    | PA8    |

| F | NRST               | PF7  | PF6      | VDD | VDD            | VDD  | VDD    | VDD  | VDD    | VDD  | PC8    | PC7    |

| G | PF10               | PF9  | PF8      | vss | VDD            | VDD  | VDD    | vss  | VCAP_2 | vss  | PG8    | PC6    |

| н | PC0                | PC1  | PC2      | PC3 | BYPASS_<br>REG | VSS  | VCAP_1 | PE11 | PD11   | PG7  | PG6    | PG5    |

| J | VSSA               | PA0  | PA4      | PC4 | PB2            | PG1  | PE10   | PE12 | PD10   | PG4  | PG3    | PG2    |

| к | VREF-              | PA1  | PA5      | PC5 | PF13           | PG0  | PE9    | PE13 | PD9    | PD13 | PD14   | PD15   |

| L | VREF+              | PA2  | PA6      | PB0 | PF12           | PF15 | PE8    | PE14 | PD8    | PD12 | PB14   | PB15   |

| м | VDDA               | PA3  | PA7      | PB1 | PF11           | PF14 | PE7    | PE15 | PB10   | PB11 | PB12   | PB13   |

|   | ·                  |      |          |     |                |      |        |      |        |      | •      | MSv372 |

### Figure 17. STM32F412xE/G UFBGA144 pinout

1. The above figure shows the package top view.

### Table 8. Legend/abbreviations used in the pinout table

| Name                    | Abbreviation       | Definition                                                                                         |

|-------------------------|--------------------|----------------------------------------------------------------------------------------------------|

| Pin name                |                    | specified in brackets below the pin name, the pin function during and after as the actual pin name |

|                         | S                  | Supply pin                                                                                         |

| Pin type                | I                  | Input only pin                                                                                     |

|                         | I/O                | Input/ output pin                                                                                  |

|                         | FT                 | 5 V tolerant I/O                                                                                   |

| I/O structure           | TC                 | Standard 3.3 V I/O                                                                                 |

|                         | В                  | Dedicated BOOT0 pin                                                                                |

|                         | NRST               | Bidirectional reset pin with embedded weak pull-up resistor                                        |

| Notes                   | Unless otherwise   | specified by a note, all I/Os are set as floating inputs during and after reset                    |

| Alternate<br>functions  | Functions selected | d through GPIOx_AFR registers                                                                      |

| Additional<br>functions | Functions directly | selected/enabled through peripheral registers                                                      |

Г

|          |        | Pi      | n Nui   | mber     |          |         |                                                         |             |                  |       |                                                                                       |                         |

|----------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|-------------|------------------|-------|---------------------------------------------------------------------------------------|-------------------------|

| UFQFPN48 | LQFP64 | WLCSP64 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin<br>type | I/O<br>structure | Notes | Alternate functions                                                                   | Additional<br>functions |

| -        | -      | -       | -       | -        | M6       | 54      | PF14                                                    | I/O         | FT               | -     | I2CFMP1_SCL,<br>FSMC_A8, EVENTOUT                                                     | -                       |

| -        | -      | -       | -       | -        | L6       | 55      | PF15                                                    | I/O         | FT               | -     | I2CFMP1_SDA,<br>FSMC_A9, EVENTOUT                                                     | -                       |

| -        | -      | -       | -       | -        | K6       | 56      | PG0                                                     | I/O         | FT               | -     | CAN1_RX, FSMC_A10,<br>EVENTOUT                                                        | -                       |

| -        | -      | -       | -       | -        | J6       | 57      | PG1                                                     | I/O         | FT               | -     | CAN1_TX, FSMC_A11,<br>EVENTOUT                                                        | -                       |

| -        | -      | -       | 38      | M7       | M7       | 58      | PE7                                                     | I/O         | FT               | -     | TIM1_ETR,<br>DFSDM1_DATIN2,<br>QUADSPI_BK2_IO0,<br>FSMC_D4/FSMC_DA4,<br>EVENTOUT      | -                       |

| -        | -      | -       | 39      | L7       | L7       | 59      | PE8                                                     | I/O         | FT               | -     | TIM1_CH1N,<br>DFSDM1_CKIN2,<br>QUADSPI_BK2_IO1,<br>FSMC_D5/FSMC_DA5,<br>EVENTOUT      | -                       |

| -        | -      | -       | 40      | M8       | K7       | 60      | PE9                                                     | I/O         | FT               | -     | TIM1_CH1,<br>DFSDM1_CKOUT,<br>QUADSPI_BK2_IO2,<br>FSMC_D6/FSMC_DA6,<br>EVENTOUT       | -                       |

| -        | -      | -       | -       | -        | -        | 61      | VSS                                                     | S           | -                | -     | -                                                                                     | -                       |

| -        | -      | -       | -       | -        | G6       | 62      | VDD                                                     | S           | -                | -     | -                                                                                     | -                       |

| -        | -      | -       | 41      | L8       | J7       | 63      | PE10                                                    | I/O         | FT               | -     | TIM1_CH2N,<br>QUADSPI_BK2_IO3,<br>FSMC_D7/FSMC_DA7,<br>EVENTOUT                       | -                       |

| -        | -      | -       | 42      | M9       | H8       | 64      | PE11                                                    | I/O         | FT               | -     | TIM1_CH2,<br>SPI4_NSS/I2S4_WS,<br>SPI5_NSS/I2S5_WS,<br>FSMC_D8/FSMC_DA8,<br>EVENTOUT  | -                       |

| -        | -      | -       | 43      | L9       | J8       | 65      | PE12                                                    | I/O         | FT               | -     | TIM1_CH3N,<br>SPI4_SCK/I2S4_CK,<br>SPI5_SCK/I2S5_CK,<br>FSMC_D9/FSMC_DA9,<br>EVENTOUT | -                       |

Table 9. STM32F412xE/G pin definition (continued)

|          |        | Pir     | n Nu    | mber     |          |         |                                                         |             |                  |       |                                                                                                      |                         |

|----------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|-------------|------------------|-------|------------------------------------------------------------------------------------------------------|-------------------------|

| UFQFPN48 | LQFP64 | WLCSP64 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin<br>type | I/O<br>structure | Notes | Alternate functions                                                                                  | Additional<br>functions |

| -        | 51     | C3      | 78      | B11      | B11      | 111     | PC10                                                    | I/O         | FT               | -     | SPI3_SCK/I2S3_CK,<br>USART3_TX,<br>QUADSPI_BK1_IO1,<br>SDIO_D2, EVENTOUT                             | -                       |

| -        | 52     | B3      | 79      | C10      | B10      | 112     | PC11                                                    | I/O         | FT               | -     | I2S3ext_SD, SPI3_MISO,<br>USART3_RX,<br>QUADSPI_BK2_NCS,<br>FSMC_D2, SDIO_D3,<br>EVENTOUT            | -                       |

| -        | 53     | A3      | 80      | B10      | C10      | 113     | PC12                                                    | I/O         | FT               | -     | SPI3_MOSI/I2S3_SD,<br>USART3_CK, FSMC_D3,<br>SDIO_CK, EVENTOUT                                       | -                       |

| -        | -      | -       | 81      | C9       | E10      | 114     | PD0                                                     | I/O         | FT               | -     | CAN1_RX,<br>FSMC_D2/FSMC_DA2,<br>EVENTOUT                                                            | -                       |

| -        | -      | -       | 82      | B9       | D10      | 115     | PD1                                                     | I/O         | FT               | -     | CAN1_TX,<br>FSMC_D3/FSMC_DA3,<br>EVENTOUT                                                            | -                       |

| -        | 54     | A4      | 83      | C8       | E9       | 116     | PD2                                                     | I/O         | FT               | -     | TIM3_ETR, FSMC_NWE,<br>SDIO_CMD, EVENTOUT                                                            | -                       |

| -        | -      | -       | 84      | B8       | D9       | 117     | PD3                                                     | I/O         | FT               | -     | TRACED1,<br>SPI2_SCK/I2S2_CK,<br>DFSDM1_DATIN0,<br>USART2_CTS,<br>QUADSPI_CLK,<br>FSMC_CLK, EVENTOUT | -                       |

| -        | -      | -       | 85      | B7       | C9       | 118     | PD4                                                     | I/O         | FT               | -     | DFSDM1_CKIN0,<br>USART2_RTS,<br>FSMC_NOE, EVENTOUT                                                   | -                       |

| -        | -      | -       | 86      | A6       | B9       | 119     | PD5                                                     | I/O         | FT               | -     | USART2_TX,<br>FSMC_NWE, EVENTOUT                                                                     | -                       |

| -        | -      | -       | -       | -        | E7       | 120     | VSS                                                     | S           | -                | -     | -                                                                                                    | -                       |

| -        | -      | -       | -       | -        | F7       | 121     | VDD                                                     | S           | -                | -     | -                                                                                                    | -                       |

| -        | -      | -       | 87      | B6       | A8       | 122     | PD6                                                     | I/O         | FT               | -     | SPI3_MOSI/I2S3_SD,<br>DFSDM1_DATIN1,<br>USART2_RX,<br>FSMC_NWAIT,<br>EVENTOUT                        | -                       |

Table 9. STM32F412xE/G pin definition (continued)

|          |        | Pir     | n Nui   | nber     |          |         |                                                         |             |                  |       |                                                                                                    |                         |

|----------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|-------------|------------------|-------|----------------------------------------------------------------------------------------------------|-------------------------|

| UFQFPN48 | LQFP64 | WLCSP64 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin<br>type | I/O<br>structure | Notes | Alternate functions                                                                                | Additional<br>functions |

| 42       | 58     | B5      | 92      | В5       | C6       | 136     | PB6                                                     | I/O         | FT               | -     | TIM4_CH1, I2C1_SCL,<br>USART1_TX, CAN2_TX,<br>QUADSPI_BK1_NCS,<br>SDIO_D0, EVENTOUT                | -                       |

| 43       | 59     | A6      | 93      | B4       | D6       | 137     | PB7                                                     | I/O         | FT               | -     | TIM4_CH2, I2C1_SDA,<br>USART1_RX, FSMC_NL,<br>EVENTOUT                                             | -                       |

| 44       | 60     | D4      | 94      | A4       | D5       | 138     | BOOT0                                                   | Ι           | В                | -     | -                                                                                                  | VPP                     |

| 45       | 61     | C5      | 95      | A3       | C5       | 139     | PB8                                                     | I/O         | FT               | -     | TIM4_CH3, TIM10_CH1,<br>I2C1_SCL,<br>SPI5_MOSI/I2S5_SD,<br>CAN1_RX, I2C3_SDA,<br>SDIO_D4, EVENTOUT | -                       |

| 46       | 62     | B6      | 96      | В3       | В5       | 140     | PB9                                                     | I/O         | FT               | -     | TIM4_CH4, TIM11_CH1,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS,<br>CAN1_TX, I2C2_SDA,<br>SDIO_D5, EVENTOUT  | -                       |

| -        | -      | -       | 97      | C3       | A5       | 141     | PE0                                                     | I/O         | FT               | -     | TIM4_ETR, FSMC_NBL0,<br>EVENTOUT                                                                   | -                       |

| -        | -      | -       | 98      | A2       | A4       | 142     | PE1                                                     | I/O         | FT               | -     | FSMC_NBL1, EVENTOUT                                                                                | -                       |

| 47       | 63     | A7      | 99      | -        | E6       | -       | VSS                                                     | S           | -                | -     | -                                                                                                  | -                       |

| -        | -      | C6      | -       | H3       | E5       | 143     | PDR_ON                                                  | Ι           | FT               | -     | -                                                                                                  | -                       |

| 48       | 64     | A8      | 10<br>0 | -        | F5       | 144     | VDD                                                     | S           | -                | -     | -                                                                                                  | -                       |

Table 9. STM32F412xE/G pin definition (continued)

1. Function availability depends on the chosen device.

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited: - The speed should not exceed 2 MHz with a maximum load of 30 pF. 2.

- These I/Os must not be used as a current source (e.g. to drive an LED).

3. Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F412xE/Greference manual.

4. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

### 6.3 Operating conditions

### 6.3.1 General operating conditions

### Table 15. General operating conditions

| Symbol                             | Parameter                                                        | Conditions                                                             | Min                 | Тур  | Max                 | Unit |

|------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|------|---------------------|------|

|                                    |                                                                  | Power Scale3: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x01 | 0                   | -    | 64                  |      |

| f <sub>HCLK</sub>                  | Internal AHB clock frequency                                     | Power Scale2: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x10 | 0                   | -    | 84                  | MHz  |

|                                    |                                                                  | Power Scale1: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x11 | 0                   | -    | 100                 |      |

| f <sub>PCLK1</sub>                 | Internal APB1 clock<br>frequency                                 | -                                                                      | 0                   | -    | 50                  | MHz  |

| f <sub>PCLK2</sub>                 | Internal APB2 clock<br>frequency                                 | -                                                                      | 0                   | -    | 100                 | MHz  |

| $V_{DD}$                           | Standard operating voltage                                       | -                                                                      | 1.7 <sup>(1)</sup>  | -    | 3.6                 | V    |

| V <sub>DDA</sub> <sup>(2)(3)</sup> | Analog operating voltage<br>(ADC limited to 1.2 M<br>samples)    | Must be the same potential as $V_{DD}^{(4)}$                           | 1.7 <sup>(1)</sup>  | -    | 2.4                 | v    |

| VDDA <sup>(-),(-)</sup>            | Analog operating voltage<br>(ADC limited to 2.4 M<br>samples)    |                                                                        | 2.4                 | -    | 3.6                 | V    |

|                                    | USB supply voltage                                               | USB not used                                                           | 1.7                 | 3.3  | 3.6                 |      |

| V <sub>DDUSB</sub>                 | (supply voltage for PA11 and PA12 pins)                          | USB used <sup>(5)</sup>                                                | 3.0                 | -    | 3.6                 | V    |

| V <sub>BAT</sub>                   | Backup operating voltage                                         | -                                                                      | 1.65                | -    | 3.6                 | V    |

|                                    |                                                                  | VOS[1:0] bits in PWR_CR register = 0x01<br>Max frequency 64 MHz        | 1.08 <sup>(6)</sup> | 1.14 | 1.20 <sup>(6)</sup> |      |

| V <sub>12</sub>                    | Regulator ON: 1.2 V<br>internal voltage on<br>VCAP_1/VCAP_2 pins | VOS[1:0] bits in PWR_CR register = 0x10<br>Max frequency 84 MHz        | 1.20 <sup>(6)</sup> | 1.26 | 1.32 <sup>(6)</sup> | V    |

|                                    |                                                                  | VOS[1:0] bits in PWR_CR register = 0x11<br>Max frequency 100 MHz       | 1.26                | 1.32 | 1.38                |      |

|                                    | Regulator OFF: 1.2 V                                             | Max frequency 64 MHz                                                   | 1.10                | 1.14 | 1.20                |      |

| V <sub>12</sub>                    | external voltage must be<br>supplied on                          | Max frequency 84 MHz                                                   | 1.20                | 1.26 | 1.32                | V    |

|                                    | VCAP_1/VCAP_2 pins                                               | Max frequency 100 MHz                                                  | 1.26                | 1.32 | 1.38                |      |

|                                    | Input voltage on RST, FT and                                     | $2 \text{ V} \leq \text{V}_{DD} \leq 3.6 \text{ V}$                    | -0.3                | -    | 5.5                 |      |

| V <sub>IN</sub>                    | TC pins <sup>(7)</sup>                                           | $V_{DD} \le 2 V$                                                       | -0.3                | -    | 5.2                 | V    |

|                                    | Input voltage on BOOT0 pin                                       | -                                                                      | 0                   | -    | 9                   |      |

|                 |                    |                                                      |                            | Тур                                            |                           | Max <sup>(1)</sup>        |                            |      |     |      |      |

|-----------------|--------------------|------------------------------------------------------|----------------------------|------------------------------------------------|---------------------------|---------------------------|----------------------------|------|-----|------|------|

| Symbol          | Parameter          | Conditions                                           | f <sub>HCLK</sub><br>(MHz) | T <sub>A</sub> =<br>25 °C                      | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |     |      |      |

|                 |                    |                                                      | 100                        | 36.3                                           | 38.95                     | 41.19                     | 42.95                      |      |     |      |      |

|                 |                    |                                                      | 84                         | 31.1                                           | 33.22                     | 34.81                     | 36.10                      |      |     |      |      |

|                 |                    | External clock,<br>PLL ON <sup>(2)</sup> ,           | 64                         | 22.3                                           | 23.97                     | 25.10                     | 26.23                      |      |     |      |      |

|                 |                    | all peripherals enabled <sup>(3)</sup>               | 50                         | 18.3                                           | 19.77                     | 20.65                     | 21.73                      |      |     |      |      |

|                 |                    |                                                      | 25                         | 10.1                                           | 11.39                     | 12.16                     | 13.11                      |      |     |      |      |

|                 |                    | HSI, PLL OFF, all peripherals enabled <sup>(3)</sup> | 20 8.6 9.60 10.25          | 10.25                                          | 11.06                     |                           |                            |      |     |      |      |

|                 |                    |                                                      | 16                         | 6.3                                            | 6.85                      | 7.51                      | 8.38                       |      |     |      |      |

|                 | Supply current     |                                                      | 1                          | 1.1                                            | 1.39                      | 1.82                      | 2.61                       | mA   |     |      |      |

| I <sub>DD</sub> | in <b>Run mode</b> |                                                      | 100                        | 22.1                                           | 23.95                     | 25.80                     | 27.50                      |      |     |      |      |

|                 |                    |                                                      | 84                         | 19.7                                           | 20.79                     | 22.52                     | 24.12                      |      |     |      |      |

|                 |                    | External clock, PLL ON <sup>(2)</sup>                | 64                         | 14.5                                           | 15.88                     | 17.21                     | 18.54                      |      |     |      |      |

|                 |                    | all peripherals disabled <sup>(3)</sup>              |                            | Il peripherals disabled <sup>(3)</sup> 50 12.2 | 13.38                     | 14.59                     | 15.79                      |      |     |      |      |

|                 |                    |                                                      |                            |                                                |                           |                           | -                          | 25   | 7.0 | 8.05 | 8.89 |

|                 |                    |                                                      | 20                         | 6.0                                            | 6.84                      | 7.51                      | 8.52                       | ]    |     |      |      |

|                 |                    | HSI, PLL OFF, all                                    | 16                         | 4.4                                            | 4.91                      | 5.56                      | 6.54                       | ]    |     |      |      |

|                 |                    | peripherals disabled <sup>(3)</sup>                  | 1                          | 0.9                                            | 1.25                      | 1.79                      | 2.59                       | ]    |     |      |      |

## Table 25. Typical and maximum current consumption in run mode, code with data processing<br/>(ART accelerator disabled) running from Flash memory - $V_{DD}$ = 3.6 V

1. Based on characterization, not tested in production unless otherwise specified.

2. Refer to Table 44 and RM0383 for the possible PLL VCO setting

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

Г

٦

### SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 64* for the SPI interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 15*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

Т

| Symbol                                       | Parameter                            | Conditions                                                                  | Min                    | Тур               | Мах                       | Unit |

|----------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------|------------------------|-------------------|---------------------------|------|

|                                              |                                      | Master full duplex/receiver mode,<br>2.7 V < $V_{DD}$ < 3.6 V<br>SPI1/4/5   | -                      | -                 | 50                        |      |

|                                              |                                      | Master transmitter mode<br>1.7 V < V <sub>DD</sub> < 3.6 V<br>SPI1/4/5      | -                      | -                 | 50                        |      |

|                                              |                                      | Master mode<br>1.7 V < V <sub>DD</sub> < 3.6 V<br>SPI1/2/3/4/5              | -                      | -                 | 25                        |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave transmitter/full duplex mode<br>2.7 V < $V_{DD}$ < 3.6 V<br>SPI1//4/5 | -                      | -                 | 50                        | MHz  |

|                                              |                                      | Slave transmitter/full duplex mode<br>1.7 V < $V_{DD}$ < 3.6 V<br>SPI1/4/5  | -                      | -                 | 35 <sup>(2)</sup>         |      |

|                                              |                                      | Slave receiver mode,<br>1.7 V < V <sub>DD</sub> < 3.6 V<br>SPI1/4/5         | -                      | -                 | 50                        |      |

|                                              |                                      | Slave mode,<br>1.7 V < V <sub>DD</sub> < 3.6 V<br>SPI2/3                    | -                      | -                 | 25                        |      |

| Duty(SCK)                                    | Duty cycle of SPI clock<br>frequency | Slave mode                                                                  | 30                     | 50                | 70                        | %    |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode, SPI presc = 2                                                  | T <sub>PCLK</sub> -1.5 | T <sub>PCLK</sub> | Т <sub>РСLК</sub><br>+1.5 | ns   |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                                   | 3T <sub>PCLK</sub>     | -                 | -                         | ns   |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                                   | 2T <sub>PCLK</sub>     | -                 | -                         | ns   |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode                                                                 | 4.5                    | -                 | -                         | ns   |

| t <sub>su(SI)</sub>                          |                                      | Slave mode                                                                  | 1.5                    | -                 | -                         | ns   |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                                                 | 5                      | -                 | -                         | ns   |

| t <sub>h(SI)</sub>                           |                                      | Slave mode                                                                  | 0.5                    | -                 | -                         | ns   |

| Table 64. SPI dynamic characteristics <sup>v</sup> | 4. SPI dynamic characteristics | (1) |

|----------------------------------------------------|--------------------------------|-----|

|----------------------------------------------------|--------------------------------|-----|

### **QSPI** interface characteristics

Unless otherwise specified, the parameters given in the following tables for QSPI are derived from tests performed under the ambient temperature,  $f_{AHB}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 15*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C=20pF

- Measurement points are done at CMOS levels: 0.5VDD

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics.

| Symbol                                    | Parameter                | Conditions                                                                 | Min                       | Тур | Мах                       | Unit |

|-------------------------------------------|--------------------------|----------------------------------------------------------------------------|---------------------------|-----|---------------------------|------|

| £                                         |                          | Write mode<br>1.71 V≤V <sub>DD</sub> ≤3.6 V<br>C <sub>load</sub> = 15 pF   | -                         | -   | 80                        |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> | QSPI clock<br>frequency  | Read mode<br>2.7 V <v<sub>DD&lt;3.6 V<br/>C<sub>load</sub> = 15 pF</v<sub> | -                         | -   | 100                       | MHz  |

|                                           |                          | 1.71 V≤V <sub>DD</sub> ≤3.6 V                                              | -                         | -   | 50                        |      |

| t <sub>w(CKH)</sub>                       | QSPI clock high          |                                                                            | (T <sub>(CK)</sub> / 2)-1 | -   | Т <sub>(СК)</sub> / 2     |      |

| t <sub>w(CKL)</sub>                       | and low                  | -                                                                          | T <sub>(CK)</sub> / 2)    | -   | (T <sub>(CK)</sub> / 2)+1 |      |

| t <sub>s(IN)</sub>                        | Data input setup<br>time | -                                                                          | 0.5                       | -   | -                         |      |

| t <sub>h(IN)</sub>                        | Data input hold<br>time  | -                                                                          | 3.5                       | -   | -                         | ns   |

| t <sub>v(OUT)</sub>                       | Data output valid time   | -                                                                          | -                         | 1   | 1.5                       |      |

| t <sub>h(OUT)</sub>                       | Data output hold<br>time | -                                                                          | 0.5                       | -   | -                         |      |

| Table 66. QSPI dynamic characteristics in SDR mode | able 66. | vnamic chara | cteristics in SE | R mode <sup>(1)</sup> |

|----------------------------------------------------|----------|--------------|------------------|-----------------------|

|----------------------------------------------------|----------|--------------|------------------|-----------------------|

1. Guaranteed by characterization results, not tested in production.

| Symbol                                                         | Parameter                                                                       | Conditions                                                               | Min | Тур | Мах | Unit |

|----------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>SCK</sub> QSPI clock<br>1/t <sub>c(SCK)</sub> frequency |                                                                                 | Write mode<br>1.71 V≤V <sub>DD</sub> ≤3.6 V<br>C <sub>load</sub> = 15 pF | -   | -   | 80  |      |

|                                                                | Read mode<br>2.7 V <v<sub>DD&lt;3.6 V<br/><math>C_{load}</math> = 15 pF</v<sub> | -                                                                        | -   | 80  | MHz |      |

|                                                                |                                                                                 | 1.71 V≤V <sub>DD</sub> ≤3.6 V                                            | -   | -   | 50  |      |

- 2. The USB OTG FS functionality is ensured down to 2.7 V but not the full USB full speed electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{\text{DD}}$  voltage range.

- 3. Guaranteed by design, not tested in production.

- 4.  $\mbox{ R}_{\rm L}$  is the load connected on the USB OTG FS drivers.

Note: When VBUS sensing feature is enabled, PA9 should be left at their default state (floating input), not as alternate function. A typical 200 µA current consumption of the embedded sensing block (current to voltage conversion to determine the different sessions) can be observed on PA9 when the feature is enabled.

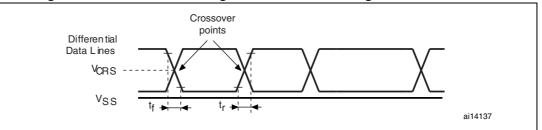

Figure 45. USB OTG FS timings: definition of data signal rise and fall time

### Table 70. USB OTG FS electrical characteristics<sup>(1)</sup>

| Driver characteristics |                                 |                                |     |     |      |  |  |  |

|------------------------|---------------------------------|--------------------------------|-----|-----|------|--|--|--|

| Symbol                 | Parameter                       | Conditions Min                 |     | Max | Unit |  |  |  |

| t <sub>r</sub>         | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |

| t <sub>f</sub>         | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |

| t <sub>rfm</sub>       | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |  |

| V <sub>CRS</sub>       | Output signal crossover voltage |                                | 1.3 | 2.0 | V    |  |  |  |

1. Guaranteed by design, not tested in production.

Measured from 10% to 90% of the data signal. For more detailed informations, refer to USB Specification -Chapter 7 (version 2.0).

#### CAN (controller area network) interface

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CANx\_TX and CANx\_RX).

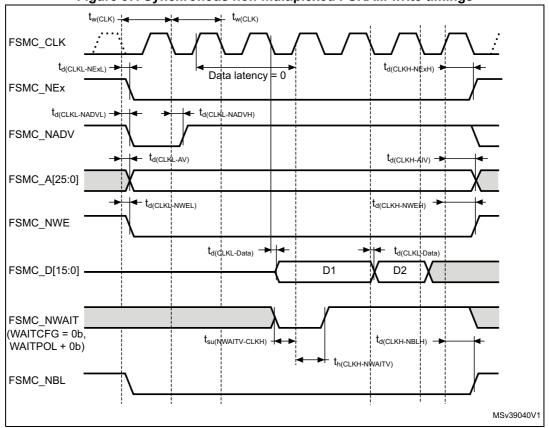

| Symbol                      | Parameter                                                            | Min                      | Мах | Unit |

|-----------------------------|----------------------------------------------------------------------|--------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FSMC_CLK period, V <sub>DD</sub> range= 2.7 to 3.6 V                 | 2T <sub>HCLK</sub> - 0.5 | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FSMC_CLK low to FSMC_NEx low (x= 02)                                 | -                        | 1   |      |

| t <sub>d(CLKH-NExH)</sub>   | FSMC_CLK high to FSMC_NEx high (x= 02)                               | T <sub>HCLK</sub> + 0.5  | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FSMC_CLK low to FSMC_NADV low                                        | -                        | 1   |      |

| t <sub>d(CLKL-NADVH)</sub>  | FSMC_CLK low to FSMC_NADV high                                       | 0                        | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FSMC_CLK low to FSMC_Ax valid (x=1625)                               | -                        | 2   |      |

| t <sub>d(CLKH-AIV)</sub>    | (CLKH-AIV) FSMC_CLK high to FSMC_Ax invalid (x=1625) T <sub>HC</sub> |                          | -   |      |

| t <sub>d(CLKL-NWEL)</sub>   | EL) FSMC_CLK low to FSMC_NWE low                                     |                          | 1.5 | ns   |

| t <sub>(CLKH-NWEH)</sub>    | FSMC_CLK high to FSMC_NWE high                                       | T <sub>HCLK</sub> + 0.5  | -   | 115  |

| t <sub>d(CLKL-ADV)</sub>    | t <sub>d(CLKL-ADV)</sub> FSMC_CLK low to FSMC_AD[15:0] valid         |                          | 2.5 |      |

| t <sub>d(CLKL-ADIV)</sub>   | LKL-ADIV) FSMC_CLK low to FSMC_AD[15:0] invalid                      |                          | -   |      |

| t <sub>d(CLKL-DATA)</sub>   | FSMC_A/D[15:0] valid data after FSMC_CLK low                         | -                        | 4   |      |

| t <sub>d(CLKL-NBLL)</sub>   | FSMC_CLK low to FSMC_NBL low                                         | -                        | 3   |      |

| t <sub>d(CLKH-NBLH)</sub>   | t <sub>d(CLKH-NBLH)</sub> FSMC_CLK high to FSMC_NBL high             |                          | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high                                | 2                        | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FSMC_NWAIT valid after FSMC_CLK high                                 | 2                        | -   |      |

Table 92. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

1.  $C_L = 30 \text{ pF.}$

2. Based on characterization, not tested in production.

- 1. C<sub>L</sub> = 30 pF.

- 2. Based on characterization, not tested in production.

### Figure 57. Synchronous non-multiplexed PSRAM write timings

| millimeters inches <sup>(1)</sup> |       |        |       |        |        |        |

|-----------------------------------|-------|--------|-------|--------|--------|--------|

| Symbol                            | Min   | Тур    | Мах   | Min    | Тур    | Max    |

| А                                 | 0.525 | 0.555  | 0.585 | 0.0207 | 0.0219 | 0.0230 |

| A1                                | -     | 0.170  | -     | -      | 0.0067 | -      |

| A2                                | -     | 0.380  | -     | -      | 0.0150 | -      |

| A3 <sup>(2)</sup>                 | -     | 0.025  | -     | -      | 0.0010 | -      |

| b <sup>(3)</sup>                  | 0.220 | 0.250  | 0.280 | 0.0087 | 0.0098 | 0.0110 |

| D                                 | 3.588 | 3.623  | 3.658 | 0.1413 | 0.1426 | 0.1440 |

| E                                 | 3.616 | 3.651  | 3.686 | 0.1424 | 0.1437 | 0.1451 |

| е                                 | -     | 0.400  | -     | -      | 0.0157 | -      |

| e1                                | -     | 2.800  | -     | -      | 0.1102 | -      |

| e2                                | -     | 2.800  | -     | -      | 0.1102 | -      |

| F                                 | -     | 0.4115 | -     | -      | 0.0162 | -      |

| G                                 | -     | 0.4255 | -     | -      | 0.0168 | -      |

| aaa                               | -     | -      | 0.100 | -      | -      | 0.0039 |

| bbb                               | -     | -      | 0.100 | -      | -      | 0.0039 |

| ссс                               | -     | -      | 0.100 | -      | -      | 0.0039 |

| ddd                               | -     | -      | 0.050 | -      | -      | 0.0020 |

| eee                               | -     | -      | 0.050 | -      | -      | 0.0020 |

## Table 98. WLCSP64 - 64-pin, 3.658 x 3.686 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

## Figure 61. WLCSP64 - 64-pin, 3.658 x 3.686 mm, 0.4 mm pitch wafer level chip scale recommended footprint

| 0000000<br>0000000<br>0000000<br>Dpad<br>0000000<br>000000<br>000000<br>000000<br>000000<br>0000 |

|--------------------------------------------------------------------------------------------------|

|                                                                                                  |

### Table 99. WLCSP64 recommended PCB design rules (0.4 mm pitch)

| Dimension | Recommended values |  |  |

|-----------|--------------------|--|--|

| Pitch     | 0.4 mm             |  |  |

| Dpad      | 0.225 mm           |  |  |

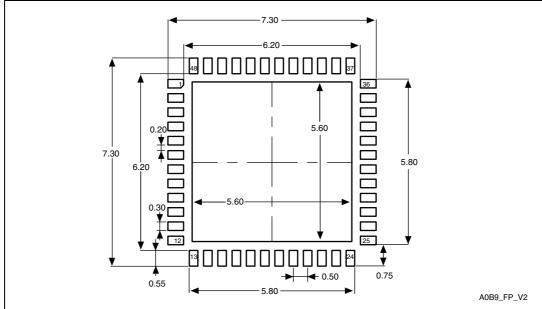

## Table 100. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data (continued)

| P      |             |       |       |                       |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

| Symbol | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |

| E2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |

| Т      | -           | 0.152 | -     | -                     | 0.0060 | -      |  |

| b      | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

### Figure 64. UFQFPN48 recommended footprint

1. Dimensions are in millimeters.

1. Dimensions are expressed in millimeters.

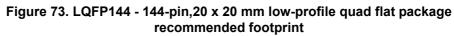

### **Device marking for LQFP144**

The following figure gives an example of topside marking and pin 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# Appendix A Recommendations when using the internal reset OFF

When the internal reset is OFF, the following integrated features are no longer supported:

- The integrated power-on-reset (POR)/power-down reset (PDR) circuitry is disabled.

- The brownout reset (BOR) circuitry must be disabled. By default BOR is OFF.

- The embedded programmable voltage detector (PVD) is disabled.

- V<sub>BAT</sub> functionality is no more available and VBAT pin should be connected to V<sub>DD</sub>.