## STMicroelectronics - STM32F412VET3TR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                                       |

|----------------------------|----------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                              |

| Core Size                  | 32-Bit Single-Core                                                                           |

| Speed                      | 100MHz                                                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                            |

| Number of I/O              | 81                                                                                           |

| Program Memory Size        | 512KB (512K x 8)                                                                             |

| Program Memory Type        | FLASH                                                                                        |

| EEPROM Size                |                                                                                              |

| RAM Size                   | 256K x 8                                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                  |

| Data Converters            | A/D 16x12b                                                                                   |

| Oscillator Type            | Internal                                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                           |

| Mounting Type              | Surface Mount                                                                                |

| Package / Case             | 100-LQFP                                                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f412vet3tr                      |

|                            |                                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 91.  | Synchronous multiplexed NOR/PSRAM read timings                            |       |

|------------|---------------------------------------------------------------------------|-------|

| Table 92.  | Synchronous multiplexed PSRAM write timings                               | 156   |

| Table 93.  | Synchronous non-multiplexed NOR/PSRAM read timings                        | 157   |

| Table 94.  | Synchronous non-multiplexed PSRAM write timings                           | 159   |

| Table 95.  | Dynamic characteristics: SD / MMC characteristics                         | 160   |

| Table 96.  | Dynamic characteristics: eMMC characteristics VDD = 1.7 V to 1.9 V        | 161   |

| Table 97.  | RTC characteristics                                                       | 161   |

| Table 98.  | WLCSP64 - 64-pin, 3.658 x 3.686 mm, 0.4 mm pitch wafer level chip scale   |       |

|            | package mechanical data                                                   | 163   |

| Table 99.  | WLCSP64 recommended PCB design rules (0.4 mm pitch)                       | 163   |

| Table 100. | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |       |

|            | package mechanical data                                                   | 165   |

| Table 101. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat                         |       |

|            | package mechanical data                                                   | 169   |

| Table 102. | LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package               |       |

|            | mechanical data                                                           | 171   |

| Table 103. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package               |       |

|            | mechanical data                                                           | 175   |

| Table 104. | UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball        |       |

|            | grid array package mechanical data                                        | . 178 |

| Table 105. | UFBGA100 recommended PCB design rules (0.5 mm pitch BGA)                  | 179   |

| Table 106. | UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball      |       |

|            | grid array package mechanical data                                        | . 181 |

| Table 107. | UFBGA144 recommended PCB design rules (0.80 mm pitch BGA)                 |       |

| Table 108. | Package thermal characteristics                                           |       |

| Table 109. | Ordering information scheme                                               |       |

| Table 110. | Document revision history                                                 |       |

|            |                                                                           |       |

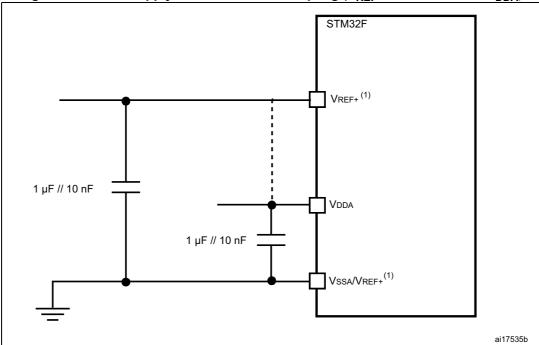

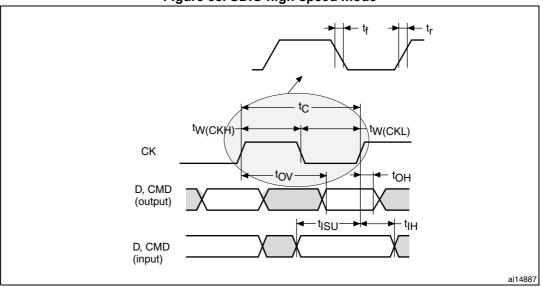

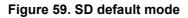

| Figure 45.<br>Figure 46.<br>Figure 47.<br>Figure 48.<br>Figure 50.<br>Figure 51.<br>Figure 52.<br>Figure 53.<br>Figure 54.<br>Figure 55.<br>Figure 56.<br>Figure 57.<br>Figure 58. | USB OTG FS timings: definition of data signal rise and fall time135ADC accuracy characteristics139Typical connection diagram using the ADC140Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> )141Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )142Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms146Asynchronous nultiplexed PSRAM/NOR write waveforms148Asynchronous multiplexed PSRAM/NOR write waveforms151Synchronous multiplexed PSRAM/NOR write waveforms153Synchronous multiplexed PSRAM write timings153Synchronous non-multiplexed PSRAM write timings155Synchronous non-multiplexed PSRAM write timings155Synchronous non-multiplexed PSRAM write timings155Synchronous non-multiplexed PSRAM write timings157Synchronous non-multiplexed PSRAM write timings157Synchronous non-multiplexed PSRAM write timings157Synchronous non-multiplexed PSRAM write timings158SDIO high-speed mode160 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 59.                                                                                                                                                                         | SD default mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 60.                                                                                                                                                                         | WLCSP64 - 64-pin, 3.658 x 3.686 mm, 0.4 mm pitch wafer level chip scale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| U U                                                                                                                                                                                | package outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 61.                                                                                                                                                                         | WLCSP64 - 64-pin, 3.658 x 3.686 mm, 0.4 mm pitch wafer level chip scale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                    | recommended footprint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 62.                                                                                                                                                                         | WLCSP64 marking example (package top view) 164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 63.                                                                                                                                                                         | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                    | package outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 64.                                                                                                                                                                         | UFQFPN48 recommended footprint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

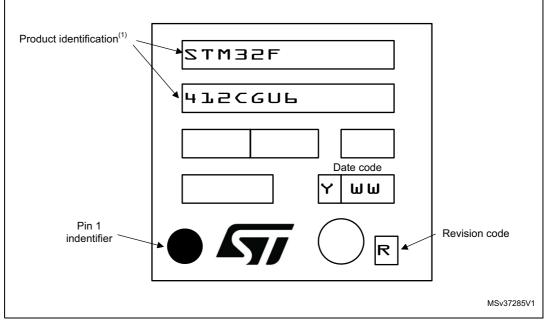

| Figure 65.                                                                                                                                                                         | UFQFPN48 marking example (package top view)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 66.                                                                                                                                                                         | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 67.                                                                                                                                                                         | LQFP64 recommended footprint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 68.                                                                                                                                                                         | LQFP64 marking example (package top view)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 69.                                                                                                                                                                         | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 70.                                                                                                                                                                         | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

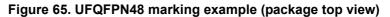

| Figure 71.                                                                                                                                                                         | LQFP100 marking example (package top view)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 72.                                                                                                                                                                         | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 73.                                                                                                                                                                         | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| riguie 70.                                                                                                                                                                         | recommended footprint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 74.                                                                                                                                                                         | LQFP144 marking example (package top view)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 75.                                                                                                                                                                         | UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| i igure i e.                                                                                                                                                                       | grid array package outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 76.                                                                                                                                                                         | UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0                                                                                                                                                                                  | grid array package recommended footprint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 77.                                                                                                                                                                         | UFBGA100 marking example (package top view)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 78.                                                                                                                                                                         | UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -                                                                                                                                                                                  | grid array package outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 79.                                                                                                                                                                         | UFBGA144 - 144-pin, 10 x 10 mm, 0.80 mm pitch, ultra fine pitch ball                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                    | grid array recommended footprint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 80.                                                                                                                                                                         | UFBGA144 marking example (package top view)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 81.                                                                                                                                                                         | USB controller configured as peripheral-only and used in Full speed mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 82.                                                                                                                                                                         | USB peripheral-only Full speed mode with direct connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>F</b> ' 0.0                                                                                                                                                                     | for VBUS sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 83.                                                                                                                                                                         | USB peripheral-only Full speed mode, VBUS detection using GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 84.                                                                                                                                                                         | USB controller configured as host-only and used in full speed mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 85.<br>Figure 86.                                                                                                                                                           | USB controller configured in dual mode and used in full speed mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

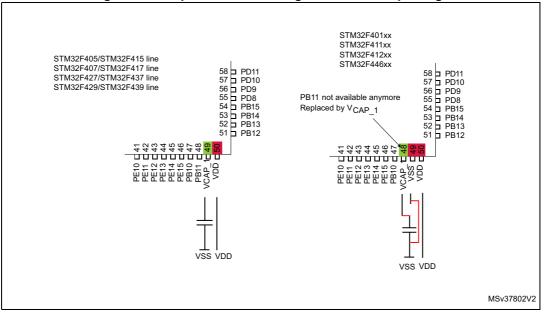

# 2.1 Compatibility with STM32F4 series

The STM32F412xE/G are fully software and feature compatible with the STM32F4 series (STM32F42x, STM32F401, STM32F43x, STM32F41x, STM32F405 and STM32F407)

The STM32F412xE/G can be used as drop-in replacement of the other STM32F4 products but some slight changes have to be done on the PCB board.

#### Figure 1. Compatible board design for LQFP100 package

# 3.4 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 byte and the whole 4 Gbyte of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

## 3.5 Embedded Flash memory

The devices embed up to 1 Mbyte of Flash memory available for storing programs and data.

The Flash user area can be protected against reading by an entrusted code (Read Protection, RDP) with different protection levels.

The flash user sectors can also be individually protected against write operation.

Furthermore the proprietary readout protection (PCROP) can also individually protect the flash user sectors against D-bus read accesses.

(Additional information can be found in the product reference manual).

To optimize the power consumption the Flash memory can also be switched off in Run or in Sleep mode (see Section 3.21: Low-power modes).

Two modes are available: Flash in Stop mode or in DeepSleep mode (trade off between power saving and startup time.

Before disabling the Flash, the code must be executed from the internal RAM.

## 3.6 One-time programmable bytes

A one-time programmable area is available with16 OTP blocks of 32 bytes. Each block can be individually locked

(Additional information can be found in the product reference manual)

# 3.7 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

DocID028087 Rev 4

The DMA can be used with the main peripherals:

- SPI and I<sup>2</sup>S

- I<sup>2</sup>C and I<sup>2</sup>CFMP

- USART

- General-purpose, basic and advanced-control timers TIMx

- SD/SDIO/MMC/eMMC host interface

- Quad-SPI

- ADC

- Digital Filter for sigma-delta modulator (DFSDM) with a separate stream for each filter.

## **3.11** Flexible static memory controller (FSMC)

The Flexible static memory controller (FSMC) includes a NOR/PSRAM memory controller. It features four Chip Select outputs supporting the following modes: SRAM, PSRAM and NOR Flash memory.

The main functions are:

- 8-,16-bit data bus width

- Write FIFO

- Maximum FSMC\_CLK frequency for synchronous accesses is 90 MHz.

## LCD parallel interface

The FSMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

# 3.12 Quad-SPI memory interface (QUAD-SPI)

All devices embed a Quad-SPI memory interface, which is a specialized communication interface targeting single, dual or quad-SPI Flash memories. It can work in direct mode through registers, external Flash status register polling mode and memory mapped mode. Up to 256 Mbyte of external Flash memory are mapped. They can be accessed in 8, 16 or 32-bit mode. Code execution is also supported. The opcode and the frame format are fully programmable. Communication can be performed either in single data rate or dual data rate.

There are three power modes configured by software when the regulator is ON:

- MR is used in the nominal regulation mode (With different voltage scaling in Run mode) In Main regulator mode (MR mode), different voltage scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption.

- LPR is used in the Stop mode

The LP regulator mode is configured by software when entering Stop mode.

• Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Depending on the package, one or two external ceramic capacitors should be connected on the VCAP\_1 and VCAP\_2 pins. The VCAP\_2 pin is only available for the 100 pins and 144 pins packages.

All packages have the regulator ON feature.

## 3.19.2 Regulator OFF

This feature is available only on UFBGA100 and UFBGA144 packages, which feature the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V<sub>12</sub> voltage source through V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency.

The two 2.2  $\mu\text{F}$  ceramic capacitors should be replaced by two 100 nF decoupling capacitors.

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

The DFSDM peripheral supports:

- 4 multiplexed input digital serial channels:

- configurable SPI interface to connect various SD modulator(s)

- configurable Manchester coded 1 wire interface support

- PDM (Pulse Density Modulation) microphone input support

- maximum input clock frequency up to 20 MHz (10 MHz for Manchester coding)

- clock output for SD modulator(s): 0...20 MHz

- alternative inputs from 4 internal digital parallel channels (up to 16 bit input resolution):

- internal sources: device memory data streams (DMA)

- 2 digital filter modules with adjustable digital signal processing:

- Sinc<sup>x</sup> filter: filter order/type (1...5), oversampling ratio (up to 1...1024)

- integrator: oversampling ratio (1...256)

- up to 24-bit output data resolution, signed output data format

- automatic data offset correction (offset stored in register by user)

- continuous or single conversion

- start-of-conversion triggered by

- software trigger

- internal timers

- external events

- start-of-conversion synchronously with first digital filter module (DFSDM1FLT0)

- analog watchdog feature:

- low value and high value data threshold registers

- dedicated configurable Sinc<sup>x</sup> digital filter (order = 1...3, oversampling ratio = 1...32

- input from digital output data or from selected input digital serial channels

- continuous monitoring independently from standard conversion

- short circuit detector to detect saturated analog input values (bottom and top range):

- up to 8-bit counter to detect 1...256 consecutive 0's or 1's on serial data stream

- monitoring continuously each input serial channel

- break signal generation on analog watchdog event or on short circuit detector event

- extremes detector:

- storage of minimum and maximum values of final conversion data

- refreshed by software

- DMA capability to read the final conversion data

- interrupts: end of conversion, overrun, analog watchdog, short circuit input serial channel clock absence

- "regulator" or injected" conversions:

- "regular" conversions can be requested at any time or even in continuous mode without having any impact on the timing of "injected" conversions

- "injected" conversions for precise timing and with high conversion priority.

Г

|          |        | Pir     | n Nui   | mber     |          |         |                                                         |             |                  |       |                                                                                                                   |                         |

|----------|--------|---------|---------|----------|----------|---------|---------------------------------------------------------|-------------|------------------|-------|-------------------------------------------------------------------------------------------------------------------|-------------------------|

| UFQFPN48 | LQFP64 | WLCSP64 | LQFP100 | UFBGA100 | UFBGA144 | LQFP144 | Pin name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin<br>type | I/O<br>structure | Notes | Alternate functions                                                                                               | Additional<br>functions |

| -        | -      | -       | 88      | A5       | A9       | 123     | PD7                                                     | I/O         | FT               | -     | DFSDM1_CKIN1,<br>USART2_CK,<br>FSMC_NE1, EVENTOUT                                                                 | -                       |

| -        | -      | -       | _       | -        | E8       | 124     | PG9                                                     | I/O         | FT               | -     | USART6_RX,<br>QUADSPI_BK2_IO2,<br>FSMC_NE2, EVENTOUT                                                              | -                       |

| -        | -      | -       | -       | -        | D8       | 125     | PG10                                                    | I/O         | FT               | -     | FSMC_NE3, EVENTOUT                                                                                                | -                       |

| -        | -      | -       | -       | -        | C8       | 126     | PG11                                                    | I/O         | FT               | -     | CAN2_RX, EVENTOUT                                                                                                 | -                       |

| -        | -      | -       | -       | -        | B8       | 127     | PG12                                                    | I/O         | FT               | -     | USART6_RTS, CAN2_TX,<br>FSMC_NE4, EVENTOUT                                                                        | -                       |

| -        | -      | -       | -       | -        | D7       | 128     | PG13                                                    | I/O         | FT               | -     | TRACED2,<br>USART6_CTS,<br>FSMC_A24, EVENTOUT                                                                     | -                       |

| -        | -      | -       | -       | -        | C7       | 129     | PG14                                                    | I/O         | FT               | -     | TRACED3, USART6_TX,<br>QUADSPI_BK2_IO3,<br>FSMC_A25, EVENTOUT                                                     | -                       |

| -        | -      | -       | -       | -        | -        | 130     | VSS                                                     | S           | -                | -     | -                                                                                                                 | -                       |

| -        | -      | -       | -       | -        | F6       | 131     | VDD                                                     | S           | -                | -     | -                                                                                                                 | -                       |

| -        | -      | -       | -       | -        | B7       | 132     | PG15                                                    | I/O         | FT               | -     | USART6_CTS,<br>EVENTOUT                                                                                           | -                       |

| 39       | 55     | A5      | 89      | A8       | A7       | 133     | PB3                                                     | I/O         | FT               | -     | JTDO-SWO, TIM2_CH2,<br>I2CFMP1_SDA,<br>SPI1_SCK/I2S1_CK,<br>SPI3_SCK/I2S3_CK,<br>USART1_RX, I2C2_SDA,<br>EVENTOUT | -                       |

| 40       | 56     | B4      | 90      | A7       | A6       | 134     | PB4                                                     | I/O         | FT               | -     | JTRST, TIM3_CH1,<br>SPI1_MISO, SPI3_MISO,<br>I2S3ext_SD, I2C3_SDA,<br>SDIO_D0, EVENTOUT                           | -                       |

| 41       | 57     | C4      | 91      | C5       | B6       | 135     | PB5                                                     | I/O         | FT               | -     | TIM3_CH2, I2C1_SMBA,<br>SPI1_MOSI/I2S1_SD,<br>SPI3_MOSI/I2S3_SD,<br>CAN2_RX, SDIO_D3,<br>EVENTOUT                 | -                       |

Table 9. STM32F412xE/G pin definition (continued)

66/193

DocID028087 Rev 4

|        |      | AF0     | AF1           | AF2                    | AF3                               | AF4                                | AF5                                                 | AF6                                                        | AF7                                        | AF8                                   | AF9                                                                       | AF10                                    | AF12       | AF15     |

|--------|------|---------|---------------|------------------------|-----------------------------------|------------------------------------|-----------------------------------------------------|------------------------------------------------------------|--------------------------------------------|---------------------------------------|---------------------------------------------------------------------------|-----------------------------------------|------------|----------|

| F      | Port | SYS_AF  | TIM1/<br>TIM2 | TIM3/<br>TIM4/<br>TIM5 | TIM8/<br>TIM9/<br>TIM10/<br>TIM11 | 12C1/<br>12C2/<br>12C3/<br>12CFMP1 | SPI1/I2S1/<br>SPI2/I2S2/<br>SPI3/I2S3/<br>SPI4/I2S4 | SPI2/I2S2/SPI3<br>/I2S3/SPI4/<br>I2S4/SPI5/I2S5<br>/DFSDM1 | SPI3/I2S3/<br>USART1/<br>USART2/<br>USART3 | DFSDM1/<br>USART3/<br>USART6/<br>CAN1 | I2C2/I2C3/<br>I2CFMP1/<br>CAN1/CAN2<br>/TIM12/<br>TIM13/TIM14<br>/QUADSPI | DFSDM1/<br>QUADSPI/<br>FSMC<br>/OTG1_FS | FSMC /SDIO | SYS_AF   |

|        | PF0  | -       | -             | -                      | -                                 | I2C2_SDA                           | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | FSMC_A0    | EVENTOUT |

|        | PF1  | -       | -             | -                      | -                                 | I2C2_SCL                           | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | FSMC_A1    | EVENTOUT |

|        | PF2  | -       | -             | -                      | -                                 | I2C2_SMBA                          | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | FSMC_A2    | EVENTOUT |

|        | PF3  | -       | -             | TIM5_CH1               | -                                 | -                                  | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | FSMC_A3    | EVENTOUT |

|        | PF4  | -       | -             | TIM5_CH2               | -                                 | -                                  | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | FSMC_A4    | EVENTOUT |

|        | PF5  | -       | -             | TIM5_CH3               | -                                 | -                                  | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | FSMC_A5    | EVENTOUT |

|        | PF6  | TRACED0 | -             | -                      | TIM10_CH1                         | -                                  | -                                                   | -                                                          | -                                          | -                                     | QUADSPI_<br>BK1_IO3                                                       | -                                       | -          | EVENTOUT |

|        | PF7  | TRACED1 | -             | -                      | TIM11_CH1                         | -                                  | -                                                   | -                                                          | -                                          | -                                     | QUADSPI_<br>BK1_IO2                                                       | -                                       | -          | EVENTOUT |

| Port F | PF8  | -       | -             | -                      | -                                 | -                                  | -                                                   | -                                                          | -                                          | -                                     | TIM13_CH1                                                                 | QUADSPI_<br>BK1_IO0                     | -          | EVENTOUT |

|        | PF9  | -       | -             | -                      | -                                 | -                                  | -                                                   | -                                                          | -                                          | -                                     | TIM14_CH1                                                                 | QUADSPI_<br>BK1_IO1                     | -          | EVENTOUT |

|        | PF10 | -       | TIM1_ETR      | TIM5_CH4               | -                                 | -                                  | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | -          | EVENTOUT |

|        | PF11 | -       | -             | -                      | TIM8_ETR                          | -                                  | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | -          | EVENTOUT |

|        | PF12 | -       | -             | -                      | TIM8_BKIN                         | -                                  | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | FSMC_A6    | EVENTOUT |

|        | PF13 | -       | -             | -                      | -                                 | I2CFMP1_<br>SMBA                   | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | FSMC_A7    | EVENTOUT |

|        | PF14 | -       | -             | -                      | -                                 | I2CFMP1_<br>SCL                    | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | FSMC_A8    | EVENTOUT |

|        | PF15 | -       | -             | -                      | -                                 | I2CFMP1_<br>SDA                    | -                                                   | -                                                          | -                                          | -                                     | -                                                                         | -                                       | FSMC_A9    | EVENTOUT |

Table 10. STM32F412xE/G alternate functions (continued)

Pinouts and pin description

5

| Symbol | Parameter                             | Conditions                           | Min | Тур | Max | Unit |  |

|--------|---------------------------------------|--------------------------------------|-----|-----|-----|------|--|

|        |                                       | UFQFPN48                             | -   | -   | 625 |      |  |

|        |                                       | WLCSP64                              | -   | -   | 392 |      |  |

|        | Power dissipation at                  | LQFP64                               | -   | -   | 425 |      |  |

| $P_D$  | TA = 85°C for range 6 or              | LQFP100                              | -   | -   | 465 | mW   |  |

|        | TA = 105°C for range 7 <sup>(8)</sup> | LQFP144                              |     |     | 571 |      |  |

|        |                                       | UFBGA100                             | -   | -   | 351 |      |  |

|        |                                       | UFBGA144                             | -   | -   | 416 |      |  |

|        | Ambient temperature for               | Maximum power dissipation            | -40 | -   | 85  |      |  |

| Та     | range 6                               | Low power dissipation <sup>(9)</sup> | -40 | -   | 105 |      |  |

| IA     | Ambient temperature for               | Maximum power dissipation            | -40 | -   | 105 | °C   |  |

|        | range 7                               | Low power dissipation <sup>(9)</sup> | -40 | -   | 125 |      |  |

| т.     |                                       | Range 6                              | -40 | -   | 105 |      |  |

| TJ     | Junction temperature range            | Range 7                              | -40 | -   | 125 |      |  |

Table 15. General operating conditions (continued)

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V with the use of an external power supply supervisor (refer to Section 3.18.2: Internal reset OFF).

2. When the ADC is used, refer to Table 71: ADC characteristics.

- 3. If  $V_{REF+}$  pin is present, it must respect the following condition:  $V_{DDA}-V_{REF}+ < 1.2$  V.

- 4. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and power-down operation.

- 5. Only the DM ( $P_{A11}$ ) and DP ( $P_{A12}$ ) pads are supplied through  $V_{DDUSB}$ . For application where the  $V_{BUS}$  ( $P_{A9}$ ) is directly connected to the chip, a minimum  $V_{DD}$  supply of 2.7V is required.

(some application examples are shown in appendix B)

- 6. Guaranteed by test in production

- 7. To sustain a voltage higher than  $V_{DD}$ +0.3, the internal Pull-up and Pull-Down resistors must be disabled

- 8. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

- 9. In low power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$ .

|                 |                    |                                                      |                            | Тур                       |                           | Max <sup>(1)</sup>        |                            |      |

|-----------------|--------------------|------------------------------------------------------|----------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter          | Conditions                                           | f <sub>HCLK</sub><br>(MHz) | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                    |                                                      | 100                        | 27.2                      | 28.70 <sup>(4)</sup>      | 30.14                     | 31.98                      |      |

|                 |                    |                                                      | 84                         | 21.9                      | 23.60                     | 24.31                     | 25.37                      |      |

|                 |                    | External clock,<br>PLL ON <sup>(2)</sup> ,           | 64                         | 15.2                      | 16.45                     | 17.03                     | 17.87                      |      |

|                 |                    | all peripherals enabled <sup>(3)</sup>               | 50                         | 12.1                      | 13.12                     | 13.67                     | 14.46                      |      |