Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 20MHz                                                                                  |

| Connectivity               | I <sup>2</sup> C, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT                                        |

| Number of I/O              | 18                                                                                     |

| Program Memory Size        | 2KB (2K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | 256 x 8                                                                                |

| RAM Size                   | 256 x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                            |

| Data Converters            | A/D 4x10b                                                                              |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                         |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/n79e822asg |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2 FEATURES

- Fully static design 8-bit Turbo 51 CMOS microcontroller up to 20MHz when V\_{DD}=4.5V to 5.5V, 12MHz when V\_{DD}=2.7V to 5.5V

- 16K/8K/4K/2K bytes of AP Flash EPROM, with ICP and external writer programmable mode.

- 256 bytes of on-chip RAM.

- **256** bytes NVM Data Flash EPROM for customer data storage used and 10K writer cycles; Data Flash program/erase  $V_{DD}$ =3.0V to 5.5V

- Instruction-set compatible with MCS-51.

- Built-in internal RC oscillator (about 6MHz)

- Two 8-bit bi-directional and one 2-bit bi-directional ports.

- Two 16-bit timer/counters.

- 13 interrupts source with four levels of priority.

- One enhanced full duplex serial port with framing error detection and automatic address recognition.

- The 4 outputs mode and TTL/Schmitt trigger selectable Port.

- Programmable Watchdog Timer.

- Four-channel 10-bit PWM (Pulse Width Modulator).

- Four-channel multiplexed with 10-bits A/D convert.

- One I2C communication port (Master / Slave).

- Eight keypad interrupt inputs.

- Two analog comparators.

- Configurable on-chip oscillator.

- LED drive capability (20mA) on all port pins.

- Brownout voltage detect interrupt and reset.

- Development Tools:

- JTAG ICE(In Circuit Emulation) tool

- ICP(In Circuit Programming) writer

- Packages:

N79E825ADG ---- PDIP20 N79E825ASG ---- SOP20 N79E825ARG ---- SSOP20 N79E824ADG ---- PDIP20 N79E824ASG ---- SOP20 N79E823ADG ---- PDIP20 N79E823ASG ---- SOP20 N79E823ARG ---- SSOP20 N79E823ARG ---- PDIP20

- 5 -

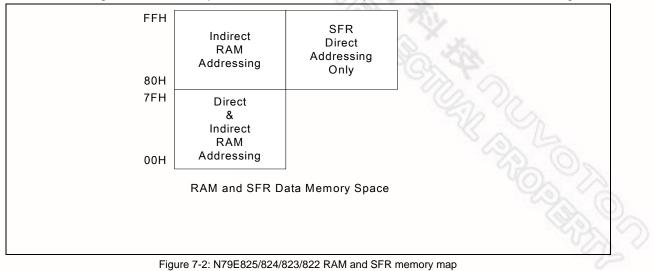

#### 7.3 Register Map

As mentioned before the N79E825 series have separate Program and Data Memory areas. The onchip **256** bytes scratch pad RAM is in addition to the internal memory. There are also several Special Function Registers (SFRs) which can be accessed by software. The SFRs can be accessed only by direct addressing, while the on-chip RAM can be accessed by either direct or indirect addressing.

Since the scratch-pad RAM is only **256** bytes it can be used only when data contents are small. There are several other special purpose areas within the scratch-pad RAM. These are described as follows.

# nuvoTon

| BIT    | NAME       | FUNCTION                                                                                                                                                             |

|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | 7 PWMRUN   | 0: The PWM is not running.                                                                                                                                           |

|        |            | 1: The PWM counter is running.                                                                                                                                       |

|        |            | 0: The registers value of PWMP and PWMn are never loaded to counter and Comparator registers.                                                                        |

| 6 Load | Load       | 1: The PWMP and PWMn registers load value to counter and compare registers<br>at the counter underflow. This bit is auto cleared by hardware at next clock<br>cycle. |

| F      | 5 CF       | 0: The 10-bit counter down count is not underflow.                                                                                                                   |

| Э      |            | 1: The 10-bit counter down count is underflow. This bit is Software clear.                                                                                           |

| 4      | CLRPWM     | 1: Clear 10-bit PWM counter to 000H. This bit is auto cleared by hardware.                                                                                           |

| 3      | PWM3I      | 0: PWM3 out is non-inverted.                                                                                                                                         |

| 3      | FVIVIOI    | 1: PWM3 output is inverted.                                                                                                                                          |

| 2      | PWM2I      | 0: PWM2 out is non-inverted.                                                                                                                                         |

| 2      | PVVIVIZI   | 1: PWM2 output is inverted.                                                                                                                                          |

| 1      | PWM1I      | 0: PWM1 out is non-inverted.                                                                                                                                         |

| 1      | PVVIVITI   | 1: PWM1 output is inverted.                                                                                                                                          |

| 0      | PWM0I      | 0: PWM0 out is non-inverted.                                                                                                                                         |

| U      |            | 1: PWM0 output is inverted.                                                                                                                                          |

| PWM2   | 2 LOW BITS |                                                                                                                                                                      |

| Bit:                         | 7                                     | 6          | 5           | 4       | 3        | 2      | 1      | 0           |  |  |

|------------------------------|---------------------------------------|------------|-------------|---------|----------|--------|--------|-------------|--|--|

|                              | PWM2.7                                | PWM2.6     | PWM2.5      | PWM2.4  | PWM2.3   | PWM2.2 | PWM2.1 | PWM2.0      |  |  |

| Mnem                         | onic: PWM2                            | L          |             |         |          |        | A      | ddress: DDh |  |  |

| BIT                          | NAME                                  |            | FUNCTION    |         |          |        |        |             |  |  |

| 7~0                          | 0 PWM2.[7:0] PWM 2 Low Bits Register. |            |             |         |          |        |        |             |  |  |

| PWM3 LOW BITS REGISTER       |                                       |            |             |         |          |        |        |             |  |  |

| Bit:                         | 7                                     | 6          | 5           | 4       | 3        | 2      | 1      | 0           |  |  |

|                              | PWM3.7                                | PWM3.6     | PWM3.5      | PWM3.4  | PWM3.3   | PWM3.2 | PWM3.1 | PWM3.0      |  |  |

| Mnemonic: PWM3L Address: DEh |                                       |            |             |         |          |        |        |             |  |  |

| BIT                          | NAME                                  |            |             |         | FUNCTION |        |        |             |  |  |

| 7~0                          | PWM3.[7:0                             | )] PWM 3 L | ow Bits Reg | jister. |          |        |        |             |  |  |

| PWM                          | CONTROL I                             | REGISTER   | 2           |         |          |        |        |             |  |  |

| Bit:                         | 7 ~ 2                                 | 6          | 5           | 4       | 3        | 2      | 1      | 0           |  |  |

|                              | ВКСН                                  | BKPS       | BPEN        | BKEN    | PWM3B    | PWM2B  | PWM1B  | PWM0B       |  |  |

| Mnem                         | onic: PWMC                            | ON2        | 5           |         |          |        | A      | ddress: DFh |  |  |

|                              |                                       |            |             |         |          |        |        |             |  |  |

# nuvoTon

| <b>BIT</b><br>7-0     | onic: B                  |                                                                |                                                             |                                                    | 100                     | N                                                |                                                      | Address:  |

|-----------------------|--------------------------|----------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------|-------------------------|--------------------------------------------------|------------------------------------------------------|-----------|

|                       | NAME                     |                                                                |                                                             |                                                    | FUNCTION                | 2 The                                            |                                                      |           |

|                       | B.[7:0]                  | The B reg                                                      | ister is the s                                              | tandard 805                                        |                         | A #                                              | s a second a                                         | accumulat |

| PORT                  | 0 DIGITAL                |                                                                | SABLE                                                       |                                                    |                         | 1997                                             | 12                                                   |           |

| Bit:                  | 7                        | 6                                                              | 5                                                           | 4                                                  | 3                       | 2                                                | 2100                                                 | 0         |

|                       | P0ID.7                   | P0ID.6                                                         | P0ID.5                                                      | P0ID.4                                             | P0ID.3                  | P0ID.2                                           | P0ID.1                                               | P0ID.0    |

| Mnem                  | onic: P0ID               |                                                                |                                                             |                                                    |                         |                                                  | 20                                                   | Address:  |

| BIT                   | NAME                     |                                                                |                                                             |                                                    | FUNCTIO                 | N                                                | Nr.                                                  | 5.0       |

| 7~0                   | POID.[7:0]               |                                                                | e Port 0 digi<br>le Port 0 dig                              | •                                                  |                         |                                                  |                                                      | Ľ         |

| Bit:                  | 7                        | 6                                                              | 5                                                           | 4                                                  | 3                       | 2                                                | 1                                                    | 0         |

|                       | -                        | -                                                              | PPWMH                                                       | PWDIH                                              | PC2H                    | PC1H                                             | PKBH                                                 | PI2H      |

| Mnem                  | onic: IP1H               | 1                                                              |                                                             |                                                    | 1                       |                                                  |                                                      | Address:  |

| BIT                   | NAME                     |                                                                |                                                             |                                                    | FUNCTIO                 | N                                                |                                                      |           |

| <u> </u>              |                          | _                                                              | d                                                           |                                                    |                         |                                                  |                                                      |           |

| 7                     | -                        | Reserve                                                        | ·u.                                                         |                                                    |                         |                                                  |                                                      |           |

|                       | -                        | Reserve<br>Reserve                                             |                                                             |                                                    |                         |                                                  |                                                      |           |

| 7                     | -<br>-<br>PPWMH          | Reserve                                                        |                                                             | gh priority of                                     | PWM's bra               | ke is highes                                     | st priority lev                                      | vel.      |

| 7<br>6                | -<br>-<br>PPWMH<br>PWDIH | Reserve<br>1: To se                                            | d.                                                          |                                                    |                         | -                                                |                                                      | vel.      |

| 7<br>6<br>5           |                          | Reserve<br>1: To se<br>1: To se                                | d.<br>t interrupt hig                                       | gh priority of                                     | Watchdog                | is highest p                                     | riority level.                                       |           |

| 7<br>6<br>5<br>4      | PWDIH<br>PC2H<br>PC1H    | Reserve   1: To se   1: To se   1: To se   1: To se            | d.<br>t interrupt hig<br>t interrupt hig                    | gh priority of<br>gh priority of                   | Watchdog i<br>Comparato | is highest p<br>or 2 is highe                    | riority level.<br>st priority lev                    | vel.      |

| 7<br>6<br>5<br>4<br>3 | PWDIH<br>PC2H            | Reserve   1: To se   1: To se   1: To se   1: To se   1: To se | d.<br>t interrupt hig<br>t interrupt hig<br>t interrupt hig | gh priority of<br>gh priority of<br>gh priority of | Watchdog i<br>Comparato | is highest p<br>or 2 is highes<br>or 1 is highes | riority level.<br>st priority lev<br>st priority lev | vel.      |

| Continued |

|-----------|

|-----------|

| OP-CODE        | HEX CODE | BYTES | N79E825<br>SERIES<br>MACHINE<br>CYCLE | N79E825<br>SERIES<br>CLOCK<br>CYCLES | 8032<br>CLOCK<br>CYCLES | N79E825<br>SERIES VS.<br>8032 SPEED<br>RATIO |

|----------------|----------|-------|---------------------------------------|--------------------------------------|-------------------------|----------------------------------------------|

| MOV A, R5      | ED       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV A, R6      | EE       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV A, R7      | EF       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV A, @R0     | E6       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV A, @R1     | E7       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV A, direct  | E5       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV A, #data   | 74       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R0, A      | F8       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV R1, A      | F9       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV R2, A      | FA       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV R3, A      | FB       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV R4, A      | FC       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV R5, A      | FD       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV R6, A      | FE       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV R7, A      | FF       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV R0, direct | A8       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R1, direct | A9       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R2, direct | AA       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R3, direct | AB       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R4, direct | AC       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R5, direct | AD       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R6, direct | AE       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R7, direct | AF       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R0, #data  | 78       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R1, #data  | 79       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R2, #data  | 7A       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R3, #data  | 7B       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R4, #data  | 7C       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R5, #data  | 7D       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R6, #data  | 7E       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV R7, #data  | 7F       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV @R0, A     | F6       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

# nuvoTon

|          | SFR RE      | SET VALUE |             |

|----------|-------------|-----------|-------------|

| SFR NAME | RESET VALUE | SFR NAME  | RESET VALUE |

| P0       | 1111 1111B  | I2DAT     | xxxx xxxxB  |

| SP       | 0000 0111B  | I2STATUS  | 0000 0xxxB  |

| DPL      | 0000 0000B  | I2TIMER   | 0000 0000B  |

| DPH      | 0000 0000B  | I2CLK     | 0000 0000B  |

| PCON     | 00xx 0000B  | I2CON     | 0000 0000B  |

| TCON     | 0000 0000B  | I2ADDR    | xxxx xxxxB  |

| TMOD     | 0000 0000B  | ТА        | 1111 1111B  |

| TL0      | 0000 0000B  | PSW       | 0000 0000B  |

| TL1      | 0000 0000B  | PWMP1     | xxxx xx00B  |

| TH0      | 0000 0000B  | PWM0H     | xxxx xx00B  |

| TH1      | 0000 0000B  | PWM1H     | xxxx xx00B  |

| CKCON    | 0000 0000B  | PWM2H     | xxxx xx00B  |

| P1       | 1111 xx11B  | PWM3H     | xxxx xx00B  |

| DIVM     | 0000 0000B  | WDCON     | 0x00 0000B  |

| SCON     | 0000 0000B  | PWMP0     | 0000 0000B  |

| SBUF     | xxxx xxxxB  | PWM0L     | 0000 0000B  |

| P2       | xxx xx11B   | PWM1L     | 0000 0000B  |

| KBI      | 0000 0000B  | PWMCON1   | 0000 0000B  |

| AUXR1    | 0000 0000B  | PWM2L     | 0000 0000B  |

| IE       | 0000 0000B  | PWM3L     | 0000 0000B  |

| SADDR    | 0000 0000B  | PWMCON2   | 0000 0000B  |

| CMP1     | 0000 0000B  | PWMCON3   | xxxxxx0B    |

| CMP2     | 0000 0000B  | ACC       | 0000 0000B  |

| P0M1     | 0000 0000B  | ADCCON    | xx00 0x00B  |

| P0M2     | 0000 0000B  | ADCH      | xxxx xxxxB  |

| P1M1     | 0000 0000B  | EIE       | xx000 000B  |

| P1M2     | 0000 0000B  | В         | 0000 0000B  |

| P2M1     | 0000 0000B  | POIDS     | 0000 0000B  |

| P2M2     | xxxx xx00B  | IPH       | xx00 0000B  |

| IP0H     | x000 0000B  | IP1       | xx00 0000B  |

| IP0      | x000 0000B  | NVMADDR   | 0000 0000B  |

| SADEN    | 0000 0000B  | NVMDAT    | 0000 0000B  |

| 3        | 2.0%        | NVMCON    | 00xx xxxxB  |

Table 11-1: SFR Reset Value

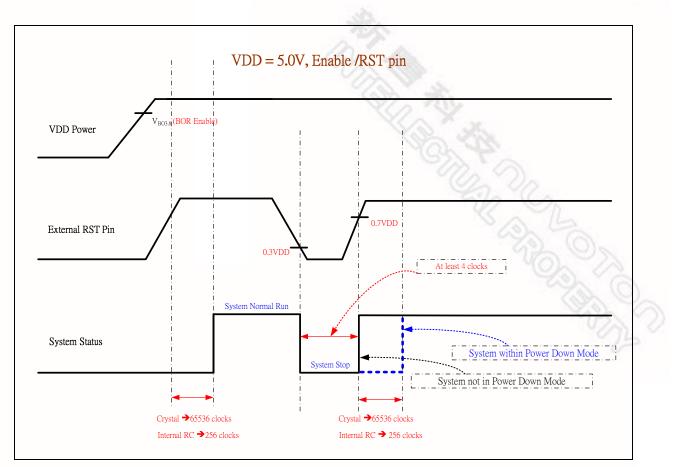

Figure 11-2: External reset timing diagram

# 12 INTERRUPTS

nuvoTon

The N79E825 series have four priority level interrupts structure with 13 interrupt sources. Each of the interrupt sources has an individual priority bit, flag, interrupt vector and enable bit. In addition, the interrupts can be globally enabled or disabled.

#### **12.1 Interrupt Sources**

The External Interrupts INT0 and INT1 can be either edge triggered or level triggered, depending on bits IT0 and IT1. The bits IE0 and IE1 in the TCON register are the flags which are checked to generate the interrupt. In the edge triggered mode, the INTx inputs are sampled in every machine cycle. If the sample is high in one cycle and low in the next, then a high to low transition is detected and the interrupts request flag IEx in TCON is set. The flag bit requests the interrupt. Since the external interrupts are sampled every machine cycle, they have to be held high or low for at least one complete machine cycle. The IEx flag is automatically cleared when the service routine is called. If the level triggered mode is selected, then the requesting source has to hold the pin low till the interrupt is serviced. The IEx flag will not be cleared by the hardware on entering the service routine. If the interrupt continues to be held low even after the service routine is completed, then the processor may acknowledge another interrupt request from the same source.

The Timer 0 and 1 Interrupts are generated by the TF0 and TF1 flags. These flags are set by the overflow in the Timer 0 and Timer 1. The TF0 and TF1 flags are automatically cleared by the hardware when the timer interrupt is serviced. The Watchdog timer can be used as a system monitor or a simple timer. In either case, when the time-out count is reached, the Watchdog Timer interrupt flag WDIF (WDCON.3) is set. If the interrupt is enabled by the enable bit EIE.4, then an interrupt will occur.

The Serial block can generate interrupt on reception or transmission. There are two interrupt sources from the Serial block, which are obtained by the RI and TI bits in the SCON SFR. These bits are not automatically cleared by the hardware, and the user will have to clear these bits by software.

All the bits that generate interrupts can be set or reset by software, and thereby software initiated interrupts can be generated. Each of the individual interrupts can be enabled or disabled by setting or clearing a bit in the IE SFR. IE also has a global enable/disable bit EA, which can be cleared to disable all interrupts.

The ADC can generate interrupt after finished ADC converter. There is one interrupt source, which is obtained by the ADCI bit in the ADCCON SFR. This bit is not automatically cleared by the hardware, and the user will have to clear this bit using software.

The two comparators can generate interrupt after comparator output has toggle occurs by CMF1 and CMF2. These bits are not automatically cleared by the hardware, and the user will have to clear these bits using software.

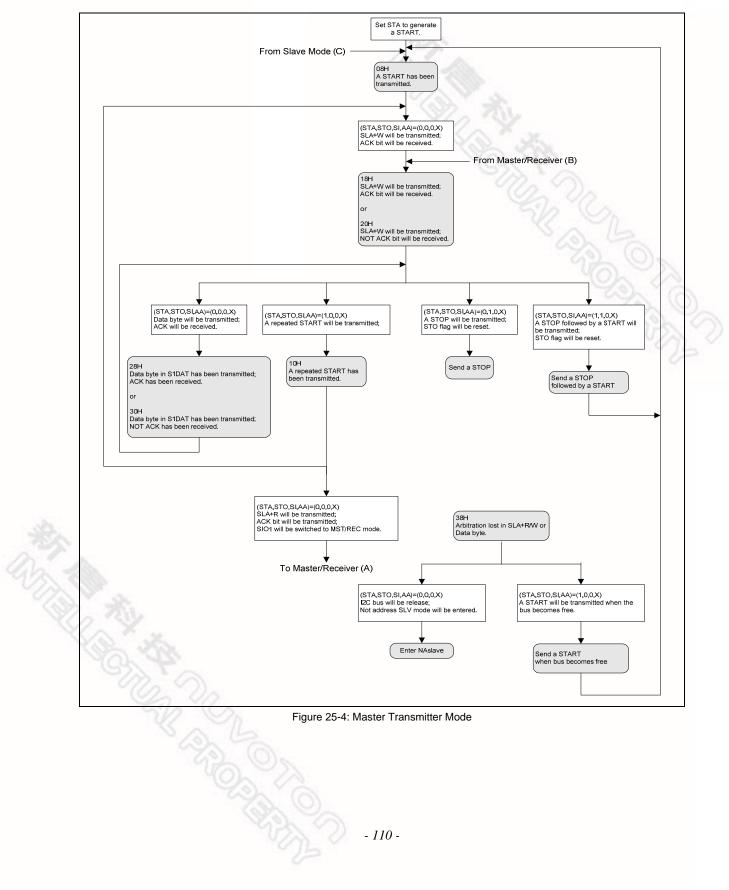

The I2C function can generate interrupt, if EI2C and EA bits are enabled, when SI Flag is set due to a new I2C status code is generated, SI flag is generated by hardware and must be cleared by software.

The PWM function can generate interrupt by BKF flag, after external brake pin has brake occurred. This bit will be cleared by software.

The interrupt flags are sampled every machine cycle. In the same machine cycle, the sampled interrupts are polled and their priority is resolved. If certain conditions are met then the hardware will execute an internally generated LCALL instruction which will vector the process to the appropriate interrupt vector address. The conditions for generating the LCALL are;

1. An interrupt of equal or higher priority is not currently being serviced.

2. The current polling cycle is the last machine cycle of the instruction currently being execute.

3. The current instruction does not involve a write to IE, EIE, IPO, IPOH, IP1 or IPH1 registers and is

Continued .

| Source                    | Flag    | Vector<br>address | Interrupt<br>Enable Bits | Interrupt<br>Priority | Flag cleared<br>by                        | Arbitration<br>Ranking | Power<br>Down<br>Wakeup |

|---------------------------|---------|-------------------|--------------------------|-----------------------|-------------------------------------------|------------------------|-------------------------|

| External<br>Interrupt 1   | IE1     | 0013H             | EX1 (IE.2)               | IP0H.2, IP0.2         | Hardware,<br>Follow the<br>inverse of pin | 7                      | Yes                     |

| KBI Interrupt             | KBF     | 003BH             | EKB (EIE.1)              | IP1H.1, IP1.1         | Software                                  | 8                      | Yes                     |

| Comparator 1<br>Interrupt | CMF1    | 0063H             | EC1 (EIE.2)              | IP1H.2, IP1.2         | Software                                  | 9                      | Yes                     |

| Timer 1 Interrupt         | TF1     | 001BH             | ET1 (IE.3)               | IP0H.3, IP0.3         | Hardware,<br>software                     | 10                     | No                      |

| Comparator 2<br>Interrupt | CMF2    | 0043H             | EC2 (EIE.3)              | IP1H.3, IP1.3         | Software                                  | 11                     | Yes                     |

| Serial Port Tx<br>and Rx  | TI & RI | 0023H             | ES (IE.4)                | IP0H.4, IP0.4         | Software                                  | 12                     | No                      |

| PWM Interrupt             | BKF     | 0073H             | EPWM (EIE.5)             | IP1H.5, IP1.5         | Software                                  | 13 (lowest)            | No                      |

Note: 1. The ADC Converter can wake up Power Down Mode when its clock source is from internal RC.

Table 12-3: Vector location for Interrupt sources and power down wakeup

### 12.3 Response Time

The response time for each interrupt source depends on several factors, such as the nature of the

interrupt and the instruction underway. In the case of external interrupts INT0 and INT1, they are sampled at C3 of every machine cycle and then their corresponding interrupt flags IEx will be set or reset. The Timer 0 and 1 overflow flags are set at C3 of the machine cycle in which overflow has occurred. These flag values are polled only in the next machine cycle. If a request is active and all three conditions are met, then the hardware generated LCALL is executed. This LCALL itself takes four machine cycles to be completed. Thus there is a minimum time of five machine cycles between the interrupt flag being set and the interrupt service routine being executed.

A longer response time should be anticipated if any of the three conditions are not met. If a higher or equal priority is being serviced, then the interrupt latency time obviously depends on the nature of the service routine currently being executed. If the polling cycle is not the last machine cycle of the instruction being executed, then an additional delay is introduced. The maximum response time (if no other interrupt is in service) occurs if the N79E825 series are performing a write to IE, EIE, IPO, IPOH, IP1 or IP1H and then executes a MUL or DIV instruction. From the time an interrupt source is activated, the longest reaction time is 12 machine cycles. This includes 1 machine cycle to detect the interrupt, 2 machine cycles to complete the IE, EIE, IPO, IPOH, IP1 or IP1H access, 5 machine cycles to complete the MUL or DIV instruction and 4 machine cycles to complete the hardware LCALL to the interrupt vector location.

Thus in a single-interrupt system the interrupt response time will always be more than 5 machine cycles and not more than 12 machine cycles. The maximum latency of 12 machine cycles is 48 clock cycles. Note that in the standard 8051 the maximum latency is 8 machine cycles which equals 96

### nuvoton

instructions to reset the Watchdog Timer, which will allow the code to run without any Watchdog Timer interrupts. Now the Watchdog Timer reset is enabled and the Watchdog interrupt may be disabled. If any errant code is executed now, then the reset Watchdog Timer instructions will not be executed at the required instants and Watchdog reset will occur.

The Watchdog Timer time-out selection will result in different time-out values depending on the clock speed. The reset, when enabled, will occur when 512 clocks after time-out has occurred.

| WD1 | WD0 | INTERRUPT<br>TIME-OUT | RESET<br>TIME-OUT     | NUMBER OF<br>CLOCKS | TIME<br>@ 10 MHZ |

|-----|-----|-----------------------|-----------------------|---------------------|------------------|

| 0   | 0   | 2 <sup>17</sup>       | 2 <sup>17</sup> + 512 | 131072              | 13.11 mS         |

| 0   | 1   | 2 <sup>20</sup>       | 2 <sup>20</sup> + 512 | 1048576             | 104.86 mS        |

| 1   | 0   | 2 <sup>23</sup>       | 2 <sup>23</sup> + 512 | 8388608             | 838.86 mS        |

| 1   | 1   | 2 <sup>26</sup>       | 2 <sup>26</sup> + 512 | 67108864            | 6710.89 mS       |

Table 15-2: Time-out values for the Watchdog Timer

The Watchdog Timer will de disabled by a power-on/fail reset. The Watchdog Timer reset does not disable the Watchdog Timer, but will restart it. In general, software should restart the timer to put it into a known state. The control bits that support the Watchdog Timer are discussed below.

#### 15.1 WATCHDOG CONTROL

WDIF: WDCON.3 - Watchdog Timer Interrupt flag. This bit is set whenever the time-out occurs in the Watchdog Timer. If the Watchdog interrupt is enabled (EIE.4), then an interrupt will occur (if the global interrupt enable is set and other interrupt requirements are met). Software or any reset can clear this bit.

WTRF: WDCON.2 - Watchdog Timer Reset flag. This bit is set whenever a watchdog reset occurs. This bit is useful for determined the cause of a reset. Software must read it, and clear it manually. A Power-fail reset will clear this bit. If EWRST = 0, then this bit will not be affected by the Watchdog Timer.

EWRST: WDCON.1 - Enable Watchdog Timer Reset. This bit when set to 1 will enable the Watchdog Timer reset function. Setting this bit to 0 will disable the Watchdog Timer reset function, but will leave the timer running.

WDCLR: WDCON.0 - Reset Watchdog Timer. This bit is used to clear the Watchdog Timer and to restart it. This bit is self-clearing, so after the software writes 1 to it the hardware will automatically clear it. If the Watchdog Timer reset is enabled, then the WDCLR has to be set by the user within 512 clocks of the time-out. If this is not done then a Watchdog Timer reset will occur. A CONCERNING AND CONC

# ηυνοτοη

#### 15.2 CLOCK CONTROL of Watchdog

WD1, WD0: WDCON.5, WDCON.4 - Watchdog Timer Mode select bits. These two bits select the time-out interval for the watchdog timer. The reset time is 512 clocks longer than the interrupt time-out value.

The default Watchdog time-out is 2<sup>17</sup> clocks, which is the shortest time-out period. The WDRUN, WD0, WD1, EWRST, WDIF and WDCLR bits are protected by the Timed Access procedure. This prevents software from accidentally enabling or disabling the watchdog timer. More importantly, it makes it highly improbable that errant code can enable or disable the Watchdog Timer.

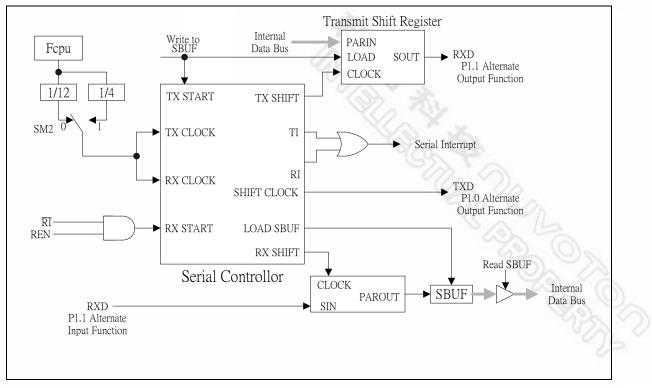

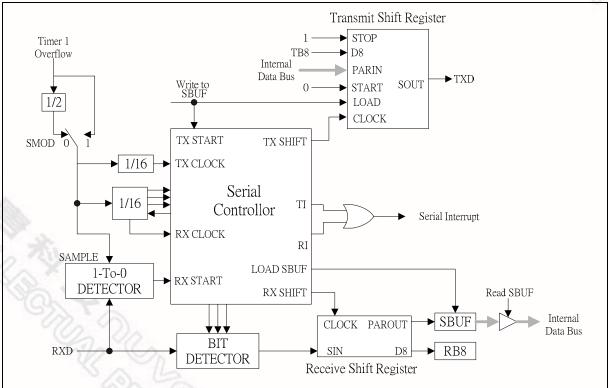

Figure 16-1: Serial Port Mode 0

The TI flag is set high in C1 following the end of transmission of the last bit. The serial port will receive data when REN is 1 and RI is zero. The shift clock (TxD) will be activated and the serial port will latch data on the rising edge of shift clock. The external device should therefore present data on the falling edge on the shift clock. This process continues till all the 8 bits have been received. The RI flag is set in C1 following the last rising edge of the shift clock on TxD. This will stop reception, till the RI is cleared by software.

#### 16.2 MODE 1

In Mode 1, the full duplex asynchronous mode is used. Serial communication frames are made up of 10 bits transmitted on TXD and received on RXD. The 10 bits consist of a start bit (0), 8 data bits (LSB first), and a stop bit (1). On received, the stop bit goes into RB8 in the SFR SCON. The baud rate in this mode is variable. The serial baud can be programmed to be 1/16 or 1/32 of the Timer 1 overflow. Since the Timer 1 can be set to different reload values, a wide variation in baud rates is possible.

Transmission begins with a write to SBUF. The serial data is brought out on to TxD pin at C1 following the first roll-over of divide by 16 counter. The next bit is placed on TxD pin at C1 following the next rollover of the divide-by-16 counter. Thus the transmission is synchronized to the divide-by-16 counter and not directly to the write to SBUF signal. After all 8 bits of data are transmitted, the stop bit is transmitted. The TI flag is set in the C1 state after the stop bit has been put out on TxD pin. This will be at the 10th rollover of the divide-by-16 counter after a write to SBUF.

If the first bit detected after the falling edge of RxD pin, is not 0, then this indicates an invalid start bit, and the reception is immediately aborted. The serial port again looks for a falling edge in the RxD line. If a valid start bit is detected, then the rest of the bits are also detected and shifted into the SBUF. After shifting in 9 data bits, there is one more shift to do, after which the SBUF and RB8 are loaded and RI is set. However certain conditions must be met before the loading and setting of RI can be done.

- 1. RI must be 0 and

- 2. Either SM2 = 0, or the received stop bit = 1.

If these conditions are met, then the stop bit goes to RB8, the 8 data bits go into SBUF and RI is set. Otherwise the received frame may be lost. After the middle of the stop bit, the receiver goes back to looking for a 1-to-0 transition on the RxD pin.

#### 16.4 MODE 3

This mode is similar to Mode 2 in all aspects, except that the baud rate is programmable. The user must first initialize the Serial related SFR SCON before any communication can take place. This involves selection of the Mode and baud rate. The Timer 1 should also be initialized if modes 1 and 3 are used. In all four modes, transmission is started by any instruction that uses SBUF as a destination register. Reception is initiated in Mode 0 by the condition RI = 0 and REN = 1. This will generate a clock on the TxD pin and shift in 8 bits on the RxD pin. Reception is initiated in the other modes by the incoming start bit if REN = 1. The external device will start the communication by transmitting the start bit.

Figure 16-4: Serial Port Mode 3

- 84 -

The Master processor can selectively communicate with groups of slaves by using the Given Address. All the slaves can be addressed together using the Broadcast Address. The addresses for each slave are defined by the SADDR and SADEN SFRs. The slave address is an 8-bit value specified in the SADDR SFR. The SADEN SFR is actually a mask for the byte value in SADDR. If a bit position in SADEN is 0, then the corresponding bit position in SADDR is don't care. Only those bit positions in SADDR whose corresponding bits in SADEN are 1 are used to obtain the Given Address. This gives the user flexibility to address multiple slaves without changing the slave address in SADDR.

The following example shows how the user can define the Given Address to address different slaves. Slave 1:

SADDR 1010 0100 SADEN 1111 1010 Given 1010 0x0x

Slave 2:

SADDR 1010 0111 SADEN 1111 1001 Given 1010 0xx1

The Given address for slave 1 and 2 differ in the LSB. For slave 1, it is a don't care, while for slave 2 it is 1. Thus to communicate only with slave 1, the master must send an address with LSB = 0 (1010 0000). Similarly the bit 1 position is 0 for slave 1 and don't care for slave 2. Hence to communicate only with slave 2 the master has to transmit an address with bit 1 = 1 (1010 0011). If the master wishes to communicate with both slaves simultaneously, then the address must have bit 0 = 1 and bit 1 = 0. The bit 3 position is don't care for both the slaves. This allows two different addresses to select both slaves (1010 0001 and 1010 0101).

The master can communicate with all the slaves simultaneously with the Broadcast Address. This address is formed from the logical OR of the SADDR and SADEN SFRs. The zeros in the result are defined as don't cares. In most cases the Broadcast Address is FFh. In the previous case, the Broadcast Address is (1111111x) for slave 1 and (1111111) for slave 2.

The SADDR and SADEN SFRs are located at address A9h and B9h respectively. On reset, these two SFRs are initialized to 00h. This results in Given Address and Broadcast Address being set as xxxx xxxx (i.e. all bits don't care). This effectively removes the multiprocessor communications feature, since any selectivity is disabled.

Example 5: Invalid Access

| MOV  | TA, #0AAh | ;3 M/C |

|------|-----------|--------|

| NOP  |           | ;1 M/C |

| MOV  | TA, #055h | ;3 M/C |

| SETB | EWT       | ;2 M/C |

In the first three examples, the writing to the protected bits is done before the 3 machine cycles window closes. In Example 4, however, the writing to the protected bit occurs after the window has closed, and so there is effectively no change in the status of the protected bit. In Example 5, the second write to TA occurs 4 machine cycles after the first write, therefore the timed access window is not opened at all, and the write to the protected bit fails.

#### 24 ANALOG-TO-DIGITAL CONVERTER

The ADC contains a DAC which converts the contents of a successive approximation register to a voltage (VDAC) which is compared to the analog input voltage (Vin). The output of the comparator is fed to the successive approximation control logic which controls the successive approximation register. A conversion is initiated by setting ADCS in the ADCCON register. There are two triggering methods by ADC to start conversion, either by purely software start or external pin STADC triggering. The software start mode is used to trigger ADC conversion regardless of ADCCON.5 (ADCEX) bit is set or cleared. A conversion will start simply by setting the ADCCON.3 (ADCS) bit. As for the external STADC pin triggering mode, ADCCON.5 (ADCEX) bit has to be set and a rise edge pulse has to apply to STADC pin to trigger the ADC conversion. For the rising edge triggering method, a minimum of at least 2 machine cycles symmetrical pulse is required.

The low-to-high transition of STADC is recognized at the end of a machine cycle, and the conversion commences at the beginning of the next cycle. When a conversion is initiated by software, the conversion starts at the beginning of the machine cycle which follows the instruction that sets ADCS. ADCS is actually implemented with tpw flip-flops: a command flip-flop which is affected by set operations, and a status flag which is accessed during read operations.

The next two machine cycles are used to initiate the converter. At the end of the first cycle, the ADCS status flag is set end a value of "1" will be returned if the ADCS flag is read while the conversion is in progress. Sampling of the analog input commences at the end of the second cycle.

During the next eight machine cycles, the voltage at the previously selected pin of one of analog input pin is sampled, and this input voltage should be stable in order to obtain a useful sample. In any event, the input voltage slew rate must be less than 10V/ms in order to prevent an undefined result.

The successive approximation control logic first sets the most significant bit and clears all other bits in the successive approximation register (10 0000 0000b). The output of the DAC (50% full scale) is compared to the input voltage Vin. If the input voltage is greater than VDAC, then the bit remains set; otherwise if is cleared.

The successive approximation control logic now sets the next most significant bit (11 0000 0000b or 01 0000 0000b, depending on the previous result), and the VDAC is compared to Vin again. If the input voltage is greater then VDAC, then the bit remains set; otherwise it is cleared. This process is repeated until all ten bits have been tested, at which stage the result of the conversion is held in the successive approximation register. The conversion takes four machine cycles per bit.

The end of the 10-bit conversion is flagged by control bit ADCCON.4 (ADCI). The upper 8 bits of the result are held in special function register ADCH, and the two remaining bits are held in ADCCON.7 (ADC.1) and ADCCON.6 (ADC.0). The user may ignore the two least significant bits in ADCCON and use the ADC as an 8-bit converter (8 upper bits in ADCH). In any event, the total actual conversion time is 52 machine cycles. ADCI will be set and the ADCS status flag will be reset 52 cycles after the ADCS is set. Control bits ADCCON.0 and ADCCON.1 are used to control an analog multiplexer which selects one of 4 analog channels. An ADC conversion in progress is unaffected by an external or software ADC start. The result of a completed conversion remains unaffected provided ADCI = logic 1; a new ADC conversion already in progress is aborted when the idle or power down mode is entered. The result of a completed conversion (ADCI = logic 1) remains unaffected when entering the idle mode.

#### 25.2 The I2C Control Registers:

The I2C has 1 control register (I2CON) to control the transmit/receive flow, 1 data register (I2DAT) to buffer the Tx/Rx data, 1 status register (I2STATUS) to catch the state of Tx/Rx, recognizable slave address register for slave mode use and 1 clock rate control block for master mode to generate the variable baud rate.

#### 25.2.1 The Address Registers, I2ADDR

I2C port is equipped with one slave address register. The contents of the register are irrelevant when I2C is in master mode. In the slave mode, the seven most significant bits must be loaded with the MCU's own slave address. The I2C hardware will react if the contents of I2ADDR are matched with the received slave address.

The I2C ports support the "General Call" function. If the GC bit is set the I2C port1 hardware will respond to General Call address (00H). Clear GC bit to disable general call function.

When GC bit is set, the I2C is in Slave mode, it can be received the general call address by 00H after Master send general call address to I2C bus, then it will follow status of GC mode. If it is in Master mode, the AA bit must be cleared when it will send general call address of 00H to I2C bus.

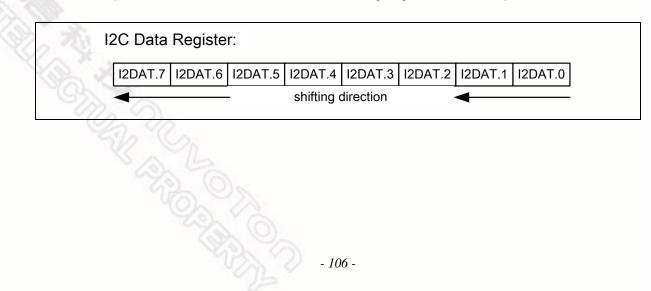

#### 25.2.2 The Data Register, I2DAT

This register contains a byte of serial data to be transmitted or a byte which has just been received. The CPU can read from or write to this 8-bit directly addressable SFR while it is not in the process of shifting a byte. This occurs when SIO is in a defined state and the serial interrupt flag (SI) is set. Data in I2DAT remains stable as long as SI bit is set. While data is being shifted out, data on the bus is simultaneously being shifted in; I2DAT always contains the last data byte present on the bus. Thus, in the event of arbitration lost, the transition from master transmitter to slave receiver is made with the correct data in I2DAT.

I2DAT and the acknowledge bit form a 9-bit shift register, the acknowledge bit is controlled by the SIO hardware and cannot be accessed by the CPU. Serial data is shifted through the acknowledge bit into I2DAT on the rising edges of serial clock pulses on the SCL line. When a byte has been shifted into I2DAT, the serial data is available in I2DAT, and the acknowledge bit (ACK or NACK) is returned by the control logic during the ninth clock pulse. Serial data is shifted out from I2DAT on the falling edges of SCL clock pulses, and is shifted into I2DAT on the rising edges of SCL clock pulses.

### nuvoTon

- 110 -

# nuvoTon

#### Continued

| BIT | NAME  | FUNCTION                         |  |

|-----|-------|----------------------------------|--|

| 3   | -     | Reserved.                        |  |

| 2   | -     | Reserved.                        |  |

| 1   | Fosc1 | CPU Oscillator Type Select bit 1 |  |

| 0   | Fosc0 | CPU Oscillator Type Select bit 0 |  |

#### Oscillator Configuration bits:

| FOSC1 | FOSC0 | OSC SOURCE                   |

|-------|-------|------------------------------|

| 0     | 0     | 4MHz ~ 20MHz crystal         |

| 0     | 1     | Internal RC Oscillator       |

| 1     | 0     | Reserved                     |

| 1     | 1     | External Oscillator in XTAL1 |

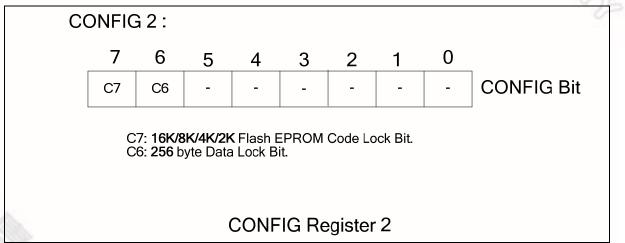

#### 27.2 CONFIG2

#### C7: 16K/8K/4K/2K Flash EPROM Lock bit

This bit is used to protect the customer's program code. It may be set after the programmer finishes the programming and verifies sequence. Once this bit is set to logic 0, both the Flash EPROM data and CONFIG Registers can not be accessed again.

#### C6: 256 byte Data Flash EPROM Lock bit

This bit is used to protect the customer's data code. It may be set after the programmer finishes the programming and verifies sequence. Once this bit is set to logic 0, both the data Flash EPROM and CONFIG Registers can not be accessed again.

|       |       | 335                                                                                                                                                         |

|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT 7 | BIT 6 | FUNCTION DESCRIPTION                                                                                                                                        |

| 1     | 1     | Both security of <b>16KB/8KB/4KB/2KB</b> program code and <b>256</b> Bytes data area are unlocked. They can be erased, programmed or read by Writer or ICP. |

| 0     | 1     | The <b>16KB/8KB/4KB/2KB</b> program code area is locked. It can't be read by Writer or ICP.                                                                 |

| 1     | 0     | Don't support (Invalid).                                                                                                                                    |

| 0     | 0     | Both security of <b>16KB/8KB/4KB/2KB</b> program code and <b>256</b> Bytes data area are locked. They can't be read by Writer or ICP.                       |