Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 20MHz                                                                                  |

| Connectivity               | I <sup>2</sup> C, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT                                        |

| Number of I/O              | 18                                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | 256 x 8                                                                                |

| RAM Size                   | 256 x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                            |

| Data Converters            | A/D 4x10b                                                                              |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

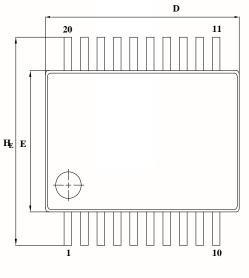

| Mounting Type              | Surface Mount                                                                          |

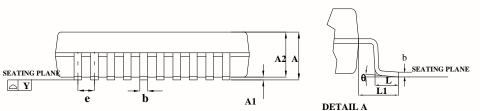

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                         |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/n79e824arg |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Continued

| BIT | NAME | FUNCTION                                                                                                                                                                                                                                                                  |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | TF0  | Timer 0 Overflow Flag. This bit is set when Timer 0 overflows. It is cleared automatically when the program does a timer 0 interrupt service routine. Software can also set or clear this bit.                                                                            |

| 4   | TR0  | Timer 0 Run Control. This bit is set or cleared by software to turn timer/counter on or off.                                                                                                                                                                              |

| 3   | IE1  | Interrupt 1 Edge Detect Flag: Set by hardware when an edge/level is detected on $\overline{\text{INT1}}$ . This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the inverse of the pin. |

| 2   | IT1  | Interrupt 1 Type Control. Set/cleared by software to specify falling edge/ low level triggered external inputs.                                                                                                                                                           |

| 1   | IE0  | Interrupt 0 Edge Detect Flag. Set by hardware when an edge/level is detected on $\overline{\rm INT0}$ . This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the inverse of the pin.    |

| 0   | IT0  | Interrupt 0 Type Control: Set/cleared by software to specify falling edge/ low level triggered external inputs.                                                                                                                                                           |

#### TIMER MODE CONTROL

| Bit: | 7      | 6                | 5  | 4  | 3      | 2                | 1  | 0  |

|------|--------|------------------|----|----|--------|------------------|----|----|

|      | GATE   | $C/\overline{T}$ | M1 | MO | GATE   | $C/\overline{T}$ | M1 | MO |

|      | TIMER1 |                  |    |    | TIMER0 |                  |    |    |

Mnemonic: TMOD

| BIT | NAME | FUNCTION                                                                                                                                                                                                                                                     |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | GATE | Gating control: When this bit is set, Timer/counter 1 is enabled only while the $\overline{INT1}$ pin is high and the TR1 control bit is set. When cleared, the $\overline{INT1}$ pin has no effect, and Timer 1 is enabled whenever TR1 control bit is set. |

| 6   | C/T  | Timer or Counter Select: When clear, Timer 1 is incremented by the internal clock. When set, the timer counts falling edges on the T1 pin.                                                                                                                   |

| 5   | M1   | Timer 1 mode select bit 1. See table below.                                                                                                                                                                                                                  |

| 4   | MO   | Timer 1 mode select bit 0. See table below.                                                                                                                                                                                                                  |

| 3   | GATE | Gating control: When this bit is set, Timer/counter 0 is enabled only while the $\overline{INT0}$ pin is high and the TR0 control bit is set. When cleared, the $\overline{INT0}$ pin has no effect, and Timer 0 is enabled whenever TR0 control bit is set. |

| 2   | C/T  | Timer or Counter Select: When clear, Timer 0 is incremented by the internal clock. When set, the timer counts falling edges on the T0 pin.                                                                                                                   |

| 1   | M1   | Timer 0 mode select bit 1. See table below.                                                                                                                                                                                                                  |

| 0   | M0   | Timer 0 mode select bit 0. See table below.                                                                                                                                                                                                                  |

Address: 89h

| SERIAL<br>Bit: | DIVM.[7:0<br>L <b>PORT C</b><br>7<br>SM0/FE | ONTROL                                                                                                                                                                                                                   |                                                                                              | s clock divid                                                                                    | er of uC R                                                                                |                                                                                  | FUNCTION                                                            |                                                                                                                                 |  |  |  |  |  |  |  |

|----------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Bit:           | 7                                           | 6                                                                                                                                                                                                                        |                                                                                              | ] The DIVM register is clock divider of uC. Refer OSCILLATOR chapter.                            |                                                                                           |                                                                                  |                                                                     |                                                                                                                                 |  |  |  |  |  |  |  |

| Mnemo          |                                             |                                                                                                                                                                                                                          |                                                                                              | ONTROL                                                                                           |                                                                                           |                                                                                  |                                                                     |                                                                                                                                 |  |  |  |  |  |  |  |

| Mnemo          | SM0/FE                                      | 0144                                                                                                                                                                                                                     | 5                                                                                            | 4                                                                                                | 3                                                                                         | 2                                                                                | 1                                                                   | 0                                                                                                                               |  |  |  |  |  |  |  |

| r              |                                             | SM1                                                                                                                                                                                                                      | SM2                                                                                          | REN                                                                                              | TB8                                                                                       | RB8                                                                              | ТІ                                                                  | RI                                                                                                                              |  |  |  |  |  |  |  |

|                | nic: SCO                                    |                                                                                                                                                                                                                          |                                                                                              |                                                                                                  |                                                                                           |                                                                                  |                                                                     |                                                                                                                                 |  |  |  |  |  |  |  |

| BIT            | NAME                                        | FUNCTION                                                                                                                                                                                                                 |                                                                                              |                                                                                                  |                                                                                           |                                                                                  |                                                                     |                                                                                                                                 |  |  |  |  |  |  |  |

| 7              | SM0/FE                                      | Serial port mode select bit 0 or Framing Error Flag: The SMOD0 b                                                                                                                                                         |                                                                                              |                                                                                                  |                                                                                           |                                                                                  |                                                                     |                                                                                                                                 |  |  |  |  |  |  |  |

| 6              | SM1                                         | Serial Port                                                                                                                                                                                                              | mode sele                                                                                    | ct bit 1. See                                                                                    | table below                                                                               | V.                                                                               | 3                                                                   | 20%                                                                                                                             |  |  |  |  |  |  |  |

| 5              | SM2                                         | communica<br>will not be<br>then RI will<br>bit controls<br>12 clock of<br>to 1, the se                                                                                                                                  | ation feature<br>activated if<br>not be action<br>the serial<br>the oscillate<br>the clock b | e in mode 2<br>f the receive<br>ivated if a va<br>port clock. I<br>tor. This give<br>ecome divid | and 3. In r<br>d 9th data<br>lid stop bit<br>f set to 0, t<br>es compatil<br>e by 4 of th | node 2 or 3,<br>bit (RB8) is<br>was not rece<br>hen the seria<br>bility with the | if SM2 is s<br>0. In mode<br>eived. In m<br>al port run<br>standard | e multiprocesses<br>set to 1, then F<br>e 1, if SM2 =<br>node 0, the SM<br>s at a divide b<br>8052. When so<br>results in faste |  |  |  |  |  |  |  |

| 4              | REN                                         | synchronous serial communication.<br>Receive enable:<br>0: Disable serial reception.<br>1: Enable serial reception.                                                                                                      |                                                                                              |                                                                                                  |                                                                                           |                                                                                  |                                                                     |                                                                                                                                 |  |  |  |  |  |  |  |

| 3              | TB8                                         | This is the 9th bit to be transmitted in modes 2 and 3. This bit is set and cleared b software as desired.                                                                                                               |                                                                                              |                                                                                                  |                                                                                           |                                                                                  |                                                                     |                                                                                                                                 |  |  |  |  |  |  |  |

| 2              | RB8                                         |                                                                                                                                                                                                                          |                                                                                              |                                                                                                  |                                                                                           | ata bit. In mode 1, if SM2 = 0, RB8 is the no function.                          |                                                                     |                                                                                                                                 |  |  |  |  |  |  |  |

| 1              | ТІ                                          | Transmit interrupt flag: This flag is set by hardware at the end of the 8th bit time in mode 0, or at the beginning of the stop bit in all other modes during serial transmission. This bit must be cleared by software. |                                                                                              |                                                                                                  |                                                                                           |                                                                                  |                                                                     |                                                                                                                                 |  |  |  |  |  |  |  |

| 0              | RI                                          | mode 0, o                                                                                                                                                                                                                | r halfway t<br>However th                                                                    | hrough the                                                                                       | stop bits t                                                                               | ime in the c                                                                     | other mode                                                          | e 8th bit time i<br>es during seria<br>can be cleare                                                                            |  |  |  |  |  |  |  |

| BIT                | NAME                           |           |                                                                                                                |                 | FUNCTION      | 1            |                              |             |  |  |  |  |  |

|--------------------|--------------------------------|-----------|----------------------------------------------------------------------------------------------------------------|-----------------|---------------|--------------|------------------------------|-------------|--|--|--|--|--|

|                    |                                | Output er | nable:                                                                                                         | 6               | n. A          | 5            |                              |             |  |  |  |  |  |

| 2                  | OE2                            |           |                                                                                                                |                 |               |              | pin if the co                |             |  |  |  |  |  |

|                    |                                | enable    | ed (CE2 = 1                                                                                                    | ). This outpι   | it is asynchr | onous to the | e CPU clock.                 |             |  |  |  |  |  |

|                    | 000                            |           | tor output:                                                                                                    |                 |               | XX.          |                              |             |  |  |  |  |  |

| 1                  | CO2                            |           | Synchronized to the CPU clock to allow reading by software. Cleared when the comparator is disabled (CE2 = 0). |                 |               |              |                              |             |  |  |  |  |  |

|                    |                                | Compara   | tor interrupt                                                                                                  | errupt flag:    |               |              |                              |             |  |  |  |  |  |

| 0                  | CMF2                           |           |                                                                                                                |                 |               |              | tput CO2 ch                  |             |  |  |  |  |  |

|                    |                                |           |                                                                                                                |                 |               |              | nd of suffic<br>d (CE2 = 0). |             |  |  |  |  |  |

| PORT               | 0 OUTPUT                       | MODE 1    |                                                                                                                |                 |               |              | N.                           | 202         |  |  |  |  |  |

| Bit:               | 7                              | 6         | 5                                                                                                              | 4               | 3             | 2            | 1 2                          | 0           |  |  |  |  |  |

|                    | P0M1.7                         | P0M1.6    | P0M1.5                                                                                                         | P0M1.4          | P0M1.3        | P0M1.2       | P0M1.1                       | P0M1.0      |  |  |  |  |  |

| Mnem               | onic: P0M1                     |           |                                                                                                                |                 |               |              | A                            | Address: B1 |  |  |  |  |  |

| BIT                | NAME                           |           |                                                                                                                |                 | FUNCTION      | N            |                              | 19          |  |  |  |  |  |

| 7-0                | P0M1.[7:0]                     | To contr  | ol the outpu                                                                                                   | t configuration | on of P0 bits | [7:0]        |                              |             |  |  |  |  |  |

| PORT               | 0 OUTPUT                       | MODE 2    |                                                                                                                |                 |               |              |                              |             |  |  |  |  |  |

| Bit:               | 7                              | 6         | 5                                                                                                              | 4               | 3             | 2            | 1                            | 0           |  |  |  |  |  |

|                    | P0M2.7                         | P0M2.6    | P0M2.5                                                                                                         | P0M2.4          | P0M2.3        | P0M2.2       | P0M2.1                       | P0M2.0      |  |  |  |  |  |

| Mnem               | onic: P0M2                     |           |                                                                                                                |                 |               |              | A                            | Address: B2 |  |  |  |  |  |

| BIT                | NAME                           |           |                                                                                                                |                 | FUNCTIO       | N            |                              |             |  |  |  |  |  |

| 7-0                | P0M2.[7:0]                     | To contr  | ol the outpu                                                                                                   | t configuration | on of P0 bits | [7:0]        |                              |             |  |  |  |  |  |

| PORT               | 1 OUTPUT                       | MODE 1    |                                                                                                                |                 |               |              |                              |             |  |  |  |  |  |

| Bit:               | 7                              | 6         | 5                                                                                                              | 4               | 3             | 2            | 1                            | 0           |  |  |  |  |  |

|                    | P1M1.7                         | P1M1.6    | -                                                                                                              | P1M1.4          | P1M1.3        | P1M1.2       | P1M1.1                       | P1M1.0      |  |  |  |  |  |

|                    | onic: P1M1                     |           |                                                                                                                |                 |               |              | A                            | Address: B3 |  |  |  |  |  |

| Mnem               | OTIC. F HVH                    |           |                                                                                                                |                 |               |              |                              |             |  |  |  |  |  |

| Mnem<br>BIT        | NAME                           |           |                                                                                                                |                 | FUNCTIO       | N            |                              |             |  |  |  |  |  |

|                    |                                | To contro | ol the outpu                                                                                                   | t configuratio  |               |              |                              |             |  |  |  |  |  |

| <b>BIT</b><br>7-0  | NAME                           | 2         | ol the outpu                                                                                                   | t configuratio  |               |              |                              |             |  |  |  |  |  |

| <b>BIT</b><br>7-0  | <b>NAME</b><br>P1M1.[7:0]      | 2         | ol the outpu                                                                                                   | t configuratio  |               |              | 1                            | 0           |  |  |  |  |  |

| BIT<br>7-0<br>PORT | NAME<br>P1M1.[7:0]<br>1 OUTPUT | MODE 2    |                                                                                                                |                 | on of P1 bits | 5 [7:0]      | 1<br>P1M2.1                  | 0<br>P1M2.0 |  |  |  |  |  |

Publication Release Date: Aug 05, 2010 Revision A02

| Continue | d |

|----------|---|

|          | BIT | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 5   | STA  | <ul> <li>The START flag.</li> <li>0: The STA bit is reset, no START condition or repeated START condition will be generated.</li> <li>1: The STA bit is set to enter a master mode. The I2C hardware checks the status of I2C bus and generates a START condition if the bus is free. If bus is not free, then I2C waits for a STOP condition and generates a START condition after a delay. If STA is set while I2C is already in a master mode and one or more bytes are transmitted or received, I2C transmits a repeated START condition. STA may be set any time. STA may also be set when I2C interface is an addressed slave mode.</li> </ul>                                                                                                                                  |

|          | 4   | STO  | The bit STO bit is set while I2C is in a master mode. A STOP condition is transmitted to the I2C bus. When the STOP condition is detected on the bus, the I2C hardware clears the STO flag. In a slave mode, the STO flag may be set to recover from a bus error condition. In this case, no STOP condition is transmitted to the I2C bus. However, the I2C hardware behaves as if a STOP condition has been received and it switches to the not addressable slave receiver mode. The STO flag is automatically cleared by hardware. If the STA and STO bits are both set, then a STOP condition is transmitted to the I2C bus if I2C is in a master mode (in a slave mode, I2C generates an internal STOP condition which is not transmitted). I2C then transmits a START condition. |

|          | 3   | SI   | <ul> <li>0: When the SI flag is reset, no serial interrupt is requested, and there is no stretching on the serial clock on the SCL line.</li> <li>1: When a new SIO state is present in the I2STATUS register, the SI flag is set by hardware, and, if the EA and EI2C(EIE.0) bits are both set, an I2C interrupt is requested when SI is set. Only one state that does not cause SI is set is I2STATUS=F8H, which indicates that no relevant state information is available. When SI is set, the low level cycle of the serial clock on the SCL line is stretched, and the serial transfer is suspended. The high level cycle on the SCL line is unaffected by the serial interrupt flag. SI must be cleared by software.</li> </ul>                                                 |

| Rel ar 7 | 2   | AA   | <ul> <li>The Assert Acknowledge Flag</li> <li>0: A not acknowledge (high level to SDA) will be returned during the acknowledge clock pulse on SCL when: 1) A data has been received while SIO is in the master receiver mode. 2) A data byte has been received while SIO is in the addressed slave receiver mode.</li> <li>1: An acknowledge (low level to SDA) will be returned during the acknowledge clock pulse on the SCL line when: 1) The own slave address has been received. 2) A data byte has been receiver wode. 3) A data byte has been received while SIO is in the master receiver mode. 4) The General Call address has been received while the general call bit (GC) in I2ADDR is set.</li> </ul>                                                                    |

|          | 1   | - 4  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          | 0   | -    | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### N79E825A/824A/823A/822A Data Sheet

### nuvoTon

| BIT | NAME  |                         |                                                                                                                                           |                                            | FUNCTION                                                                                                         |                                                    |                          |  |  |  |  |

|-----|-------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------|--|--|--|--|

| 7   | WDRUN | 0: The Wa<br>1: The Wa  | •                                                                                                                                         | • •                                        |                                                                                                                  |                                                    |                          |  |  |  |  |

| 6   | -     | Reserved                | Reserved.                                                                                                                                 |                                            |                                                                                                                  |                                                    |                          |  |  |  |  |

| 5   | WD1   |                         | Timer Time-out Select bits. These bits determine the time-out period chdog timer. The reset time-out period is 512 clocks longer than the |                                            |                                                                                                                  |                                                    |                          |  |  |  |  |

|     |       | of the wat<br>watchdog  |                                                                                                                                           |                                            | e reset time-out period                                                                                          | I IS 512 CIOCKS longer                             | than the                 |  |  |  |  |

|     |       |                         | WD1                                                                                                                                       | WD0                                        | Interrupt time-out                                                                                               | Reset time-out                                     |                          |  |  |  |  |

| 4   | WD0   |                         | 0                                                                                                                                         | 0                                          | 2 <sup>17</sup>                                                                                                  | 2 <sup>17</sup> + 512                              |                          |  |  |  |  |

|     |       |                         | 0                                                                                                                                         | 1                                          | 2 <sup>20</sup>                                                                                                  | 2 <sup>20</sup> + 512                              |                          |  |  |  |  |

|     |       |                         | 1                                                                                                                                         | 0                                          | 2 <sup>23</sup>                                                                                                  | 2 <sup>23</sup> + 512                              | 6                        |  |  |  |  |

|     |       |                         | 1                                                                                                                                         | 1                                          | 2 <sup>26</sup>                                                                                                  | 2 <sup>26</sup> + 512                              | No.                      |  |  |  |  |

| 3   | WDIF  | has ela<br>1: If the w  | apsed. T<br>atchdog                                                                                                                       | his bit m<br>interrup                      | nabled, then this bit in<br>hust be cleared by soft<br>ot is enabled, hardwar<br>has occurred.                   | ware.                                              | NY2                      |  |  |  |  |

| 2   | WTRF  | can rea<br>bit. Thi     | are will s<br>ad it but<br>is bit hel                                                                                                     | set this b<br>must c<br>lps softw          | ag<br>bit when the watchdog<br>lear it manually. A po<br>vare in determining the<br>will have no affect on t     | wer-fail reset will also<br>e cause of a reset. If | clear the                |  |  |  |  |

| 1   | EWRST | 0: Disable<br>1: Enable |                                                                                                                                           | •                                          |                                                                                                                  |                                                    |                          |  |  |  |  |

| 0   | WDCLR | resetting<br>EWRST b    | elps in p<br>the wat<br>before tir<br>er that a                                                                                           | butting th<br>tchdog<br>me-out v<br>watchd | he watchdog timer inte<br>timer before a time-o<br>vill cause an interrupt,<br>og timer reset will be g<br>ware. | out occurs. Failing t<br>if EWDI (EIE.4) is se     | to set the<br>t, and 512 |  |  |  |  |

The WDCON SFR is set to 0x000000B on a reset. WTRF (WDCON.2) is set to a 1 on a Watchdog timer reset, but to a 0 on power on/down resets. WTRF (WDCON.2) is not altered by an external reset. EWRST (WDCON.1) is set to 0 on a Power-on reset, reset pin reset, and Watch Dog Timer reset.

All the bits in this SFR have unrestricted read access. WDRUN, WD0, WD1, EWRST, WDIF and WDCLR require Timed Access procedure to write. The remaining bits have unrestricted write accesses. Please refer TA register description.

### N79E825A/824A/823A/822A Data Sheet

| AAI            | DR1             | AAD    | DR0                                                                                                                         |                                                                                     | SELECT                                                                                                             | D ANALOG                                            | INPUT CHA | ANNEL |        |        |  |  |

|----------------|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------|-------|--------|--------|--|--|

|                | 0               | (      | 0                                                                                                                           | AD0 (P0.3)                                                                          |                                                                                                                    |                                                     |           |       |        |        |  |  |

|                | 0               |        | 1                                                                                                                           | AD1 (P0.4)                                                                          |                                                                                                                    |                                                     |           |       |        |        |  |  |

|                | 1               | (      | 0                                                                                                                           | AD2 (P0.5)                                                                          |                                                                                                                    |                                                     |           |       |        |        |  |  |

|                | 1               |        | 1                                                                                                                           |                                                                                     |                                                                                                                    | AD3 (                                               | P0.6)     | 125   |        |        |  |  |

| ADC            | CONV            | ERTE   |                                                                                                                             | T HIGH REG                                                                          | SISTER                                                                                                             |                                                     | -UN       | 0     |        |        |  |  |

| Bit:           | 7               |        | 6                                                                                                                           | 5                                                                                   | 4                                                                                                                  | 3                                                   | 2         | 21 6  | 0      |        |  |  |

|                | ADC             | .9     | ADC.8                                                                                                                       | ADC.7                                                                               | ADC.6                                                                                                              | ADC.5                                               | ADC.4     | ADC.3 | AD     | C.2    |  |  |

| Mnemonic: ADCH |                 | •      |                                                                                                                             | •                                                                                   | •                                                                                                                  |                                                     | 2         | Addre | ss: E2 |        |  |  |

|                |                 |        | FUNCT                                                                                                                       | ION                                                                                 |                                                                                                                    |                                                     |           | 9     | 0      | 2      |  |  |

| 7-0            | ADC             | .[9:2] | The AD                                                                                                                      | C conversior                                                                        | n result.                                                                                                          |                                                     |           |       | - 22   | 20     |  |  |

| INTE           |                 |        | BLE REG                                                                                                                     | ISTER 1                                                                             |                                                                                                                    |                                                     |           |       | 2      | 525    |  |  |

| Bit:           | 7               |        | 6                                                                                                                           | 5                                                                                   | 4                                                                                                                  | 3                                                   | 2         | 1     | 0      |        |  |  |

|                | -               |        | -                                                                                                                           | EPWM                                                                                | EWDI                                                                                                               | EC2                                                 | EC1       | EKB   | El2    | 2C     |  |  |

| Mnem           | nonic: I        | EIE    |                                                                                                                             | •                                                                                   |                                                                                                                    |                                                     |           |       | Addre  | ss: E8 |  |  |

| BIT            | NA              | ME     |                                                                                                                             | FUNCTION                                                                            |                                                                                                                    |                                                     |           |       |        |        |  |  |

| 7              | -               |        |                                                                                                                             |                                                                                     |                                                                                                                    |                                                     |           |       |        |        |  |  |

|                | -               |        | Reserve                                                                                                                     | ed.                                                                                 |                                                                                                                    |                                                     |           |       |        |        |  |  |

| 5 EPWM 0:      |                 |        | Reserve<br>Reserve                                                                                                          |                                                                                     |                                                                                                                    |                                                     |           |       |        |        |  |  |

| -              | -               | /M     | Reserve<br>0: Disat                                                                                                         |                                                                                     | •                                                                                                                  |                                                     | •         |       |        |        |  |  |

| -              | -               |        | Reserve<br>0: Disat<br>1: Enab<br>0: Disat                                                                                  | ed.<br>ble PWM Inte                                                                 | rrupt when e<br>g Timer Inter                                                                                      | external brai                                       | •         |       |        |        |  |  |

| 5              | -<br>EPW        | DI     | Reserve<br>0: Disat<br>1: Enab<br>0: Disat<br>1: Enab<br>0: Disat                                                           | ed.<br>ble PWM Inte<br>ble PWM Inte<br>ble Watchdog                                 | rrupt when e<br>g Timer Inter<br>I Timer Inter<br>tor 2 Interrup                                                   | external brak<br>rrupt.<br>rupt.<br>pt.             | •         |       |        |        |  |  |

| 5              | -<br>EPW<br>EWD | DI     | Reserve<br>0: Disat<br>1: Enab<br>0: Disat<br>1: Enab<br>0: Disat<br>1: Enab<br>0: Disat                                    | ed.<br>ble PWM Inte<br>ble PWM Inte<br>ble Watchdog<br>ble Watchdog<br>ble Compara  | rrupt when e<br>g Timer Inter<br>Timer Inter<br>tor 2 Interrup<br>or 2 Interrup<br>tor 1 Interrup                  | external brai<br>rupt.<br>rupt.<br>ot.<br>ot.<br>t. | •         |       |        |        |  |  |

| 5<br>4<br>3    | -<br>EPW<br>EWD | DI     | Reserve<br>0: Disat<br>1: Enab<br>0: Disat<br>1: Enab<br>0: Disat<br>1: Enab<br>0: Disat<br>1: Enab<br>0: Disat<br>0: Disat | ed.<br>ble PWM Inte<br>ble PWM Inte<br>ble Watchdog<br>ble Comparat<br>ble Comparat | rrupt when e<br>g Timer Inter<br>Timer Inter<br>tor 2 Interrup<br>or 2 Interrup<br>tor 1 Interrup<br>or 1 Interrup | external brai<br>rupt.<br>rupt.<br>ot.<br>ot.<br>t. | •         |       |        |        |  |  |

| EXTE | NDED INTEI | RRUPT PRI   | ORITY         |              |              |                |                |              |

|------|------------|-------------|---------------|--------------|--------------|----------------|----------------|--------------|

| Bit: | 7          | 6           | 5             | 4            | 3            | 2              | 1              | 0            |

|      | -          | -           | PPWM          | PWDI         | PC2          | PC1            | PKB            | Pl2          |

| Mnem | onic: IP1  |             |               |              | NON.         | 1 - C          |                | Address: F8h |

| BIT  | NAME       |             |               |              | FUNCTIC      | N N            |                |              |

| 7    | -          | Reserved    |               |              | X            | 5 °            | 250            |              |

| 6    | -          | Reserved    |               |              |              | NOY.           | de la          |              |

| 5    | PPWM       | 1: To set i | interrupt pri | ority of PWI | Vis externa  | l brake is hi  | igher priority | level.       |

| 4    | PWDI       | 1: To set i | nterrupt pri  | ority of Wat | chdog is hi  | gher priority  | level.         | 126          |

| 3    | PC2        | 1: To set i | interrupt pri | ority of Con | nparator 2 i | s higher prie  | ority level.   | 16           |

| 2    | PC1        | 1: To set i | nterrupt pri  | ority of Con | nparator 1 i | s higher prie  | ority level.   | 200          |

| 1    | PKB        | 1: To set i | nterrupt pri  | ority of Key | pad is high  | er priority le | vel.           | 0200         |

| 0    | PI2        | 1: To set i | nterrupt pri  | ority of I2C | is higher pi | iority level.  |                | ~ XD (C      |

#### Continued

| OP-CODE               | HEX CODE | BYTES | N79E825<br>SERIES<br>MACHINE<br>CYCLE | N79E825<br>SERIES<br>CLOCK<br>CYCLES | 8032<br>CLOCK<br>CYCLES | N79E825<br>SERIES VS.<br>8032 SPEED<br>RATIO |

|-----------------------|----------|-------|---------------------------------------|--------------------------------------|-------------------------|----------------------------------------------|

| MOV @R1, A            | F7       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| MOV @R0, direct       | A6       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV @R1, direct       | A7       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV @R0, #data        | 76       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV @R1, #data        | 77       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, A         | F5       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, R0        | 88       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, R1        | 89       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, R2        | 8A       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, R3        | 8B       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, R4        | 8C       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, R5        | 8D       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, R6        | 8E       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, R7        | 8F       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, @R0       | 86       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, @R1       | 87       | 2     | 2                                     | 8                                    | 12                      | 1.5                                          |

| MOV direct, direct    | 85       | 3     | 3                                     | 12                                   | 24                      | 2                                            |

| MOV direct, #data     | 75       | 3     | 3                                     | 12                                   | 24                      | 2                                            |

| MOV DPTR, #data<br>16 | 90       | 3     | 3                                     | 12                                   | 24                      | 2                                            |

| MOVC A,<br>@A+DPTR    | 93       | 1     | 2                                     | 8                                    | 24                      | 3                                            |

| MOVC A, @A+PC         | 83       | 1     | 2                                     | 8                                    | 24                      | 3                                            |

| MOVX A, @R0           | E2       | 1     | 2 - 9                                 | 8 - 36                               | 24                      | 3 - 0.66                                     |

| MOVX A, @R1           | E3       | 1     | 2 - 9                                 | 8 - 36                               | 24                      | 3 - 0.66                                     |

| MOVX A, @DPTR         | E0       | 1     | 2 - 9                                 | 8 - 36                               | 24                      | 3 - 0.66                                     |

| MOVX @R0, A           | F2       | 1     | 2 - 9                                 | 8 - 36                               | 24                      | 3 - 0.66                                     |

| MOVX @R1, A           | F3       | 1     | 2 - 9                                 | 8 - 36                               | 24                      | 3 - 0.66                                     |

| MOVX @DPTR, A         | F0       | 1     | 2 - 9                                 | 8 - 36                               | 24                      | 3 - 0.66                                     |

| PUSH direct           | CO       | 2     | 2                                     | 8                                    | 24                      | 3                                            |

| POP direct            | D0       | 2     | 2                                     | 8                                    | 24                      | 3                                            |

| XCH A, R0             | C8       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

| XCH A, R1             | C9       | 1     | 1                                     | 4                                    | 12                      | 3                                            |

machine cycles. This is a 50% reduction in terms of clock periods.

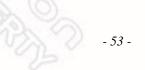

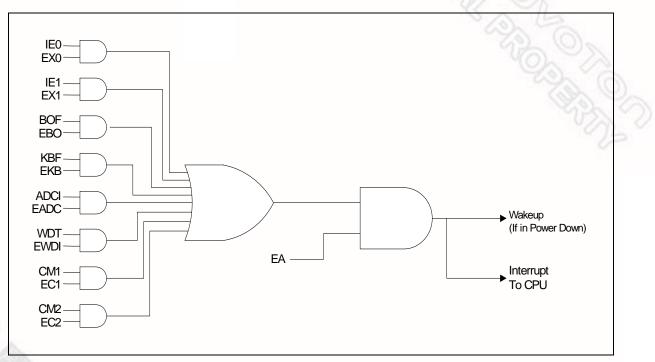

#### **12.4 Interrupt Inputs**

The N79E825 series have 13 interrupts source, and two individual interrupt inputs sources, one is for IE0, IE1, BOF, KBF, WDT, ADC, CMF1 and CMF2, and other is IF0, IF1, RI+TI, SI and BKF. Two interrupt inputs are identical to those present on the standard 80C51 microcontroller as show in below figures.

If an external interrupt is enabled when the N79E825 series are put into Power Down or Idle mode, the interrupt will cause the processor to wake up and resume operation.

### N79E825A/824A/823A/822A Data Sheet

Figure 12-2: Interrupt Sources that cannot wake up from Power Down Mode

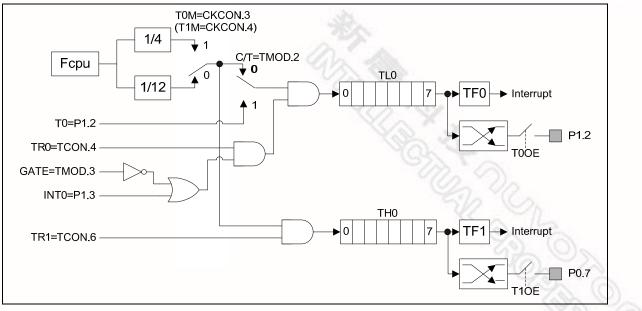

Figure 13-4: Timer/Counter Mode 3

Publication Release Date: Aug 05, 2010 Revision A02

### nuvoton

#### 16.3 MODE 2

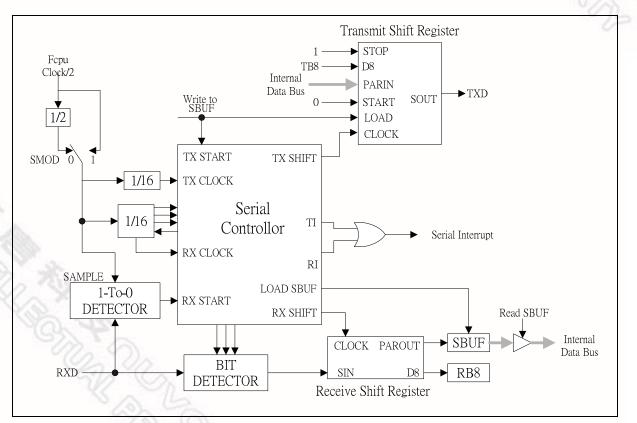

This mode uses a total of 11 bits in asynchronous full-duplex communication. The functional description is shown in the figure below. The frame consists of one start bit (0), 8 data bits (LSB first), a programmable 9th bit (TB8) and a stop bit (0). The 9th bit received is put into RB8. The baud rate is programmable to 1/32 or 1/64 of the oscillator frequency, which is determined by the SMOD bit in PCON SFR. Transmission begins with a write to SBUF. The serial data is brought out on to TxD pin at C1 following the first roll-over of the divide-by-16 counter. The next bit is placed on TxD pin at C1 following the next rollover of the divide-by-16 counter. Thus the transmission is synchronized to the divide-by-16 counter, and not directly to the write to SBUF signal. After all 9 bits of data are transmitted, the stop bit is transmitted. The TI flag is set in the C1 state after the stop bit has been put out on TxD pin. This will be at the 11th rollover of the divide-by-16 counter after a write to SBUF. Reception is enabled only if REN is high. The serial port actually starts the receiving of serial data, with the detection of a falling edge on the RxD pin. The 1-to-0 detector continuously monitors the RxD line, sampling it at the rate of 16 times the selected baud rate. When a falling edge is detected, the divide- by-16 counter is immediately reset. This helps to align the bit boundaries with the rollovers of the divide-by-16 counter. The 16 states of the counter effectively divide the bit time into 16 slices. The bit detection is done on a best of three bases. The bit detector samples the RxD pin, at the 8th, 9th and 10th counter states. By using a majority 2 of 3 voting system, the bit value is selected. This is done to improve the noise rejection feature of the serial port.

Figure 16-3: Serial Port Mode 2

#### **17 TIME ACCESS PROCTECTION**

The N79E825 series have a new feature, like the Watchdog Timer which is a crucial to proper operation of the system. If left unprotected, errant code may write to the Watchdog control bits resulting in incorrect operation and loss of control. In order to prevent this, the N79E825 series have a protection scheme which controls the write access to critical bits. This protection scheme is done using a timed access.

In this method, the bits which are to be protected have a timed write enable window. A write is successful only if this window is active, otherwise the write will be discarded. This write enable window is open for 3 machine cycles if certain conditions are met. After 3 machine cycles, this window automatically closes. The window is opened by writing AAh and immediately 55h to the Timed Access (TA) SFR. This SFR is located at address C7h. The suggested code for opening the timed access window is

| TA | REG | 0C7h      |

|----|-----|-----------|

|    | MOV | TA, #0AAh |

|    | MOV | TA, #055h |

;Define new register TA, located at 0C7h

When the software writes AAh to the TA SFR, a counter is started. This counter waits for 3 machine cycles looking for a write of 55h to TA. If the second write (55h) occurs within 3 machine cycles of the first write (AAh), then the timed access window is opened. It remains open for 3 machine cycles, during which the user may write to the protected bits. Once the window closes the procedure must be repeated to access the other protected bits.

Examples of Timed Assessing are shown below.

| Example 1: Valid a  | ccess             |                                   |

|---------------------|-------------------|-----------------------------------|

| MOV                 | TA, #0AAh         | ;3 M/C Note: M/C = Machine Cycles |

| MOV                 | TA, #055h         | ;3 M/C                            |

| MOV                 | WDCON, #00h       | ;3 M/C                            |

| Example 2: Valid a  | ccess             |                                   |

| MOV                 | TA, #0AAh         | ;3 M/C                            |

| MOV                 | TA, #055h         | ;3 M/C                            |

| NOP                 |                   | ;1 M/C                            |

| SETB                | EWRST             | ;2 M/C                            |

| Example 3: Valid ad | ccess             |                                   |

| MOV                 | TA, #0AAh         | ;3 M/C                            |

| MOV                 | TA, #055h         | ;3 M/C                            |

| ORL                 | WDCON, #00000010B | ;3M/C                             |

| Example 4: Invalid  | access            |                                   |

| MOV                 | TA, #0AAh         | ;3 M/C                            |

| MOV                 | TA, #055h         | ;3 M/C                            |

| NOP                 |                   | ;1 M/C                            |

| NOP                 |                   | ;1 M/C                            |

|                     |                   |                                   |

Publication Release Date: Aug 05, 2010 Revision A02

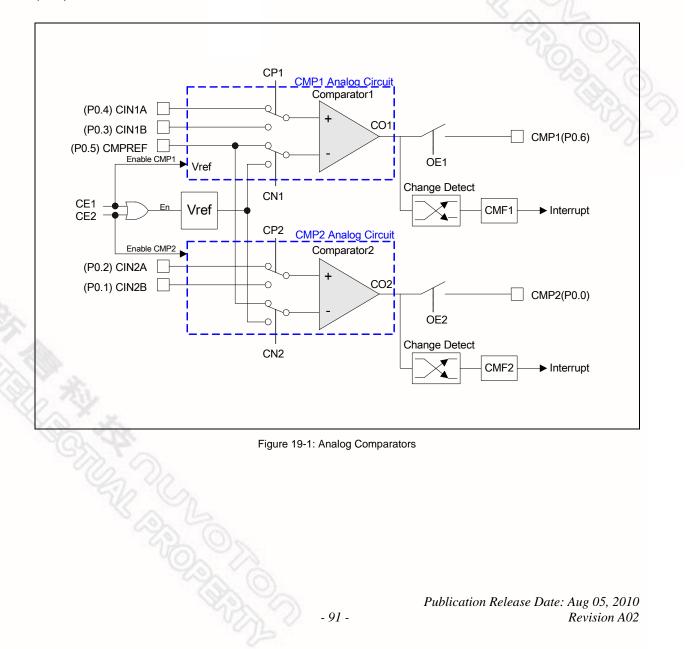

#### **19 ANALOG COMPARATORS**

The N79E825 series are provided two Comparators. Input and output options allow use of the comparators in a number of different Configurations. The Comparator output is a logical one when its positive input is greater than its negative input, otherwise the output is a zero. Each Comparator can be configured to cause to an interrupt when the output value change. The block diagram is as below.

Each Comparator has a control register (CMP1 and CMP2), Both Inputs are CINnA, CINnB, CMPREF and internal reference voltage, and outputs are CMP1 and CMP2 by setting OEn bit. After enable Comparators the Comparator need waited stable time to guarantee Comparator output. If programmer used internal reference voltage, it will be set OEn bit to "1". The value of internal reference voltage (Vref) is 1.19V +/- 10%.

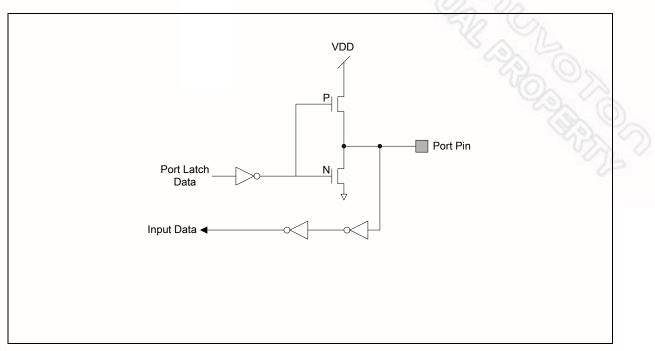

#### 20.3 Push-Pull Output Configuration

nuvoton

The push-pull output mode has two strong pull-up and pull-down structure that support large source and sink current output. It removes "weak" pull-up and "very weak" pull-up resister and remain "strong pull-up resister on quasi-bidirectional output mode. The "strong" pull-up is always turns on when port latch is logic "1" to support source current. The push-pull port configuration is shown in below Figure.

The N79E825 series have three port pins that can't be configured. They are P1.2, P1.3, and P1.5. The port pins P1.2 and P1.3 are configured to open drain outputs. They may be used as inputs by writing ones to their respective port latches.

#### Figure 20-4: Push-Pull Output

#### 20.4 Input Only Configuration

By configure this mode, the ports are only digital input and disable digital output. The N79E825 series can select input pin to Schmitt trigger or TTL level input by PxM1.y and PxM2.y registers.

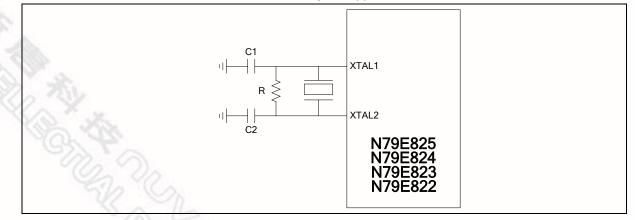

#### 21.2 External Clock Input Option

The clock source pin (XTAL1) is from External Clock Input by FOSC1, FOSC0 = 11H, and frequency range is form 0Hz up to 20MHz. A clock output on P2.0 (XTAL2) may be enabled when External Clock Input is used.

The N79E825 series supports a clock output function when either the on-chip RC oscillator or the external clock input options is selected. This allows external devices to synchronize to the N79E825 serial. When enabled, via the ENCLK bit in the P2M1 register, the clock output appears on the XTAL2/CLKOUT pin whenever the on-chip oscillator is running, including in Idle Mode. The frequency of the clock output is 1/4 of the CPU clock rate. If the clock output is not needed in Idle Mode, it may be turned off prior to entering Idle mode, saving additional power. The clock output may also be enabled when the external clock input option is selected.

#### 21.3 CPU Clock Rate select

The CPU clock of N79E825 series may be selected by the DIVM register. If DIVM = 00H, the CPU clock is running at 4 CPU clock per machine cycle, and without any division from source clock (Fosc). When the DIVM register is set to N value, the CPU clock is divided by 2(DVIM+1), so CPU clock frequency division is from 4 to 512. The user may use this feature to set CPU at a lower speed rate for reducing power consumption. This is very similar to the situation when CPU has entered Idle mode. In addition this frequency division function affect all peripheral timings as they are all sourcing from the CPU clock(Fcpu).

#### 25.2.3 The Control Register, I2CON

The CPU can read from and write to this 8-bit, directly addressable SFR. Two bits are affected by hardware: the SI bit is set when the I2C hardware requests a serial interrupt, and the STO bit is cleared when a STOP condition is present on the bus. The STO bit is also cleared when ENS = "0".

- ENSI Set to enable I2C serial function block. When ENS=1 the I2C serial function enables. The port latches of SDA1 and SCL1 must be set to logic high.

- STA I2C START Flag. Setting STA to logic 1 to enter master mode, the I2C hardware sends a START or repeat START condition to bus when the bus is free.

- STO I2C STOP Flag. In master mode, setting STO to transmit a STOP condition to bus then I2C hardware will check the bus condition if a STOP condition is detected this flag will be cleared by hardware automatically. In a slave mode, setting STO resets I2C hardware to the defined "not addressed" slave mode. This means it is NO LONGER in the slave receiver mode to receive data from the master transmit device.

- SI I2C Port 1 Interrupt Flag. When a new SIO state is present in the S1STA register, the SI flag is set by hardware, and if the EA and EI2C bits are both set, the I2C1 interrupt is requested. SI must be cleared by software.

- AA Assert Acknowledge control bit. When AA=1 prior to address or data received, an acknowledged (low level to SDA) will be returned during the acknowledge clock pulse on the SCL line when 1.) A slave is acknowledging the address sent from master, 2.) The receiver devices are acknowledging the data sent by transmitter. When AA=0 prior to address or data received, a Not acknowledged (high level to SDA) will be returned during the acknowledge clock pulse on the SCL line.

#### 25.2.4 The Status Register, I2STATUS

I2STATUS is an 8-bit read-only register. The three least significant bits are always 0. The five most significant bits contain the status code. There are 23 possible status codes. When I2STATUS contains F8H, no serial interrupt is requested. All other I2STATUS values correspond to defined SIO states. When each of these states is entered, a status interrupt is requested (SI = 1). A valid status code is present in I2STATUS one machine cycle after SI is set by hardware and is still present one machine cycle after SI has been reset by software.

#### 25.2.5 The I2C Clock Baud Rate Bits, I2CLK

The data baud rate of I2C is determines by I2CLK register when SIO is in a master mode. It is not important when SIO is in a slave mode. In the slave modes, SIO will automatically synchronize with any clock frequency up to 400 KHz from master I2C device.

The data baud rate of I2C setting is Data Baud Rate of I2C = Fcpu / (I2CLK+1). The Fcpu=Fosc/4. If Fosc = 16MHz, the I2CLK = 40(28H), so data baud rate of I2C = 16MHz/(4X (40 + 1)) =97.56Kbits/sec. The block diagram is as below figure.

Publication Release Date: Aug 05, 2010 Revision A02

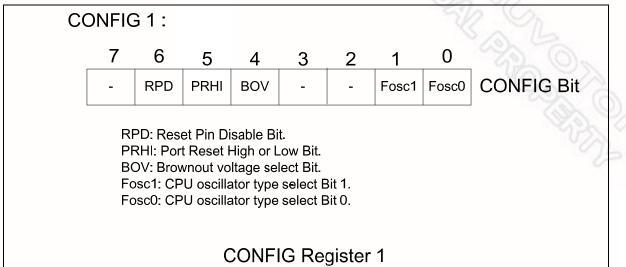

#### 27 CONFIG BITS