Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 20MHz                                                                                  |

| Connectivity               | I <sup>2</sup> C, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT                                        |

| Number of I/O              | 18                                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | 256 x 8                                                                                |

| RAM Size                   | 256 x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                            |

| Data Converters            | A/D 4x10b                                                                              |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                         |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/n79e825asg |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2 FEATURES

- Fully static design 8-bit Turbo 51 CMOS microcontroller up to 20MHz when V\_{DD}=4.5V to 5.5V, 12MHz when V\_{DD}=2.7V to 5.5V

- 16K/8K/4K/2K bytes of AP Flash EPROM, with ICP and external writer programmable mode.

- 256 bytes of on-chip RAM.

- **256** bytes NVM Data Flash EPROM for customer data storage used and 10K writer cycles; Data Flash program/erase  $V_{DD}$ =3.0V to 5.5V

- Instruction-set compatible with MCS-51.

- Built-in internal RC oscillator (about 6MHz)

- Two 8-bit bi-directional and one 2-bit bi-directional ports.

- Two 16-bit timer/counters.

- 13 interrupts source with four levels of priority.

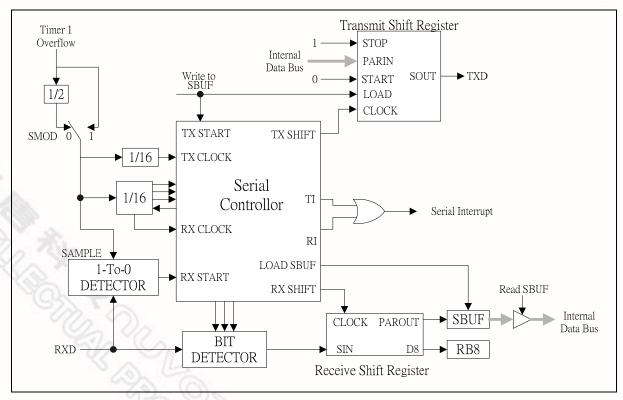

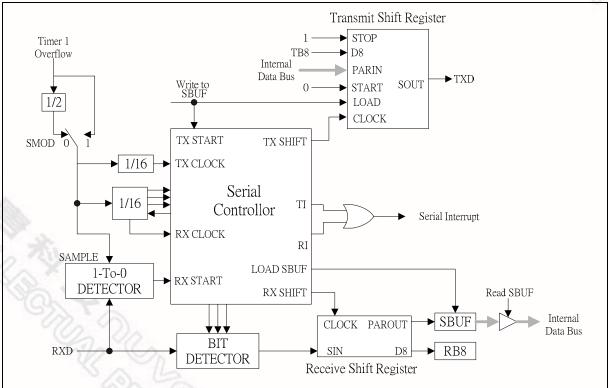

- One enhanced full duplex serial port with framing error detection and automatic address recognition.

- The 4 outputs mode and TTL/Schmitt trigger selectable Port.

- Programmable Watchdog Timer.

- Four-channel 10-bit PWM (Pulse Width Modulator).

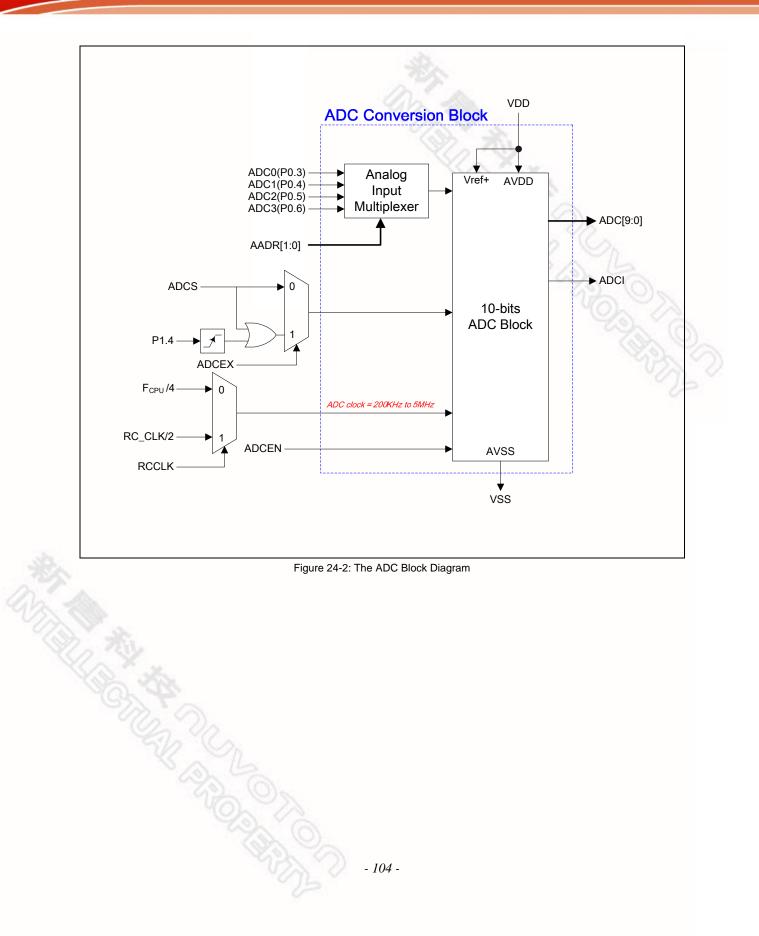

- Four-channel multiplexed with 10-bits A/D convert.

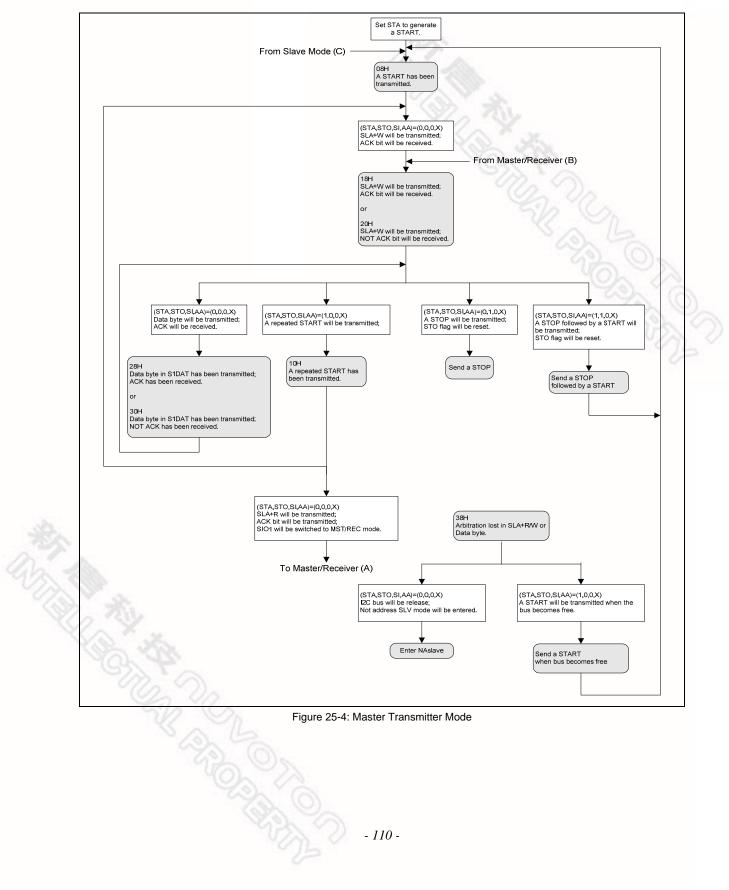

- One I2C communication port (Master / Slave).

- Eight keypad interrupt inputs.

- Two analog comparators.

- Configurable on-chip oscillator.

- LED drive capability (20mA) on all port pins.

- Brownout voltage detect interrupt and reset.

- Development Tools:

- JTAG ICE(In Circuit Emulation) tool

- ICP(In Circuit Programming) writer

- Packages:

N79E825ADG ---- PDIP20 N79E825ASG ---- SOP20 N79E825ARG ---- SSOP20 N79E824ADG ---- PDIP20 N79E824ASG ---- SOP20 N79E823ADG ---- PDIP20 N79E823ASG ---- SOP20 N79E823ARG ---- SSOP20 N79E823ARG ---- PDIP20

- 5 -

| FFH       Indirect RAM         00H       Direct RAM         70H       76       78       70       70         70H       76       75       74       79       78         70H       76       75       74       73       72       71       70         70H       66       66       64       63       62       61       60         20H       67       66       56       54       53       52       51       50         20H       67       56       56       54       53       52       51       50         20H       67       56       54       53       52       51       50         20H       67       56       54       53       52       51       50         20H       67       56       54       53       52       51       50         20H       47       46       45       44       33       32       31       30         20H       27       26       26       28       24       23       22       21       20         21       17       16       15       14                                                                                                                                                                                                                                                                        |        |            |    |        |        |         |          |     |    |     |         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|----|--------|--------|---------|----------|-----|----|-----|---------|

| Print         Direct RAM           30H<br>2FH         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7                                                                                                                          |        | FFH        |    |        |        |         | X        | 2   |    |     |         |

| Direct RAM         2FH       7F       7E       7D       7C       7B       7A       79       78         2FH       77       76       75       74       73       72       71       70         2DH       6F       6E       6D       6C       6B       6A       69       68         2CH       67       66       65       54       53       52       50         2BH       5F       5E       55       54       53       55       50         2BH       5F       5E       55       54       53       55       50         2BH       4F       4E       4D       4C       4B       44       40         2H       4F       4E       4D       4C       4B       40         2H       2F       2E       2D       2C       2B       2A       29       2B         2H       1F       1E       1D       1C       1B       1A       19       18         2H       2F       2E       2D       2C       2B       2A       29       2B         2H       1F       1E       1D                                                                                                                                                                                                                                                                                 |        |            |    |        |        | Indired | ct RAM   | 1   |    | r   |         |

| Direct RAM         2FH       7F       7E       7D       7C       7B       7A       79       78         2FH       77       76       75       74       73       72       71       70         2DH       6F       6E       6D       6C       6B       6A       69       68         2CH       67       66       65       54       53       52       50         2BH       5F       5E       55       54       53       55       50         2BH       5F       5E       55       54       53       55       50         2BH       4F       4E       4D       4C       4B       44       40         2H       4F       4E       4D       4C       4B       40         2H       2F       2E       2D       2C       2B       2A       29       2B         2H       1F       1E       1D       1C       1B       1A       19       18         2H       2F       2E       2D       2C       2B       2A       29       2B         2H       1F       1E       1D                                                                                                                                                                                                                                                                                 |        |            |    |        |        |         |          |     |    | ÷., |         |

| 30H         2FH       7F       7E       7D       7C       7B       7A       79       78         2FH       77       76       75       74       73       72       71       70         2FH       6F       6E       6D       6C       6B       6A       69       68         2CH       67       56       55       54       53       52       51       50         2HH       57       56       55       54       53       52       51       50         2HH       4F       4E       4D       4C       4B       4A       49       48         2HH       47       46       45       44       43       42       41       40         2HH       37       36       35       34       33       32       31       30         2H       2F       2E       2D       2C       2B       2A       29       28         2H       17       16       15       14       13       12       11       10         2H       17       16       15       14       13       12       11       10 </td <td></td> <td>80H<br/>7FH</td> <td></td> <td></td> <td></td> <td></td> <td>- 7</td> <td>+</td> <td></td> <td>X</td> <td></td>                                                                                                                                    |        | 80H<br>7FH |    |        |        |         | - 7      | +   |    | X   |         |

| 30H         2FH       7F       7E       7D       7C       7B       7A       79       78         2FH       77       76       75       74       73       72       71       70         2FH       6F       6E       6D       6C       6B       6A       69       68         2CH       67       56       55       54       53       52       51       50         2HH       57       56       55       54       53       52       51       50         2HH       4F       4E       4D       4C       4B       4A       49       48         2HH       47       46       45       44       43       42       41       40         2HH       37       36       35       34       33       32       31       30         2H       2F       2E       2D       2C       2B       2A       29       28         2H       17       16       15       14       13       12       11       10         2H       17       16       15       14       13       12       11       10 </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>3</td> <td></td>                                                                                                                                                   |        |            |    |        |        |         |          |     |    | 3   |         |

| 2FH       7F       7E       7D       7C       7B       7A       79       78         2EH       77       76       75       74       73       72       71       70         2DH       6F       6E       6D       6C       6B       6A       69       68         2CH       67       66       65       64       63       62       61       60         2BH       5F       5E       5D       5C       5B       5A       59       58         2AH       57       56       55       54       53       52       51       50         29H       4F       4E       4D       4C       4B       4A       49       48         28H       37       36       35       34       33       32       31       30         27H       26       25       24       23       22       21       20         27H       16       15       14       13       12       11       10         27H       17       16       15       14       13       12       11       10         27H       17       16                                                                                                                                                                                                                                                                    |        |            |    |        |        | Direc   | t RAM    |     |    | S   | 183     |

| 2EH       77       76       75       74       73       72       71       70         2DH       6F       6E       6D       6C       6B       6A       69       68         2CH       67       66       65       64       63       62       61       60         2BH       5F       5E       5D       5C       5B       5A       59       58         2AH       57       56       55       54       53       52       51       50         2PH       4F       4E       4D       4C       4B       4A       49       48         2BH       37       36       35       34       33       32       31       30         2FH       2E       2D       2C       2B       2A       29       28         2H       17       16       15       14       13       12       11       10         2H       17       16       15       14       13       12       11       10         2H       17       16       15       14       13       12       11       10         2H       0F <t< td=""><td></td><td></td><td></td><td></td><td></td><td>1</td><td></td><td>•</td><td></td><td>53</td><td>AT COL</td></t<>                                                                                                                                           |        |            |    |        |        | 1       |          | •   |    | 53  | AT COL  |

| 2DH       6F       6E       6D       6C       6B       6A       69       68         2CH       67       66       65       64       63       62       61       60         2BH       5F       5E       5D       5C       5B       5A       59       58         2AH       57       56       55       54       53       52       51       50         29H       4F       4E       4D       4C       4B       4A       49       48         28H       47       46       45       44       43       42       41       40         27H       3F       3E       3D       3C       3B       3A       39       38         26H       37       36       35       34       33       32       31       30         25H       2F       2E       2D       2C       2B       2A       29       28         24H       27       26       25       24       23       22       21       20         21H       0F       0E       0D       0C       0B       0A       09       08         20H                                                                                                                                                                                                                                                                    |        |            |    |        |        |         |          |     |    |     | On Dr.  |

| 2EH     5F     5E     5D     5C     5B     5A     59     58       2AH     57     56     55     54     53     52     51     50       29H     4F     4E     4D     4C     4B     4A     49     48       28H     47     46     45     44     43     42     41     40       27H     3F     3E     3D     3C     3B     3A     39     38       26H     37     36     35     34     33     32     31     30       25H     2F     2E     2D     2C     2B     2A     29     28       24H     27     26     25     24     23     22     21     20       23H     1F     1E     1D     1C     1B     1A     19     18       22H     17     16     15     14     13     12     11     10       21H     0F     0E     0D     0C     0B     0A     09     08       20H     07     06     05     04     03     02     01     00       1FH     H     Bank 1                                                                                                                                                                                                                                                                                                                                                                                       |        |            |    |        |        |         |          |     |    |     | SO Sh   |

| 2EH     5F     5E     5D     5C     5B     5A     59     58       2AH     57     56     55     54     53     52     51     50       29H     4F     4E     4D     4C     4B     4A     49     48       28H     47     46     45     44     43     42     41     40       27H     3F     3E     3D     3C     3B     3A     39     38       26H     37     36     35     34     33     32     31     30       25H     2F     2E     2D     2C     2B     2A     29     28       24H     27     26     25     24     23     22     21     20       23H     1F     1E     1D     1C     1B     1A     19     18       22H     17     16     15     14     13     12     11     10       21H     0F     0E     0D     0C     0B     0A     09     08       20H     07     06     05     04     03     02     01     00                                                                                                                                                                                                                                                                                                                                                                                                                  |        |            |    |        |        |         | L        |     |    |     | Non the |

| 2AH       57       56       55       54       53       52       51       50         29H       4F       4E       4D       4C       4B       4A       49       48         28H       47       46       45       44       43       42       41       40         27H       3F       3E       3D       3C       3B       3A       39       38         26H       37       36       35       34       33       32       31       30         25H       2F       2E       2D       2C       2B       2A       29       28         24H       27       26       25       24       23       22       21       20         23H       1F       1E       1D       1C       1B       1A       19       18         22H       17       16       15       14       13       12       11       10         21H       0F       0E       0D       0C       0B       0A       09       08         20H       07       06       05       04       03       02       01       00         1FH                                                                                                                                                                                                                                                                    |        |            |    |        |        |         |          |     |    |     | 20 00   |

| 29H       4F       4E       4D       4C       4B       4A       49       48         28H       47       46       45       44       43       42       41       40         27H       3F       3E       3D       3C       3B       3A       39       38         26H       37       36       35       34       33       32       31       30         25H       2F       2E       2D       2C       2B       2A       29       28         24H       27       26       25       24       23       22       21       20         23H       1F       1E       1D       1C       1B       1A       19       18         22H       17       16       15       14       13       12       11       10         21H       0F       0E       0D       0C       0B       0A       09       08         20H       07       06       05       04       03       02       01       00         1FH       Bank 3       3       3       3       3       3       3       3         0H <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>On M</td></t<>                                                                                                                                                 |        |            |    |        |        |         |          |     |    |     | On M    |

| 27H       3F       3E       3D       3C       3B       3A       39       38         26H       37       36       35       34       33       32       31       30         25H       2F       2E       2D       2C       2B       2A       29       28         24H       27       26       25       24       23       22       21       20         23H       1F       1E       1D       1C       1B       1A       19       18         22H       17       16       15       14       13       12       11       10         21H       0F       0E       0D       0C       0B       0A       09       08         20H       07       06       05       04       03       02       01       00         1FH       Bank 3       Bank 4       Image: State 1       Image: State 1 </td <td></td> <td></td> <td></td> <td>4E</td> <td></td> <td></td> <td></td> <td>4A</td> <td></td> <td>48</td> <td>~~~ (O)</td> |        |            |    | 4E     |        |         |          | 4A  |    | 48  | ~~~ (O) |

| 26H       37       36       35       34       33       32       31       30         25H       2F       2E       2D       2C       2B       2A       29       28         24H       27       26       25       24       23       22       21       20         23H       1F       1E       1D       1C       1B       1A       19       18         22H       17       16       15       14       13       12       11       10         21H       0F       0E       0D       0C       0B       0A       09       08         20H       17       06       05       04       03       02       01       00         1FH       0F       0E       0D       0C       0B       0A       09       08         20H       07       06       05       04       03       02       01       00         1FH            5       5       5       5       5       5       5       5       5       5       5       5       5       5<                                                                                                                                                                                                                                                                                                                      |        | 28H        | 47 | 46     | 45     | 44      | 43       | 42  | 41 | 40  | NO. C   |

| 25H     2F     2E     2D     2C     2B     2A     29     28       24H     27     26     25     24     23     22     21     20       23H     1F     1E     1D     1C     1B     1A     19     18       22H     17     16     15     14     13     12     11     10       21H     0F     0E     0D     0C     0B     0A     09     08       20H     07     06     05     04     03     02     01     00       1FH     Bank 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 27H        | 3F | 3E     | 3D     | 3C      | 3B       | ЗA  | 39 | 38  | "B      |

| 24H 27 26 25 24 23 22 21 20<br>23H 1F 1E 1D 1C 1B 1A 19 18<br>22H 17 16 15 14 13 12 11 10<br>21H 0F 0E 0D 0C 0B 0A 09 08<br>20H 07 06 05 04 03 02 01 00<br>1FH Bank 3<br>18H<br>17H<br>0FH 0FH Bank 1<br>00H Bank 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |            | -  |        |        |         |          |     |    |     | 0       |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |            |    |        |        |         |          |     |    |     |         |

| 22H 17 16 15 14 13 12 11 10<br>21H 0F 0E 0D 0C 0B 0A 09 08<br>20H 07 06 05 04 03 02 01 00<br>1FH Bank 3<br>18H<br>17H Bank 2<br>10H OFH 0FH Bank 1<br>08H 00H Bank 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |            |    |        |        |         |          |     |    |     |         |

| 21H     0F     0E     0D     0C     0B     0A     09     08       20H     07     06     05     04     03     02     01     00       1FH     Bank 3     Bank 2     5     5     5     5     5       18H     Bank 1     Bank 1     5     5     5     5     5       10H     Bank 1     5     5     5     5     5     5       00H     Bank 0     5     5     5     5     5     5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |            |    |        |        |         |          |     |    |     |         |

| 20H     07     06     05     04     03     02     01     00       1FH     Bank 3     Bank 2     00     00     00       10H     0FH     Bank 1     00       00H     Bank 0     00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |            |    |        |        |         | <u> </u> | L   |    |     |         |

| Bank 3<br>18H<br>17H<br>Bank 2<br>10H<br>0FH<br>Bank 1<br>08H<br>07H<br>Bank 0<br>00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |            | -  |        | 05     |         | 03       | 02  | 01 | 00  |         |

| 18H       17H       Bank 2       10H       0FH       Bank 1       08H       07H       Bank 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        | 1FH        |    |        |        | Ba      |          |     |    |     |         |

| Bank 2<br>10H<br>0FH<br>Bank 1<br>08H<br>07H<br>Bank 0<br>00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        | 18H        |    |        |        | Dai     | IK J     |     |    |     |         |

| 10H       0FH       Bank 1       08H       07H       Bank 0       00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | 17H        |    |        |        | Bai     | nk 2     |     |    |     |         |

| Bank 1<br>08H<br>07H<br>Bank 0<br>00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | 10H<br>0FH |    |        |        |         |          |     |    |     |         |

| Bank 0<br>00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |            |    |        |        | Bai     | nk 1     |     |    |     |         |

| оон                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | 08H<br>07H |    |        |        |         |          |     |    |     |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | 00H        |    |        |        | Bai     | nk 0     |     |    |     |         |

| Figure 7-3: Scratch pad RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Sec. 1 |            |    |        |        |         |          |     |    |     |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |            |    | Figure | e 7-3: | Scrate  | ch pad   | RAM |    |     |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |            |    |        |        |         |          |     |    |     |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |            |    |        |        |         |          |     |    |     |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |            |    |        |        |         |          |     |    |     |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |            |    |        |        |         |          |     |    |     |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |            |    |        |        |         |          |     |    |     |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |            |    |        |        |         |          |     |    |     |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |            |    |        |        |         |          |     |    |     |         |

| -14-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |            |    |        |        | - 14 -  |          |     |    |     |         |

### 8 SPECIAL FUNCTION REGISTERS

The N79E825 series uses Special Function Registers (SFRs) to control and monitor peripherals and their Modes. The SFRs reside in the register locations 80-FFh and are accessed by direct addressing only. Some of the SFRs are bit addressable. This is very useful in cases where users wish to modify a particular bit without changing the others. The SFRs that are bit addressable are those whose addresses end in 0 or 8. The N79E825 series contain all the SFRs present in the standard 8052. However some additional SFRs are added. In some cases the unused bits in the original 8052, have been given new functions. The list of the SFRs is as follows.

| F8 | IP1   |        |              |       |         | S.       | 2°C     |         |

|----|-------|--------|--------------|-------|---------|----------|---------|---------|

| F0 | В     |        |              |       |         |          | P0ID    | IP1H    |

| E8 | EIE   |        |              |       |         |          | 32      | 10,     |

| E0 | ACC   | ADCCON | ADCH         |       |         |          | P)      |         |

| D8 | WDCON | PWMPL  | <b>PWM0L</b> | PWM1L | PWMCON1 | PWM2L    | PWM3L   | PWMCON2 |

| D0 | PSW   | PWMPH  | PWM0H        | PWM1H |         | PWM2H    | PWM3H   | PWMCON3 |

| C8 |       |        |              |       |         |          | NVMCON  | NVMDAT  |

| C0 | I2CON | I2ADDR |              |       |         |          | NVMADDR | ТА      |

| B8 | IP0   | SADEN  |              |       | I2DAT   | I2STATUS | I2CLK   | I2TIMER |

| B0 |       | P0M1   | P0M2         | P1M1  | P1M2    | P2M1     | P2M2    | IP0H    |

| A8 | IE    | SADDR  |              |       | CMP1    | CMP2     |         |         |

| A0 | P2    | KBI    | AUXR1        |       |         |          |         |         |

| 98 | SCON  | SBUF   |              |       |         |          |         |         |

| 90 | P1    |        |              |       |         | DIVM     |         |         |

| 88 | TCON  | TMOD   | TL0          | TL1   | TH0     | TH1      | CKCON   |         |

| 80 | P0    | SP     | DPL          | DPH   |         |          |         | PCON    |

Table 8-1: Special Function Register Location Table

Note: 1. The SFRs in the column with dark borders are bit-addressable

2. The table is condensed with eight locations per row. Empty locations indicate that these are no registers at these addresses. When a bit or register is not implemented, it will read high.

# nuvoTon

#### Continued .

| NAME  | FUNCTION                                           |

|-------|----------------------------------------------------|

| KBI.3 | 1: Enable P0.3 as a cause of a Keyboard interrupt. |

| KBI.2 | 1: Enable P0.2 as a cause of a Keyboard interrupt. |

| KBI.1 | 1: Enable P0.1 as a cause of a Keyboard interrupt. |

| KBI.0 | 1: Enable P0.0 as a cause of a Keyboard interrupt. |

|       | KBI.3<br>KBI.2<br>KBI.1                            |

#### **AUX FUNCTION REGISTER 1**

| Bit: | 7           | 6   | 5   | 4     | 3    | 2     | 1  | 0          |

|------|-------------|-----|-----|-------|------|-------|----|------------|

|      | KBF         | BOD | BOI | LPBOV | SRST | ADCEN | 0  | DPS        |

| Mnem | onic: AUXR' | 1   |     |       | -    | 3     | Ac | dress: A2h |

#### Mnemonic: AUXR1

| BIT | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | KBF   | <ul><li>Keyboard Interrupt Flag:</li><li>1: When any pin of port 0 that is enabled for the Keyboard Interrupt function goes low. Must be cleared by software.</li></ul>                                                                                                                                                                                                                                           |

| 6   | BOD   | Brown Out Disable:<br>0: Enable Brownout Detect function.<br>1: Disable Brownout Detect function and save power.                                                                                                                                                                                                                                                                                                  |

| 5   | BOI   | <ul> <li>Brown Out Interrupt:</li> <li>0: Disable Brownout Detect Interrupt function and it will cause chip reset when BOF is set.</li> <li>1: This prevents Brownout Detection from causing a chip reset and allows the Brownout Detect function to be used as an interrupt.</li> </ul>                                                                                                                          |

| 4   | LPBOV | <ul> <li>Low Power Brown Out Detect control:</li> <li>0: When BOD is enable, the Brown Out detect is always turned on by normal run or Power Down mode.</li> <li>1: When BOD is enable, the Brown Out detect circuit is turned on by Power Down mode. This control can help save 15/16 of the Brownout circuit power. When uC is in Power Down mode, the BOD will enable internal RC OSC (2MHz~0.5MHZ)</li> </ul> |

| 3   | SRST  | Software reset:<br>1: reset the chip as if a hardware reset occurred.                                                                                                                                                                                                                                                                                                                                             |

| 2   | ADCEN | 0: Disable ADC circuit.<br>1: Enable ADC circuit.                                                                                                                                                                                                                                                                                                                                                                 |

| 1   | 0     | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0   | DPS   | Dual Data Pointer Select<br>0: To select DPTR of standard 8051.<br>1: To select DPTR1                                                                                                                                                                                                                                                                                                                             |

#### **INTERRUPT ENABLE**

| I2ADDR<br>NAME<br>2ADDR.[                         | E                                   | 12C /                             |                                                                            |                                                                                | 122                                                                               |                                                                                                                                 |                                                                                                                                                       | GC                                                                                                                                                                                                                    |

|---------------------------------------------------|-------------------------------------|-----------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                   |                                     | 12C /                             |                                                                            |                                                                                |                                                                                   |                                                                                                                                 | А                                                                                                                                                     | ddres                                                                                                                                                                                                                 |

| 2ADDR.[                                           | [7:1]                               | 12C /                             |                                                                            |                                                                                | FUNCTIO                                                                           | ON                                                                                                                              |                                                                                                                                                       |                                                                                                                                                                                                                       |

| 2ADDR.[                                           | [7:4]                               |                                   | Address reg                                                                | ister:                                                                         | X                                                                                 | NY JA                                                                                                                           |                                                                                                                                                       |                                                                                                                                                                                                                       |

|                                                   | .[7.1]                              | SFR<br>In th                      | . The conter<br>e slave moo<br>J's own add                                 | nt of this reg<br>de, the seve                                                 | m and write<br>gister is irrel<br>n most sign<br>C hardware                       | evant when<br>ificant bits n                                                                                                    | I2C is in manust be load                                                                                                                              | aster<br>led v                                                                                                                                                                                                        |

|                                                   |                                     | Gene                              | eral Call Fur                                                              | nction.                                                                        |                                                                                   |                                                                                                                                 | "LON"                                                                                                                                                 | 2                                                                                                                                                                                                                     |

| ЭС                                                |                                     |                                   |                                                                            |                                                                                |                                                                                   |                                                                                                                                 |                                                                                                                                                       |                                                                                                                                                                                                                       |

| RESS                                              | L                                   |                                   |                                                                            |                                                                                |                                                                                   |                                                                                                                                 |                                                                                                                                                       | X                                                                                                                                                                                                                     |

| 6                                                 | 6                                   | 4                                 | 5                                                                          | 4                                                                              | 3                                                                                 | 2                                                                                                                               | 1                                                                                                                                                     | 0                                                                                                                                                                                                                     |

| DDR.7 NV                                          | VMADE                               | DR.6                              | NVMADDR.5                                                                  | NVMADDR.4                                                                      | NVMADDR.3                                                                         | NVMADDR.2                                                                                                                       | NVMADDR.1                                                                                                                                             | NVM                                                                                                                                                                                                                   |

| NVMAD                                             | DDR                                 |                                   |                                                                            |                                                                                |                                                                                   |                                                                                                                                 | A                                                                                                                                                     | ddre                                                                                                                                                                                                                  |

|                                                   |                                     |                                   |                                                                            |                                                                                |                                                                                   |                                                                                                                                 |                                                                                                                                                       |                                                                                                                                                                                                                       |

| NAME                                              |                                     |                                   |                                                                            |                                                                                | FUNCTI                                                                            | ON                                                                                                                              |                                                                                                                                                       |                                                                                                                                                                                                                       |

| NAME<br>MADDR.                                    |                                     | The                               | NVM addre<br>register inc<br>e memory s                                    | licates NVM                                                                    | FUNCTIO                                                                           |                                                                                                                                 | rte address                                                                                                                                           |                                                                                                                                                                                                                       |

|                                                   |                                     | The                               | register inc                                                               | licates NVM                                                                    |                                                                                   |                                                                                                                                 | rte address                                                                                                                                           |                                                                                                                                                                                                                       |

| MADDR.                                            |                                     | The                               | register inc                                                               | licates NVM                                                                    |                                                                                   |                                                                                                                                 | rte address                                                                                                                                           |                                                                                                                                                                                                                       |