Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detalls                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | ARM® Cortex®-M0                                                                       |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 24MHz                                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                            |

| Number of I/O              | 29                                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 2K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x10b                                                                             |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 32-WFQFN Exposed Pad                                                                  |

| Supplier Device Package    | 33-QFN (4x4)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/mini52tde |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### LIST OF FIGURES

| Figure 4.1-1 NuMicro Mini51™ Series Selection Code             | 13 |

|----------------------------------------------------------------|----|

| Figure 4.3-1 NuMicro Mini51™ Series LQFP 48-pin Diagram        | 15 |

| Figure 4.3-2 NuMicro Mini51™ Series QFN 33-pin Diagram         | 16 |

| Figure 4.3-3 NuMicro Mini51™ Series TSSOP 20-pin Diagram       | 17 |

| Figure 4.3-4 NuMicro Mini51™ Series TSSOP 20-pin Diagram       | 17 |

| Figure 5.1-1 NuMicro Mini51™ Series Block Diagram              | 22 |

| Figure 6.3-1 NuMicro Mini51™ Series Power Architecture Diagram |    |

| Figure 6.4-1 Clock Generator Block Diagram                     | 31 |

| Figure 6.4-2 System Clock Block Diagram                        |    |

| Figure 6.4-3 SysTick Clock Control Block Diagram               |    |

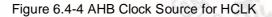

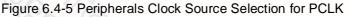

| Figure 6.4-4 AHB Clock Source for HCLK                         |    |

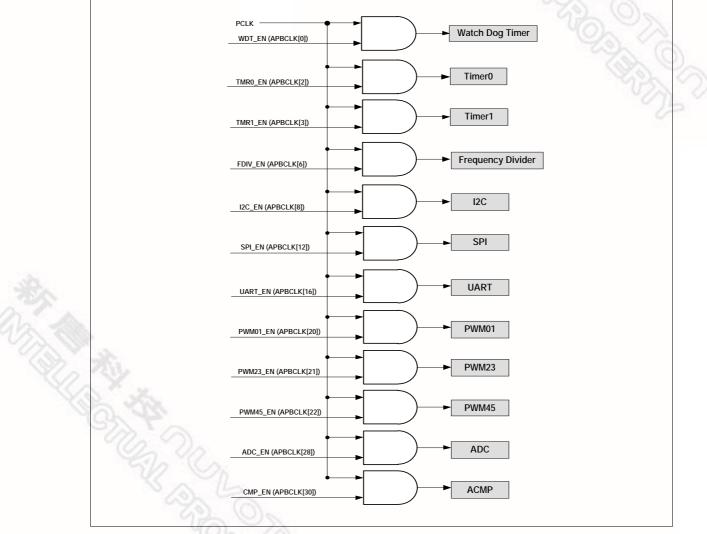

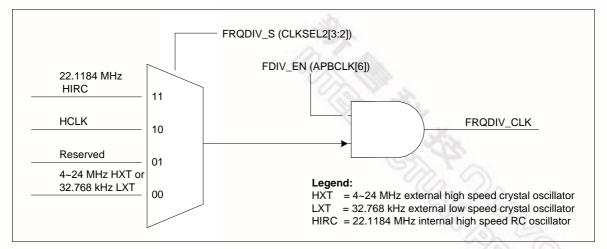

| Figure 6.4-5 Peripherals Clock Source Selection for PCLK       | 33 |

| Figure 6.4-6 Clock Source of Frequency Divider                 | 35 |

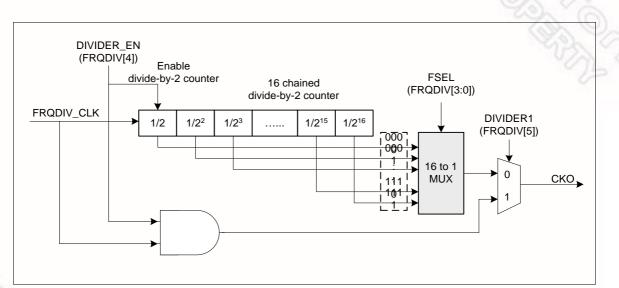

| Figure 6.4-7 Block Diagram of Frequency Divider                | 35 |

| Figure 7.1-1 Functional Block Diagram                          | 47 |

| Figure 9-1Mini5xDE Typical Crystal Application Circuit         | 59 |

| Figure 9-2Power-up Ramp Condition                              | 64 |

### LIST OF TABLES

| Table 4.1-1 List of Abbreviations                         | 12 |

|-----------------------------------------------------------|----|

| Table 4.2-1NuMicro Mini51™ Series Product Selection Guide | 14 |

| Table 6.1-1 Address Space Assignments for On-Chip Modules | 23 |

| Table 6.2-1 Exception Model                               | 25 |

| Table 6.2-2 System Interrupt Map Vector Table             | 26 |

| Table 6.2-3 Vector Table Format                           | 26 |

| Table 6.3-1 Memory Mapping Table                          | 30 |

| Table 6.4-1 Peripheral Clock Source Selection Table       | 34 |

|                                                           |    |

- Full-duplex synchronous serial data transfer

- Provides 3-wire function

- Variable length of transfer data from 8 to 32 bits

- MSB or LSB first data transfer

- Rx latching data can be either at rising edge or at falling edge of serial clock

- Tx sending data can be either at rising edge or at falling edge of serial clock

- Supports Byte Suspend mode in 32-bit transmission

- 4-level depth FIFO buffer

- I<sup>2</sup>C

- Supports Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Programmable clocks allow for versatile rate control

- Supports 7-bit addressing mode

- Supports multiple address recognition (four slave addresses with mask option)

- Supports Power-down wake-up function

- Support FIFO function

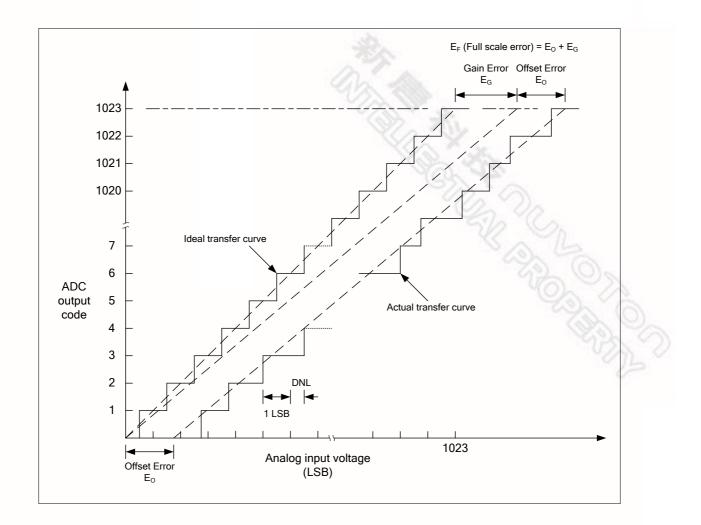

- ADC (Analog-to-Digital Converter)

- 10-bit SAR ADC with 300K SPS

- Up to 8-ch single-end input and one internal input from band-gap

- Conversion started either by software trigger, PWM trigger, or external pin trigger

- Supports conversion value monitoring (or comparison) for threshold voltage detection

- Analog Comparator

- Two analog comparators with programmable 16-level internal voltage reference

- Build-in CRV (comparator reference voltage)

- Supports Hysteresis function

- Interrupt when compared results changed

- ISP (In-System Programming) and ICP (In-Circuit Programming)

- BOD (Brown-out Detector)

- With 4 programmable threshold levels: 4.4V/3.7V/2.7V/2.2V

## 4 PARTS INFORMATION LIST AND PIN CONFIGURATION

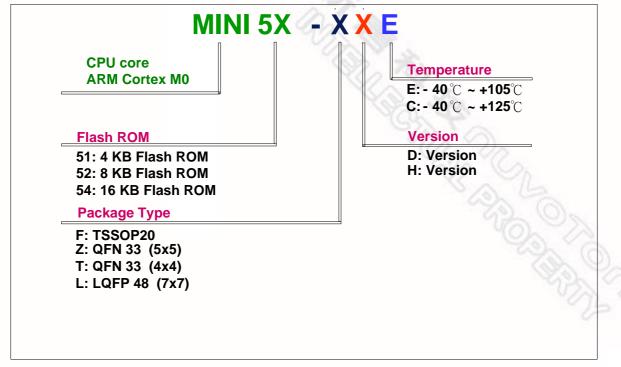

## 4.1 NuMicro Mini51™ Series Selection Code

Figure 4.1-1 NuMicro Mini51™ Series Selection Code

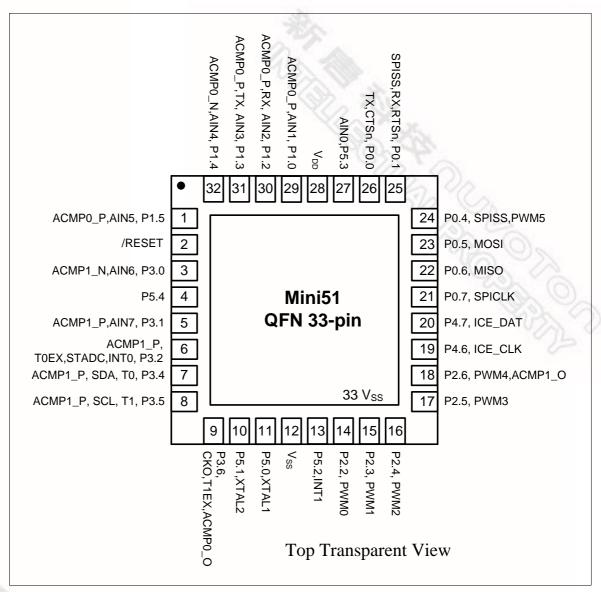

### 4.3.2 QFN 33-pin

Figure 4.3-2 NuMicro Mini51™ Series QFN 33-pin Diagram

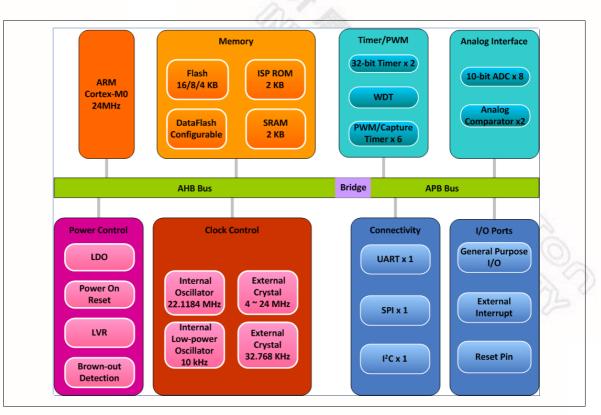

## 5 BLOCK DIAGRAM

## 5.1 NuMicro Mini51™ Block Diagram

Figure 5.1-1 NuMicro Mini51™ Series Block Diagram

## NuMicro MINI51<sup>™</sup> DE Series Datasheet

# nuvoTon

| Exception<br>Number | Interrupt Number<br>(Bit In Interrupt<br>Registers) | Interrupt Name    | Source<br>Module | Interrupt Description                                                 | Power-Down<br>Wake-Up |

|---------------------|-----------------------------------------------------|-------------------|------------------|-----------------------------------------------------------------------|-----------------------|

| 29                  | 13                                                  | -                 | - 23             | 17                                                                    |                       |

| 30                  | 14                                                  | SPI_INT           | SPI              | SPI interrupt                                                         | No                    |

| 31                  | 15                                                  | -                 | -                | the COV-                                                              |                       |

| 32                  | 16                                                  | GP5_INT           | GPIO             | External signal interrupt from GPIO group P5 except P5.2              | Yes                   |

| 33                  | 17                                                  | HIRC_TRIM_IN<br>T | HIRC             | HIRC trim interrupt                                                   | No                    |

| 34                  | 18                                                  | I2C_INT           | I <sup>2</sup> C | I <sup>2</sup> C interrupt                                            | Yes                   |

| 35 ~ 40             | 19 ~ 24                                             | -                 | -                | -                                                                     | n.                    |

| 41                  | 25                                                  | ACMP_INT          | ACMP             | Analog Comparator 0 or Comparator 1<br>interrupt                      | Yes                   |

| 42 ~ 43             | 26 ~ 27                                             | -                 | -                | -                                                                     | 20.0                  |

| 44                  | 28                                                  | PWRWU_INT         | CLKC             | Clock controller interrupt for chip wake-<br>up from Power-down state | Yes                   |

| 45                  | 29                                                  | ADC_INT           | ADC              | ADC interrupt                                                         | No                    |

| 46 ~ 47             | 30 ~ 31                                             | -                 | -                | -                                                                     | 1                     |

| Table 6.2-2 System | Interrupt Map | Vector Table |

|--------------------|---------------|--------------|

|--------------------|---------------|--------------|

### 6.2.4 Vector Table

When an interrupt is accepted, the processor will automatically fetch the starting address of the interrupt service routine (ISR) from a vector table in memory. For ARMv6-M, the vector table based address is fixed at 0x00000000. The vector table contains the initialization value for the stack pointer on reset, and the entry point addresses for all exception handlers. The vector number on previous page defines the order of entries in the vector table associated with the exception handler entry as illustrated in previous section.

| Vector Table Word Offset (Bytes) | Description                                         |  |  |  |  |

|----------------------------------|-----------------------------------------------------|--|--|--|--|

| 0x00                             | Initial Stack Pointer Value                         |  |  |  |  |

| Exception Number * 0x04          | Exception Entry Pointer using that Exception Number |  |  |  |  |

#### Table 6.2-3 Vector Table Format

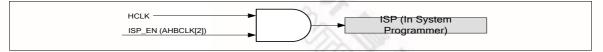

### 6.4.3 ISP Clock Source Selection

The clock source of ISP is from AHB clock (HCLK). Please refer to the register AHBCLK.

### 6.4.4 Module Clock Source Selection

The peripheral clock has different clock source switch settings depending on different peripherals. Please refer to the CLKSEL1 and APBCLK register description in section **Error! Reference source not found.**

## 6.7 Flash Memory Controller (FMC)

#### 6.7.1 Overview

The NuMicro Mini51<sup>™</sup> series is equipped with 4K/8K/16K bytes on chip embedded flash memory for application program (APROM) that can be updated through ISP procedure. In-System-Programming (ISP) and In-Application-Programming (IAP) enable user to update program memory when chip is soldered on PCB. After chip power on Cortex<sup>™</sup>-M0 CPU fetches code from APROM or LDROM decided by boot select (CBS) in CONFIG0. By the way, the NuMicro Mini51<sup>™</sup> series also provides Data Flash region that is shared with APROM and its start address is configurable and defined by user in CONFIG1.

### 6.7.2 Features

- Running up to 24 MHz with zero wait state for discontinuous address read access

- 4/8/16 Kbytes application program memory (APROM)

- 2 Kbytes in system programming (ISP) loader program memory (LDROM)

- Programmable data flash start address

- All embedded flash memory supports 512 bytes page erase

- In System Program (ISP)/In Application Program (IAP) to update on chip flash memory

### 6.10 Enhanced PWM Generator

#### 6.10.1 Overview

The NuMicro Mini51<sup>™</sup> series has built one PWM unit which is specially designed for motor driving control applications. The PWM unit supports six PWM generators which can be configured as six independent PWM outputs, PWM0~PWM5, or as three complementary PWM pairs, (PWM0, PWM1), (PWM2, PWM3) and (PWM4, PWM5) with three programmable dead-zone generators.

Every complementary PWM pairs share one 8-bit prescaler. There are six clock dividers providing five divided frequencies (1, 1/2, 1/4, 1/8, 1/16) for each channel. Each PWM output has independent 16-bit counter for PWM period control, and 16-bit comparators for PWM duty control. The six PWM generators provide twelve independent PWM interrupt flags which are set by hardware when the corresponding PWM period counter comparison matched period and duty. Each PWM interrupt source with its corresponding enable bit can request PWM interrupt. The PWM generators can be configured as One-shot mode to produce only one PWM cycle signal or Auto-reload mode to output PWM waveform continuously.

To prevent PWM driving output pin with unsteady waveform, the 16-bit period down counter and 16-bit comparator are implemented with double buffer. When user writes data to counter/comparator buffer registers, the updated value will be loaded into the 16-bit down counter/ comparator at the end of current period. The double buffering feature avoids glitch at PWM outputs.

Besides PWM, Motor controlling also need Timer, ACMP and ADC to work together. In order to control motor more precisely, we provide some registers that not only configure PWM but also Timer, ADC and ACMP, by doing so, it can save more CPU time and control motor with ease especially in BLDC.

### 6.10.2 Features

The PWM unit supports the following features:

- Independent 16-bit PWM duty control units with maximum six port pins:

- Six independent PWM outputs PWM0, PWM1, PWM2, PWM3, PWM4, and PWM5

- Three complementary PWM pairs, with each pin in a pair mutually complement to each other and capable of programmable dead-zone insertion – (PWM0, PWM1), (PWM2, PWM3) and (PWM4, PWM5)

- Three synchronous PWM pairs, with each pin in a pair in-phase (PWM0, PWM1), (PWM2, PWM3) and (PWM4, PWM5)

- Group control bit PWM2 and PWM4 are synchronized with PWM0, PWM3 and PWM5 are synchronized with PWM1

- One-shot (only support edge alignment mode) or Auto-reload mode PWM

- Up to 16-bit resolution

- Supports Edge-aligned and Center-aligned mode

- Programmable dead-zone insertion between complementary paired PWMs

- Each pin of PWM0 to PWM5 has independent polarity setting control

- Hardware fault brake protections

- Two Interrupt source types:

- Synchronously requested at PWM frequency when down counter comparison matched (edge- and center-aligned mode) or underflow (edgealigned mode)

- Requested when external fault brake asserted

- BKP0: EINT0 or CPO1

- ♦ BKP1: EINT1 or CPO0

- The PWM signals before polarity control stage are defined in the view of positive logic. The PWM ports is active high or active low are controlled by polarity control register.

- Supports independently rising CMR matching (in Center-aligned mode), CNR matching (in Center-aligned mode), falling CMR matching, period matching to trigger ADC conversion

- Timer comparing matching event trigger PWM to do phase change in BLDC application

- Supports ACMP output event trigger PWM to force PWM output at most one period low, this feature is usually for step motor control

- Provides interrupt accumulation function

### 7 ARM® CORTEX<sup>™</sup>-M0 CORE

### 7.1 Overview

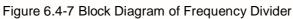

The Cortex<sup>™</sup>-M0 processor is a configurable, multistage, 32-bit RISC processor which has an AMBA AHB-Lite interface and includes an NVIC component. It also has optional hardware debug functionality. The processor can execute Thumb code and is compatible with other Cortex<sup>TM</sup>-M profile processors. The profile supports two modes - Thread mode and Handler mode. Handler mode is entered as a result of an exception. An exception return can only be issued in Handler mode. Thread mode is entered on Reset and can be entered as a result of an exception return. The following figure shows the functional controller of the processor.

Figure 7.1-1 Functional Block Diagram

### 7.2 Features

- A low gate count processor

- ARMv6-M Thumb<sup>®</sup> instruction set

- Thumb-2 technology

- ARMv6-M compliant 24-bit SysTick timer

- A 32-bit hardware multiplier

- System interface supported with little-endian data accesses

- Ability to have deterministic, fixed-latency, interrupt handling

- Load/store-multiples and multicycle-multiplies that can be abandoned and restarted to facilitate rapid interrupt handling

- C Application Binary Interface compliant exception model:

- This is the ARMv6-M, C Application Binary Interface (C-ABI) compliant exception model that enables the use of pure C functions as interrupt handlers

- Low power Idle mode entry using the Wait For Interrupt (WFI), Wait For Event (WFE) instructions, or return from interrupt sleep-on-exit feature

- NVIC

|                  |                                   |   |       | 100  |     | V <sub>DD</sub>        | 5.5V                 |   |

|------------------|-----------------------------------|---|-------|------|-----|------------------------|----------------------|---|

| I <sub>DD2</sub> |                                   | - | 7.0   | 22   | mA  | HXT                    | 24 MHz               |   |

|                  |                                   |   | 8     | m As |     | HIRC                   | Disabled<br>Disabled | - |

|                  | _                                 |   |       |      |     | All digital modules    | Disabled             |   |

|                  |                                   |   |       | S22  | 25  | M                      | 3.3V                 |   |

|                  |                                   |   |       | X    | 8   | V <sub>DD</sub><br>HXT | 3.3V<br>24 MHz       |   |

| I <sub>DD3</sub> |                                   | - | 7.1   |      | mA  | HIRC                   | Disable              |   |

|                  |                                   |   |       |      | -27 | All digital            | Enabled              |   |

|                  | -                                 |   |       |      |     | modules                | Lindbied             |   |

|                  |                                   |   |       |      |     | V <sub>DD</sub>        | 3.3 V                |   |

|                  |                                   |   |       |      |     | HXT                    | 24 MHz               |   |

| I <sub>DD4</sub> |                                   | - | 5.0   | -    | mA  | HIRC                   | Disabled             |   |

|                  |                                   |   |       |      |     | All digital            | Disabled             |   |

|                  |                                   |   |       |      |     | modules                | Disabied             |   |

|                  |                                   |   |       | -    |     |                        |                      |   |

|                  |                                   |   | 6.1   |      |     | V <sub>DD</sub>        | 5.5V                 | - |

| I <sub>DD5</sub> |                                   | - |       |      | mA  | HXT                    | Disabled             |   |

|                  |                                   |   |       |      |     | HIRC                   | Enabled              |   |

|                  |                                   |   |       |      |     | All digital modules    | Enabled              |   |

|                  |                                   |   |       |      |     | V <sub>DD</sub>        | 5.5V                 |   |

|                  |                                   |   | 3.9   |      | mA  | HXT                    | Disabled             |   |

| I <sub>DD6</sub> | Operating Current                 | - |       | -    |     | HIRC                   | Enabled              |   |

|                  | Normal Run Mode                   |   |       |      |     | All digital            | Disabled             |   |

|                  | HCLK =22.1184<br>MHz              |   |       |      |     | modules                |                      |   |

|                  | while(1){}<br>Executed from Flash |   | - 6.0 | -    | mA  | V <sub>DD</sub>        | 3.3V                 |   |

| 1                |                                   | _ |       |      |     | HXT                    | Disabled             |   |

| I <sub>DD7</sub> |                                   | - |       |      |     | HIRC                   | Enabled              |   |

| SX.              |                                   |   |       |      |     | All digital modules    | Enabled              |   |

| 2.33             | -                                 |   |       |      |     | V <sub>DD</sub>        | 3.3V                 |   |

| UN.              | 3                                 |   | 3.9   |      | mA  | HXT                    | Disabled             |   |

| I <sub>DD8</sub> | 40.                               | - | 3.9   | -    | mA  | HIRC                   | Enabled              |   |

| K                | AL                                |   |       |      |     | All digital modules    | Disabled             |   |

|  |                     |                                |   |       |          |       | V <sub>DD</sub>        | 5.5 V    |  |

|--|---------------------|--------------------------------|---|-------|----------|-------|------------------------|----------|--|

|  |                     |                                |   | 4.4   | 32.      |       | HXT                    | 12 MHz   |  |

|  | I <sub>IDLE9</sub>  |                                | - |       | ~~~      | mA    | HIRC                   | Disabled |  |

|  |                     |                                |   |       | China Co |       | All digital<br>modules | Enabled  |  |

|  |                     | -                              |   |       |          | 261   |                        |          |  |

|  |                     |                                |   |       | 100      | . X   | V <sub>DD</sub>        | 5.5 V    |  |

|  | I <sub>IDLE10</sub> |                                | - | 3.3   | - X      | mA    | HXT                    | 12 MHz   |  |

|  |                     |                                |   |       |          | (CS)  | HIRC                   | Disabled |  |

|  |                     | Operating Current<br>Idle Mode |   |       |          | 4     | All digital modules    | Disabled |  |

|  |                     | HCLK =12 MHz                   |   |       |          |       |                        |          |  |

|  |                     |                                |   |       |          |       | V <sub>DD</sub>        | 3.3 V    |  |

|  | I <sub>IDLE11</sub> |                                | - | 2.9   | -        | mA    | HXT                    | 12 MHz   |  |

|  |                     |                                |   |       |          |       | HIRC                   | Disabled |  |

|  |                     | _                              |   |       |          |       | All digital modules    | Enabled  |  |

|  |                     |                                |   |       | -        | mA    |                        |          |  |

|  | I <sub>IDLE12</sub> |                                | - | 1.8   |          |       | V <sub>DD</sub>        | 3.3 V    |  |

|  |                     |                                |   |       |          |       | HXT                    | 12 MHz   |  |

|  |                     |                                |   |       |          |       | HIRC                   | Disabled |  |

|  |                     |                                |   |       |          |       | All digital modules    | Disabled |  |

|  |                     |                                |   | - 2.9 | _        | mA    | V <sub>DD</sub>        | 5.5 V    |  |

|  | I <sub>IDLE13</sub> |                                | _ |       |          |       | HXT                    | 4 MHz    |  |

|  | IDLE 13             |                                |   |       |          | 110 ( | HIRC                   | Disabled |  |

|  |                     |                                |   |       |          |       | All digital modules    | Enabled  |  |

|  |                     | Operating Current<br>Idle Mode | - | 2.5   | -        | mA    | V <sub>DD</sub>        | 5.5 V    |  |

|  |                     |                                |   |       |          |       | HXT                    | 4 MHz    |  |

|  | I <sub>IDLE14</sub> | HCLK =4 MHz                    |   |       |          |       | HIRC                   | Disabled |  |

|  | Ş.,                 |                                |   |       |          |       | All digital modules    | Disabled |  |

|  | 2.33                |                                |   |       |          |       | V <sub>DD</sub>        | 3.3 V    |  |

|  | 23                  | 3                              |   | . –   |          |       | HXT                    | 4 MHz    |  |

|  | I <sub>IDLE15</sub> | 00                             | - | 1.5   | -        | mA    | HIRC                   | Disabled |  |

|  | N                   | AL.                            |   |       |          |       | All digital<br>modules | Enabled  |  |

|                     |                                                                      |            |                     | 1000     |      | V <sub>DD</sub>                                       | 3.3 V                          |  |

|---------------------|----------------------------------------------------------------------|------------|---------------------|----------|------|-------------------------------------------------------|--------------------------------|--|

| I <sub>IDLE16</sub> |                                                                      | -          | 1.1                 | X        | mA   | HXT                                                   | 4 MHz                          |  |

| IDLE16              |                                                                      |            | 1.1                 | mr.      |      | HIRC                                                  | Disabled                       |  |

|                     |                                                                      |            | All digital modules | Disabled |      |                                                       |                                |  |

|                     |                                                                      |            |                     | - SU     | 2    | V <sub>DD</sub>                                       | 5.5 V                          |  |

|                     |                                                                      |            |                     | X        | 0    | HXT                                                   | Disabled                       |  |

|                     |                                                                      |            |                     |          | No.  | HIRC                                                  | Disabled                       |  |

| I <sub>IDLE17</sub> |                                                                      | -          | 225                 | -        | μA   | LIRC                                                  | Enabled                        |  |

|                     |                                                                      |            |                     |          |      | All digital<br>modules                                | Enabled                        |  |

|                     |                                                                      |            |                     |          |      |                                                       | ules which support 1<br>source |  |

|                     |                                                                      |            |                     |          |      | 17                                                    | 190                            |  |

|                     |                                                                      |            |                     |          |      | V <sub>DD</sub>                                       | 5.5 V                          |  |

|                     |                                                                      |            |                     |          |      | HXT                                                   | Disabled                       |  |

| IDLE18              | - 225 -                                                              | μA         | HIRC                | Disabled |      |                                                       |                                |  |

|                     |                                                                      |            |                     |          |      | LIRC                                                  | Enabled                        |  |

|                     | Operating Current<br>Idle Mode                                       |            |                     |          |      | All digital modules                                   | Disabled                       |  |

|                     | at 10 kHz                                                            |            |                     |          |      |                                                       | 0.01/                          |  |

|                     |                                                                      |            |                     |          |      | V <sub>DD</sub>                                       | 3.3 V                          |  |

|                     |                                                                      |            |                     |          |      | HXT                                                   | Disabled                       |  |

| I <sub>IDLE19</sub> |                                                                      | - 200 - 4  | 200 - μA            | μA       | HIRC | Disabled                                              |                                |  |

|                     |                                                                      |            |                     |          |      |                                                       | Enabled                        |  |

|                     |                                                                      |            |                     |          |      | All digital modules                                   | Enabled                        |  |

|                     |                                                                      |            |                     |          |      | Only enable mod<br>kHz LIRC clock s                   | ules which support 1<br>ource  |  |

|                     |                                                                      |            |                     |          |      | V <sub>DD</sub>                                       | 3.3 V                          |  |

|                     |                                                                      |            |                     |          |      | HXT                                                   | Disabled                       |  |

| I <sub>IDLE20</sub> |                                                                      | -          | 200                 | -        | μA   | HIRC                                                  | Disabled                       |  |

|                     |                                                                      |            |                     |          |      | LIRC                                                  | Enabled                        |  |

|                     |                                                                      |            |                     |          |      | All digital<br>modules                                | Disabled                       |  |

| I <sub>PWD1</sub>   | Standby Current<br>Power-down Mode                                   | -          | 10                  | -        | μΑ   |                                                       | cillators and analog           |  |

| I <sub>PWD2</sub>   | (Deep Sleep Mode)                                                    | -          | 9                   | -        | μA   | V <sub>DD</sub> = 3.3 V, All os<br>blocks turned off. | cillators and analog           |  |

| IL                  | Logic 0 Input Current<br>P0/1/2/3/4/5 (Quasi-<br>bidirectional Mode) | <u>.</u> - | -70                 | -75      | μΑ   | $V_{DD} = 5.5 \text{ V}, V_{IN} = 0 \text{ V}$        |                                |  |

| I <sub>SK13</sub> | Drain and Push-pull<br>Mode) | 5 | 8 | -   | mA | $V_{DD} = 2.5 \text{ V}, V_S = 0.45 \text{ V}$ |

|-------------------|------------------------------|---|---|-----|----|------------------------------------------------|

|                   | -                            |   |   | . 2 |    |                                                |

Notes:

- 1. /RESET pin is a Schmitt trigger input.

- 2. XTAL1 is a CMOS input.

3. Pins of P0, P1, P2, P3, P4 and P5 can source a transition current when they are being externally driven from 1 to 0. In the condition of VDD=5.5V, the transition current reaches its maximum value when VIN approximates to 2V.

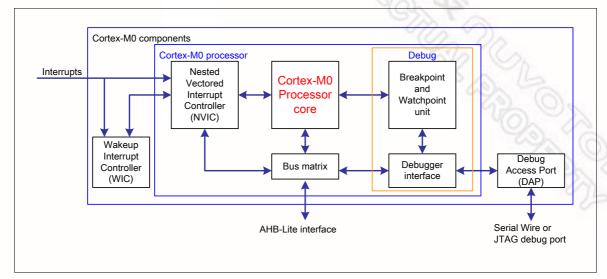

### 9.3 AC Electrical Characteristics

### 9.3.1 External Input Clock

Note: Duty cycle is 50%.

| Symbol            | Parameter       | Min | Тур | Мах | Unit | Test Conditions |

|-------------------|-----------------|-----|-----|-----|------|-----------------|

| t <sub>CHCX</sub> | Clock High Time | 10  | -   | -   | ns   | -               |

| t <sub>CLCX</sub> | Clock Low Time  | 10  | -   | -   | ns   | -               |

| t <sub>CLCH</sub> | Clock Rise Time | 2   | -   | 15  | ns   | -               |

| t <sub>CHCL</sub> | Clock Fall Time | 2   | -   | 15  | ns   | -               |

### 9.3.2 External 4~24 MHz High Speed Crystal (HXT)

| Symbol           | Parameter         | Min. | Тур. | Max | Unit | Test Conditions                |

|------------------|-------------------|------|------|-----|------|--------------------------------|

| V <sub>HXT</sub> | Operation Voltage | 2.5  | -    | 5.5 | V    | -                              |

| T <sub>A</sub>   | Temperature       | -40  | -    | 105 | °C   | -                              |

| I <sub>HXT</sub> | Operating Current | -    | 2.5  | -   | mA   | 12 MHz, V <sub>DD</sub> = 5.5V |

| HXT              | Operating Current | -    | 1.0  | -   | mA   | 12 MHz, $V_{DD} = 3.3V$        |

| f <sub>HXT</sub> | Clock Frequency   | 4    | -    | 24  | MHz  | -                              |

### 9.4.2 LDO & Power Management

| Symbol           | Parameter       | Min  | Тур | Max  | Unit | Test Condition |

|------------------|-----------------|------|-----|------|------|----------------|

| V <sub>DD</sub>  | DC Power Supply | 2.5  | -   | 5.5  | V    | -              |

| V <sub>LDO</sub> | Output Voltage  | 1.62 | 1.8 | 1.98 | V    | -              |

| T <sub>A</sub>   | Temperature     | -40  | 25  | 105  | °C   |                |

Notes:

1. It is recommended a  $0.1\mu F$  bypass capacitor is connected between  $V_{DD}$  and the closest  $V_{SS}$  pin of the device.

## 9.4.3 Low Voltage Reset

| Symbol           | Parameter      | Min | Тур | Мах | Unit | Test Condition |

|------------------|----------------|-----|-----|-----|------|----------------|

| AV <sub>DD</sub> | Supply Voltage | 0   | -   | 5.5 | V    | -              |

| T <sub>A</sub>   | Temperature       | -40  | 25   | 105  | °C | -                     |

|------------------|-------------------|------|------|------|----|-----------------------|

| I <sub>LVR</sub> | Quiescent Current | -    | 1    | 5    | μA | $AV_{DD} = 5.5V$      |

| V <sub>LVR</sub> | Threshold Voltage | 1.90 | 2.00 | 2.10 | V  | T <sub>A</sub> =25°C  |

|                  |                   | 1.70 | 1.90 | 2.05 | V  | T <sub>A</sub> =-40°C |

|                  |                   | 2.00 | 2.20 | 2.45 | V  | T <sub>A</sub> =105°C |

### 9.4.4 Brown-out Detector

| Symbol           | Parameter                            | Min | Тур  | Max  | Unit | Test Condition         |

|------------------|--------------------------------------|-----|------|------|------|------------------------|

| $AV_{DD}$        | Supply Voltage                       | 0   | -    | 5.5  | V    | 25                     |

| T <sub>A</sub>   | Temperature                          | -40 | 25   | 105  | °C   | 22-02                  |

| I <sub>BOD</sub> | Quiescent Current                    | -   | -    | 140  | μA   | AV <sub>DD</sub> =5.5V |

|                  | Brown-out Detector<br>(Falling edge) | 4.2 | 4.38 | 4.55 | V    | BOD_VL [1:0]=11        |

| V <sub>BOD</sub> |                                      | 3.5 | 3.68 | 3.85 | V    | BOD_VL [1:0]=10        |

| ▲ BOD            |                                      | 2.5 | 2.68 | 2.85 | V    | BOD_VL [1:0]=01        |

|                  |                                      | 2.0 | 2.18 | 2.35 | V    | BOD_VL [1:0]=00        |

|                  | Brown-out Detector<br>(Rising edge)  | 4.3 | 4.52 | 4.75 | V    | BOD_VL [1:0]=11        |

| V <sub>BOD</sub> |                                      | 3.5 | 3.8  | 4.05 | V    | BOD_VL [1:0]=10        |

| A ROD            |                                      | 2.5 | 2.77 | 3.05 | V    | BOD_VL [1:0]=01        |

|                  |                                      | 2.0 | 2.25 | 2.55 | V    | BOD_VL [1:0]=00        |

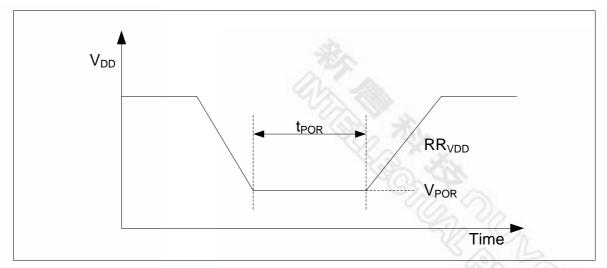

### 9.4.5 Power-on Reset

| Symbol            | Parameter                                                                      | Min   | Тур | Max | Unit | Test Condition |

|-------------------|--------------------------------------------------------------------------------|-------|-----|-----|------|----------------|

| T <sub>A</sub>    | Temperature                                                                    | -40   | 25  | 105 | °C   | -              |

| V <sub>POR</sub>  | Reset Voltage                                                                  | 1.6   | 2   | 2.4 | V    | -              |

| V <sub>POR</sub>  | V <sub>DD</sub> Start Voltage to Ensure<br>Power-on Reset                      | -     | -   | 100 | mV   |                |

| RR <sub>VDD</sub> | V <sub>DD</sub> Raising Rate to Ensure<br>Power-on Reset                       | 0.025 | -   | -   | V/ms |                |

| t <sub>POR</sub>  | Minimum Time for V <sub>DD</sub> Stays<br>at VPOR to Ensure Power-<br>on Reset | 0.5   | -   | -   | ms   |                |

Figure 9-2Power-up Ramp Condition

## 9.4.6 Comparator

| Symbol           | Parameter               | Min | Тур | Max                     | Unit | Test Condition                                       |

|------------------|-------------------------|-----|-----|-------------------------|------|------------------------------------------------------|

| V <sub>CMP</sub> | Supply Voltage          | 2.5 | -   | 5.5                     | V    |                                                      |

| T <sub>A</sub>   | Temperature -40         |     | 25  | 105                     | °C   | -                                                    |

| I <sub>CMP</sub> | Operation Current       | -   | 40  | 80                      | μA   | AV <sub>DD</sub> =5V                                 |

| $V_{OFF}$        | Input Offset Voltage    |     | 10  | 20                      | mV   | -                                                    |

| V <sub>SW</sub>  | Output Swing            | 0.1 | -   | AV <sub>DD</sub> -0.1   | V    | -                                                    |

| V <sub>COM</sub> | Input Common Mode Range | 0.1 | -   | AV <sub>DD</sub> - 0.1  | V    | -                                                    |

| -                | DC Gain                 | 40  | 70  | -                       | dB   | -                                                    |

| T <sub>PGD</sub> | Propagation Delay       | -   | 200 | -                       | ns   | V <sub>COM</sub> =1.2 V,<br>V <sub>DIFF</sub> =0.1 V |

| V <sub>HYS</sub> | Hysteresis - ±30 ±60 mV |     | mV  | V <sub>COM</sub> =1.2 V |      |                                                      |

| T <sub>STB</sub> | Stable time             | -   | -   | 1                       | μs   |                                                      |