#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIL                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ed2-3csum |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

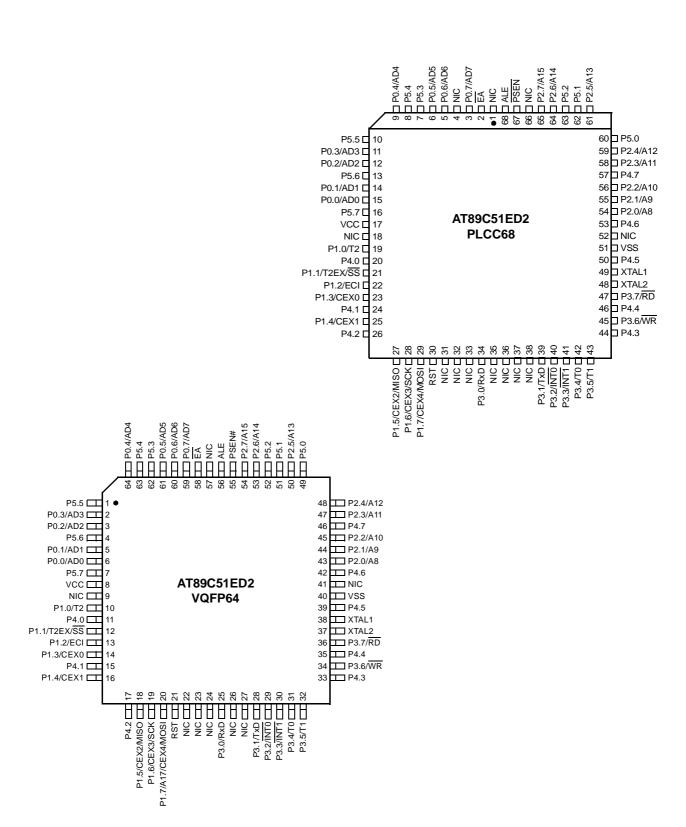

NIC: Not Internaly Connected

useful if external peripherals are mapped at addresses already used by the internal XRAM.

- With <u>EXTRAM = 0</u>, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 (WR) and P3.7 (RD). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than the accessible size of the XRAM will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Accesses to XRAM above 0FFH can only be done by the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @Ri and MOVX @DPTR will be similar to the standard 80C51.MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the high-order eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ Ri and MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

The M0 bit allows to stretch the XRAM timings; if M0 is set, the read and write pulses are extended from 6 to 30 clock periods. This is useful to access external slow peripherals.

### Registers

### Table 19. AUXR Register

AUXR - Auxiliary Register (8Eh)

| 7             | 6               | 5                                                                                                                                                                                                                                            | 4                                                                                                                                                                                                      | 3                                                       | 2              | 1            | 0  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------|--------------|----|--|

| DPU           | -               | МО                                                                                                                                                                                                                                           | XRS2                                                                                                                                                                                                   | XRS1                                                    | XRS0           | EXTRAM       | AO |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                  |                                                                                                                                                                                                        |                                                         |                |              |    |  |

| 7             | DPU             | Cleared by s                                                                                                                                                                                                                                 | Disable Weak Pull-up<br>Cleared by software to activate the permanent weak pull-up (default)<br>Set by software to disable the weak pull-up (reduce power consumption)                                 |                                                         |                |              |    |  |

| 6             | -               | Reserved<br>The value re                                                                                                                                                                                                                     | ad from this                                                                                                                                                                                           | bit is indetermir                                       | nate. Do not s | et this bit. |    |  |

| 5             | MO              | Pulse lengthCleared to stretch MOVX control: the $\overline{RD}$ and the $\overline{WR}$ pulse length is 6 clockperiods (default).Set to stretch MOVX control: the $\overline{RD}$ and the $\overline{WR}$ pulse length is 30 clock periods. |                                                                                                                                                                                                        |                                                         |                |              |    |  |

| 4             | XRS2            | XRAM Size                                                                                                                                                                                                                                    |                                                                                                                                                                                                        |                                                         |                |              |    |  |

| 3             | XRS1            | <u>XRS2</u> <u>XR</u><br>0 0                                                                                                                                                                                                                 | <u>8S1</u> <u>XRS0</u><br>0                                                                                                                                                                            | <u>XRAM size</u><br>256 bytes                           |                |              |    |  |

| 2             | XRS0            | 0 0<br>0 1<br>0 1<br>1 0                                                                                                                                                                                                                     | 1<br>0<br>1<br>0                                                                                                                                                                                       | 512 bytes<br>768 bytes(defa<br>1024 bytes<br>1792 bytes | ault)          |              |    |  |

| 1             | EXTRAM          | EXTRAM bit<br>Cleared to access internal XRAM using movx @ Ri/ @ DPTR.<br>Set to access external memory.<br>Programmed by hardware after Power-up regarding Hardware Security Byte<br>(HSB), default setting, XRAM selected.                 |                                                                                                                                                                                                        |                                                         |                |              |    |  |

| 0             | AO              | Cleared, ALE<br>X2 mode is u                                                                                                                                                                                                                 | ALE Output bit<br>Cleared, ALE is emitted at a constant rate of 1/6 the oscillator frequency (or 1/3 if X2 mode is used). (default) Set, ALE is active only during a MOVX or MOVC instruction is used. |                                                         |                |              |    |  |

Reset Value = 0X00 10'HSB. XRAM'0b Not bit addressable

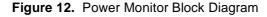

### **Power Monitor**

The POR/PFD function monitors the internal power-supply of the CPU core memories and the peripherals, and if needed, suspends their activity when the internal power supply falls below a safety threshold. This is achieved by applying an internal reset to them.

By generating the Reset the Power Monitor insures a correct start up when AT89C51RD2/ED2 is powered up.

**Description** In order to startup and maintain the microcontroller in correct operating mode, V<sub>CC</sub> has to be stabilized in the V<sub>CC</sub> operating range and the oscillator has to be stabilized with a nominal amplitude compatible with logic level VIH/VIL.

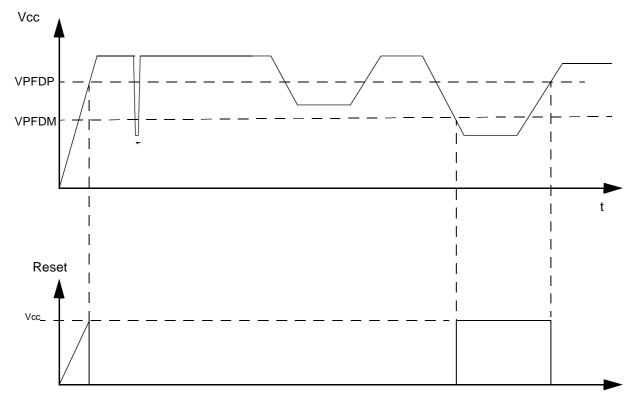

These parameters are controlled during the three phases: power-up, normal operation and power going down. See Figure 12.

Note: 1. Once XTAL1 High and low levels reach above and below VIH/VIL. a 1024 clock period delay will extend the reset coming from the Power Fail Detect. If the power falls below the Power Fail Detect threshold level, the Reset will be applied immediately.

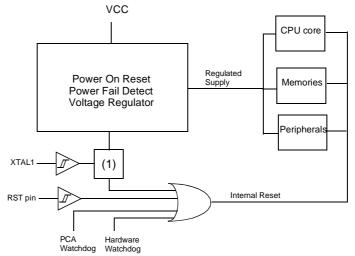

The Voltage regulator generates a regulated internal supply for the CPU core the memories and the peripherals. Spikes on the external Vcc are smoothed by the voltage regulator.

The Power fail detect monitor the supply generated by the voltage regulator and generate a reset if this supply falls below a safety threshold as illustrated in the Figure 13 below.

When the power is applied, the Power Monitor immediately asserts a reset. Once the internal supply after the voltage regulator reach a safety level, the power monitor then looks at the XTAL clock input. The internal reset will remain asserted until the Xtal1 levels are above and below VIH and VIL. Further more. An internal counter will count 1024 clock periods before the reset is de-asserted.

If the internal power supply falls below a safety level, a reset is immediately asserted.

| Timer 2          | The Timer 2 in the AT89C51RD2/ED2 is the standard C52 Timer 2. It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2 are cascaded. It is controlled by T2CON (Table 20) and T2MOD (Table 21) registers. Timer 2 operation is similar to Timer 0 and Timer 1. $C/T2$ selects $F_{OSC}/12$ (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to increment by the selected input. |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).                                                                                                                                                                                                                                                                                                                            |

|                  | Refer to the Atmel 8-bit Microcontroller Hardware Manual for the description of Capture and Baud Rate Generator Modes.                                                                                                                                                                                                                                                                                                                                                               |

|                  | Timer 2 includes the following enhancements:                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  | Auto-reload mode with up or down counter                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                  | Programmable clock-output                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Auto-reload Mode | The auto-reload mode configures Timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. If DCEN bit in T2MOD is cleared, Timer 2 behaves as in 80C52 (refer to<br>the Atmel C51 Microcontroller Hardware Manual). If DCEN bit is set, Timer 2 acts as an<br>Up/down timer/counter as shown in Figure 14. In this mode the T2EX pin controls the<br>direction of count.                                                                                                |

|                  | When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                                                                                         |

|                  | When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                                                                                      |

|                  | The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.                                                                                                                                                                                                                                                                                          |

#### Table 23. CCON Register

CCON - PCA Counter Control Register (D8h)

| 7             | 6               | 5                                                                                                              | 4                                                                                                                                                                                                                  | 3               | 2              | 1            | 0    |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|------|--|

| CF            | CR              | -                                                                                                              | CCF4                                                                                                                                                                                                               | CCF3            | CCF2           | CCF1         | CCF0 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                    |                                                                                                                                                                                                                    |                 |                |              |      |  |

| 7             | CF              | Set by hardw<br>CMOD is set                                                                                    | PCA Counter Overflow flag<br>Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in<br>CMOD is set. CF<br>may be set by either hardware or software but can only be cleared by software. |                 |                |              |      |  |

| 6             | CR              | Must be clea                                                                                                   | PCA Counter Run control bit<br>Must be cleared by software to turn the PCA counter off.<br>Set by software to turn the PCA counter on.                                                                             |                 |                |              |      |  |

| 5             | -               | Reserved<br>The value re                                                                                       | ad from this b                                                                                                                                                                                                     | it is indetermi | nate. Do not s | et this bit. |      |  |

| 4             | CCF4            | Must be clea                                                                                                   | <b>e 4 interrupt</b> f<br>red by softwa<br>vare when a n                                                                                                                                                           | •               | re occurs.     |              |      |  |

| 3             | CCF3            | Must be clea                                                                                                   | PCA Module 3 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs.                                                                                                     |                 |                |              |      |  |

| 2             | CCF2            | PCA Module 2 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs. |                                                                                                                                                                                                                    |                 |                |              |      |  |

| 1             | CCF1            | PCA Module 1 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs. |                                                                                                                                                                                                                    |                 |                |              |      |  |

| 0             | CCF0            | Must be clea                                                                                                   | e 0 interrupt f<br>red by softwa<br>vare when a n                                                                                                                                                                  | •               | re occurs.     |              |      |  |

Reset Value = 00X0 0000b Bit addressable

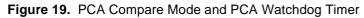

The watchdog timer function is implemented in Module 4 (See Figure 19).

The PCA interrupt system is shown in Figure 17.

Table 24 shows the CCAPMn settings for the various PCA functions.

#### Table 24. CCAPMn Registers (n = 0-4)

CCAPM0 - PCA Module 0 Compare/Capture Control Register (0DAh)

CCAPM1 - PCA Module 1 Compare/Capture Control Register (0DBh)

- CCAPM2 PCA Module 2 Compare/Capture Control Register (0DCh)

- CCAPM3 PCA Module 3 Compare/Capture Control Register (0DDh)

CCAPM4 - PCA Module 4 Compare/Capture Control Register (0DEh)

| 7             | 6               | 5                                | 4                                                                                                                                                                                               | 3                                | 2              | 1            | 0         |  |

|---------------|-----------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|--------------|-----------|--|

| -             | ECOMn           | CAPPn                            | CAPNn                                                                                                                                                                                           | MATn                             | TOGn           | PWMn         | ECCFn     |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                      |                                                                                                                                                                                                 |                                  |                |              |           |  |

| 7             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                                                                                                  | it is indetermir                 | nate. Do not s | et this bit. |           |  |

| 6             | ECOMn           | Cleared to di                    | Enable Comparator<br>Cleared to disable the comparator function.<br>Set to enable the comparator function.                                                                                      |                                  |                |              |           |  |

| 5             | CAPPn           | Cleared to di                    | Capture Positive<br>Cleared to disable positive edge capture.<br>Set to enable positive edge capture.                                                                                           |                                  |                |              |           |  |

| 4             | CAPNn           |                                  |                                                                                                                                                                                                 | e edge captur<br>ge capture.     | e.             |              |           |  |

| 3             | MATn            |                                  |                                                                                                                                                                                                 | of the PCA co<br>causes the CC   |                |              | agging an |  |

| 2             | TOGn            |                                  | ,                                                                                                                                                                                               | of the PCA co<br>causes the CE   |                |              |           |  |

| 1             | PWMn            | Cleared to di                    | <b>Pulse Width Modulation Mode</b><br>Cleared to disable the CEXn pin to be used as a pulse width modulated output.<br>Set to enable the CEXn pin to be used as a pulse width modulated output. |                                  |                |              |           |  |

| 0             | CCF0            | an interrupt.                    | sable compar                                                                                                                                                                                    | e/capture flag<br>oture flag CCF |                | -            | -         |  |

Reset Value = X000 0000b Not bit addressable

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen. Writing to CCAPnH will set the ECOM bit.

Once ECOM is set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

#### **High Speed Output Mode** In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the modules capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (See Figure 20).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

### **Keyboard Interface**

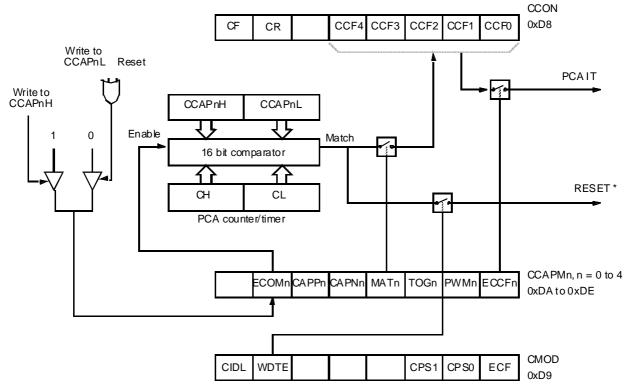

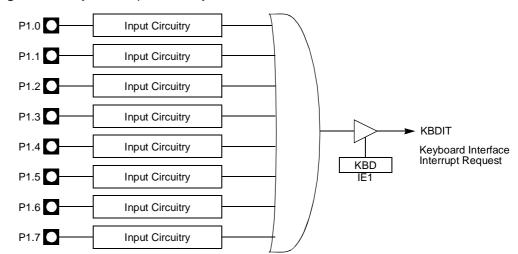

The AT89C51RD2/ED2 implements a keyboard interface allowing the connection of a 8 x n matrix keyboard. It is based on 8 inputs with programmable interrupt capability on both high or low level. These inputs are available as alternate function of P1 and allow to exit from idle and power-down modes.

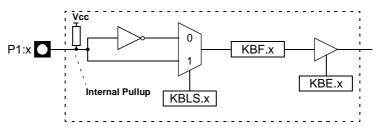

The keyboard interfaces with the C51 core through 3 special function registers: KBLS, the Keyboard Level Selection register (Table 45), KBE, the Keyboard interrupt Enable register (Table 44), and KBF, the Keyboard Flag register (Table 43).

Interrupt The keyboard inputs are considered as 8 independent interrupt sources sharing the same interrupt vector. An interrupt enable bit (KBD in IE1) allows global enable or disable of the keyboard interrupt (see Figure 27). As detailed in Figure 28 each keyboard input has the capability to detect a programmable level according to KBLS. x bit value. Level detection is then reported in interrupt flags KBF.x that can be masked by software using KBE. x bits.

This structure allow keyboard arrangement from 1 by n to 8 by n matrix and allows usage of P1 inputs for other purpose.

Figure 28. Keyboard Input Circuitry

#### **Power Reduction Mode**

P1 inputs allow exit from idle and power-down modes as detailed in Section "Power Management", page 82.

### Table 45. KBLS Register

KBLS-Keyboard Level Selector Register (9Ch)

| 7             | 6               | 5                                                                                                                                                             | 4                                                                                                                                                             | 3                                                  | 2     | 1     | 0     |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------|-------|-------|

| KBLS7         | KBLS6           | KBLS5                                                                                                                                                         | KBLS4                                                                                                                                                         | KBLS3                                              | KBLS2 | KBLS1 | KBLS0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                   |                                                                                                                                                               |                                                    |       |       |       |

| 7             | KBLS7           | Cleared to en                                                                                                                                                 |                                                                                                                                                               | election bit<br>vel detection on<br>detection on P |       |       |       |

| 6             | KBLS6           | Cleared to en                                                                                                                                                 |                                                                                                                                                               | election bit<br>vel detection on<br>detection on P |       |       |       |

| 5             | KBLS5           | Cleared to en                                                                                                                                                 | <b>Keyboard line 5 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 5.<br>Set to enable a high level detection on Port line 5. |                                                    |       |       |       |

| 4             | KBLS4           | Cleared to en                                                                                                                                                 | <b>Keyboard line 4 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 4.<br>Set to enable a high level detection on Port line 4. |                                                    |       |       |       |

| 3             | KBLS3           | Cleared to en                                                                                                                                                 | <b>Keyboard line 3 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 3.<br>Set to enable a high level detection on Port line 3. |                                                    |       |       |       |

| 2             | KBLS2           | Cleared to en                                                                                                                                                 | <b>Keyboard line 2 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 2.<br>Set to enable a high level detection on Port line 2. |                                                    |       |       |       |

| 1             | KBLS1           | <b>Keyboard line 1 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 1.<br>Set to enable a high level detection on Port line 1. |                                                                                                                                                               |                                                    |       |       |       |

| 0             | KBLS0           | Cleared to en                                                                                                                                                 |                                                                                                                                                               | election bit<br>vel detection on<br>detection on P |       |       |       |

Reset Value = 0000 0000b

| Error Conditions         | The following flags in the SPSTA signal SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | error conditions:                                                                                                                                                                     |  |  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Mode Fault (MODF)        | Node Fault error in Master mode SPI indicates that the level on the Slave Select (SS<br>in is inconsistent with the actual mode of the device. MODF is set to warn that then<br>hay be a multi-master conflict for system control. In this case, the SPI system<br>ffected in the following ways:<br>An SPI receiver/error CPU interrupt request is generated<br>The SPEN bit in SPCON is cleared. This disables the SPI<br>The MSTR bit in SPCON is cleared<br>When SS Disable (SSDIS) bit in the SPCON register is cleared, the MODF flag is so<br>when the SS signal becomes '0'. |                                                                                                                                                                                       |  |  |  |

|                          | However, as stated before, for a system with one Master, if the $\overline{SS}$ pin of the Master device is pulled low, there is no way that another Master attempts to drive the network. In this case, to prevent the MODF flag from being set, software can set the SSDIS bit in the SPCON register and therefore making the $\overline{SS}$ pin as a general-purpose I/O pin.                                                                                                                                                                                                    |                                                                                                                                                                                       |  |  |  |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | a read of SPSTA register with MODF bit set,<br>SPEN Control bit may be restored to its orig-<br>leared.                                                                               |  |  |  |

| Write Collision (WCOL)   | A Write Collision (WCOL) flag in the SPSTA done during a transmit sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | is set when a write to the SPDAT register is                                                                                                                                          |  |  |  |

|                          | WCOL does not cause an interruption, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | the transfer continues uninterrupted.                                                                                                                                                 |  |  |  |

|                          | Clearing the WCOL bit is done through a sand an access to SPDAT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | software sequence of an access to SPSTA                                                                                                                                               |  |  |  |

| Overrun Condition        | and the Slave devise has not cleared the S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ster device tries to send several data Bytes<br>SPIF bit issuing from the previous data Byte<br>contains the Byte sent after the SPIF bit was<br>his Byte. All others Bytes are lost. |  |  |  |

|                          | This condition is not detected by the SPI pe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ripheral.                                                                                                                                                                             |  |  |  |

| SS Error Flag (SSERR)    | A Synchronous Serial Slave Error occurs when $\overline{SS}$ goes high before the end of a received data in slave mode. SSERR does not cause in interruption, this bit is cleared by writing 0 to SPEN bit (reset of the SPI state machine).                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                       |  |  |  |

| Interrupts               | Two SPI status flags can generate a CPU ir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nterrupt requests:                                                                                                                                                                    |  |  |  |

| Table 47. SPI Interrupts |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                       |  |  |  |

|                          | Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Request                                                                                                                                                                               |  |  |  |

| Flag                    | Request                                               |

|-------------------------|-------------------------------------------------------|

| SPIF (SP data transfer) | SPI Transmitter Interrupt request                     |

| MODF (Mode Fault)       | SPI Receiver/Error Interrupt Request (if SSDIS = '0') |

Serial Peripheral data transfer flag, SPIF: This bit is set by hardware when a transfer has been completed. SPIF bit generates transmitter CPU interrupt requests.

Mode Fault flag, MODF: This bit becomes set to indicate that the level on the SS is inconsistent with the mode of the SPI. MODF with SSDIS reset, generates receiver/error CPU interrupt requests. When SSDIS is set, no MODF interrupt request is generated.

Figure 35 gives a logical view of the above statements.

### Table 56. IEN1 Register

IEN1 - Interrupt Enable Register (B1h)

| 7             | 6               | 5                                                                                                                   | 4                                                                                             | 3 | 2    | 1 | 0   |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---|------|---|-----|--|

| -             | -               | -                                                                                                                   | -                                                                                             | - | ESPI | - | KBD |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                         | Description                                                                                   |   |      |   |     |  |

| 7             | -               | Reserved                                                                                                            |                                                                                               |   |      |   |     |  |

| 6             | -               | Reserved                                                                                                            |                                                                                               |   |      |   |     |  |

| 5             | -               | Reserved                                                                                                            | Reserved                                                                                      |   |      |   |     |  |

| 4             | -               | Reserved                                                                                                            |                                                                                               |   |      |   |     |  |

| 3             | -               | Reserved                                                                                                            |                                                                                               |   |      |   |     |  |

| 2             | ESPI            | Cleared to di                                                                                                       | SPI interrupt Enable bit<br>Cleared to disable SPI interrupt.<br>Set to enable SPI interrupt. |   |      |   |     |  |

| 1             |                 | Reserved                                                                                                            | Reserved                                                                                      |   |      |   |     |  |

| 0             | KBD             | <b>Keyboard interrupt Enable bit</b><br>Cleared to disable keyboard interrupt.<br>Set to enable keyboard interrupt. |                                                                                               |   |      |   |     |  |

Reset Value = XXXX X000b Bit addressable

### Table 58. IPH1 Register

IPH1 - Interrupt Priority High Register (B3h)

| 7             | 6               | 5                                                                                | 4                                                                                                                                           | 3                | 2              | 1            | 0    |  |

|---------------|-----------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|--------------|------|--|

| -             | -               | -                                                                                | -                                                                                                                                           | -                | SPIH           | -            | KBDH |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                      |                                                                                                                                             |                  |                |              |      |  |

| 7             | -               | <b>Reserved</b><br>The value re                                                  | ad from this b                                                                                                                              | oit is indetermi | nate. Do not s | et this bit. |      |  |

| 6             | -               | Reserved<br>The value re                                                         | ad from this b                                                                                                                              | it is indetermi  | nate. Do not s | et this bit. |      |  |

| 5             | -               | Reserved<br>The value re                                                         | ad from this b                                                                                                                              | it is indetermi  | nate. Do not s | et this bit. |      |  |

| 4             | -               | Reserved<br>The value re                                                         | ad from this b                                                                                                                              | it is indetermi  | nate. Do not s | et this bit. |      |  |

| 3             | -               | Reserved<br>The value re                                                         | ad from this b                                                                                                                              | it is indetermi  | nate. Do not s | et this bit. |      |  |

| 2             | SPIH            | SPIH         S           0         0           0         1           1         0 | 0 0 Lowest<br>0 1<br>1 0                                                                                                                    |                  |                |              |      |  |

| 1             | -               | Reserved<br>The value re                                                         | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                      |                  |                |              |      |  |

| 0             | KBDH            | KB DH K                                                                          | Keyboard interrupt Priority High bit         KB DH       KBDL       Priority Level         0       0       Lowest         0       1       0 |                  |                |              |      |  |

Reset Value = XXXX X000b Not bit addressable

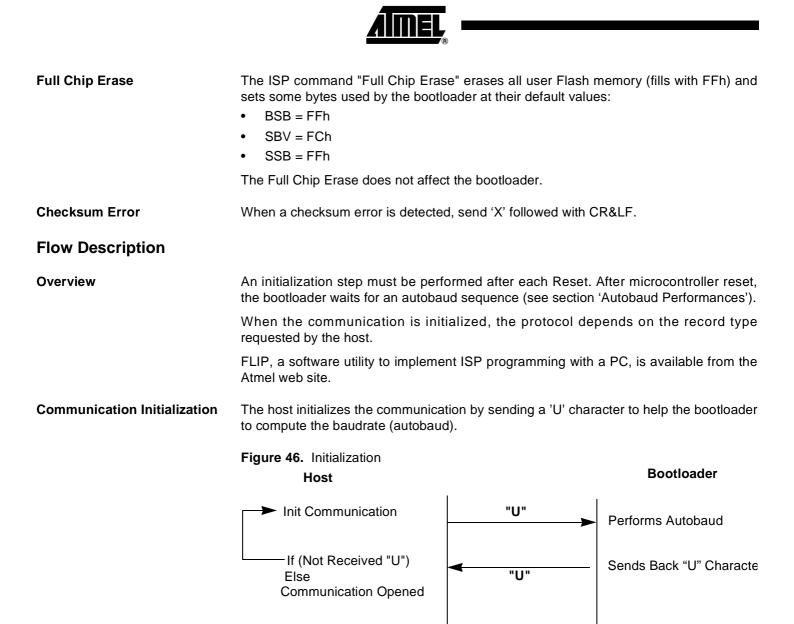

#### External Program Memory Read Cycle

#### External Data Memory Characteristics

Table 80. Symbol Description

| Symbol            | Parameter                                     |  |  |  |  |  |  |

|-------------------|-----------------------------------------------|--|--|--|--|--|--|

| T <sub>RLRH</sub> | RD Pulse Width                                |  |  |  |  |  |  |

| T <sub>WLWH</sub> | WR Pulse Width                                |  |  |  |  |  |  |

| T <sub>RLDV</sub> | RD to Valid Data In                           |  |  |  |  |  |  |

| T <sub>RHDX</sub> | Data Hold After RD                            |  |  |  |  |  |  |

| T <sub>RHDZ</sub> | Data Float After RD                           |  |  |  |  |  |  |

| T <sub>LLDV</sub> | ALE to Valid Data In                          |  |  |  |  |  |  |

| T <sub>AVDV</sub> | Address to Valid Data In                      |  |  |  |  |  |  |

| T <sub>LLWL</sub> | ALE to WR or RD                               |  |  |  |  |  |  |

| T <sub>AVWL</sub> | Address to $\overline{WR}$ or $\overline{RD}$ |  |  |  |  |  |  |

| T <sub>QVWX</sub> | Data Valid to WR Transition                   |  |  |  |  |  |  |

| T <sub>QVWH</sub> | Data Set-up to WR High                        |  |  |  |  |  |  |

| T <sub>WHQX</sub> | Data Hold After WR                            |  |  |  |  |  |  |

| T <sub>RLAZ</sub> | RD Low to Address Float                       |  |  |  |  |  |  |

| T <sub>WHLH</sub> | RD or WR High to ALE high                     |  |  |  |  |  |  |

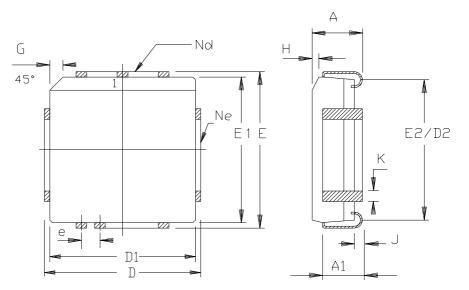

PLCC68

|    | м      | М      | IN    | ~u    |

|----|--------|--------|-------|-------|

|    | 111    | 1.1    | 1110  |       |

| A  | 4. 20  | 5.08   | .165  | . 200 |

| A1 | 2, 29  | 3.30   | . 090 | . 130 |

| D  | 25.02  | 25. 27 | . 985 | . 995 |

| D1 | 24.13  | 24. 33 | . 950 | . 958 |

| D2 | 22. 61 | 23. 62 | . 890 | . 930 |

| E  | 25.02  | 25. 27 | . 985 | . 995 |

| E1 | 24.13  | 24.33  | . 950 | . 958 |

| E5 | 22. 61 | 23. 62 | . 890 | . 930 |

| е  | 1.27   | BSC    | . 050 | BSC   |

| G  | 1.07   | 1.22   | .042  | . 048 |

| н  | 1.07   | 1.42   | .042  | .056  |

| J  | 0.51   | -      | . 020 | -     |

| К  | 0.33   | 0.53   | . 013 | . 021 |

| Nd | 1      | 7      | 1     | 7     |

| Ne | 17     |        | 1     | 7     |

| PI | KG STD | 00     |       |       |

130 AT89C51RD2/ED2

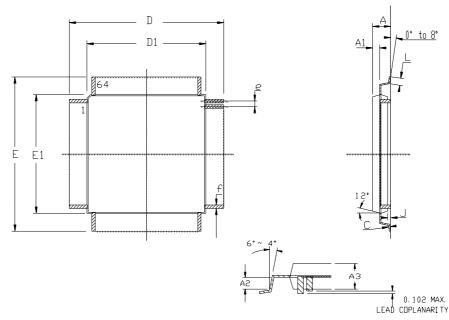

### VQFP64

|    | ММ       |        | I NCH     |       |

|----|----------|--------|-----------|-------|

|    | Min      | Max    | Min       | Max   |

| А  | -        | 1.60   | _         | . 063 |

| A1 | Ο.       | 64 REF | .025 REF  |       |

| A2 | 0.       | 64 REF | .025 REF  |       |

| A3 | 1.35     | 1.45   | . 053     | . 057 |

| D  | 11.75    | 12.25  | . 463     | . 483 |

| D1 | 9.90     | 10.10  | . 390     | . 398 |

| E  | 11.75    | 12.25  | . 463     | . 483 |

| E1 | 9.90     | 10.10  | . 390     | . 398 |

| J  | 0.05     | -      | . 002     | -     |

| L  | 0.45     | 0.75   | . 018     | .030  |

| e  | 0.50 BSC |        | .0197 BSC |       |

| f  | 0.25 BSC |        | .010 BSC  |       |

### Datasheet Change Log for AT89C51RD2/ED2

| Changes from 4235A -                           | 1. | $V_{H}$ min changed from 0.2 $V_{CC}$ + 1.1 to 0.2 $V_{CC}$ + 0.9.                                                           |

|------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------------------|

| 04/03 to 4135B - 06/03                         | 2. | Added POR/PFD and reset specific sections.                                                                                   |

|                                                | 3. | Added DIL40 package.                                                                                                         |

|                                                | 4. | Added Flash write programming time specification.                                                                            |

| Changes from 4235B -<br>06/03 to 4235C - 08/03 | 1. | Changed maximum frequency to 60 MHz in X1 mode and 30 MHz in X2 mode for Vcc = $4.5V$ to $5.5V$ and internal code execution. |

|                                                | 2. | Added PDIL40 Packaging for AT89C51ED2.                                                                                       |

| Changes from 4235C -<br>08/03 to 4235D - 12/03 | 1. | Improved explanations throughout the document.                                                                               |

| Changes from 4235D -<br>12/03 to 4235E - 04/04 | 1. | Improved explanations throughout the document.                                                                               |

| Changes from 4235E -<br>04/04 to 4235F - 09/04 | 1. | Improved explanations in Flash and EEPROM sections.                                                                          |

| Changes from 4235F -<br>09/04 to 4235G 08/05   | 1. | Added 'Industrial & Green" product versions.                                                                                 |

| Changes from 4235G<br>08/05 to 4235H - 10/06   | 1. | Correction to PDIL figure on page 9.                                                                                         |

### **Table of Contents**

| Description                                                                                                                                            | 1                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Block Diagram                                                                                                                                          | 3                                                                                                       |

| SFR Mapping                                                                                                                                            | 4                                                                                                       |

| Pin Configurations                                                                                                                                     | 9                                                                                                       |

| Port Types                                                                                                                                             | 14                                                                                                      |

| Oscillator                                                                                                                                             | 15                                                                                                      |

| Registers                                                                                                                                              | . 15                                                                                                    |

| Functional Block Diagram                                                                                                                               |                                                                                                         |

| Enhanced Features                                                                                                                                      | 17                                                                                                      |

| X2 Feature                                                                                                                                             | . 17                                                                                                    |

| Dual Data Pointer Register (DPTR)                                                                                                                      | 21                                                                                                      |

| Expanded RAM (XRAM)                                                                                                                                    | 24                                                                                                      |

| Registers                                                                                                                                              | . 26                                                                                                    |

| Reset                                                                                                                                                  | 27                                                                                                      |

|                                                                                                                                                        |                                                                                                         |

|                                                                                                                                                        | . 27                                                                                                    |

| Reset Input                                                                                                                                            |                                                                                                         |

| Reset Input<br>Reset Output                                                                                                                            | . 27                                                                                                    |

| Reset Output                                                                                                                                           | . 27<br>28                                                                                              |

| Reset Output Power Monitor                                                                                                                             | . 27<br>28<br><b>29</b>                                                                                 |

| Reset Output                                                                                                                                           | . 27<br>28<br><b>29</b>                                                                                 |

| Reset Output Power Monitor                                                                                                                             | . 27<br>28<br><b>29</b><br>. 29                                                                         |

| Reset Output Power Monitor Description                                                                                                                 | 27<br>28<br><b>29</b><br>.29<br><b>31</b>                                                               |

| Reset Output Power Monitor Description Timer 2 Auto-reload Mode Programmable                                                                           | . 27<br>28<br><b>29</b><br>. 29<br><b>31</b><br>. 31                                                    |

| Reset Output Power Monitor Description Timer 2 Auto-reload Mode Programmable Clock-output                                                              | . 27<br>28<br><b>29</b><br>. 29<br><b>31</b><br>. 31                                                    |

| Reset Output Power Monitor Description Timer 2 Auto-reload Mode Programmable                                                                           | . 27<br>28<br><b>29</b><br>. 29<br><b>31</b><br>. 31                                                    |

| Reset Output Power Monitor Description Timer 2 Auto-reload Mode Programmable Clock-output                                                              | . 27<br>28<br><b>29</b><br>. 29<br><b>31</b><br>. 31<br>. 32<br>. 34                                    |

| Reset Output Power Monitor Description Timer 2 Auto-reload Mode Programmable Clock-output Registers                                                    | . 27<br>28<br><b>29</b><br>. 29<br><b>31</b><br>. 31<br>. 32<br>. 34<br><b>36</b>                       |

| Reset Output Power Monitor Description Timer 2 Auto-reload Mode Programmable Clock-output Registers Programmable Counter Array (PCA)                   | . 27<br>28<br><b>29</b><br>. 29<br>. 31<br>. 31<br>. 32<br>. 34<br>. 36<br>. 44                         |

| Reset Output Power Monitor Description Timer 2 Auto-reload Mode Programmable Clock-output Registers Programmable Counter Array (PCA) PCA Capture Mode. | . 27<br>28<br><b>29</b><br>. 29<br><b>31</b><br>. 31<br>. 32<br>. 34<br><b>36</b><br>. 44<br>. 44       |

| Reset Output Power Monitor Description Timer 2 Auto-reload Mode Programmable Clock-output Registers Programmable Counter Array (PCA) PCA Capture Mode  | . 27<br>28<br><b>29</b><br>. 29<br>. 31<br>. 31<br>. 32<br>. 34<br>. 34<br>. 44<br>. 44<br>. 45<br>. 46 |

i