#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LQFP                                                                    |

| Supplier Device Package    | 44-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ed2-rdrim |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 8 AT89C51RD2/ED2

| reserved |

|----------|

|          |

|     | Addressable                        | Non Bit Addressable |                     |                     |                     |                     |                     |                                     |     |

|-----|------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------------------------------|-----|

|     | 0/8                                | 1/9                 | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                                 |     |

| F8h |                                    | CH<br>0000 0000     | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAP2H<br>XXXX XXXX | CCAP3H<br>XXXX XXXX | CCAP4H<br>XXXX XXXX |                                     | FFh |

| F0h | B<br>0000 0000                     |                     |                     |                     |                     |                     |                     |                                     | F7h |

| E8h | P5 bit<br>addressable<br>1111 1111 | CL<br>0000 0000     | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAP2L<br>XXXX XXXX | CCAP3L<br>XXXX XXXX | CCAP4L<br>XXXX XXXX |                                     | EFł |

| E0h | ACC<br>0000 0000                   |                     |                     |                     |                     |                     |                     |                                     | E7h |

| D8h | CCON<br>00X0 0000                  | CMOD<br>00XX X000   | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000 | CCAPM3<br>X000 0000 | CCAPM4<br>X000 0000 |                                     | DFł |

| D0h | PSW<br>0000 0000                   | FCON<br>XXXX 0000   | EECON<br>xxxx xx00  |                     |                     |                     |                     |                                     | D7h |

| C8h | T2CON<br>0000 0000                 | T2MOD<br>XXXX XX00  | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000    | TH2<br>0000 0000    |                     |                                     | CFr |

| C0h | P4<br>1111 1111                    |                     |                     | SPCON<br>0001 0100  | SPSTA<br>0000 0000  | SPDAT<br>XXXX XXXX  |                     | P5 byte<br>Addressable<br>1111 1111 | C7ł |

| B8h | IPL0<br>X000 000                   | SADEN<br>0000 0000  |                     |                     |                     |                     |                     |                                     | BFł |

| B0h | P3<br>1111 1111                    | IEN1<br>XXXX X000   | IPL1<br>XXXX X000   | IPH1<br>XXXX X111   |                     |                     |                     | IPH0<br>X000 0000                   | B7h |

| A8h | IEN0<br>0000 0000                  | SADDR<br>0000 0000  |                     |                     |                     |                     |                     | CKCON1<br>XXXX XXX0                 | AFł |

| A0h | P2<br>1111 1111                    |                     | AUXR1<br>0XXX X0X0  |                     |                     |                     | WDTRST<br>XXXX XXXX | WDTPRG<br>XXXX X000                 | A7ł |

| 98h | SCON<br>0000 0000                  | SBUF<br>XXXX XXXX   | BRL<br>0000 0000    | BDRCON<br>XXX0 0000 | KBLS<br>0000 0000   | KBE<br>0000 0000    | KBF<br>0000 0000    |                                     | 9Fł |

| 90h | P1<br>1111 1111                    |                     |                     |                     |                     |                     |                     | CKRL<br>1111 1111                   | 97h |

| 88h | TCON<br>0000 0000                  | TMOD<br>0000 0000   | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000    | TH1<br>0000 0000    | AUXR<br>XX00 1000   | CKCON0<br>0000 0000                 | 8Fł |

| 80h | P0<br>1111 1111                    | SP<br>0000 0111     | DPL<br>0000 0000    | DPH<br>0000 0000    |                     |                     |                     | PCON<br>00X1 0000                   | 87h |

|     | 0/8                                | 1/9                 | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                                 |     |

### Table 12. SFR Mapping

Bit

Table 12 shows all SFRs with their address and their reset value.

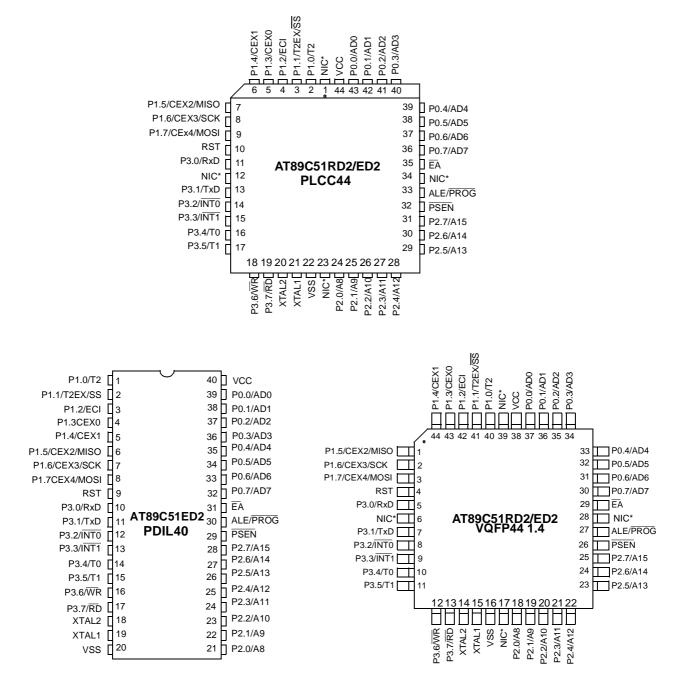

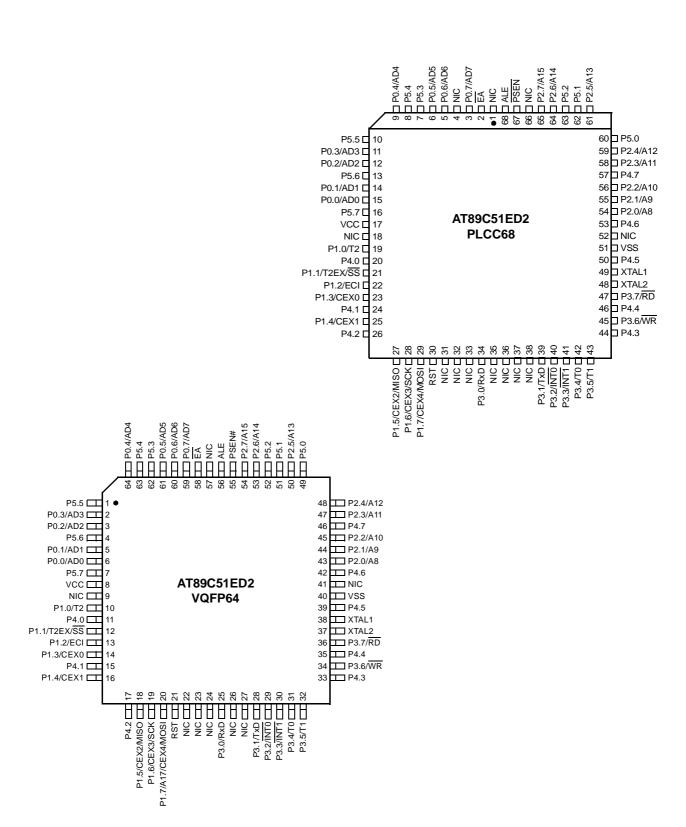

# **Pin Configurations**

#### Figure 2. Pin Configurations

NIC: Not Internaly Connected

### Table 17. CKCON1 Register

CKCON1 - Clock Control Register (AFh)

| 7             | 6               | 5                                 | 4                             | 3                                                 | 2               | 1    | 0            |

|---------------|-----------------|-----------------------------------|-------------------------------|---------------------------------------------------|-----------------|------|--------------|

| -             | -               | -                                 | -                             | -                                                 | -               | -    | SPIX2        |

| Bit<br>Number | Bit<br>Mnemonic | Description                       |                               |                                                   |                 |      |              |

| 7             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 6             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 5             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 4             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 3             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 2             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 1             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 0             | SPIX2           | this bit has no<br>Clear to selec | o effect).<br>ct 6 clock peri | dated when th<br>ods per periph<br>ods per periph | neral clock cyc | cle. | n X2 is low, |

Reset Value = XXXX XXX0b Not bit addressable

#### Table 18. AUXR1 Register

AUXR1- Auxiliary Register 1(0A2h)

| 7             | 6               | 5                                              | 4                                                                               | 3                   | 2                         | 1            | 0   |  |

|---------------|-----------------|------------------------------------------------|---------------------------------------------------------------------------------|---------------------|---------------------------|--------------|-----|--|

| -             | -               | ENBOOT                                         | -                                                                               | GF3                 | 0                         | -            | DPS |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                    |                                                                                 |                     |                           |              |     |  |

| 7             | -               | <b>Reserved</b><br>The value rea               | ad from this b                                                                  | it is indetermir    | ate. Do not se            | et this bit. |     |  |

| 6             | -               | Reserved<br>The value rea                      | ad from this b                                                                  | it is indetermir    | ate. Do not se            | et this bit. |     |  |

| 5             | ENBOOT          | Enable Boot<br>Cleared to dis<br>Set to map th | sable boot RC                                                                   | DM.<br>between F800 | h - 0FFFFh.               |              |     |  |

| 4             | -               | Reserved<br>The value rea                      | ad from this b                                                                  | it is indetermir    | ate. Do not se            | et this bit. |     |  |

| 3             | GF3             | This bit is a                                  | general-pur                                                                     | oose user flaç      | <b>j</b> . <sup>(1)</sup> |              |     |  |

| 2             | 0               | Always clea                                    | red                                                                             |                     |                           |              |     |  |

| 1             | -               | Reserved<br>The value rea                      | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                     |                           |              |     |  |

| 0             | DPS             | Data Pointer<br>Cleared to se<br>Set to select | lect DPTR0.                                                                     |                     |                           |              |     |  |

Reset Value = XXXX XX0X0b

#### Not bit addressable

Note: 1. Bit 2 stuck at 0; this allows to use INC AUXR1 to toggle DPS without changing GF3.

#### ASSEMBLY LANGUAGE

; Block move using dual data pointers ; Modifies DPTR0, DPTR1, A and PSW ; note: DPS exits opposite of entry state ; unless an extra INC AUXR1 is added ; 00A2 AUXR1 EQU 0A2H ; 0000 909000MOV DPTR, #SOURCE ; address of SOURCE 0003 05A2 INC AUXR1 ; switch data pointers 0005 90A000 MOV DPTR, #DEST ; address of DEST 0008 LOOP: 0008 05A2 INC AUXR1 ; switch data pointers 000A E0 MOVX A,@DPTR ; get a byte from SOURCE 000B A3 INC DPTR ; increment SOURCE address 000C 05A2 INC AUXR1 ; switch data pointers 000E FO MOVX @DPTR,A ; write the byte to DEST 000F A3 INC DPTR ; increment DEST address 0010 70F6JNZ LOOP ; check for 0 terminator 0012 05A2 INC AUXR1 ; (optional) restore DPS

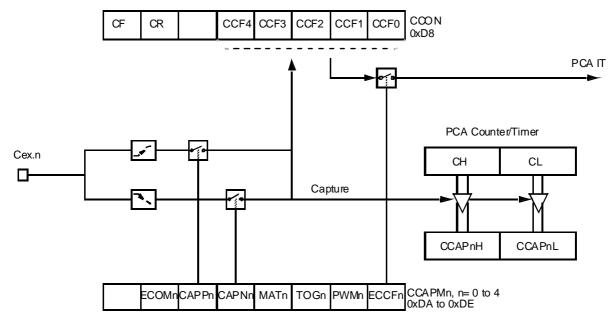

Table 24 shows the CCAPMn settings for the various PCA functions.

#### Table 24. CCAPMn Registers (n = 0-4)

CCAPM0 - PCA Module 0 Compare/Capture Control Register (0DAh)

CCAPM1 - PCA Module 1 Compare/Capture Control Register (0DBh)

- CCAPM2 PCA Module 2 Compare/Capture Control Register (0DCh)

- CCAPM3 PCA Module 3 Compare/Capture Control Register (0DDh)

CCAPM4 - PCA Module 4 Compare/Capture Control Register (0DEh)

| 7             | 6               | 5                                | 4                                                                                                                                                                                        | 3                                | 2              | 1            | 0         |  |

|---------------|-----------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|--------------|-----------|--|

| -             | ECOMn           | CAPPn                            | CAPNn                                                                                                                                                                                    | MATn                             | TOGn           | PWMn         | ECCFn     |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                      |                                                                                                                                                                                          |                                  |                |              |           |  |

| 7             | -               | <b>Reserved</b><br>The value rea | ad from this b                                                                                                                                                                           | it is indetermir                 | nate. Do not s | et this bit. |           |  |

| 6             | ECOMn           |                                  | -                                                                                                                                                                                        | nparator functi<br>tor function. | on.            |              |           |  |

| 5             | CAPPn           |                                  |                                                                                                                                                                                          | e edge capture<br>e capture.     |                |              |           |  |

| 4             | CAPNn           |                                  |                                                                                                                                                                                          | e edge captur<br>ge capture.     | e.             |              |           |  |

| 3             | MATn            |                                  |                                                                                                                                                                                          | of the PCA co<br>causes the CC   |                |              | agging an |  |

| 2             | TOGn            |                                  | ,                                                                                                                                                                                        | of the PCA co<br>causes the CE   |                |              |           |  |

| 1             | PWMn            | Cleared to di                    | Pulse Width Modulation Mode<br>Cleared to disable the CEXn pin to be used as a pulse width modulated output.<br>Set to enable the CEXn pin to be used as a pulse width modulated output. |                                  |                |              |           |  |

| 0             | CCF0            | an interrupt.                    | sable compar                                                                                                                                                                             | e/capture flag<br>oture flag CCF |                | -            | -         |  |

Reset Value = X000 0000b Not bit addressable

# PCA Capture Mode

To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated (Refer to Figure 18).

#### Figure 18. PCA Capture Mode

## 16-bit Software Timer/ Compare Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (See Figure 19).

| Baud Rates | F <sub>osc</sub> = 16 | . 384 MHz     | F <sub>OSC</sub> = 24MHz |           |  |

|------------|-----------------------|---------------|--------------------------|-----------|--|

|            | BRL                   | BRL Error (%) |                          | Error (%) |  |

| 115200     | 247                   | 1.23          | 243                      | 0.16      |  |

| 57600      | 238                   | 1.23          | 230                      | 0.16      |  |

| 38400      | 229                   | 1.23          | 217                      | 0.16      |  |

| 28800      | 220                   | 1.23          | 204                      | 0.16      |  |

| 19200      | 203                   | 0.63          | 178                      | 0.16      |  |

| 9600       | 149                   | 0.31          | 100                      | 0.16      |  |

| 4800       | 43                    | 1.23          | -                        | -         |  |

| Table 34 | . Example of Computed | Value When X2=1, | SMOD1=1, SPD=1 |

|----------|-----------------------|------------------|----------------|

|----------|-----------------------|------------------|----------------|

Table 35. Example of Computed Value When X2=0, SMOD1=0, SPD=0

| Baud Rates | F <sub>osc</sub> = 16 | . 384 MHz     | F <sub>OSC</sub> = 24MHz |           |  |

|------------|-----------------------|---------------|--------------------------|-----------|--|

|            | BRL                   | BRL Error (%) |                          | Error (%) |  |

| 4800       | 247                   | 1.23          | 243                      | 0.16      |  |

| 2400       | 238                   | 1.23          | 230                      | 0.16      |  |

| 1200       | 220                   | 1.23          | 202                      | 3.55      |  |

| 600        | 185                   | 0.16          | 152                      | 0.16      |  |

The baud rate generator can be used for mode 1 or 3 (refer to Figure 25.), but also for mode 0 for UART, thanks to the bit SRC located in BDRCON register (Table 42.)

## **UART Registers**

#### Table 36. SADEN Register

SADEN - Slave Address Mask Register for UART (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

#### Table 37. SADDR Register

SADDR - Slave Address Register for UART (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

# AT89C51RD2/ED2

### Table 42. BDRCON Register

BDRCON - Baud Rate Control Register (9Bh)

| 7             | 6               | 5                        | 4                                                                                                                                      | 3                                                | 2               | 1                             | 0   |  |

|---------------|-----------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|-------------------------------|-----|--|

| -             | -               | -                        | BRR                                                                                                                                    | ТВСК                                             | RBCK            | SPD                           | SRC |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptior              | 1                                                                                                                                      |                                                  |                 |                               |     |  |

| 7             | -               | Reserved<br>The value re | ead from this                                                                                                                          | bit is indeterm                                  | inate. Do not s | set this bit                  |     |  |

| 6             | -               | Reserved<br>The value re | ead from this                                                                                                                          | bit is indeterm                                  | inate. Do not s | set this bit                  |     |  |

| 5             | -               | Reserved<br>The value re | ead from this I                                                                                                                        | oit is indetermi                                 | nate. Do not s  | et this bit.                  |     |  |

| 4             | BRR             | Cleared to s             | •                                                                                                                                      | <b>bit</b><br>al Baud Rate (<br>aud Rate Gene    |                 |                               |     |  |

| 3             | ТВСК            | Cleared to s             | elect Timer 1                                                                                                                          | e Generator S<br>or Timer 2 for<br>d Rate Genera | the Baud Rate   |                               |     |  |

| 2             | RBCK            | Cleared to s             | elect Timer 1                                                                                                                          | enerator Sele<br>or Timer 2 for<br>d Rate Genera | the Baud Rate   |                               |     |  |

| 1             | SPD             | Cleared to s             | Baud Rate Speed Control bit for UART<br>Cleared to select the SLOW Baud Rate Generator.<br>Set to select the FAST Baud Rate Generator. |                                                  |                 |                               |     |  |

| 0             | SRC             | Cleared to s<br>mode).   | elect F <sub>OSC</sub> /12                                                                                                             |                                                  | Rate Generato   | or (F <sub>CLK PERIPH</sub> / |     |  |

Reset Value = XXX0 0000b Not bit addressable

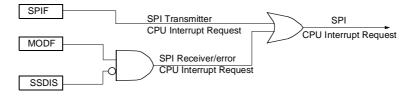

#### Figure 35. SPI Interrupt Requests Generation

There are three registers in the Module that provide control, status and data storage functions. These registers

#### Registers

Register (SPCON)

are describes in the following paragraphs.Serial Peripheral Control• The Serial Peripheral Control Register does the following:

Selects one of the Master clock rates

- Configure the SPI Module as Master or Slave

- Selects serial clock polarity and phase

- Enables the SPI Module

- Frees the SS pin for a general-purpose

Table 48 describes this register and explains the use of each bit

#### Table 48. SPCON Register

SPCON - Serial Peripheral Control Register (0C3H)

| 7          | 6       | 5      | 4                                                                                                                                                                                                                                               | 3    | 2    | 1    | 0    |  |  |

|------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|

| SPR2       | SPEN    | SSDIS  | MSTR                                                                                                                                                                                                                                            | CPOL | СРНА | SPR1 | SPR0 |  |  |

| Bit Number | Bit Mne | emonic | Description                                                                                                                                                                                                                                     |      |      |      |      |  |  |

| 7          | SF      | PR2    | Serial Peripheral Rate 2<br>Bit with SPR1 and SPR0 define the clock rate.                                                                                                                                                                       |      |      |      |      |  |  |

| 6          | SF      | 'EN    | Serial Peripheral Enable<br>Cleared to disable the SPI interface.<br>Set to enable the SPI interface.                                                                                                                                           |      |      |      |      |  |  |

| 5          | SS      | DIS    | <b>SS</b> Disable<br>Cleared to enable SS in both Master and Slave modes.<br>Set to disable SS in both Master and Slave modes. In Slave mo<br>this bit has no effect if CPHA ='0'. When SSDIS is set, no MOD<br>interrupt request is generated. |      |      |      |      |  |  |

| 4          | MS      | STR    | Serial Peripheral Master<br>Cleared to configure the SPI as a Slave.<br>Set to configure the SPI as a Master.                                                                                                                                   |      |      |      |      |  |  |

| 3          | CF      | POL    | <b>Clock Polarity</b><br>Cleared to have the SCK set to '0' in idle state.<br>Set to have the SCK set to '1' in idle low.                                                                                                                       |      |      |      |      |  |  |

| 2          | CF      |        | Clock Phase<br>Cleared to have the data sampled when the SCK leaves the idle<br>state (see CPOL).<br>Set to have the data sampled when the SCK returns to idle state (see<br>CPOL).                                                             |      |      |      |      |  |  |

## Table 57. IPL1 Register

IPL1 - Interrupt Priority Register (B2h)

| 7             | 6               | 5                               | 4                                                                               | 3               | 2              | 1            | 0    |  |  |

|---------------|-----------------|---------------------------------|---------------------------------------------------------------------------------|-----------------|----------------|--------------|------|--|--|

| -             | -               | -                               | -                                                                               | -               | SPIL           | TWIL         | KBDL |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                                                                 |                 |                |              |      |  |  |

| 7             | -               | Reserved<br>The value re        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                |              |      |  |  |

| 6             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                |              |      |  |  |

| 5             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                |              |      |  |  |

| 4             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                |              |      |  |  |

| 3             | -               | <b>Reserved</b><br>The value re | ad from this b                                                                  | it is indetermi | nate. Do not s | et this bit. |      |  |  |

| 2             | SPIL            |                                 | t Priority bit<br>H for priority I                                              |                 |                |              |      |  |  |

| 1             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                |              |      |  |  |

| 0             | KBDL            | -                               | <b>Keyboard interrupt Priority bit</b><br>Refer to KBDH for priority level.     |                 |                |              |      |  |  |

Reset Value = XXXX X000b Bit addressable

# Hardware Watchdog Timer

The WDT is intended as a recovery method in situations where the CPU may be subjected to software upset. The WDT consists of a 14-bit counter and the Watchdog Timer ReSeT (WDTRST) SFR. The WDT is by default disabled from exiting reset. To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will drive an output RESET HIGH pulse at the RST-pin.

Using the WDT

To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, the user needs to service it by writing to 01EH and 0E1H to WDTRST to avoid WDT overflow. The 14-bit counter overflows when it reaches 16383 (3FFFH) and this will reset the device. When WDT is enabled, it will increment every machine cycle while the oscillator is running. This means the user must reset the WDT at least every 16383 machine cycle. To reset the WDT the user must write 01EH and 0E1H to WDTRST. WDTRST is a write only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST-pin. The RESET pulse duration is 96 x T<sub>CLK PERIPH</sub>, where T<sub>CLK PERIPH</sub>= 1/F<sub>CLK PERIPH</sub>. To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

To have a more powerful WDT, a  $2^7$  counter has been added to extend the Time-out capability, ranking from 16 ms to 2s @  $F_{OSCA}$  = 12 MHz. To manage this feature, refer to WDTPRG register description, Table 61. The WDTPRG register should be configured before the WDT activation sequence, and can not be modified until next reset.

Table 61.

WDTRST Register

WDTRST - Watchdog Reset Register (0A6h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset Value = XXXX XXXXb

Write only, this SFR is used to reset/enable the WDT by writing 01EH then 0E1H in sequence.

# ONCE<sup>®</sup> Mode (ON-Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using AT89C51RD2/ED2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the AT89C51RD2/ED2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- Hold ALE low as RST is deactivated.

While the AT89C51RD2/ED2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit. Table 63 shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

| ĺ | ALE             | PSEN            | Port 0 | Port 1          | Port 2          | Port 3          | Port I2 | XTALA1/2 | XTALB1/2 |

|---|-----------------|-----------------|--------|-----------------|-----------------|-----------------|---------|----------|----------|

|   | Weak<br>pull-up | Weak<br>pull-up | Float  | Weak<br>pull-up | Weak<br>pull-up | Weak<br>pull-up | Float   | Active   | Active   |

Table 63. External Pin Status During ONCE Mode

# **Power-off Flag**

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (Table 64). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

#### Table 64. PCON Register

| 7             | 6               | 5                              | 4                                                                                                                                                                             | 3                            | 2         | 1  | 0   |  |  |

|---------------|-----------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------|----|-----|--|--|

| SMOD1         | SMOD0           | -                              | POF                                                                                                                                                                           | GF1                          | GF0       | PD | IDL |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                    |                                                                                                                                                                               |                              |           |    |     |  |  |

| 7             | SMOD1           | Serial port N<br>Set to select |                                                                                                                                                                               | rate in mode 1               | , 2 or 3. |    |     |  |  |

| 6             | SMOD0           | Cleared to se                  | Serial port Mode bit 0<br>Cleared to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register.                                                               |                              |           |    |     |  |  |

| 5             | -               | Reserved<br>The value rea      | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                               |                              |           |    |     |  |  |

| 4             | POF             | Cleared by s                   | Power-Off Flag<br>Cleared by software to recognize the next reset type.<br>Set by hardware when $V_{CC}$ rises from 0 to its nominal voltage. Can also be set by<br>software. |                              |           |    |     |  |  |

| 3             | GF1             |                                |                                                                                                                                                                               | I-purpose usa<br>pose usage. | ge.       |    |     |  |  |

| 2             | GF0             | Cleared by u                   | General-purpose Flag<br>Cleared by user for general-purpose usage.<br>Set by user for general-purpose usage.                                                                  |                              |           |    |     |  |  |

| 1             | PD              | Cleared by h                   | <b>Power-down mode bit</b><br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                                         |                              |           |    |     |  |  |

| 0             | IDL             | Cleared by h                   | <b>Idle mode bit</b><br>Cleared by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                                                                        |                              |           |    |     |  |  |

PCON - Power Control Register (87h)

Reset Value = 00X1 0000b Not bit addressable

| Mnemonic | Definition                                          | Default value | Description                        |

|----------|-----------------------------------------------------|---------------|------------------------------------|

| SBV      | Software Boot Vector                                | FCh           |                                    |

| BSB      | Boot Status Byte                                    | 0FFh          |                                    |

| SSB      | Software Security Byte                              | FFh           |                                    |

|          | Copy of the Manufacturer Code                       | 58h           | Atmel                              |

|          | Copy of the Device ID #1: Family Code               | D7h           | C51 X2, Electrically Erasable      |

|          | Copy of the Device ID #2: Memories Size<br>and Type | ECh           | AT89C51RD2/ED2 64KB                |

|          | Copy of the Device ID #3: Name and Revision         | EFh           | AT89C51RD2/ED2 64KB,<br>Revision 0 |

After programming the part by ISP, the BSB must be cleared (00h) in order to allow the application to boot at 0000h.

The content of the Software Security Byte (SSB) is described in Table 70 and Table 71.

To assure code protection from a parallel access, the HSB must also be at the required level.

Table 70. Software Security Byte

| 7             | 6               | 5                                 | 4                                     | 3 | 2 | 1   | 0   |  |  |  |  |

|---------------|-----------------|-----------------------------------|---------------------------------------|---|---|-----|-----|--|--|--|--|

| -             | -               | -                                 | -                                     | - | - | LB1 | LB0 |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                       | Description                           |   |   |     |     |  |  |  |  |

| 7             | -               | <b>Reserved</b><br>Do not clear t | Reserved<br>Do not clear this bit.    |   |   |     |     |  |  |  |  |

| 6             | -               | Reserved<br>Do not clear t        | Reserved<br>Do not clear this bit.    |   |   |     |     |  |  |  |  |

| 5             | -               | <b>Reserved</b><br>Do not clear t | Reserved<br>Do not clear this bit.    |   |   |     |     |  |  |  |  |

| 4             | -               | Reserved<br>Do not clear t        | Reserved<br>Do not clear this bit.    |   |   |     |     |  |  |  |  |

| 3             | -               | <b>Reserved</b><br>Do not clear t | Reserved<br>Do not clear this bit.    |   |   |     |     |  |  |  |  |

| 2             | -               | Reserved<br>Do not clear t        | Reserved<br>Do not clear this bit.    |   |   |     |     |  |  |  |  |

| 1-0           | LB1-0           |                                   | User Memory Lock Bits<br>See Table 71 |   |   |     |     |  |  |  |  |

The two lock bits provide different levels of protection for the on-chip code and data, when programmed as shown in Table 71.

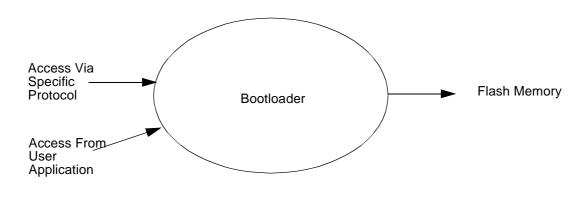

# **Bootloader Architecture**

Introduction

The bootloader manages communication according to a specifically defined protocol to provide the whole access and service on Flash memory. Furthermore, all accesses and routines can be called from the user application.

### Figure 41. Diagram Context Description

Acronyms

ISP: In-System Programming SBV: Software Boot Vector BSB: Boot Status Byte SSB: Software Security Byte HW: Hardware Byte

# AT89C51RD2/ED2

# **Functional Description**

Software Security Bits (SSB)The SSB protects any Flash access from ISP command.<br/>The command "Program Software Security Bit" can only write a higher priority level.

There are three levels of security:

level 0: NO\_SECURITY (FFh)

This is the default level. From level 0, one can write level 1 or level 2.

#### level 1: WRITE\_SECURITY (FEh)

For this level it is impossible to write in the Flash memory, BSB and SBV. The Bootloader returns 'P' on write access. From level 1, one can write only level 2.

• level 2: RD\_WR\_SECURITY (FCh

The level 2 forbids all read and write accesses to/from the Flash/EEPROM memory.

The Bootloader returns 'L' on read or write access.

Only a full chip erase in parallel mode (using a programmer) or ISP command can reset the software security bits.

From level 2, one cannot read and write anything.

|                      | Level 0                  | Level 1                  | Level 2                  |

|----------------------|--------------------------|--------------------------|--------------------------|

| Flash/EEPROM         | Any access allowed       | Read-only access allowed | Any access not allowed   |

| Fuse Bit             | Any access allowed       | Read-only access allowed | Any access not allowed   |

| BSB & SBV            | Any access allowed       | Read-only access allowed | Any access not allowed   |

| SSB                  | Any access allowed       | Write level 2 allowed    | Read-only access allowed |

| Manufacturer<br>Info | Read-only access allowed | Read-only access allowed | Read-only access allowed |

| Bootloader Info      | Read-only access allowed | Read-only access allowed | Read-only access allowed |

| Erase Block          | Allowed                  | Not allowed              | Not allowed              |

| Full Chip Erase      | Allowed                  | Allowed                  | Allowed                  |

| Blank Check          | Allowed                  | Allowed                  | Allowed                  |

Table 73. Software Security Byte Behavior

|                      | ®                                                                                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| API Call Description | The IAP allows to reprogram a microcontroller on-chip Flash memory without removing it from the system and while the embedded application is running. |

|                      | The user application can call some Application Programming Interface (API) routines allowing IAP. These API are executed by the bootloader.           |

|                      | To call the corresponding API, the user must use a set of Flash_api routines which can be linked with the application.                                |

|                      | Example of Flash_api routines are available on the Atmel web site on the software appli-<br>cation note:                                              |

|                      | C Flash Drivers for the AT89C51RD2/ED2                                                                                                                |

|                      | The API calls description and arguments are shown in Table 76.                                                                                        |

| Process              | The application selects an API by setting R1, ACC, DPTR0 and DPTR1 registers.                                                                         |

|                      | All calls are made through a common interface "USER_CALL" at the address FFF0h.                                                                       |

|                      | The jump at the USER_CALL must be done by LCALL instruction to be able to come-<br>back in the application.                                           |

|                      | Before jump at the USER_CALL, the bit ENBOOT in AUXR1 register must be set.                                                                           |

| Constraints          | The interrupts are not disabled by the bootloader.                                                                                                    |

|                      | Interrupts must be disabled by user prior to jump to the USER_CALL, then re-enabled when returning.                                                   |

|                      | Interrupts must also be disabled before accessing EEPROM Data then re-enabled after.                                                                  |

MEL

The user must take care of hardware watchdog before launching a Flash operation.

| Command              | R1  | Α             | DPTR0                            | DPTR1 | Returned Value           | Command Effect                                        |  |

|----------------------|-----|---------------|----------------------------------|-------|--------------------------|-------------------------------------------------------|--|

| READ MANUF ID        | 00h | XXh           | 0000h                            | XXh   | ACC = Manufacturer<br>Id | Read Manufacturer identifier                          |  |

| READ DEVICE ID1      | 00h | XXh           | 0001h                            | XXh   | ACC = Device Id 1        | Read Device identifier 1                              |  |

| READ DEVICE ID2      | 00h | XXh           | 0002h                            | XXh   | ACC = Device Id 2        | Read Device identifier 2                              |  |

| READ DEVICE ID3      | 00h | XXh           | 0003h                            | XXh   | ACC = Device Id 3        | Read Device identifier 3                              |  |

|                      |     |               | DPH = 00h                        |       |                          | Erase block 0                                         |  |

|                      |     |               | DPH = 20h                        |       |                          | Erase block 1                                         |  |

| ERASE BLOCK          | 01h | XXh           | DPH = 40h                        | 00h   | ACC = DPH                | Erase block 2                                         |  |

|                      |     |               | DPH = 80h                        |       |                          | Erase block 3                                         |  |

|                      |     |               | DPH = C0h                        |       |                          | Erase block 4                                         |  |

| PROGRAM DATA<br>BYTE | 02h | Vaue to write | Address of<br>byte to<br>program | XXh   | ACC = 0: DONE            | Program up one data byte in the on-chip flash memory. |  |

# Table 76. API Call Summary

Maximum total  $I_{OL}$  for all output pins: 71 mA If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

7. The maximum dV/dt value specifies the maximum Vcc drop to issure no internal POR/PFD reset.

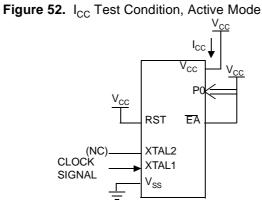

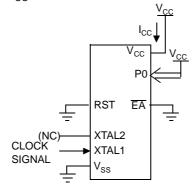

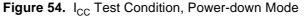

All other pins are disconnected.

All other pins are disconnected.

All other pins are disconnected.

# AT89C51RD2/ED2

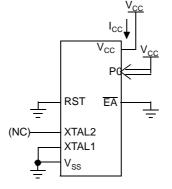

Figure 55. Clock Signal Waveform for I<sub>CC</sub> Tests in Active and Idle Modes

# **AC Parameters**

| Explanation | of | the | AC |

|-------------|----|-----|----|

| Symbols     |    |     |    |

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

Example:  $T_{AVLL}$  = Time for Addr<u>ess Valid</u> to ALE Low.  $T_{LLPL}$  = Time for ALE Low to PSEN Low.

(Load Capacitance for port 0, ALE and PSEN = 100 pF; Load Capacitance for all other outputs = 80 pF.)

Table 77 Table 80, and Table 83 give the description of each AC symbols.

Table 78, Table 79, Table 81 and Table 84 gives the range for each AC parameter.

Table 78, Table 79 and Table 85 give the frequency derating formula of the AC parameter for each speed range description. To calculate each AC symbols. take the x value in the correponding column (-M) and use this value in the formula.

Example: T<sub>LLIU</sub> for -M and 20 MHz, Standard clock.

x = 35 ns T 50 ns T<sub>CCIV</sub> = 4T - x = 165 ns

#### External Program Memory Characteristics

Table 77. Symbol Description

| Symbol            | Parameter                          |

|-------------------|------------------------------------|

| Т                 | Oscillator clock period            |

| T <sub>LHLL</sub> | ALE pulse width                    |

| T <sub>AVLL</sub> | Address Valid to ALE               |

| T <sub>LLAX</sub> | Address Hold After ALE             |

| T <sub>LLIV</sub> | ALE to Valid Instruction In        |

| T <sub>LLPL</sub> | ALE to PSEN                        |

| T <sub>PLPH</sub> | PSEN Pulse Width                   |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In       |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN  |

| T <sub>PXIZ</sub> | Input Instruction Float After PSEN |

| T <sub>AVIV</sub> | Address to Valid Instruction In    |

| T <sub>PLAZ</sub> | PSEN Low to Address Float          |