#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LQFP                                                                    |

| Supplier Device Package    | 44-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ed2-rdtim |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 13. Pin Description (Continued)

|             |                |              | Pin Numb                                | er                                      |        | _    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------------|--------------|-----------------------------------------|-----------------------------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic    | PLCC44         | VQFP44       | PLCC68                                  | VQFP64                                  | PDIL40 | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 9              | 3            | 29                                      | 20                                      | 8      | I/O  | P1.7: Input/Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                |              |                                         |                                         |        | I/O  | CEX4: Capture/Compare External I/O for PCA module 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                |              |                                         |                                         |        | I/O  | MOSI: SPI Master Output Slave Input line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                |              |                                         |                                         |        |      | When SPI is in master mode, MOSI outputs data to the slave peripheral.<br>When SPI is in slave mode, MOSI receives data from the master control-<br>ler.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

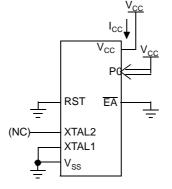

| XTALA1      | 21             | 15           | 49                                      | 38                                      | 19     | Ι    | <b>XTALA 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| XTALA2      | 20             | 14           | 48                                      | 37                                      | 18     | 0    | XTALA 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P2.0 - P2.7 | 24 - 31        | 18 - 25      | 54, 55,<br>56, 58,<br>59, 61,<br>64, 65 | 43, 44,<br>45, 47,<br>48, 50,<br>53, 54 | 21-28  | I/O  | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR).In this application, it uses strong internal pull-ups emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @Ri), port 2 emits the contents of the P2 SFR. |

| P3.0 - P3.7 | 11,<br>13 - 19 | 5,<br>7 - 13 | 34, 39,<br>40, 41,<br>42, 43,<br>45, 47 | 25, 28,<br>29, 30,<br>31, 32,<br>34, 36 | 10-17  | I/O  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                     |

|             | 11             | 5            | 34                                      | 25                                      | 10     | I    | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 13             | 7            | 39                                      | 28                                      | 11     | ο    | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 14             | 8            | 40                                      | 29                                      | 12     | I    | INT0 (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 15             | 9            | 41                                      | 30                                      | 13     | I    | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 16             | 10           | 42                                      | 31                                      | 14     | I    | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 17             | 11           | 43                                      | 32                                      | 15     | I    | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 18             | 12           | 45                                      | 34                                      | 16     | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 19             | 13           | 47                                      | 36                                      | 17     | 0    | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P4.0 - P4.7 | -              | -            | 20, 24,<br>26, 44,<br>46, 50,<br>53, 57 | 11, 15,<br>17,33,<br>35,39,<br>42, 46   | -      | I/O  | <b>Port 4:</b> Port 4 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                   |

| P5.0 - P5.7 | -              | -            | 60, 62,<br>63, 7, 8,<br>10, 13,<br>16   | 49, 51,<br>52, 62,<br>63, 1, 4,<br>7    | -      | I/O  | <b>Port 5:</b> Port 5 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                   |

| RST         | 10             | 4            | 30                                      | 21                                      | 9      | I    | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ . This pin is an output when the hardware watchdog forces a system reset.                                                                                                                                                                                                                                                                                                                                                                       |

## Table 16. CKCON0 Register

CKCON0 - Clock Control Register (8Fh)

| 7             | 6               | 5                                                                                                                                                                                                                                                        | 4                                                                                                                                                                                                                                                                           | 3                                                                        | 2                                 | 1                             | 0                        |  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------|-------------------------------|--------------------------|--|--|

| -             | WDX2            | PCAX2                                                                                                                                                                                                                                                    | SIX2                                                                                                                                                                                                                                                                        | T2X2                                                                     | T1X2                              | T0X2                          | X2                       |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                             |                                                                          |                                   |                               |                          |  |  |

| 7             | Reserved        | The values for                                                                                                                                                                                                                                           | or this bit are i                                                                                                                                                                                                                                                           | indeterminite.                                                           | Do not set thi                    | s bit.                        |                          |  |  |

| 6             | WDX2            | (This control<br>has no effect<br>Cleared to se                                                                                                                                                                                                          | Watchdog Clock<br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit<br>has no effect).<br>Cleared to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                   |                                                                          |                                   |                               |                          |  |  |

| 5             | PCAX2           | (This control<br>has no effect<br>Cleared to se                                                                                                                                                                                                          | Programmable Counter Array Clock<br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit<br>has no effect).<br>Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock<br>periods per peripheral clock cycle. |                                                                          |                                   |                               |                          |  |  |

| 4             | SIX2            | (This control<br>has no effect                                                                                                                                                                                                                           | bit is validated).<br>).<br>lect 6 clock p                                                                                                                                                                                                                                  | Mode 0 and 2<br>d when the CP<br>eriods per peri<br>ck cycle.            | U clock X2 is                     |                               |                          |  |  |

| 3             | T2X2            | has no effect<br>Cleared to se                                                                                                                                                                                                                           | bit is validated).<br>elect 6 clock p                                                                                                                                                                                                                                       | d when the CP<br>periods per per<br>ods per periph                       | ipheral clock                     | cycle.                        | s low, this bit          |  |  |

| 2             | T1X2            | has no effect                                                                                                                                                                                                                                            | bit is validated).<br>Iect 6 clock p                                                                                                                                                                                                                                        | d when the CP<br>eriods per peri<br>ck cycle.                            |                                   |                               |                          |  |  |

| 1             | T0X2            | <b>Timer0 Clock</b><br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect).<br>Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle. |                                                                                                                                                                                                                                                                             |                                                                          |                                   |                               |                          |  |  |

| 0             | X2              | all the peripherand to enable                                                                                                                                                                                                                            | erals. Set to set the individuation                                                                                                                                                                                                                                         | periods per m<br>select 6 clock p<br>al peripherals')<br>vare Security E | periods per ma<br>(2' bits. Progr | achine cycle (<br>ammed by ha | X2 mode)<br>rdware after |  |  |

Reset Value = 0000 000'HSB. X2'b (See "Hardware Security Byte") Not bit addressable

## Table 17. CKCON1 Register

CKCON1 - Clock Control Register (AFh)

| 7             | 6               | 5                                 | 4                                                                                                                                                                                                                                               | 3 | 2 | 1 | 0     |  |  |

|---------------|-----------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|-------|--|--|

| -             | -               | -                                 | -                                                                                                                                                                                                                                               | - | - | - | SPIX2 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                       |                                                                                                                                                                                                                                                 |   |   |   |       |  |  |

| 7             | -               | Reserved                          |                                                                                                                                                                                                                                                 |   |   |   |       |  |  |

| 6             | -               | Reserved                          |                                                                                                                                                                                                                                                 |   |   |   |       |  |  |

| 5             | -               | Reserved                          | Reserved                                                                                                                                                                                                                                        |   |   |   |       |  |  |

| 4             | -               | Reserved                          |                                                                                                                                                                                                                                                 |   |   |   |       |  |  |

| 3             | -               | Reserved                          |                                                                                                                                                                                                                                                 |   |   |   |       |  |  |

| 2             | -               | Reserved                          |                                                                                                                                                                                                                                                 |   |   |   |       |  |  |

| 1             | -               | Reserved                          |                                                                                                                                                                                                                                                 |   |   |   |       |  |  |

| 0             | SPIX2           | this bit has no<br>Clear to selec | <b>SPI</b> (This control bit is validated when the CPU clock X2 is set; when X2 is low,<br>his bit has no effect).<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle. |   |   |   |       |  |  |

Reset Value = XXXX XXX0b Not bit addressable

## **Power Monitor**

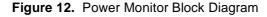

The POR/PFD function monitors the internal power-supply of the CPU core memories and the peripherals, and if needed, suspends their activity when the internal power supply falls below a safety threshold. This is achieved by applying an internal reset to them.

By generating the Reset the Power Monitor insures a correct start up when AT89C51RD2/ED2 is powered up.

**Description** In order to startup and maintain the microcontroller in correct operating mode, V<sub>CC</sub> has to be stabilized in the V<sub>CC</sub> operating range and the oscillator has to be stabilized with a nominal amplitude compatible with logic level VIH/VIL.

These parameters are controlled during the three phases: power-up, normal operation and power going down. See Figure 12.

Note: 1. Once XTAL1 High and low levels reach above and below VIH/VIL. a 1024 clock period delay will extend the reset coming from the Power Fail Detect. If the power falls below the Power Fail Detect threshold level, the Reset will be applied immediately.

The Voltage regulator generates a regulated internal supply for the CPU core the memories and the peripherals. Spikes on the external Vcc are smoothed by the voltage regulator.

| Timer 2          | The Timer 2 in the AT89C51RD2/ED2 is the standard C52 Timer 2. It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2 are cascaded. It is controlled by T2CON (Table 20) and T2MOD (Table 21) registers. Timer 2 operation is similar to Timer 0 and Timer 1. $C/T2$ selects $F_{OSC}/12$ (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to increment by the selected input. |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).                                                                                                                                                                                                                                                                                                                            |

|                  | Refer to the Atmel 8-bit Microcontroller Hardware Manual for the description of Capture and Baud Rate Generator Modes.                                                                                                                                                                                                                                                                                                                                                               |

|                  | Timer 2 includes the following enhancements:                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  | Auto-reload mode with up or down counter                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                  | Programmable clock-output                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Auto-reload Mode | The auto-reload mode configures Timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. If DCEN bit in T2MOD is cleared, Timer 2 behaves as in 80C52 (refer to<br>the Atmel C51 Microcontroller Hardware Manual). If DCEN bit is set, Timer 2 acts as an<br>Up/down timer/counter as shown in Figure 14. In this mode the T2EX pin controls the<br>direction of count.                                                                                                |

|                  | When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                                                                                         |

|                  | When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                                                                                      |

|                  | The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.                                                                                                                                                                                                                                                                                          |

# Serial I/O Port

The serial I/O port in the AT89C51RD2/ED2 is compatible with the serial I/O port in the 80C52.

It provides both synchronous and asynchronous communication modes. It operates as a Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection

- Automatic address recognition

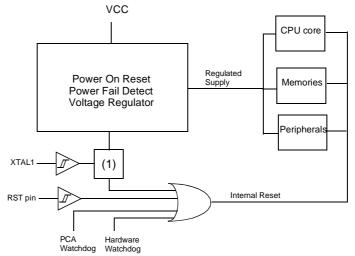

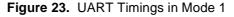

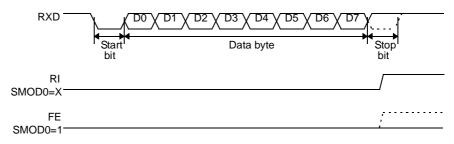

**Framing Error Detection** Framing bit error detection is provided for the three asynchronous modes (modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (See Figure 22).

Figure 22. Framing Error Block Diagram

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 33.) bit is set.

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 23. and Figure 24.).

Table 38. SBUF Register

SBUF - Serial Buffer Register for UART (99h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = XXXX XXXXb

#### Table 39. BRL Register

BRL - Baud Rate Reload Register for the internal baud rate generator, UART (9Ah)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

## Table 40. T2CON Register

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                                       | 4                                                                                                                                                                                                                                                                                                                                 | 3                                                                | 2               | 1              | 0        |  |

|---------------|-----------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------|----------------|----------|--|

| TF2           | EXF2            | RCLK                                                                    | TCLK                                                                                                                                                                                                                                                                                                                              | EXEN2                                                            | TR2             | C/T2#          | CP/RL2#  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                         |                                                                                                                                                                                                                                                                                                                                   | Desc                                                             | ription         |                |          |  |

| 7             | TF2             |                                                                         | ared by softwa                                                                                                                                                                                                                                                                                                                    | are.<br>2 overflow, if                                           | RCLK = 0 and    | d TCLK = 0.    |          |  |

| 6             | EXF2            | Set when a<br>EXEN2=1.<br>When set, c<br>interrupt is e<br>Must be clea | <b>Timer 2 External Flag</b><br>Set when a capture or a reload is caused by a negative transition on T2EX pin if EXEN2=1.<br>When set, causes the CPU to vector to timer 2 interrupt routine when timer 2 nterrupt is enabled.<br>Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down counter mode (DCEN = 1) |                                                                  |                 |                |          |  |

| 5             | RCLK            | Cleared to u                                                            |                                                                                                                                                                                                                                                                                                                                   | ART<br>erflow as rece<br>w as receive o                          |                 |                |          |  |

| 4             | TCLK            | Cleared to u                                                            |                                                                                                                                                                                                                                                                                                                                   | IART<br>erflow as trans<br>w as transmit                         |                 | •              |          |  |

| 3             | EXEN2           | Cleared to ig<br>Set to cause                                           | e a capture or                                                                                                                                                                                                                                                                                                                    | e <b>bit</b><br>on T2EX pin fo<br>reload when a<br>used to clock | a negative trar | nsition on T2E | X pin is |  |

| 2             | TR2             |                                                                         | n control bit<br>urn off timer 2<br>on timer 2.                                                                                                                                                                                                                                                                                   | 2.                                                               |                 |                |          |  |

| 1             | C/T2#           | Cleared for Set for count                                               | <b>Timer/Counter 2 select bit</b><br>Cleared for timer operation (input from internal clock system: F <sub>CLK PERIPH</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be<br>0 for clock out mode.                                                                                     |                                                                  |                 |                |          |  |

| 0             | CP/RL2#         | If RCLK=1 c<br>timer 2 over<br>Cleared to a<br>if EXEN2=1               | Timer 2 Capture/Reload bit<br>If RCLK=1 or TCLK=1, CP/RL2# is ignored and timer is forced to auto-reload on<br>timer 2 overflow.<br>Cleared to auto-reload on timer 2 overflows or negative transitions on T2EX pin<br>if EXEN2=1.<br>Set to capture on negative transitions on T2EX pin if EXEN2=1.                              |                                                                  |                 |                |          |  |

Reset Value = 0000 0000b Bit addressable

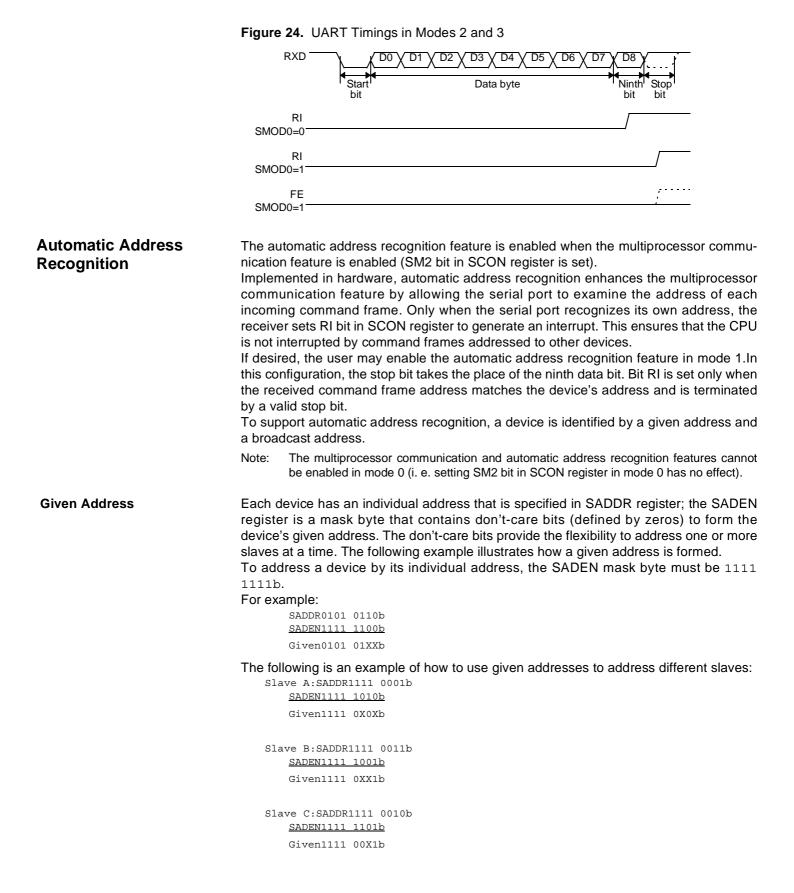

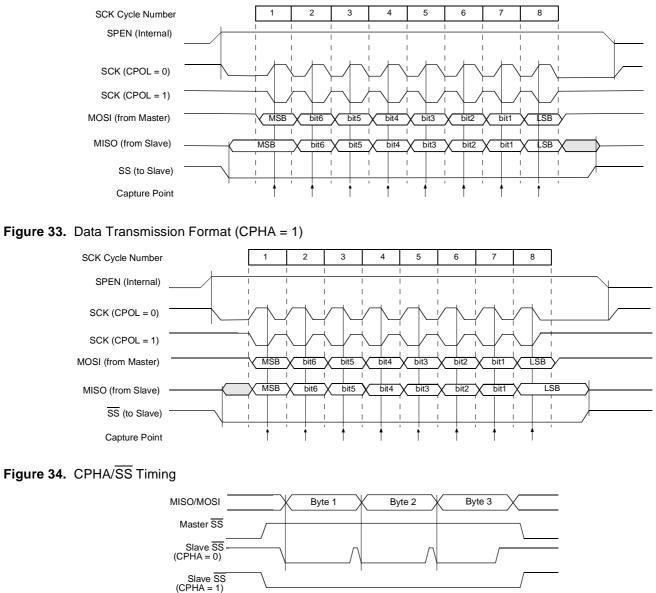

As shown in Figure 32, the first SCK edge is the MSB capture strobe. Therefore, the Slave must begin driving its data before the first SCK edge, and a falling edge on the  $\overline{SS}$  pin is used to start the transmission. The  $\overline{SS}$  pin must be toggled high and then low between each Byte transmitted (Figure 34).

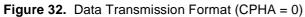

Figure 33 shows an SPI transmission in which CPHA is '1'. In this case, the Master begins driving its MOSI pin on the first SCK edge. Therefore, the Slave uses the first SCK edge as a start transmission signal. The SS pin can remain low between transmissions (Figure 34). This format may be preferred in systems having only one Master and only one Slave driving the MISO data line.

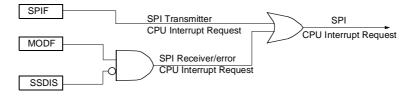

#### Figure 35. SPI Interrupt Requests Generation

There are three registers in the Module that provide control, status and data storage functions. These registers

#### Registers

Register (SPCON)

are describes in the following paragraphs.Serial Peripheral Control• The Serial Peripheral Control Register does the following:

Selects one of the Master clock rates

- Configure the SPI Module as Master or Slave

- Selects serial clock polarity and phase

- Enables the SPI Module

- Frees the SS pin for a general-purpose

Table 48 describes this register and explains the use of each bit

#### Table 48. SPCON Register

SPCON - Serial Peripheral Control Register (0C3H)

| 7          | 6       | 5      | 4                                                                                                                                                                                                                                                          | 3    | 2    | 1    | 0    |  |  |

|------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|

| SPR2       | SPEN    | SSDIS  | MSTR                                                                                                                                                                                                                                                       | CPOL | СРНА | SPR1 | SPR0 |  |  |

| Bit Number | Bit Mne | emonic | Description                                                                                                                                                                                                                                                |      |      |      |      |  |  |

| 7          | SF      | PR2    | Serial Peripheral Rate 2<br>Bit with SPR1 and SPR0 define the clock rate.                                                                                                                                                                                  |      |      |      |      |  |  |

| 6          | SF      | 'EN    | Serial Peripheral Enable<br>Cleared to disable the SPI interface.<br>Set to enable the SPI interface.                                                                                                                                                      |      |      |      |      |  |  |

| 5          | SS      | DIS    | SS Disable         Cleared to enable SS in both Master and Slave modes.         Set to disable SS in both Master and Slave modes. In Slave n         this bit has no effect if CPHA ='0'. When SSDIS is set, no MO         interrupt request is generated. |      |      |      |      |  |  |

| 4          | MS      | STR    | Serial Peripheral Master<br>Cleared to configure the SPI as a Slave.<br>Set to configure the SPI as a Master.                                                                                                                                              |      |      |      |      |  |  |

| 3          | CF      | POL    | Clock Polarity<br>Cleared to have the SCK set to '0' in idle state.<br>Set to have the SCK set to '1' in idle low.                                                                                                                                         |      |      |      |      |  |  |

| 2          | CF      |        | Clock Phase<br>Cleared to have the data sampled when the SCK leaves the<br>state (see CPOL).<br>Set to have the data sampled when the SCK returns to idle sta<br>CPOL).                                                                                    |      |      |      |      |  |  |

# Interrupt Sources and Vector Addresses

| Number | Polling Priority | Interrupt Source | Interrupt<br>Request  | Vector<br>Address |

|--------|------------------|------------------|-----------------------|-------------------|

| 0      | 0                | Reset            |                       | 0000h             |

| 1      | 1                | INT0             | IE0                   | 0003h             |

| 2      | 2                | Timer 0          | TF0                   | 000Bh             |

| 3      | 3                | INT1             | IE1                   | 0013h             |

| 4      | 4                | Timer 1          | IF1                   | 001Bh             |

| 5      | 6                | UART             | RI+TI                 | 0023h             |

| 6      | 7                | Timer 2          | TF2+EXF2              | 002Bh             |

| 7      | 5                | PCA              | CF + CCFn (n = 0 - 4) | 0033h             |

| 8      | 8                | Keyboard         | KBDIT                 | 003Bh             |

| 9      | 9                | -                | -                     | 0043h             |

| 10     | 10               | SPI              | SPIIT                 | 004Bh             |

the SFR and RAM contents are preserved. The status of the Port pins during Power-Down mode is detailed in Table 59.

Note: VCC may be reduced to as low as V<sub>RET</sub> during Power-Down mode to further reduce power dissipation. Take care, however, that VDD is not reduced until Power-Down mode is invoked.

**Entering Power-Down Mode** To enter Power-Down mode, set PD bit in PCON register. The AT89C51RD2/ED2 enters the Power-Down mode upon execution of the instruction that sets PD bit. The instruction that sets PD bit is the last instruction executed.

#### Exiting Power-Down Mode

Note: If VCC was reduced during the Power-Down mode, do not exit Power-Down mode until VCC is restored to the normal operating level.

There are three ways to exit the Power-Down mode:

- 1. Generate an enabled external interrupt.

- The AT89C51RD2/ED2 provides capability to exit from Power-Down using INT0#, INT1#.

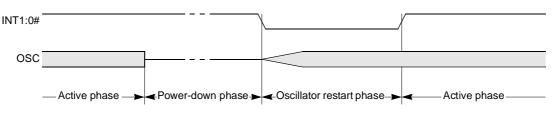

Hardware clears PD bit in PCON register which starts the oscillator and restores the clocks to the CPU and peripherals. Using INTx# input, execution resumes when the input is released (see Figure 37). Execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Power-Down mode.

- Note: The external interrupt used to exit Power-Down mode must be configured as level sensitive (INT0# and INT1#) and must be assigned the highest priority. In addition, the duration of the interrupt must be long enough to allow the oscillator to stabilize. The execution will only resume when the interrupt is deasserted.

- Note: Exit from power-down by external interrupt does not affect the SFRs nor the internal RAM content.

#### Figure 37. Power-Down Exit Waveform Using INT1:0#

- 2. Generate a reset.

- A logic high on the RST pin clears PD bit in PCON register directly and asynchronously. This starts the oscillator and restores the clock to the CPU and peripherals. Program execution momentarily resumes with the instruction immediately following the instruction that activated Power-Down mode and may continue for a number of clock cycles before the internal reset algorithm takes control. Reset initializes the AT89C51RD2/ED2 and vectors the CPU to address 0000h.

| Mnemonic | Definition                                          | Default value | Description                        |

|----------|-----------------------------------------------------|---------------|------------------------------------|

| SBV      | Software Boot Vector                                | FCh           |                                    |

| BSB      | Boot Status Byte                                    | 0FFh          |                                    |

| SSB      | Software Security Byte                              | FFh           |                                    |

|          | Copy of the Manufacturer Code                       | 58h           | Atmel                              |

|          | Copy of the Device ID #1: Family Code               | D7h           | C51 X2, Electrically Erasable      |

|          | Copy of the Device ID #2: Memories Size<br>and Type | ECh           | AT89C51RD2/ED2 64KB                |

|          | Copy of the Device ID #3: Name and Revision         | EFh           | AT89C51RD2/ED2 64KB,<br>Revision 0 |

After programming the part by ISP, the BSB must be cleared (00h) in order to allow the application to boot at 0000h.

The content of the Software Security Byte (SSB) is described in Table 70 and Table 71.

To assure code protection from a parallel access, the HSB must also be at the required level.

Table 70. Software Security Byte

| 7             | 6               | 5                                  | 4                                  | 3 | 2 | 1   | 0   |  |

|---------------|-----------------|------------------------------------|------------------------------------|---|---|-----|-----|--|

| -             | -               | -                                  | -                                  | - | - | LB1 | LB0 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                        |                                    |   |   |     |     |  |

| 7             | -               | <b>Reserved</b><br>Do not clear t  | Reserved<br>Do not clear this bit. |   |   |     |     |  |

| 6             | -               | Reserved<br>Do not clear t         | Reserved<br>Do not clear this bit. |   |   |     |     |  |

| 5             | -               | <b>Reserved</b><br>Do not clear t  | Reserved<br>Do not clear this bit. |   |   |     |     |  |

| 4             | -               | Reserved<br>Do not clear t         | Reserved<br>Do not clear this bit. |   |   |     |     |  |

| 3             | -               | Reserved<br>Do not clear this bit. |                                    |   |   |     |     |  |

| 2             | -               | Reserved<br>Do not clear this bit. |                                    |   |   |     |     |  |

| 1-0           | LB1-0           | User Memory<br>See Table 71        |                                    |   |   |     |     |  |

The two lock bits provide different levels of protection for the on-chip code and data, when programmed as shown in Table 71.

| Program           | Program Lock Bits |     |                                                                       |  |

|-------------------|-------------------|-----|-----------------------------------------------------------------------|--|

| Security<br>Level | LB0               | LB1 | Protection Description                                                |  |

| 1                 | 1                 | 1   | No program lock features enabled.                                     |  |

| 2                 | 0                 | 1   | ISP programming of the Flash is disabled.                             |  |

| 3                 | Х                 | 0   | Same as 2, also verify through ISP programming interface is disabled. |  |

Table 71.

User Memory Lock Bits of the SSB

Note: X: Do not care

WARNING: Security level 2 and 3 should only be programmed after Flash verification.

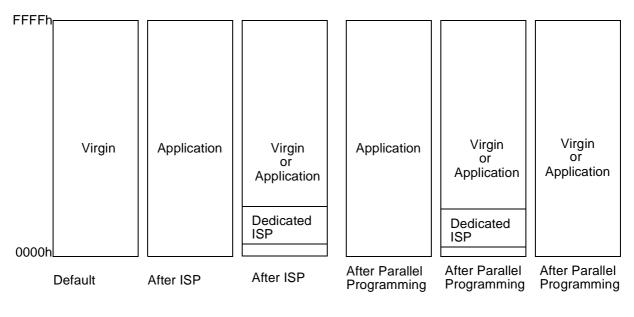

Flash Memory Status AT89C51RD2/ED2 parts are delivered in standard with the ISP ROM bootloader.

After ISP or parallel programming, the possible contents of the Flash memory are summarized in Figure 40:

#### Figure 40. Flash Memory Possible Contents

**Memory Organization** When the EA pin is high, the processor fetches instructions from internal program Flash. If the EA pin is tied low, all program memory fetches are from external memory.

## **ISP Protocol Description**

#### **Physical Layer**

The UART used to transmit information has the following configuration:

- Character: 8-bit data

- Parity: none

- Stop: 2 bits

- Flow control: none

- Baudrate: autobaud is performed by the bootloader to compute the baudrate chosen by the host.

#### Frame Description The Serial Protocol is based on the Intel Hex-type records.

Intel Hex records consist of ASCII characters used to represent hexadecimal values and are summarized below.

#### Figure 45. Intel Hex Type Frame

| Record<br>Mark<br>':' | Reclen | Load<br>Offset | Record<br>Type | Data<br>or<br>Info | Checksum |

|-----------------------|--------|----------------|----------------|--------------------|----------|

| 1-byte                | 1-byte | 2-bytes        | 1-byte         | n-bytes            | 1-byte   |

Record Mark:

Record Mark is the start of frame. This field must contain ':'.

Reclen:

Reclen specifies the number of bytes of information or data which follows the Record Type field of the record.

Load Offset:

Load Offset specifies the 16-bit starting load offset of the data bytes, therefore this field is used only for Data Program Record (see Section "ISP Commands Summary").

• Record Type:

Record Type specifies the command type. This field is used to interpret the remaining information within the frame. The encoding for all the current record types is described in Section "ISP Commands Summary".

Data/Info:

Data/Info is a variable length field. It consists of zero or more bytes encoded as pairs of hexadecimal digits. The meaning of data depends on the **Record Type**.

Checksum:

The two's complement of the 8-bit bytes that result from converting each pair of ASCII hexadecimal digits to one byte of binary, and including the **Reclen** field to and including the last byte of the **Data/Info** field. Therefore, the sum of all the ASCII pairs in a record after converting to binary, from the **Reclen** field to and including the **Checksum** field, is zero.

|                      | ®                                                                                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| API Call Description | The IAP allows to reprogram a microcontroller on-chip Flash memory without removing it from the system and while the embedded application is running. |

|                      | The user application can call some Application Programming Interface (API) routines allowing IAP. These API are executed by the bootloader.           |

|                      | To call the corresponding API, the user must use a set of Flash_api routines which can be linked with the application.                                |

|                      | Example of Flash_api routines are available on the Atmel web site on the software appli-<br>cation note:                                              |

|                      | C Flash Drivers for the AT89C51RD2/ED2                                                                                                                |

|                      | The API calls description and arguments are shown in Table 76.                                                                                        |

| Process              | The application selects an API by setting R1, ACC, DPTR0 and DPTR1 registers.                                                                         |

|                      | All calls are made through a common interface "USER_CALL" at the address FFF0h.                                                                       |

|                      | The jump at the USER_CALL must be done by LCALL instruction to be able to come-<br>back in the application.                                           |

|                      | Before jump at the USER_CALL, the bit ENBOOT in AUXR1 register must be set.                                                                           |

| Constraints          | The interrupts are not disabled by the bootloader.                                                                                                    |

|                      | Interrupts must be disabled by user prior to jump to the USER_CALL, then re-enabled when returning.                                                   |

|                      | Interrupts must also be disabled before accessing EEPROM Data then re-enabled after.                                                                  |

MEL

The user must take care of hardware watchdog before launching a Flash operation.

| Command              | R1  | Α             | DPTR0                            | DPTR1 | Returned Value           | Command Effect                                        |

|----------------------|-----|---------------|----------------------------------|-------|--------------------------|-------------------------------------------------------|

| READ MANUF ID        | 00h | XXh           | 0000h                            | XXh   | ACC = Manufacturer<br>Id | Read Manufacturer identifier                          |

| READ DEVICE ID1      | 00h | XXh           | 0001h                            | XXh   | ACC = Device Id 1        | Read Device identifier 1                              |

| READ DEVICE ID2      | 00h | XXh           | 0002h                            | XXh   | ACC = Device Id 2        | Read Device identifier 2                              |

| READ DEVICE ID3      | 00h | XXh           | 0003h                            | XXh   | ACC = Device Id 3        | Read Device identifier 3                              |

|                      | 01h | XXh           | DPH = 00h                        | 00h   | ACC = DPH                | Erase block 0                                         |

| ERASE BLOCK          |     |               | DPH = 20h                        |       |                          | Erase block 1                                         |

|                      |     |               | DPH = 40h                        |       |                          | Erase block 2                                         |

|                      |     |               | DPH = 80h                        |       |                          | Erase block 3                                         |

|                      |     |               | DPH = C0h                        |       |                          | Erase block 4                                         |

| PROGRAM DATA<br>BYTE | 02h | Vaue to write | Address of<br>byte to<br>program | XXh   | ACC = 0: DONE            | Program up one data byte in the on-chip flash memory. |

## Table 76. API Call Summary

Maximum total  $I_{OL}$  for all output pins: 71 mA If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

7. The maximum dV/dt value specifies the maximum Vcc drop to issure no internal POR/PFD reset.

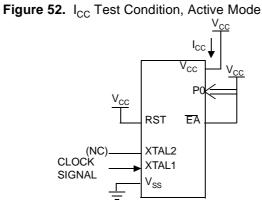

All other pins are disconnected.

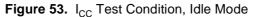

All other pins are disconnected.

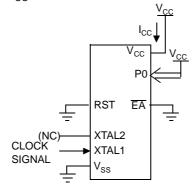

All other pins are disconnected.

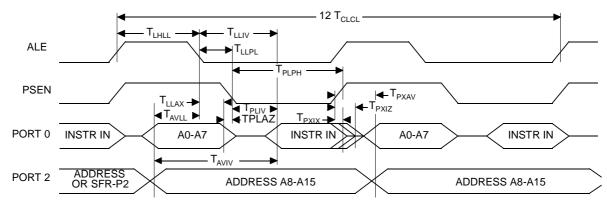

#### External Program Memory Read Cycle

#### External Data Memory Characteristics

Table 80. Symbol Description

| Symbol            | Parameter                                           |  |  |  |  |  |

|-------------------|-----------------------------------------------------|--|--|--|--|--|

| T <sub>RLRH</sub> | RD Pulse Width                                      |  |  |  |  |  |

| T <sub>WLWH</sub> | WR Pulse Width                                      |  |  |  |  |  |

| T <sub>RLDV</sub> | RD to Valid Data In                                 |  |  |  |  |  |

| T <sub>RHDX</sub> | Data Hold After RD                                  |  |  |  |  |  |

| T <sub>RHDZ</sub> | Data Float After RD                                 |  |  |  |  |  |

| T <sub>LLDV</sub> | ALE to Valid Data In                                |  |  |  |  |  |

| T <sub>AVDV</sub> | Address to Valid Data In                            |  |  |  |  |  |

| T <sub>LLWL</sub> | ALE to WR or RD                                     |  |  |  |  |  |

| T <sub>AVWL</sub> | Address to $\overline{WR}$ or $\overline{RD}$       |  |  |  |  |  |

| T <sub>QVWX</sub> | Data Valid to WR Transition                         |  |  |  |  |  |

| T <sub>QVWH</sub> | Data Set-up to WR High                              |  |  |  |  |  |

| T <sub>WHQX</sub> | Data Hold After WR                                  |  |  |  |  |  |

| T <sub>RLAZ</sub> | RD Low to Address Float                             |  |  |  |  |  |

| T <sub>WHLH</sub> | $\overline{RD}$ or $\overline{WR}$ High to ALE high |  |  |  |  |  |

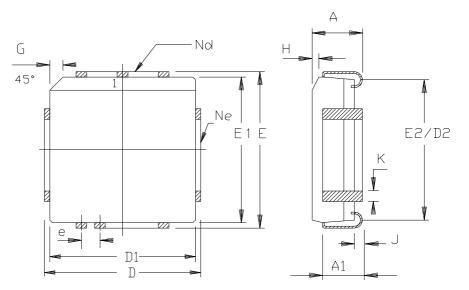

PLCC68

|    | м      | М      | INCH  |        |  |

|----|--------|--------|-------|--------|--|

|    | 111    | 1.1    |       |        |  |

| A  | 4. 20  | 5.08   | .165  | . 200  |  |

| A1 | 2, 29  | 3.30   | . 090 | . 1 30 |  |

| D  | 25.02  | 25. 27 | . 985 | . 995  |  |

| D1 | 24.13  | 24. 33 | . 950 | . 958  |  |

| D2 | 22. 61 | 23. 62 | . 890 | . 930  |  |

| E  | 25.02  | 25. 27 | . 985 | . 995  |  |

| E1 | 24.13  | 24. 33 | . 950 | . 958  |  |

| E5 | 22. 61 | 23. 62 | . 890 | . 930  |  |

| е  | 1.27   | BSC    | . 050 | BSC    |  |

| G  | 1.07   | 1.22   | .042  | . 048  |  |

| н  | 1.07   | 1.42   | .042  | .056   |  |

| J  | 0.51   | -      | . 020 | -      |  |

| К  | 0.33   | 0.53   | . 013 | . 021  |  |

| Nd | 1      | 7      | 1     | 7      |  |

| Ne | 17     |        | 17    |        |  |

| PI | KG STD | 00     |       |        |  |

130 AT89C51RD2/ED2