Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

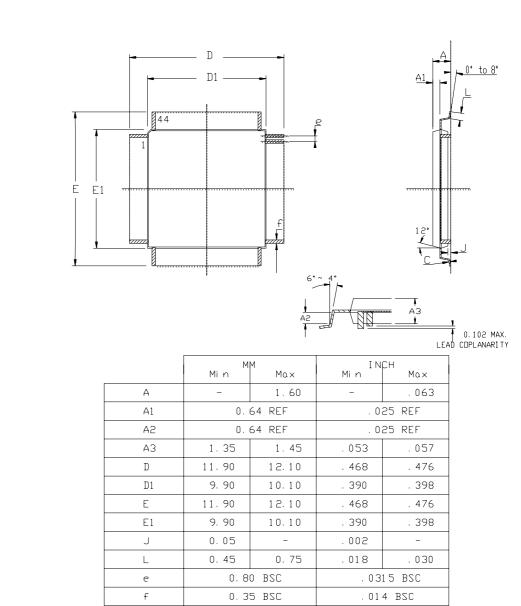

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ed2-slsim |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

## Registers

### Table 19. AUXR Register

AUXR - Auxiliary Register (8Eh)

| 7             | 6               | 5                                          | 4                                                                                                                                                                                                                                                        | 3                                                       | 2     | 1      | 0  |  |  |  |

|---------------|-----------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------|--------|----|--|--|--|

| DPU           | -               | МО                                         | XRS2                                                                                                                                                                                                                                                     | XRS1                                                    | XRS0  | EXTRAM | AO |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                | Description                                                                                                                                                                                                                                              |                                                         |       |        |    |  |  |  |

| 7             | DPU             | Cleared by s                               | Disable Weak Pull-up<br>Cleared by software to activate the permanent weak pull-up (default)<br>Set by software to disable the weak pull-up (reduce power consumption)                                                                                   |                                                         |       |        |    |  |  |  |

| 6             | -               | Reserved<br>The value re                   | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                                                          |                                                         |       |        |    |  |  |  |

| 5             | MO              | Cleared to st<br>periods (defa             | Pulse length<br>Cleared to stretch MOVX control: the $\overline{RD}$ and the $\overline{WR}$ pulse length is 6 clock<br>periods (default).<br>Set to stretch MOVX control: the $\overline{RD}$ and the $\overline{WR}$ pulse length is 30 clock periods. |                                                         |       |        |    |  |  |  |

| 4             | XRS2            | XRAM Size                                  |                                                                                                                                                                                                                                                          |                                                         |       |        |    |  |  |  |

| 3             | XRS1            | <u>XRS2</u> <u>XR</u><br>0 0               | <u>8S1</u> <u>XRS0</u><br>0                                                                                                                                                                                                                              | <u>XRAM size</u><br>256 bytes                           |       |        |    |  |  |  |

| 2             | XRS0            | 0 0<br>0 1<br>0 1<br>1 0                   | 1<br>0<br>1<br>0                                                                                                                                                                                                                                         | 512 bytes<br>768 bytes(defa<br>1024 bytes<br>1792 bytes | ault) |        |    |  |  |  |

| 1             | EXTRAM          | Cleared to a<br>Set to acces<br>Programmed | EXTRAM bit<br>Cleared to access internal XRAM using movx @ Ri/ @ DPTR.<br>Set to access external memory.<br>Programmed by hardware after Power-up regarding Hardware Security Byte<br>(HSB), default setting, XRAM selected.                             |                                                         |       |        |    |  |  |  |

| 0             | AO              |                                            | E is emitted a<br>used). (defau                                                                                                                                                                                                                          | t a constant rat<br>lt) Set, ALE is a                   |       | •      |    |  |  |  |

Reset Value = 0X00 10'HSB. XRAM'0b Not bit addressable

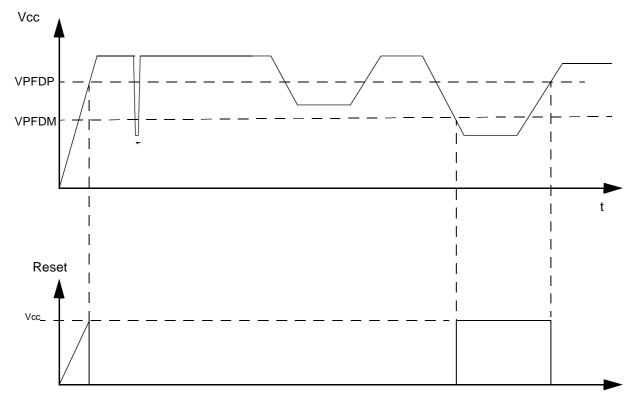

The Power fail detect monitor the supply generated by the voltage regulator and generate a reset if this supply falls below a safety threshold as illustrated in the Figure 13 below.

When the power is applied, the Power Monitor immediately asserts a reset. Once the internal supply after the voltage regulator reach a safety level, the power monitor then looks at the XTAL clock input. The internal reset will remain asserted until the Xtal1 levels are above and below VIH and VIL. Further more. An internal counter will count 1024 clock periods before the reset is de-asserted.

If the internal power supply falls below a safety level, a reset is immediately asserted.

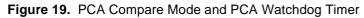

### Table 22. CMOD Register

CMOD - PCA Counter Mode Register (D9h)

| 7             | 6               | 5                                                                                  | 4                                                                                                                                                             | 3               | 2              | 1            | 0   |  |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|-----|--|--|--|

| CIDL          | WDTE            | -                                                                                  | -                                                                                                                                                             | -               | CPS1           | CPS0         | ECF |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                        | Description                                                                                                                                                   |                 |                |              |     |  |  |  |

| 7             | CIDL            | Cleared to p                                                                       | Counter Idle Control<br>Cleared to program the PCA Counter to continue functioning during idle Mode.<br>Set to program PCA to be gated off during idle.       |                 |                |              |     |  |  |  |

| 6             | WDTE            | Cleared to di                                                                      | <b>Watchdog Timer Enable</b><br>Cleared to disable Watchdog Timer function on PCA Module 4.<br>Set to enable Watchdog Timer function on PCA Module 4.         |                 |                |              |     |  |  |  |

| 5             | -               | Reserved<br>The value re                                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                               |                 |                |              |     |  |  |  |

| 4             | -               | Reserved<br>The value re                                                           | ad from this b                                                                                                                                                | it is indetermi | nate. Do not s | et this bit. |     |  |  |  |

| 3             | -               | Reserved<br>The value re                                                           | ad from this b                                                                                                                                                | it is indetermi | nate. Do not s | et this bit. |     |  |  |  |

| 2             | CPS1            | PCA Count                                                                          | Pulse Select                                                                                                                                                  |                 |                |              |     |  |  |  |

| 1             | CPS0            | CPS1         CPS           0         0           1         0           1         1 | 0     1     Internal clock F <sub>CLK PERIPH</sub> /2       1     0     Timer 0 Overflow                                                                      |                 |                |              |     |  |  |  |

| 0             | ECF             | Cleared to di                                                                      | PCA Enable Counter Overflow Interrupt<br>Cleared to disable CF bit in CCON to inhibit an interrupt.<br>Set to enable CF bit in CCON to generate an interrupt. |                 |                |              |     |  |  |  |

Reset Value = 00XX X000b Not bit addressable

The CCON register contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (Refer to Table 23).

- Bit CR (CCON.6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

- Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software.

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn | Module Function                                   |

|-------|-------|-------|------|------|------|-------|---------------------------------------------------|

| 0     | 0     | 0     | 0    | 0    | 0    | 0     | No Operation                                      |

| х     | 1     | 0     | 0    | 0    | 0    | х     | 16-bit capture by a positive-edge trigger on CEXn |

| х     | 0     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a negative trigger on CEXn      |

| х     | 1     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a transition on CEXn            |

| 1     | 0     | 0     | 1    | 0    | 0    | х     | 16-bit Software Timer/Compare mode.               |

| 1     | 0     | 0     | 1    | 1    | 0    | Х     | 16-bit High Speed Output                          |

| 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                         |

| 1     | 0     | 0     | 1    | Х    | 0    | Х     | Watchdog Timer (module 4 only)                    |

Table 25. PCA Module Modes (CCAPMn Registers)

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output (See Table 26 & Table 27).

Table 26. CCAPnH Registers (n = 0 - 4)

6

CCAP0H - PCA Module 0 Compare/Capture Control Register High (0FAh)

CCAP1H - PCA Module 1 Compare/Capture Control Register High (0FBh)

CCAP2H - PCA Module 2 Compare/Capture Control Register High (0FCh)

CCAP3H - PCA Module 3 Compare/Capture Control Register High (0FDh)

CCAP4H - PCA Module 4 Compare/Capture Control Register High (0FEh)

٨

5

| 1             | 0               | 5                        | - | 5           | 2    | • | U |

|---------------|-----------------|--------------------------|---|-------------|------|---|---|

| -             | -               | -                        | - | -           | -    | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description              |   |             |      |   |   |

| 7 - 0         | -               | PCA Module<br>CCAPnH Val |   | Capture Con | trol |   |   |

2

2

1

Λ

Reset Value = 0000 0000b Not bit addressable

7

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen. Writing to CCAPnH will set the ECOM bit.

Once ECOM is set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

#### **High Speed Output Mode** In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the modules capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (See Figure 20).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

## Serial I/O Port

The serial I/O port in the AT89C51RD2/ED2 is compatible with the serial I/O port in the 80C52.

It provides both synchronous and asynchronous communication modes. It operates as a Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection

- Automatic address recognition

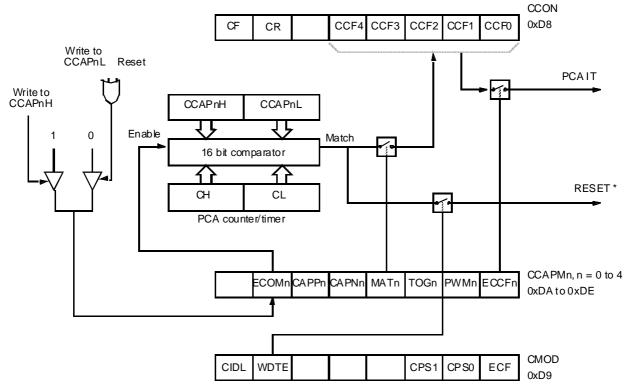

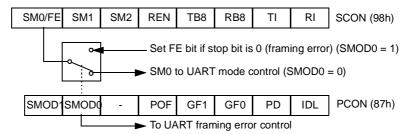

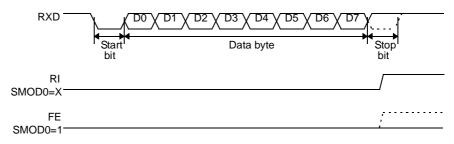

**Framing Error Detection** Framing bit error detection is provided for the three asynchronous modes (modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (See Figure 22).

Figure 22. Framing Error Block Diagram

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 33.) bit is set.

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 23. and Figure 24.).

Table 38. SBUF Register

SBUF - Serial Buffer Register for UART (99h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = XXXX XXXXb

### Table 39. BRL Register

BRL - Baud Rate Reload Register for the internal baud rate generator, UART (9Ah)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

### Table 41. PCON Register

PCON - Power Control Register (87h)

| 7             | 6               | 5                                           | 4                                                                                                                                                        | 3                               | 2            | 1  | 0   |  |  |  |

|---------------|-----------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------|----|-----|--|--|--|

| SMOD1         | SMOD0           | -                                           | POF                                                                                                                                                      | GF1                             | GF0          | PD | IDL |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                             | Description                                                                                                                                              |                                 |              |    |     |  |  |  |

| 7             | SMOD1           |                                             | Serial port Mode bit 1 for UART<br>Set to select double baud rate in mode 1, 2 or 3.                                                                     |                                 |              |    |     |  |  |  |

| 6             | SMOD0           | Cleared to s                                | Serial port Mode bit 0 for UART<br>Cleared to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register.                                 |                                 |              |    |     |  |  |  |

| 5             | -               | Reserved<br>The value re                    | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                          |                                 |              |    |     |  |  |  |

| 4             | POF             | Cleared to re<br>Set by hard                | Power-Off Flag<br>Cleared to recognize next reset type.<br>Set by hardware when VCC rises from 0 to its nominal voltage. Can also be set<br>by software. |                                 |              |    |     |  |  |  |

| 3             | GF1             |                                             | user for gener                                                                                                                                           | al purpose usa<br>irpose usage. | age.         |    |     |  |  |  |

| 2             | GF0             |                                             | user for gener                                                                                                                                           | al purpose usa<br>irpose usage. | age.         |    |     |  |  |  |

| 1             | PD              | Cleared by I                                | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                           |                                 |              |    |     |  |  |  |

| 0             | IDL             | Idle mode I<br>Cleared by I<br>Set to enter | nardware whe                                                                                                                                             | en interrupt or i               | eset occurs. |    |     |  |  |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

### Table 44. KBE Register

KBE-Keyboard Input Enable Register (9Dh)

| 7             | 6               | 5             | 4                                                                                                                                                     | 3    | 2             | 1              | 0     |  |  |  |

|---------------|-----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|----------------|-------|--|--|--|

| KBE7          | KBE6            | KBE5          | KBE4                                                                                                                                                  | KBE3 | KBE2          | KBE1           | KBE0  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description   | Description                                                                                                                                           |      |               |                |       |  |  |  |

| 7             | KBE7            | Cleared to en | <b>Keyboard line 7 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.7 bit in KBF register to generate an interrupt request. |      |               |                |       |  |  |  |

| 6             | KBE6            | Cleared to en | <b>Keyboard line 6 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.6 bit in KBF register to generate an interrupt request. |      |               |                |       |  |  |  |

| 5             | KBE5            | Cleared to en | <b>Keyboard line 5 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.5 bit in KBF register to generate an interrupt request. |      |               |                |       |  |  |  |

| 4             | KBE4            | Cleared to en | <b>ne 4 Enable I</b><br>nable standar<br>e KBF.4 bit in                                                                                               |      | o generate an | interrupt requ | iest. |  |  |  |

| 3             | KBE3            | Cleared to en | ne 3 Enable I<br>nable standar<br>e KBF.3 bit in                                                                                                      |      | o generate an | interrupt requ | iest. |  |  |  |

| 2             | KBE2            | Cleared to en | ne 2 Enable I<br>nable standar<br>e KBF.2 bit in                                                                                                      |      | o generate an | interrupt requ | iest. |  |  |  |

| 1             | KBE1            | Cleared to en | <b>Keyboard line 1 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.1 bit in KBF register to generate an interrupt request. |      |               |                |       |  |  |  |

| 0             | KBE0            | Cleared to en | ne 0 Enable I<br>nable standar<br>e KBF.0 bit in                                                                                                      |      | o generate an | interrupt requ | iest. |  |  |  |

Reset Value = 0000 0000b

| Bit Number | Bit Mnemonic | Descri | ption |      |                              |

|------------|--------------|--------|-------|------|------------------------------|

|            |              | SPR2   | SPR1  | SPR0 | Serial Peripheral Rate       |

| 1          | SPR1         | 0      | 0     | 0    | F <sub>CLK PERIPH</sub> /2   |

| 1          |              | 0      | 0     | 1    | F <sub>CLK PERIPH</sub> /4   |

|            |              | 0      | 1     | 0    | F <sub>CLK PERIPH</sub> /8   |

|            |              | 0      | 1     | 1    | F <sub>CLK PERIPH</sub> /16  |

|            |              | 1      | 0     | 0    | F <sub>CLK PERIPH</sub> /32  |

| 0          | SPR0         | 1      | 0     | 1    | F <sub>CLK PERIPH</sub> /64  |

| -          |              | 1      | 1     | 0    | F <sub>CLK PERIPH</sub> /128 |

|            |              | 1      | 1     | 1    | Invalid                      |

Reset Value = 0001 0100b

Not bit addressable

Serial Peripheral Status Register The Serial Peripheral Status Register contains flags to signal the following conditions:

(SPSTA)

- Data transfer complete

- Write collision

- Inconsistent logic level on SS pin (mode fault error)

Table 49 describes the SPSTA register and explains the use of every bit in the register.

#### Table 49. SPSTA Register

SPSTA - Serial Peripheral Status and Control register (0C4H)

| 7             | 6               | 5                                                                                                                                                                                                                              | 4                                                                                                                                                                                                         | 3                                                   | 2               | 1            | 0        |  |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------|--------------|----------|--|--|--|--|

| SPIF          | WCOL            | SSERR                                                                                                                                                                                                                          | MODF                                                                                                                                                                                                      | -                                                   | -               | -            | -        |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                    | Description                                                                                                                                                                                               |                                                     |                 |              |          |  |  |  |  |

| 7             | SPIF            | Serial Peripheral Data Transfer Flag<br>Cleared by hardware to indicate data transfer is in progress or has been<br>approved by a clearing sequence.<br>Set by hardware to indicate that the data transfer has been completed. |                                                                                                                                                                                                           |                                                     |                 |              |          |  |  |  |  |

| 6             | WCOL            | Cleared by ha                                                                                                                                                                                                                  | Write Collision Flag<br>Cleared by hardware to indicate that no collision has occurred or has been<br>approved by a clearing sequence.<br>Set by hardware to indicate that a collision has been detected. |                                                     |                 |              |          |  |  |  |  |

| 5             | SSERR           | -                                                                                                                                                                                                                              | are when $\overline{SS}$                                                                                                                                                                                  | e Error Flag<br>is de-asserted<br>PI (clearing Sl   |                 |              | ed data. |  |  |  |  |

| 4             | MODF            | has been app                                                                                                                                                                                                                   | proved by a cl                                                                                                                                                                                            | dicate that the<br>earing sequer<br>e that the SS p | nce.            |              |          |  |  |  |  |

| 3             | -               | Reserved<br>The value rea                                                                                                                                                                                                      | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                                                                                                            |                                                     |                 |              |          |  |  |  |  |

| 2             | -               | Reserved<br>The value rea                                                                                                                                                                                                      | ad from this b                                                                                                                                                                                            | it is indetermir                                    | nate. Do not se | et this bit. |          |  |  |  |  |

## Registers

## Table 60. PCON Register

PCON (S87:h) Power configuration Register

| 7             | 6               | 5                                             | 4                                                                                                                                                                         | 3                                         | 2             | 1              | 0            |  |  |  |

|---------------|-----------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------|----------------|--------------|--|--|--|

| -             | -               | -                                             | -                                                                                                                                                                         | GF1                                       | GF0           | PD             | IDL          |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                   |                                                                                                                                                                           |                                           |               |                |              |  |  |  |

| 7-4           | -               | Reserved<br>The value rea                     | Reserved<br>The value read from these bits is indeterminate. Do not set these bits.                                                                                       |                                           |               |                |              |  |  |  |

| 3             | GF1             | One use is to                                 | General Purpose flag 1<br>One use is to indicate whether an interrupt occurred during normal operation or<br>during Idle mode.                                            |                                           |               |                |              |  |  |  |

| 2             | GF0             | General Pur<br>One use is to<br>during Idle m | indicate whe                                                                                                                                                              | ether an interru                          | pt occurred d | uring normal o | operation or |  |  |  |

| 1             | PD              | Cleared by h<br>Set to activat                | Power-Down Mode bit<br>Cleared by hardware when an interrupt or reset occurs.<br>Set to activate the Power-Down mode.<br>If IDL and PD are both set, PD takes precedence. |                                           |               |                |              |  |  |  |

| 0             | IDL             | Set to activat                                | ardware when<br>the Idle mo                                                                                                                                               | n an interrupt o<br>de.<br>, PD takes pre |               | S.             |              |  |  |  |

Reset Value= XXXX 0000b

|                                                                                                                                                                          | Table 68.                                                                                                                                                               | Prog                                                                                                                                                                                             | ram Lo | ck Bit           | S                                                                                                                                                                                                                                                                                                   |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                          | Prog                                                                                                                                                                    | Program Lock Bits                                                                                                                                                                                |        |                  |                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                          | Security<br>Level                                                                                                                                                       | -                                                                                                                                                                                                |        | LB2              | Protection Description                                                                                                                                                                                                                                                                              |  |  |  |

|                                                                                                                                                                          | 1                                                                                                                                                                       | U                                                                                                                                                                                                | U      | U                | No program lock features enabled.                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                                                                                                                          | 2                                                                                                                                                                       | 2 P U U<br>3 X P U                                                                                                                                                                               |        | U                | MOVC instruction executed from external program memory is disabled<br>from fetching code bytes from internal memory, EA is sampled and<br>latched on reset, and further parallel programming of the on chip code<br>memory is disabled.<br>ISP and software programming with API are still allowed. |  |  |  |

|                                                                                                                                                                          | 3                                                                                                                                                                       |                                                                                                                                                                                                  |        | U                | Same as 2, also verify code memory through parallel programming interface is disabled.                                                                                                                                                                                                              |  |  |  |

|                                                                                                                                                                          | 4                                                                                                                                                                       | Х                                                                                                                                                                                                | х      | Р                | Same as 3, also external execution is disabled (Default).                                                                                                                                                                                                                                           |  |  |  |

|                                                                                                                                                                          | P:<br>X:<br>W                                                                                                                                                           | Note: U: Unprogrammed or "one" level.<br>P: Programmed or "zero" level.<br>X: Do not care<br>WARNING: Security level 2 and 3 should only be programme<br>verification.                           |        |                  |                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                          | They are s                                                                                                                                                              | he code access through the parallel programming interface.<br>vel 4. The code access through the ISP is still possible and<br>e security bits" which are stored in the extra Flash memory<br>re. |        |                  |                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                          | th the parallel programmer, a chip erase must first be done.<br>nactive state and will erase the Flash memory. The part ref-<br>using Flash parallel programming modes. |                                                                                                                                                                                                  |        |                  |                                                                                                                                                                                                                                                                                                     |  |  |  |

| Default ValuesThe default value of the HSB provides parts ready to be program• BLJB: Programmed force ISP operation.• X2: Unprogrammed to force X1 mode (Standard Mode). |                                                                                                                                                                         |                                                                                                                                                                                                  |        | e ISP operation. |                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                          | <ul> <li>X2: Unprogrammed to force X1 mode (standard Mode).</li> <li>XRAM: Unprogrammed to valid XRAM</li> </ul>                                                        |                                                                                                                                                                                                  |        |                  |                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                          | <ul> <li>LB2-0: Security level four to protect the code from a parallel access with maximum security.</li> </ul>                                                        |                                                                                                                                                                                                  |        |                  |                                                                                                                                                                                                                                                                                                     |  |  |  |

| Software Registers                                                                                                                                                       | Several registers are used in factory and by parallel programmers. These values are used by Atmel ISP.                                                                  |                                                                                                                                                                                                  |        |                  |                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                          |                                                                                                                                                                         | These registers are in the "Extra Flash Memory" part of the Flash memory. This block is also called "XAF" or eXtra Array Flash. They are accessed in the following ways:                         |        |                  |                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                          | Commands issued by the parallel memory programmer.                                                                                                                      |                                                                                                                                                                                                  |        |                  |                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                          | Commands issued by the ISP software.                                                                                                                                    |                                                                                                                                                                                                  |        |                  |                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                          | <ul> <li>Calls of API issued by the application software.</li> </ul>                                                                                                    |                                                                                                                                                                                                  |        |                  |                                                                                                                                                                                                                                                                                                     |  |  |  |

Table 68 Program Lock Bits

Several software registers are described in Table 69.

| Mnemonic | Definition                                                                                                                                                                                                                             | Default value | Description                        |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------|

| SBV      | SBVSoftware Boot VectorBSBBoot Status ByteSSBSoftware Security ByteCopy of the Manufacturer CodeCopy of the Device ID #1: Family CodeCopy of the Device ID #2: Memories Size<br>and TypeCopy of the Device ID #3: Name and<br>Revision |               |                                    |

| BSB      |                                                                                                                                                                                                                                        |               |                                    |

| SSB      |                                                                                                                                                                                                                                        |               |                                    |

|          |                                                                                                                                                                                                                                        |               | Atmel                              |

|          |                                                                                                                                                                                                                                        |               | C51 X2, Electrically Erasable      |

|          |                                                                                                                                                                                                                                        |               | AT89C51RD2/ED2 64KB                |

|          |                                                                                                                                                                                                                                        |               | AT89C51RD2/ED2 64KB,<br>Revision 0 |

After programming the part by ISP, the BSB must be cleared (00h) in order to allow the application to boot at 0000h.

The content of the Software Security Byte (SSB) is described in Table 70 and Table 71.

To assure code protection from a parallel access, the HSB must also be at the required level.

Table 70. Software Security Byte

| 7             | 6               | 5                                                                                          | 4        | 3 | 2 | 1   | 0   |

|---------------|-----------------|--------------------------------------------------------------------------------------------|----------|---|---|-----|-----|

| -             | -               | -                                                                                          | -        | - | - | LB1 | LB0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                |          |   |   |     |     |

| 7             | -               | <b>Reserved</b><br>Do not clear t                                                          | his bit. |   |   |     |     |

| 6             | -               | Reserved<br>Do not clear this bit.                                                         |          |   |   |     |     |

| 5             | -               | Reserved         Do not clear this bit.         Reserved         Do not clear this bit.    |          |   |   |     |     |

| 4             | -               |                                                                                            |          |   |   |     |     |

| 3             | -               | Reserved<br>Do not clear this bit.                                                         |          |   |   |     |     |

| 2             | -               | Reserved         Do not clear this bit.         User Memory Lock Bits         See Table 71 |          |   |   |     |     |

| 1-0           | LB1-0           |                                                                                            |          |   |   |     |     |

The two lock bits provide different levels of protection for the on-chip code and data, when programmed as shown in Table 71.

### **Functional Description**

Software Security Bits (SSB)The SSB protects any Flash access from ISP command.<br/>The command "Program Software Security Bit" can only write a higher priority level.

There are three levels of security:

level 0: NO\_SECURITY (FFh)

This is the default level. From level 0, one can write level 1 or level 2.

#### level 1: WRITE\_SECURITY (FEh)

For this level it is impossible to write in the Flash memory, BSB and SBV. The Bootloader returns 'P' on write access. From level 1, one can write only level 2.

• level 2: RD\_WR\_SECURITY (FCh

The level 2 forbids all read and write accesses to/from the Flash/EEPROM memory.

The Bootloader returns 'L' on read or write access.

Only a full chip erase in parallel mode (using a programmer) or ISP command can reset the software security bits.

From level 2, one cannot read and write anything.

|                      | Level 0                                     | Level 1                  | Level 2                                              |  |  |

|----------------------|---------------------------------------------|--------------------------|------------------------------------------------------|--|--|

| Flash/EEPROM         | Any access allowed                          | Read-only access allowed | Any access not allowed                               |  |  |

| Fuse Bit             | Any access allowed Read-only access allowed |                          | Any access not allowed                               |  |  |

| BSB & SBV            | Any access allowed                          | Read-only access allowed | Any access not allowed                               |  |  |

| SSB                  | Any access allowed                          | Write level 2 allowed    | Read-only access allowed<br>Read-only access allowed |  |  |

| Manufacturer<br>Info | Read-only access allowed                    | Read-only access allowed |                                                      |  |  |

| Bootloader Info      | Read-only access allowed                    | Read-only access allowed | Read-only access allowed                             |  |  |

| Erase Block          | Allowed                                     | Not allowed              | Not allowed                                          |  |  |

| Full Chip Erase      | Allowed                                     | Allowed                  | Allowed                                              |  |  |

| Blank Check          | Allowed                                     | Allowed                  | Allowed                                              |  |  |

Table 73. Software Security Byte Behavior

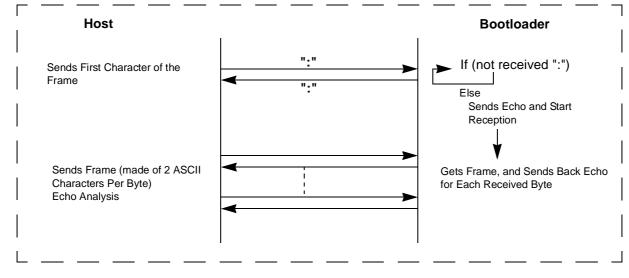

### Figure 47. Command Flow

## **Electrical Characteristics**

## **Absolute Maximum Ratings**

| I = industrial<br>Storage Temperature<br>Voltage on $V_{CC}$ to $V_{SS}$<br>VVoltage on Any Pin to $V_{SS}$<br>Power Dissipation | -65°C to + 150°C<br> |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Power Dissipation                                                                                                                | 1 W <sup>(2)</sup>   |

|                                                                                                                                  |                      |

Note: Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Power dissipation is based on the maximum allowable die temperature and the thermal resistance of the package.

### **DC Parameters for Standard Voltage**

$T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ;  $V_{SS} = 0V$ ;

$V_{CC}$  =2.7V to 5.5V and F = 0 to 40 MHz (both internal and external code execution)

$V_{CC}$  =4.5V to 5.5V and F = 0 to 60 MHz (internal code execution only)

| Symbol           | Parameter                                            | Min                                                                     | Тур | Max                       | Unit        | Test Conditions                                                                                                                                        |

|------------------|------------------------------------------------------|-------------------------------------------------------------------------|-----|---------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                    | -0.5                                                                    |     | 0.2 V <sub>CC</sub> - 0.1 | V           |                                                                                                                                                        |

| V <sub>IH</sub>  | Input High Voltage except RST, XTAL1                 | 0.2 V <sub>CC</sub> + 0.9                                               |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                                                        |

| V <sub>IH1</sub> | Input High Voltage RST, XTAL1                        | 0.7 V <sub>CC</sub>                                                     |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                                                        |

| V <sub>OL</sub>  | Output Low Voltage, ports 1, 2, 3, 4 <sup>(6)</sup>  |                                                                         |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} V_{CC} &= 4.5 V \text{ to } 5.5 V \\ I_{OL} &= 100 \ \mu A^{(4)} \\ I_{OL} &= 1.6 \ m A^{(4)} \\ I_{OL} &= 3.5 \ m A^{(4)} \end{split}$ |

|                  |                                                      |                                                                         |     | 0.45                      | V           | $V_{CC} = 2.7V \text{ to } 5.5V$<br>$I_{OL} = 0.8 \text{ mA}^{(4)}$                                                                                    |

| V <sub>OL1</sub> | Output Low Voltage, port 0, ALE, PSEN <sup>(6)</sup> |                                                                         |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} V_{CC} &= 4.5 V \text{ to } 5.5 V \\ I_{OL} &= 200 \ \mu A^{(4)} \\ I_{OL} &= 3.2 \ m A^{(4)} \\ I_{OL} &= 7.0 \ m A^{(4)} \end{split}$ |

|                  |                                                      |                                                                         |     | 0.45                      | V           | $V_{CC} = 2.7V \text{ to } 5.5V$<br>$I_{OL} = 1.6 \text{ mA}^{(4)}$                                                                                    |

| V <sub>OH</sub>  | Output High Voltage, ports 1, 2, 3, 4                | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |     |                           | V<br>V<br>V | $V_{CC} = 5V \pm 10\%$<br>$I_{OH} = -10 \ \mu A$<br>$I_{OH} = -30 \ \mu A$<br>$I_{OH} = -60 \ \mu A$                                                   |

|                  |                                                      | 0.9 V <sub>CC</sub>                                                     |     |                           | V           | $V_{CC}$ = 2.7V to 5.5V<br>$I_{OH}$ = -10 $\mu$ A                                                                                                      |

Maximum total  $I_{OL}$  for all output pins: 71 mA If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

7. The maximum dV/dt value specifies the maximum Vcc drop to issure no internal POR/PFD reset.

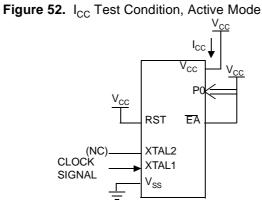

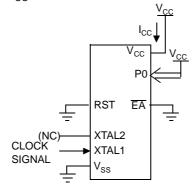

All other pins are disconnected.

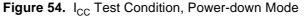

All other pins are disconnected.

All other pins are disconnected.

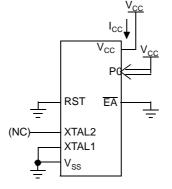

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A = 25^{\circ}C$  fully loaded)  $\overline{RD}$  and  $\overline{WR}$  propagation delays are approximately 50 ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

VQFP44