Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-LCC (J-Lead)                                                            |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ed2-smrim |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2. C51 Core SFRs

| Mnemonic | Add | Name                   | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator            |    |    |    |     |     |    |    |   |

| В        | F0h | B Register             |    |    |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word    | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer          |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low Byte  |    |    |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High Byte |    |    |    |     |     |    |    |   |

### Table 3. System Management SFRs

| Mnemonic | Add | Name                     | 7     | 6     | 5      | 4    | 3    | 2    | 1      | 0     |

|----------|-----|--------------------------|-------|-------|--------|------|------|------|--------|-------|

| PCON     | 87h | Power Control            | SMOD1 | SMOD0 | -      | POF  | GF1  | GF0  | PD     | IDL   |

| AUXR     | 8Eh | Auxiliary Register 0     | DPU   | -     | MO     | XRS2 | XRS1 | XRS0 | EXTRAM | AO    |

| AUXR1    | A2h | Auxiliary Register 1     | -     | -     | ENBOOT | -    | GF3  | 0    | -      | DPS   |

| CKRL     | 97h | Clock Reload Register    | -     | -     | -      | -    | -    | -    | -      | -     |

| CKCKON0  | 8Fh | Clock Control Register 0 | -     | WDTX2 | PCAX2  | SIX2 | T2X2 | T1X2 | T0X2   | X2    |

| CKCKON1  | AFh | Clock Control Register 1 | -     | -     | -      | -    | -    | -    | -      | SPIX2 |

### Table 4. Interrupt SFRs

| Mnemonic | Add | Name                              | 7  | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|----------|-----|-----------------------------------|----|------|------|-----|------|------|------|------|

| IEN0     | A8h | Interrupt Enable Control 0        | EA | EC   | ET2  | ES  | ET1  | EX1  | ET0  | EX0  |

| IEN1     | B1h | Interrupt Enable Control 1        | -  | -    | -    | -   | -    | ESPI |      | KBD  |

| IPH0     | B7h | Interrupt Priority Control High 0 | -  | PPCH | PT2H | PHS | PT1H | PX1H | PT0H | PX0H |

| IPL0     | B8h | Interrupt Priority Control Low 0  | -  | PPCL | PT2L | PLS | PT1L | PX1L | PTOL | PX0L |

| IPH1     | B3h | Interrupt Priority Control High 1 | -  | -    | -    | -   | -    | SPIH |      | KBDH |

| IPL1     | B2h | Interrupt Priority Control Low 1  | -  | -    | -    | -   | -    | SPIL |      | KBDL |

### Table 5. Port SFRs

| Mnemonic | Add | Name         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|--------------|---|---|---|---|---|---|---|---|

| P0       | 80h | 8-bit Port 0 |   |   |   |   |   |   |   |   |

| P1       | 90h | 8-bit Port 1 |   |   |   |   |   |   |   |   |

| P2       | A0h | 8-bit Port 2 |   |   |   |   |   |   |   |   |

| P3       | B0h | 8-bit Port 3 |   |   |   |   |   |   |   |   |

| P4       | C0h | 8-bit Port 4 |   |   |   |   |   |   |   |   |

## **Port Types**

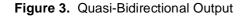

AT89C51RD2/ED2 I/O ports (P1, P2, P3, P4, P5) implement the quasi-bidirectional output that is common on the 80C51 and most of its derivatives. This output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is pulled low, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open drain output except that there are three pull-up transistors in the quasi-bidirectional output that serve different purposes. One of these pull-ups, called the "weak" pull-up, is turned on whenever the port latch for the pin contains a logic 1. The weak pull-up sources a very small current that will pull the pin high if it is left floating. A second pull-up, called the "medium" pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the medium pull-up turns off, and only the weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the medium pull-up and take the voltage on the port pin below its input threshold.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-to-high transitions on a quasi-bidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for a brief time, two CPU clocks, in order to pull the port pin high quickly. Then it turns off again.

The DPU bit (bit 7 in AUXR register) allows to disable the permanent weak pull up of all ports when latch data is logical 0.

The quasi-bidirectional port configuration is shown in Figure 3.

### **Enhanced Features**

In comparison to the original 80C52, the AT89C51RD2/ED2 implements some new features, which are:

- X2 option

- Dual Data Pointer

- Extended RAM

- Programmable Counter Array (PCA)

- Hardware Watchdog

- SPI interface

- 4-level interrupt priority system

- Power-off flag

- ONCE mode

- ALE disabling

- Some enhanced features are also located in the UART and the Timer 2

**X2 Feature** The AT89C51RD2/ED2 core needs only 6 clock periods per machine cycle. This feature called 'X2' provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

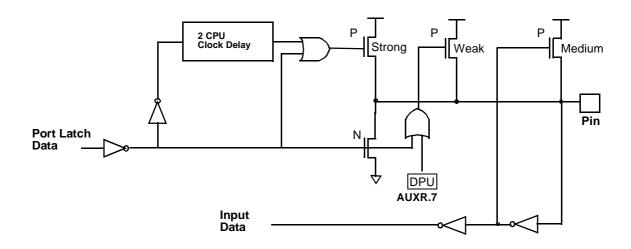

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

The clock for the whole circuit and peripherals is first divided by two before being used by the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.

Figure 5 shows the clock generation block diagram. X2 bit is validated on the rising edge of the XTAL1  $\div$  2 to avoid glitches when switching from X2 to STD mode. Figure 6 shows the switching mode waveforms.

Figure 5. Clock Generation Diagram

Description

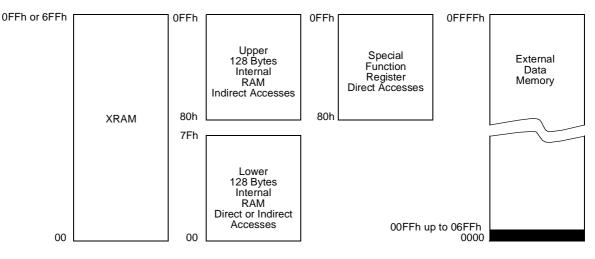

## Expanded RAM (XRAM)

The AT89C51RD2/ED2 provides additional on-chip random access memory (RAM) space for increased data parameter handling and high level language usage.

AT89C51RD2/ED2 device haS expanded RAM in external data space configurable up to 1792 bytes (see Table 19).

The AT89C51RD2/ED2 internal data memory is mapped into four separate segments.

The four segments are:

- 1. The Lower 128 bytes of RAM (addresses 00h to 7Fh) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80h to FFh) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80h to FFh) are directly addressable only.

- 4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register (see Table 19).

The lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7Fh, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction.

- Instructions that use direct addressing access SFR space. For example: MOV 0A0H, # data, accesses the SFR at location 0A0h (which is P2).

- Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0h, accesses the data byte at address 0A0h, rather than P2 (whose address is 0A0h).

- The XRAM bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory which is physically located on-chip, logically occupies the first bytes of external data memory. The bits XRS0 and XRS1 are used to hide a part of the available XRAM as explained in Table 19. This can be

## Reset

Introduction

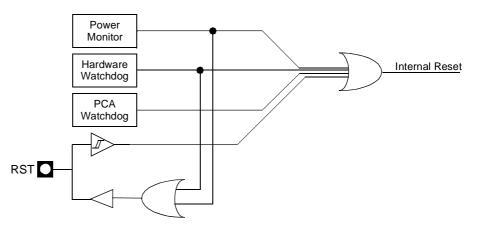

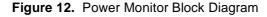

The reset sources are: Power Management, Hardware Watchdog, PCA Watchdog and Reset input.

Figure 9. Reset schematic

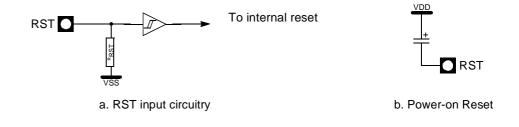

### **Reset Input**

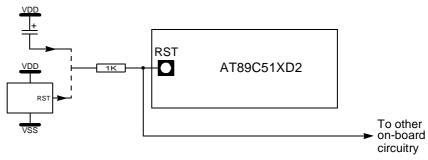

The Reset input can be used to force a reset pulse longer than the internal reset controlled by the Power Monitor. RST input has a pull-down resistor allowing power-on reset by simply connecting an external capacitor to  $V_{CC}$  as shown in Figure 10. Resistor value and input characteristics are discussed in the Section "DC Characteristics" of the AT89C51RD2/ED2 datasheet.

#### Figure 10. Reset Circuitry and Power-On Reset

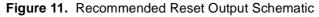

### **Reset Output**

Reset output can be generated by two sources:

- Internal POR/PFD

- Hardware watchdog timer

As detailed in Section "Hardware Watchdog Timer", page 86, the WDT generates a 96clock period pulse on the RST pin.

In order to properly propagate this pulse to the rest of the application in case of external capacitor or power-supply supervisor circuit, a 1 k $\Omega$  resistor must be added as shown Figure 11.

## **Power Monitor**

The POR/PFD function monitors the internal power-supply of the CPU core memories and the peripherals, and if needed, suspends their activity when the internal power supply falls below a safety threshold. This is achieved by applying an internal reset to them.

By generating the Reset the Power Monitor insures a correct start up when AT89C51RD2/ED2 is powered up.

**Description** In order to startup and maintain the microcontroller in correct operating mode, V<sub>CC</sub> has to be stabilized in the V<sub>CC</sub> operating range and the oscillator has to be stabilized with a nominal amplitude compatible with logic level VIH/VIL.

These parameters are controlled during the three phases: power-up, normal operation and power going down. See Figure 12.

Note: 1. Once XTAL1 High and low levels reach above and below VIH/VIL. a 1024 clock period delay will extend the reset coming from the Power Fail Detect. If the power falls below the Power Fail Detect threshold level, the Reset will be applied immediately.

The Voltage regulator generates a regulated internal supply for the CPU core the memories and the peripherals. Spikes on the external Vcc are smoothed by the voltage regulator.

| Timer 2          | The Timer 2 in the AT89C51RD2/ED2 is the standard C52 Timer 2. It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2 are cascaded. It is controlled by T2CON (Table 20) and T2MOD (Table 21) registers. Timer 2 operation is similar to Timer 0 and Timer 1. $C/T2$ selects $F_{OSC}/12$ (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to increment by the selected input. |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).                                                                                                                                                                                                                                                                                                                            |

|                  | Refer to the Atmel 8-bit Microcontroller Hardware Manual for the description of Capture and Baud Rate Generator Modes.                                                                                                                                                                                                                                                                                                                                                               |

|                  | Timer 2 includes the following enhancements:                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  | Auto-reload mode with up or down counter                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                  | Programmable clock-output                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Auto-reload Mode | The auto-reload mode configures Timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. If DCEN bit in T2MOD is cleared, Timer 2 behaves as in 80C52 (refer to<br>the Atmel C51 Microcontroller Hardware Manual). If DCEN bit is set, Timer 2 acts as an<br>Up/down timer/counter as shown in Figure 14. In this mode the T2EX pin controls the<br>direction of count.                                                                                                |

|                  | When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                                                                                         |

|                  | When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                                                                                      |

|                  | The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.                                                                                                                                                                                                                                                                                          |

**Table 27.** CCAPnL Registers (n = 0 - 4)

CCAP0L - PCA Module 0 Compare/Capture Control Register Low (0EAh)

CCAP1L - PCA Module 1 Compare/Capture Control Register Low (0EBh)

CCAP2L - PCA Module 2 Compare/Capture Control Register Low (0ECh)

CCAP3L - PCA Module 3 Compare/Capture Control Register Low (0EDh)

CCAP4L - PCA Module 4 Compare/Capture Control Register Low (0EEh)

| 7             | 6               | 5                        | 4 | 3            | 2    | 1 | 0 |

|---------------|-----------------|--------------------------|---|--------------|------|---|---|

| -             | -               | -                        | - | -            | -    | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description              |   |              |      |   |   |

| 7 - 0         | -               | PCA Module<br>CCAPnL Val |   | /Capture Con | trol |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 28. CH Register

CH - PCA Counter Register High (0F9h)

| 7             | 6               | 5                      | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|------------------------|---|---|---|---|---|

| -             | -               | -                      | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description            |   |   |   |   |   |

| 7 - 0         | -               | PCA counte<br>CH Value | r |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 29. CL Register

CL - PCA Counter Register Low (0E9h)

| 7             | 6               | 5                      | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|------------------------|---|---|---|---|---|

| -             | -               | -                      | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description            |   |   |   |   |   |

| 7 - 0         | -               | PCA Counte<br>CL Value | r |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

| TCLK<br>(T2CON) | RCLK<br>(T2CON) | TBCK<br>(BDRCON) | RBCK<br>(BDRCON) | Clock Source<br>UART Tx | Clock Source<br>UART Rx |

|-----------------|-----------------|------------------|------------------|-------------------------|-------------------------|

| 0               | 0               | 0                | 0                | Timer 1                 | Timer 1                 |

| 1               | 0               | 0                | 0                | Timer 2                 | Timer 1                 |

| 0               | 1               | 0                | 0                | Timer 1                 | Timer 2                 |

| 1               | 1               | 0                | 0                | Timer 2                 | Timer 2                 |

| Х               | 0               | 1                | 0                | INT_BRG                 | Timer 1                 |

| Х               | 1               | 1                | 0                | INT_BRG                 | Timer 2                 |

| 0               | Х               | 0                | 1                | Timer 1                 | INT_BRG                 |

| 1               | х               | 0                | 1                | Timer 2                 | INT_BRG                 |

| Х               | Х               | 1                | 1                | INT_BRG                 | INT_BRG                 |

Table 32. Baud Rate Selection Table UART

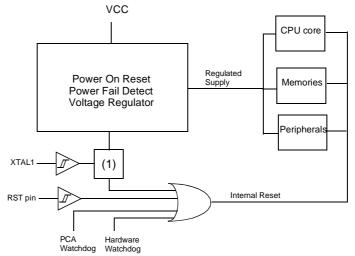

# Internal Baud Rate Generator (BRG)

When the internal Baud Rate Generator is used, the Baud Rates are determined by the BRG overflow depending on the BRL reload value, the value of SPD bit (Speed Mode) in BDRCON register and the value of the SMOD1 bit in PCON register.

Figure 26. Internal Baud Rate

• The baud rate for UART is token by formula:

$$Baud_Rate = \frac{2^{SMOD1} \cdot F_{PER}}{6^{(1-SPD)} \cdot 32 \cdot (256 \cdot BRL)}$$

$$BRL = 256 - \frac{2^{SMOD1} \cdot F_{PER}}{6^{(1-SPD)} \cdot 32 \cdot Baud_Rate}$$

### Table 40. T2CON Register

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                                       | 4                                                                                                                                                                                                                                                                                                                                | 3                                                                 | 2               | 1              | 0        |  |  |  |  |

|---------------|-----------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|----------------|----------|--|--|--|--|

| TF2           | EXF2            | RCLK                                                                    | RCLK TCLK EXEN2 TR2 C/T2# CP/RL2#                                                                                                                                                                                                                                                                                                |                                                                   |                 |                |          |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                         | Description                                                                                                                                                                                                                                                                                                                      |                                                                   |                 |                |          |  |  |  |  |

| 7             | TF2             |                                                                         | ared by softwa                                                                                                                                                                                                                                                                                                                   | are.<br>2 overflow, if                                            | RCLK = 0 and    | d TCLK = 0.    |          |  |  |  |  |

| 6             | EXF2            | Set when a<br>EXEN2=1.<br>When set, c<br>interrupt is e<br>Must be clea | imer 2 External Flag<br>et when a capture or a reload is caused by a negative transition on T2EX pin if<br>XEN2=1.<br>/hen set, causes the CPU to vector to timer 2 interrupt routine when timer 2<br>iterrupt is enabled.<br>/lust be cleared by software. EXF2 doesn't cause an interrupt in Up/down<br>ounter mode (DCEN = 1) |                                                                   |                 |                |          |  |  |  |  |

| 5             | RCLK            | Cleared to u                                                            |                                                                                                                                                                                                                                                                                                                                  | ART<br>erflow as rece<br>w as receive o                           |                 |                |          |  |  |  |  |

| 4             | TCLK            | Cleared to u                                                            |                                                                                                                                                                                                                                                                                                                                  | IART<br>erflow as trans<br>w as transmit                          |                 | •              |          |  |  |  |  |

| 3             | EXEN2           | Cleared to ig<br>Set to cause                                           | e a capture or                                                                                                                                                                                                                                                                                                                   | e <b>bit</b><br>on T2EX pin fo<br>reload when a<br>used to clock  | a negative trar | nsition on T2E | X pin is |  |  |  |  |

| 2             | TR2             |                                                                         | n control bit<br>urn off timer 2<br>on timer 2.                                                                                                                                                                                                                                                                                  | 2.                                                                |                 |                |          |  |  |  |  |

| 1             | C/T2#           | Cleared for Set for count                                               | <b>Timer/Counter 2 select bit</b><br>Cleared for timer operation (input from internal clock system: F <sub>CLK PERIPH</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be<br>0 for clock out mode.                                                                                    |                                                                   |                 |                |          |  |  |  |  |

| 0             | CP/RL2#         | If RCLK=1 of<br>timer 2 over<br>Cleared to a<br>if EXEN2=1              | flow.<br>auto-reload on                                                                                                                                                                                                                                                                                                          | <b>bit</b><br>P/RL2# is igno<br>timer 2 overfl<br>e transitions o | ows or negativ  | ve transitions |          |  |  |  |  |

Reset Value = 0000 0000b Bit addressable

### Table 57. IPL1 Register

IPL1 - Interrupt Priority Register (B2h)

| 7             | 6               | 5                               | 4                                       | 3                | 2              | 1            | 0    |

|---------------|-----------------|---------------------------------|-----------------------------------------|------------------|----------------|--------------|------|

| -             | -               | -                               | -                                       | -                | SPIL           | TWIL         | KBDL |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                         |                  |                |              |      |

| 7             | -               | Reserved<br>The value re        | ad from this b                          | oit is indetermi | nate. Do not s | et this bit. |      |

| 6             | -               | <b>Reserved</b><br>The value re | ad from this b                          | oit is indetermi | nate. Do not s | et this bit. |      |

| 5             | -               | <b>Reserved</b><br>The value re | ad from this b                          | oit is indetermi | nate. Do not s | et this bit. |      |

| 4             | -               | <b>Reserved</b><br>The value re | ad from this b                          | oit is indetermi | nate. Do not s | et this bit. |      |

| 3             | -               | <b>Reserved</b><br>The value re | ad from this b                          | it is indetermi  | nate. Do not s | et this bit. |      |

| 2             | SPIL            |                                 | t Priority bit<br>H for priority I      |                  |                |              |      |

| 1             | -               | <b>Reserved</b><br>The value re | ad from this b                          | oit is indetermi | nate. Do not s | et this bit. |      |

| 0             | KBDL            | -                               | <b>iterrupt Prio</b><br>DH for priority | -                |                |              |      |

Reset Value = XXXX X000b Bit addressable

### Table 58. IPH1 Register

IPH1 - Interrupt Priority High Register (B3h)

| 7             | 6               | 5                                                                                      | 4              | 3                       | 2              | 1            | 0    |

|---------------|-----------------|----------------------------------------------------------------------------------------|----------------|-------------------------|----------------|--------------|------|

| -             | -               | -                                                                                      | -              | -                       | SPIH           | -            | KBDH |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                            |                |                         |                |              |      |

| 7             | -               | <b>Reserved</b><br>The value re                                                        | ad from this b | oit is indetermi        | nate. Do not s | et this bit. |      |

| 6             | -               | Reserved<br>The value re                                                               | ad from this b | it is indetermi         | nate. Do not s | et this bit. |      |

| 5             | -               | Reserved<br>The value re                                                               | ad from this b | it is indetermi         | nate. Do not s | et this bit. |      |

| 4             | -               | Reserved<br>The value re                                                               | ad from this b | it is indetermi         | nate. Do not s | et this bit. |      |

| 3             | -               | Reserved<br>The value re                                                               | ad from this b | it is indetermi         | nate. Do not s | et this bit. |      |

| 2             | SPIH            |                                                                                        | Lowe           | t <u>y Level</u><br>st  |                |              |      |

| 1             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |                |                         |                |              |      |

| 0             | KBDH            |                                                                                        |                | t <u>y Level</u><br>est |                |              |      |

Reset Value = XXXX X000b Not bit addressable

## **Power-off Flag**

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (Table 64). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

#### Table 64. PCON Register

| 7             | 6               | 5                                                                                                               | 4                                                                               | 3                                | 2            | 1             | 0             |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------|--------------|---------------|---------------|

| SMOD1         | SMOD0           | -                                                                                                               | POF                                                                             | GF1                              | GF0          | PD            | IDL           |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                     |                                                                                 |                                  |              |               |               |

| 7             | SMOD1           | Serial port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                                     |                                                                                 |                                  |              |               |               |

| 6             | SMOD0           | Serial port Mode bit 0<br>Cleared to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register. |                                                                                 |                                  |              |               |               |

| 5             | -               | Reserved<br>The value rea                                                                                       | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                  |              |               |               |

| 4             | POF             |                                                                                                                 | oftware to rec                                                                  | ognize the nex<br>rises from 0 t |              | oltage. Can a | lso be set by |

| 3             | GF1             |                                                                                                                 |                                                                                 | I-purpose usa<br>pose usage.     | ge.          |               |               |

| 2             | GF0             |                                                                                                                 |                                                                                 | I-purpose usa<br>pose usage.     | ge.          |               |               |

| 1             | PD              |                                                                                                                 |                                                                                 | n reset occurs.<br>node.         |              |               |               |

| 0             | IDL             | Idle mode b<br>Cleared by h<br>Set to enter i                                                                   | ardware wher                                                                    | n interrupt or re                | eset occurs. |               |               |

PCON - Power Control Register (87h)

Reset Value = 00X1 0000b Not bit addressable

| EEPROM Data | This feature is available only for the AT89C51ED2 device.                                                                                                               |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Memory      | the 2K bytes on-chip EEPROM memory block is located at addresses 0000h to 07FFh the XRAM/ERAM memory space and is selected by setting control bits in the EECON gister. |  |  |  |  |

|             | A read or write access to the EEPROM memory is done with a MOVX instruction.                                                                                            |  |  |  |  |

| Write Data  | Data is written by byte to the EEPROM memory block as for an external RAM memory.                                                                                       |  |  |  |  |

|             | The following procedure is used to write to the EEPROM memory:                                                                                                          |  |  |  |  |

|             | Check EEBUSY flag                                                                                                                                                       |  |  |  |  |

|             | <ul> <li>If the user application interrupts routines use XRAM memory space: Save and<br/>disable interrupts.</li> </ul>                                                 |  |  |  |  |

|             | Load DPTR with the address to write                                                                                                                                     |  |  |  |  |

|             | Store A register with the data to be written                                                                                                                            |  |  |  |  |

|             | Set bit EEE of EECON register                                                                                                                                           |  |  |  |  |

- Execute a MOVX @DPTR, A

- Clear bit EEE of EECON register

- Restore interrupts.

- EEBUSY flag in EECON is then set by hardware to indicate that programming is in progress and that the EEPROM segment is not available for reading or writing.

- The end of programming is indicated by a hardware clear of the EEBUSY flag.

Figure 38 represents the optimal write sequence to the on-chip EEPROM data memory.

| Program Lock Bits |     | Bits |                                                                       |

|-------------------|-----|------|-----------------------------------------------------------------------|

| Security<br>Level | LB0 | LB1  | Protection Description                                                |

| 1                 | 1   | 1    | No program lock features enabled.                                     |

| 2                 | 0   | 1    | ISP programming of the Flash is disabled.                             |

| 3                 | Х   | 0    | Same as 2, also verify through ISP programming interface is disabled. |

Table 71.

User Memory Lock Bits of the SSB

Note: X: Do not care

WARNING: Security level 2 and 3 should only be programmed after Flash verification.

Flash Memory Status AT89C51RD2/ED2 parts are delivered in standard with the ISP ROM bootloader.

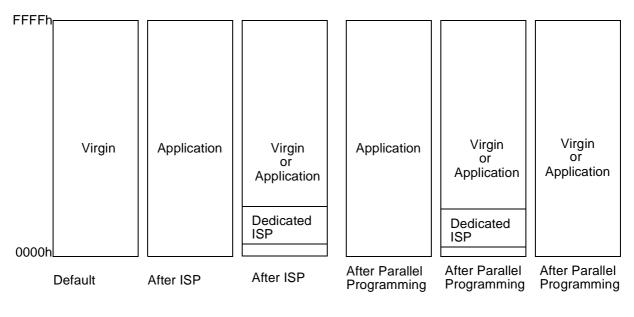

After ISP or parallel programming, the possible contents of the Flash memory are summarized in Figure 40:

#### Figure 40. Flash Memory Possible Contents

**Memory Organization** When the EA pin is high, the processor fetches instructions from internal program Flash. If the EA pin is tied low, all program memory fetches are from external memory.

### **Bootloader Architecture**

Introduction

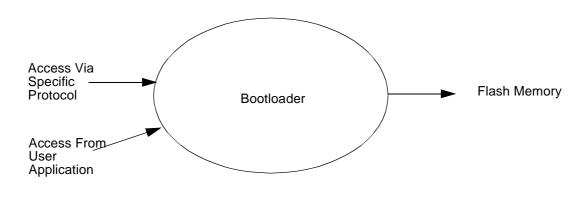

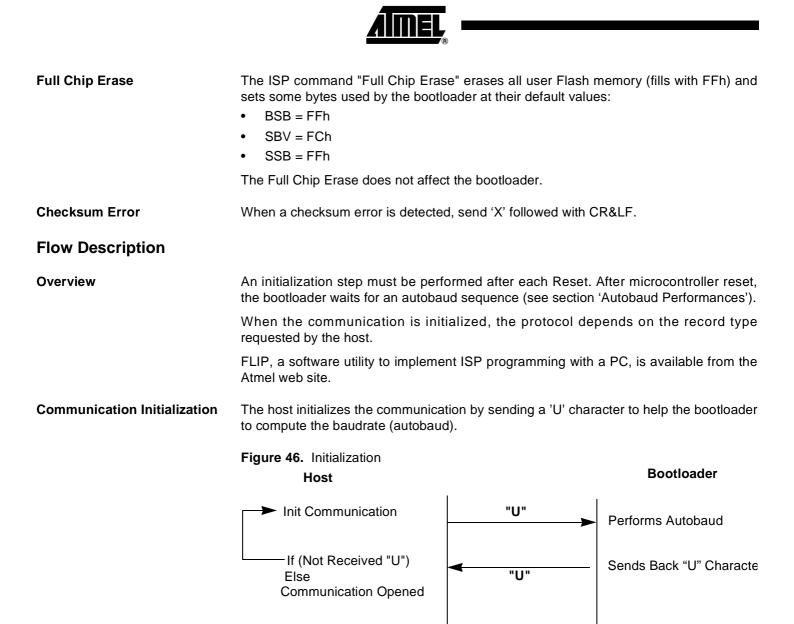

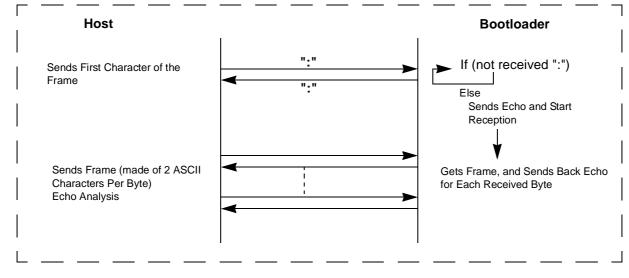

The bootloader manages communication according to a specifically defined protocol to provide the whole access and service on Flash memory. Furthermore, all accesses and routines can be called from the user application.

### Figure 41. Diagram Context Description

Acronyms

ISP: In-System Programming SBV: Software Boot Vector BSB: Boot Status Byte SSB: Software Security Byte HW: Hardware Byte

#### Figure 47. Command Flow

| Serial I/O Port                               | 49  |

|-----------------------------------------------|-----|

| Framing Error Detection                       | 49  |

| Automatic Address Recognition                 | 50  |

| Registers                                     |     |

| Baud Rate Selection for UART for Mode 1 and 3 | 52  |

| UART Registers                                | 55  |

| Keyboard Interface                            | 60  |

| Registers                                     |     |

| Serial Port Interface (SPI)                   | 64  |

| Features                                      |     |

| Signal Description                            |     |

| Functional Description                        |     |

| Interrupt System                              | 73  |

| Registers                                     |     |

| Interrupt Sources and Vector Addresses        |     |

|                                               | 75  |

| Power Management                              | 82  |

| Introduction                                  | 82  |

| Idle Mode                                     | 82  |

| Power-Down Mode                               | 82  |

| Registers                                     | 85  |

| Hardware Watchdog Timer                       | 86  |

| Using the WDT                                 | 86  |

| WDT during Power-down and Idle                | 87  |

| ONCE <sup>®</sup> Mode (ON- Chip Emulation)   | 88  |

| Power-off Flag                                | 89  |

|                                               | ••• |

| Reduced EMI Mode                              | 90  |

| EEPROM Data Memory                            | 91  |

| Write Data                                    | 91  |

| Read Data                                     | 93  |

| Registers                                     | 94  |

| Flash/EEPROM Memory                           | 95  |

| Features                                      | 95  |

| Flash Programming and Erasure                 | 95  |

| Flash Registers and Memory Map                | 96  |

| Flash Memory Status                           |     |

| Memory Organization                           | 99  |