#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LQFP                                                                    |

| Supplier Device Package    | 44-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51rd2-rltim |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 2. C51 Core SFRs

| Mnemonic | Add | Name                   | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator            |    |    |    |     |     |    |    |   |

| В        | F0h | B Register             |    |    |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word    | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer          |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low Byte  |    |    |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High Byte |    |    |    |     |     |    |    |   |

### Table 3. System Management SFRs

| Mnemonic | Add | Name                     | 7     | 6     | 5      | 4    | 3    | 2    | 1      | 0     |

|----------|-----|--------------------------|-------|-------|--------|------|------|------|--------|-------|

| PCON     | 87h | Power Control            | SMOD1 | SMOD0 | -      | POF  | GF1  | GF0  | PD     | IDL   |

| AUXR     | 8Eh | Auxiliary Register 0     | DPU   | -     | MO     | XRS2 | XRS1 | XRS0 | EXTRAM | AO    |

| AUXR1    | A2h | Auxiliary Register 1     | -     | -     | ENBOOT | -    | GF3  | 0    | -      | DPS   |

| CKRL     | 97h | Clock Reload Register    | -     | -     | -      | -    | -    | -    | -      | -     |

| CKCKON0  | 8Fh | Clock Control Register 0 | -     | WDTX2 | PCAX2  | SIX2 | T2X2 | T1X2 | T0X2   | X2    |

| CKCKON1  | AFh | Clock Control Register 1 | -     | -     | -      | -    | -    | -    | -      | SPIX2 |

### Table 4. Interrupt SFRs

| Mnemonic | Add | Name                              | 7  | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|----------|-----|-----------------------------------|----|------|------|-----|------|------|------|------|

| IEN0     | A8h | Interrupt Enable Control 0        | EA | EC   | ET2  | ES  | ET1  | EX1  | ET0  | EX0  |

| IEN1     | B1h | Interrupt Enable Control 1        | -  | -    | -    | -   | -    | ESPI |      | KBD  |

| IPH0     | B7h | Interrupt Priority Control High 0 | -  | PPCH | PT2H | PHS | PT1H | PX1H | PT0H | PX0H |

| IPL0     | B8h | Interrupt Priority Control Low 0  | -  | PPCL | PT2L | PLS | PT1L | PX1L | PTOL | PX0L |

| IPH1     | B3h | Interrupt Priority Control High 1 | -  | -    | -    | -   | -    | SPIH |      | KBDH |

| IPL1     | B2h | Interrupt Priority Control Low 1  | -  | -    | -    | -   | -    | SPIL |      | KBDL |

## Table 5. Port SFRs

| Mnemonic | Add | Name         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|--------------|---|---|---|---|---|---|---|---|

| P0       | 80h | 8-bit Port 0 |   |   |   |   |   |   |   |   |

| P1       | 90h | 8-bit Port 1 |   |   |   |   |   |   |   |   |

| P2       | A0h | 8-bit Port 2 |   |   |   |   |   |   |   |   |

| P3       | B0h | 8-bit Port 3 |   |   |   |   |   |   |   |   |

| P4       | C0h | 8-bit Port 4 |   |   |   |   |   |   |   |   |

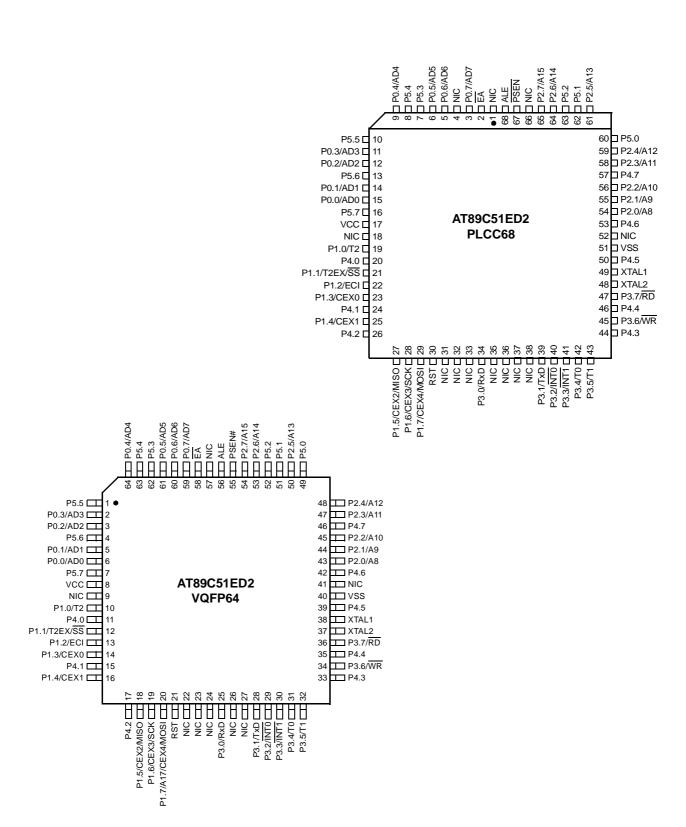

NIC: Not Internaly Connected

## Oscillator

To optimize the power consumption and execution time needed for a specific task, an internal prescaler feature has been implemented between the oscillator and the CPU and peripherals.

### Registers

#### Table 14. CKRL Register

CKRL - Clock Reload Register (97h)

| 7        |    | 6    | 5      | 4                                        | 3     | 2     | 1     | 0     |

|----------|----|------|--------|------------------------------------------|-------|-------|-------|-------|

| CKRL7    | C  | KRL6 | CKRL5  | CKRL4                                    | CKRL3 | CKRL2 | CKRL1 | CKRL0 |

| Bit Numb | er | Mne  | emonic | Description                              |       |       |       |       |

| 7:0      |    | (    | CKRL   | Clock Reload Register<br>Prescaler value |       |       |       |       |

Reset Value = 1111 1111b Not bit addressable

### Table 15. PCON Register

PCON - Power Control Register (87h)

| 7        | 6     |       | 5                                                                                                     | 4                                                                                                                                                                     | 3              | 2   | 1  | 0   |                                        |  |  |  |  |

|----------|-------|-------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|----|-----|----------------------------------------|--|--|--|--|

| SMOD1    | SMOE  | D0    | -                                                                                                     | POF                                                                                                                                                                   | GF1            | GF0 | PD | IDL |                                        |  |  |  |  |

| Bit Numb | er l  | Bit M | nemonic                                                                                               | Description                                                                                                                                                           |                |     |    |     |                                        |  |  |  |  |

| 7        |       | S     | MOD1                                                                                                  | Serial Port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                                                                                           |                |     |    |     |                                        |  |  |  |  |

| 6        |       | SMOD0 |                                                                                                       | Serial Port Mode bit 0<br>Cleared to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register.                                                       |                |     |    |     |                                        |  |  |  |  |

| 5        | -     |       | -                                                                                                     | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                |                |     |    |     |                                        |  |  |  |  |

| 4        |       |       | POF                                                                                                   | Power-off FlagCleared by software to recognize the next reset type.Set by hardware when $V_{CC}$ rises from 0 to its nominal voltage. Can<br>also be set by software. |                |     |    |     |                                        |  |  |  |  |

| 3        | 3 GF1 |       | GF1                                                                                                   | General-purp<br>Cleared by sof<br>Set by software                                                                                                                     | tware for gene |     | 0  |     |                                        |  |  |  |  |

| 2        | 2 GF0 |       |                                                                                                       | General-purp<br>Cleared by sof<br>Set by software                                                                                                                     | tware for gene |     | -  |     |                                        |  |  |  |  |

| 1 PD     |       | PD    | <b>Power-down Mode bit</b><br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode. |                                                                                                                                                                       |                |     |    |     | Cleared by hardware when reset occurs. |  |  |  |  |

| 0        |       |       | IDL                                                                                                   | Idle Mode bit<br>Cleared by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                                                                       |                |     |    |     |                                        |  |  |  |  |

Reset Value = 00X1 0000b Not bit addressable

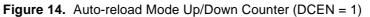

(UP COUNTING RELOAD VALUE)

## Programmable Clock-output

In the clock-out mode, Timer 2 operates as a 50% duty-cycle, programmable clock generator (See Figure 15). The input clock increments TL2 at frequency  $F_{CLK PERIPH}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, Timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers:

$Clock-OutFrequency = \frac{F_{CLKPERIPH}}{4 \times (65536 - RCAP2H/RCAP2L)}$

For a 16 MHz system clock, Timer 2 has a programmable frequency range of 61 Hz  $(F_{CLK PERIPH}/2^{16})$  to 4 MHz  $(F_{CLK PERIPH}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use Timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

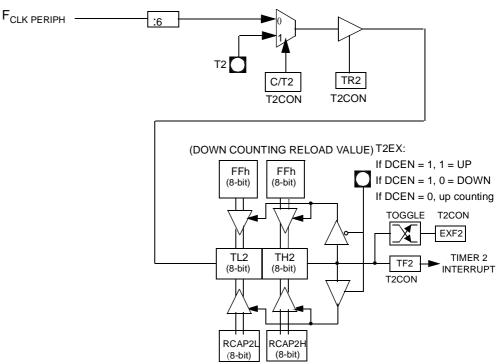

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn | Module Function                                   |

|-------|-------|-------|------|------|------|-------|---------------------------------------------------|

| 0     | 0     | 0     | 0    | 0    | 0    | 0     | No Operation                                      |

| х     | 1     | 0     | 0    | 0    | 0    | х     | 16-bit capture by a positive-edge trigger on CEXn |

| х     | 0     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a negative trigger on CEXn      |

| х     | 1     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a transition on CEXn            |

| 1     | 0     | 0     | 1    | 0    | 0    | х     | 16-bit Software Timer/Compare mode.               |

| 1     | 0     | 0     | 1    | 1    | 0    | Х     | 16-bit High Speed Output                          |

| 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                         |

| 1     | 0     | 0     | 1    | Х    | 0    | Х     | Watchdog Timer (module 4 only)                    |

Table 25. PCA Module Modes (CCAPMn Registers)

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output (See Table 26 & Table 27).

Table 26. CCAPnH Registers (n = 0 - 4)

6

CCAP0H - PCA Module 0 Compare/Capture Control Register High (0FAh)

CCAP1H - PCA Module 1 Compare/Capture Control Register High (0FBh)

CCAP2H - PCA Module 2 Compare/Capture Control Register High (0FCh)

CCAP3H - PCA Module 3 Compare/Capture Control Register High (0FDh)

CCAP4H - PCA Module 4 Compare/Capture Control Register High (0FEh)

٨

5

| 1             | 0               | 5                        | - | 5           | 2    | • | U |

|---------------|-----------------|--------------------------|---|-------------|------|---|---|

| -             | -               | -                        | - | -           | -    | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description              |   |             |      |   |   |

| 7 - 0         | -               | PCA Module<br>CCAPnH Val |   | Capture Con | trol |   |   |

2

2

1

Λ

Reset Value = 0000 0000b Not bit addressable

7

Figure 20. PCA High Speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen.

Once ECOM is set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

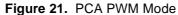

Pulse Width ModulatorModeAll of the PCA modules can be used as PWM outputs. Figure 21 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the<br/>modules will have the same frequency of output because they all share the PCA timer.<br/>The duty cycle of each module is independently variable using the modules capture reg-<br/>ister CCAPLn. When the value of the PCA CL SFR is less than the value in the modules<br/>CCAPLn SFR the output will be low, when it is equal to or greater than the output will be<br/>high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn.<br/>This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

**PCA Watchdog Timer** An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 19 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. Periodically change the compare value so it will never match the PCA timer.

- 2. Periodically change the PCA timer value so it will never match the compare values.

- 3. Disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

### Table 33. SCON Register

SCON - Serial Control Register (98h)

| 7             | 6            | 5                 | 4                                                                                                                                                                                        | 3                                                                            | 2                                                                   | 1                         | 0            |  |  |

|---------------|--------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------|--------------|--|--|

| FE/SM0        | SM1          | SM2               | REN                                                                                                                                                                                      | TB8                                                                          | RB8                                                                 | ТІ                        | RI           |  |  |

| Bit<br>Number | Bit<br>Mnemo | onic Descr        | Description                                                                                                                                                                              |                                                                              |                                                                     |                           |              |  |  |

| 7             | FE           | Clear<br>Set by   | hardware wh                                                                                                                                                                              | SMOD0=1)<br>fror state, not o<br>ten an invalid<br>t to enable acc           | stop bit is dete                                                    | ected.                    |              |  |  |

|               | SM           | ) Refer           | Serial port Mode bit 0<br>Refer to SM1 for serial port mode selection.<br>SMOD0 must be cleared to enable access to the SM0 bit.                                                         |                                                                              |                                                                     |                           |              |  |  |

| 6             | SM           | <u>SM0</u>        | 0 Sł<br>1 8-<br>0 9-                                                                                                                                                                     | ode <u>E</u><br>hift Register F<br>bit UART \<br>bit UART F                  | Baud Rate<br><sub>XTAL</sub> /12 (or F <sub>x</sub><br>/ariable<br> |                           | • X2)        |  |  |

| 5             | SM:          | 2 Clear<br>Set to | to disable mul<br>enable multip                                                                                                                                                          | bit / Multipro<br>ltiprocessor co<br>rocessor com<br>This bit should         | mmunication                                                         | feature.<br>ature in mode |              |  |  |

| 4             | REI          | l Clear           | otion Enable<br>to disable seri<br>enable serial                                                                                                                                         | ial reception.                                                               |                                                                     |                           |              |  |  |

| 3             | ТВ8          | 3 Clear           | to transmit a l                                                                                                                                                                          | <b>Ninth bit to tr</b><br>ogic 0 in the 9<br>jic 1 in the 9th                | th bit.                                                             | odes 2 and 3              |              |  |  |

| 2             | RB           | Cleare<br>Set by  | ed by hardwar<br>hardware if 9                                                                                                                                                           | nth bit receive<br>e if 9th bit receive<br>0th bit received<br>0, RB8 is the | eived is a logic<br>l is a logic 1.                                 | c 0.                      | ) RB8 is not |  |  |

| 1             | ті           | Clear<br>Set by   | <b>Transmit Interrupt flag</b><br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning<br>of the stop bit in the other modes. |                                                                              |                                                                     |                           |              |  |  |

| 0             | RI           | Clear<br>Set by   | <b>Receive Interrupt flag</b><br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0, see Figure 23.<br>and Figure 24. in the other modes.       |                                                                              |                                                                     |                           |              |  |  |

Reset Value = 0000 0000b Bit addressable

### Table 42. BDRCON Register

BDRCON - Baud Rate Control Register (9Bh)

| 7             | 6               | 5                        | 4                                                                                                                                                                                                                                      | 3                                                | 2               | 1            | 0   |  |  |  |  |

|---------------|-----------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|--------------|-----|--|--|--|--|

| -             | -               | -                        | BRR                                                                                                                                                                                                                                    | ТВСК                                             | RBCK            | SPD          | SRC |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptior              | Description                                                                                                                                                                                                                            |                                                  |                 |              |     |  |  |  |  |

| 7             | -               | Reserved<br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                         |                                                  |                 |              |     |  |  |  |  |

| 6             | -               | Reserved<br>The value re | ead from this                                                                                                                                                                                                                          | bit is indeterm                                  | inate. Do not s | set this bit |     |  |  |  |  |

| 5             | -               | Reserved<br>The value re | ead from this I                                                                                                                                                                                                                        | oit is indetermi                                 | nate. Do not s  | et this bit. |     |  |  |  |  |

| 4             | BRR             | Cleared to s             | Baud Rate Run Control bit<br>Cleared to stop the internal Baud Rate Generator.<br>Set to start the internal Baud Rate Generator.                                                                                                       |                                                  |                 |              |     |  |  |  |  |

| 3             | ТВСК            | Cleared to s             | elect Timer 1                                                                                                                                                                                                                          | e Generator S<br>or Timer 2 for<br>d Rate Genera | the Baud Rate   |              |     |  |  |  |  |

| 2             | RBCK            | Cleared to s             | elect Timer 1                                                                                                                                                                                                                          | enerator Sele<br>or Timer 2 for<br>d Rate Genera | the Baud Rate   |              |     |  |  |  |  |

| 1             | SPD             | Cleared to s             | Baud Rate Speed Control bit for UART<br>Cleared to select the SLOW Baud Rate Generator.<br>Set to select the FAST Baud Rate Generator.                                                                                                 |                                                  |                 |              |     |  |  |  |  |

| 0             | SRC             | Cleared to s<br>mode).   | Baud Rate Source select bit in Mode 0 for UART<br>Cleared to select F <sub>OSC</sub> /12 as the Baud Rate Generator (F <sub>CLK PERIPH</sub> /6 in X2<br>mode).<br>Set to select the internal Baud Rate Generator for UARTs in mode 0. |                                                  |                 |              |     |  |  |  |  |

Reset Value = XXX0 0000b Not bit addressable

## **Keyboard Interface**

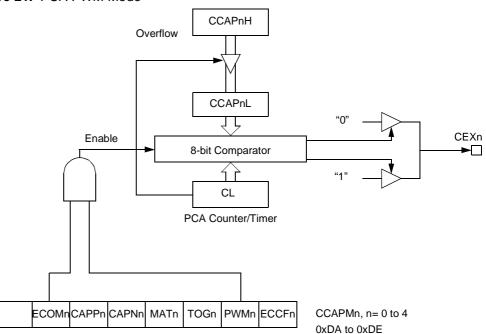

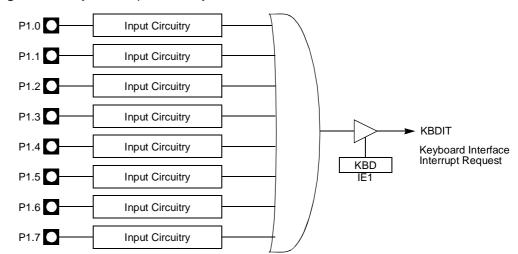

The AT89C51RD2/ED2 implements a keyboard interface allowing the connection of a 8 x n matrix keyboard. It is based on 8 inputs with programmable interrupt capability on both high or low level. These inputs are available as alternate function of P1 and allow to exit from idle and power-down modes.

The keyboard interfaces with the C51 core through 3 special function registers: KBLS, the Keyboard Level Selection register (Table 45), KBE, the Keyboard interrupt Enable register (Table 44), and KBF, the Keyboard Flag register (Table 43).

Interrupt The keyboard inputs are considered as 8 independent interrupt sources sharing the same interrupt vector. An interrupt enable bit (KBD in IE1) allows global enable or disable of the keyboard interrupt (see Figure 27). As detailed in Figure 28 each keyboard input has the capability to detect a programmable level according to KBLS. x bit value. Level detection is then reported in interrupt flags KBF.x that can be masked by software using KBE. x bits.

This structure allow keyboard arrangement from 1 by n to 8 by n matrix and allows usage of P1 inputs for other purpose.

Figure 28. Keyboard Input Circuitry

### **Power Reduction Mode**

P1 inputs allow exit from idle and power-down modes as detailed in Section "Power Management", page 82.

### Table 44. KBE Register

KBE-Keyboard Input Enable Register (9Dh)

| 7             | 6               | 5                                                                                                                                                     | 4                                                                                                                                                     | 3    | 2             | 1              | 0     |  |  |  |  |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|----------------|-------|--|--|--|--|

| KBE7          | KBE6            | KBE5                                                                                                                                                  | KBE4                                                                                                                                                  | KBE3 | KBE2          | KBE1           | KBE0  |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                           | Description                                                                                                                                           |      |               |                |       |  |  |  |  |

| 7             | KBE7            | Cleared to en                                                                                                                                         | <b>Keyboard line 7 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.7 bit in KBF register to generate an interrupt request. |      |               |                |       |  |  |  |  |

| 6             | KBE6            | Cleared to en                                                                                                                                         | <b>ne 6 Enable I</b><br>nable standar<br>e KBF.6 bit in                                                                                               |      | o generate an | interrupt requ | iest. |  |  |  |  |

| 5             | KBE5            | Cleared to en                                                                                                                                         | ne 5 Enable I<br>nable standar<br>e KBF.5 bit in                                                                                                      |      | o generate an | interrupt requ | iest. |  |  |  |  |

| 4             | KBE4            | Cleared to en                                                                                                                                         | <b>ne 4 Enable I</b><br>nable standar<br>e KBF.4 bit in                                                                                               |      | o generate an | interrupt requ | iest. |  |  |  |  |

| 3             | KBE3            | Cleared to en                                                                                                                                         | ne 3 Enable I<br>nable standar<br>e KBF.3 bit in                                                                                                      |      | o generate an | interrupt requ | iest. |  |  |  |  |

| 2             | KBE2            | Cleared to en                                                                                                                                         | ne 2 Enable I<br>nable standar<br>e KBF.2 bit in                                                                                                      |      | o generate an | interrupt requ | iest. |  |  |  |  |

| 1             | KBE1            | Cleared to en                                                                                                                                         | ne 1 Enable I<br>nable standar<br>e KBF.1 bit in                                                                                                      |      | o generate an | interrupt requ | iest. |  |  |  |  |

| 0             | KBE0            | <b>Keyboard line 0 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.0 bit in KBF register to generate an interrupt request. |                                                                                                                                                       |      |               |                |       |  |  |  |  |

Reset Value = 0000 0000b

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                            |

|---------------|-----------------|----------------------------------------------------------------------------------------|

| 1             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |

| 0             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.        |

Reset Value = 00X0 XXXXb

Not Bit addressable

Serial Peripheral DATa Register (SPDAT) The Serial Peripheral Data Register (Table 50) is a read/write buffer for the receive data register. A write to SPDAT places data directly into the shift register. No transmit buffer is available in this model.

A Read of the SPDAT returns the value located in the receive buffer and not the content of the shift register.

#### Table 50. SPDAT Register

SPDAT - Serial Peripheral Data Register (0C5H)

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

Reset Value = Indeterminate

R7:R0: Receive data bits

SPCON, SPSTA and SPDAT registers may be read and written at any time while there is no on-going exchange. However, special care should be taken when writing to them while a transmission is on-going:

- Do not change SPR2, SPR1 and SPR0

- Do not change CPHA and CPOL

- Do not change MSTR

- Clearing SPEN would immediately disable the peripheral

- Writing to the SPDAT will cause an overflow.

## **Interrupt System**

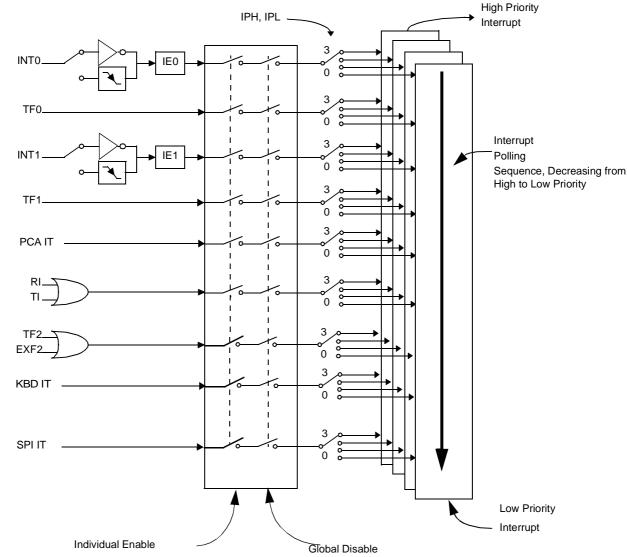

The <u>AT89C51RD2/ED2</u> has a total of 9 interrupt vectors: two external interrupts (INT0 and INT1), three timer interrupts (timers 0, 1 and 2), the serial port interrupt, SPI interrupt, Keyboard interrupt and the PCA global interrupt. These interrupts are shown in Figure 36.

Figure 36. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (Table 54 and Table 56). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (Table 57) and in the Interrupt Priority High register (Table 55 and Table 56) shows the bit values and priority levels associated with each combination.

### Table 58. IPH1 Register

IPH1 - Interrupt Priority High Register (B3h)

| 7             | 6               | 5                                                                                | 4                                                                                                                                  | 3                | 2              | 1            | 0    |  |

|---------------|-----------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|--------------|------|--|

| -             | -               | -                                                                                | -                                                                                                                                  | -                | SPIH           | -            | KBDH |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                      |                                                                                                                                    |                  |                |              |      |  |

| 7             | -               | <b>Reserved</b><br>The value re                                                  | ad from this b                                                                                                                     | oit is indetermi | nate. Do not s | et this bit. |      |  |

| 6             | -               | Reserved<br>The value re                                                         | ad from this b                                                                                                                     | it is indetermi  | nate. Do not s | et this bit. |      |  |

| 5             | -               | Reserved<br>The value re                                                         | ad from this b                                                                                                                     | it is indetermi  | nate. Do not s | et this bit. |      |  |

| 4             | -               | Reserved<br>The value re                                                         | ad from this b                                                                                                                     | it is indetermi  | nate. Do not s | et this bit. |      |  |

| 3             | -               | Reserved<br>The value re                                                         | ad from this b                                                                                                                     | it is indetermi  | nate. Do not s | et this bit. |      |  |

| 2             | SPIH            | SPIH         S           0         0           0         1           1         0 | 0 0 Lowest<br>0 1<br>1 0                                                                                                           |                  |                |              |      |  |

| 1             | -               | Reserved<br>The value re                                                         | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                    |                  |                |              |      |  |

| 0             | KBDH            | KB DH K                                                                          | Keyboard interrupt Priority High bit         KB DH       Priority Level         0       0         Lowest       0         1       0 |                  |                |              |      |  |

Reset Value = XXXX X000b Not bit addressable

## **ISP Protocol Description**

### **Physical Layer**

The UART used to transmit information has the following configuration:

- Character: 8-bit data

- Parity: none

- Stop: 2 bits

- Flow control: none

- Baudrate: autobaud is performed by the bootloader to compute the baudrate chosen by the host.

### Frame Description The Serial Protocol is based on the Intel Hex-type records.

Intel Hex records consist of ASCII characters used to represent hexadecimal values and are summarized below.

#### Figure 45. Intel Hex Type Frame

| Record<br>Mark<br>':' | Reclen | Load<br>Offset | Record<br>Type | Data<br>or<br>Info | Checksum |

|-----------------------|--------|----------------|----------------|--------------------|----------|

| 1-byte                | 1-byte | 2-bytes        | 1-byte         | n-bytes            | 1-byte   |

Record Mark:

Record Mark is the start of frame. This field must contain ':'.

Reclen:

Reclen specifies the number of bytes of information or data which follows the Record Type field of the record.

Load Offset:

Load Offset specifies the 16-bit starting load offset of the data bytes, therefore this field is used only for Data Program Record (see Section "ISP Commands Summary").

• Record Type:

Record Type specifies the command type. This field is used to interpret the remaining information within the frame. The encoding for all the current record types is described in Section "ISP Commands Summary".

Data/Info:

Data/Info is a variable length field. It consists of zero or more bytes encoded as pairs of hexadecimal digits. The meaning of data depends on the **Record Type**.

Checksum:

The two's complement of the 8-bit bytes that result from converting each pair of ASCII hexadecimal digits to one byte of binary, and including the **Reclen** field to and including the last byte of the **Data/Info** field. Therefore, the sum of all the ASCII pairs in a record after converting to binary, from the **Reclen** field to and including the **Checksum** field, is zero.

### **Functional Description**

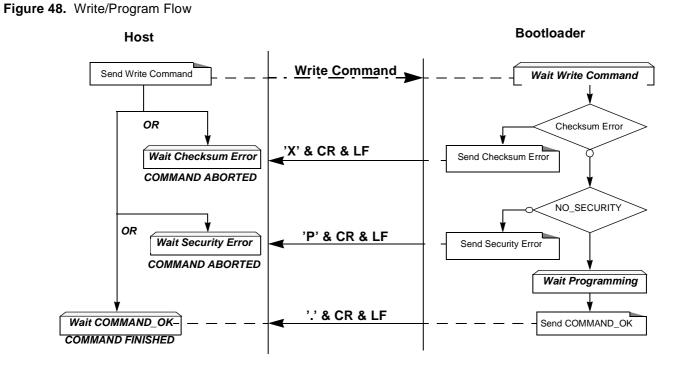

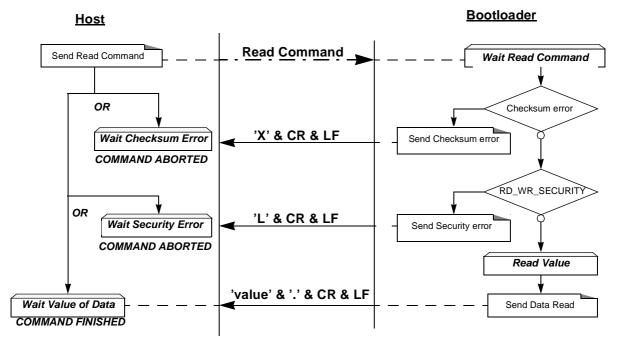

Software Security Bits (SSB)The SSB protects any Flash access from ISP command.<br/>The command "Program Software Security Bit" can only write a higher priority level.

There are three levels of security:

level 0: NO\_SECURITY (FFh)

This is the default level. From level 0, one can write level 1 or level 2.

#### level 1: WRITE\_SECURITY (FEh)

For this level it is impossible to write in the Flash memory, BSB and SBV. The Bootloader returns 'P' on write access. From level 1, one can write only level 2.

• level 2: RD\_WR\_SECURITY (FCh

The level 2 forbids all read and write accesses to/from the Flash/EEPROM memory.

The Bootloader returns 'L' on read or write access.

Only a full chip erase in parallel mode (using a programmer) or ISP command can reset the software security bits.

From level 2, one cannot read and write anything.

|                      | Level 0                  | Level 1                  | Level 2                  |

|----------------------|--------------------------|--------------------------|--------------------------|

| Flash/EEPROM         | Any access allowed       | Read-only access allowed | Any access not allowed   |

| Fuse Bit             | Any access allowed       | Read-only access allowed | Any access not allowed   |

| BSB & SBV            | Any access allowed       | Read-only access allowed | Any access not allowed   |

| SSB                  | Any access allowed       | Write level 2 allowed    | Read-only access allowed |

| Manufacturer<br>Info | Read-only access allowed | Read-only access allowed | Read-only access allowed |

| Bootloader Info      | Read-only access allowed | Read-only access allowed | Read-only access allowed |

| Erase Block          | Allowed                  | Not allowed              | Not allowed              |

| Full Chip Erase      | Allowed                  | Allowed                  | Allowed                  |

| Blank Check          | Allowed                  | Allowed                  | Allowed                  |

Table 73. Software Security Byte Behavior

# Write/Program Commands Description

This flow is common to the following frames:

- Flash/EEPROM Programming Data Frame

- EOF or Atmel Frame (only Programming Atmel Frame)

- Config Byte Programming Data Frame

- Baud Rate Frame

### Example

Programming Data (write 55h at address 0010h in the Flash)\_

HOST

:

01

0010

00

55

9A

BOOTLOADER

:

01

0010

00

55

9A

. CR

LF

Programming Atmet

turction (write SSB to level 2)

HOST

:

02

0000

03

05

01

F5

BOOTLOADER

:

02

0000

03

05

01

F5.

CR

LF

Writing Frame (write BSB to 55h)

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

<

HOST

:

0.3

0.000

0.3

0.6

0.0

5.5

9.F

BOOTLOADER

:

0.3

0.000

0.3

0.6

0.0

5.5

9.F

#### **Read Function Description**

This flow is similar for the following frames:

- Reading Frame

- EOF Frame/ Atmel Frame (only reading Atmel Frame)

### Figure 51. Read Flow

Example

Read function (read SBV)

| HOST             | : 02 0000 05 07 02 F0                |

|------------------|--------------------------------------|

| BOOTLOADER       | : 02 0000 05 07 02 F0 Value . CR LF  |

| Atmel Read funct | <u>ion (read Bootloader version)</u> |

| HOST             | : 02 0000 01 02 00 FB                |

| BOOTLOADER       | : 02 0000 01 02 00 FB Value . CR LF  |

|                      | ®                                                                                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| API Call Description | The IAP allows to reprogram a microcontroller on-chip Flash memory without removing it from the system and while the embedded application is running. |

|                      | The user application can call some Application Programming Interface (API) routines allowing IAP. These API are executed by the bootloader.           |

|                      | To call the corresponding API, the user must use a set of Flash_api routines which can be linked with the application.                                |

|                      | Example of Flash_api routines are available on the Atmel web site on the software appli-<br>cation note:                                              |

|                      | C Flash Drivers for the AT89C51RD2/ED2                                                                                                                |

|                      | The API calls description and arguments are shown in Table 76.                                                                                        |

| Process              | The application selects an API by setting R1, ACC, DPTR0 and DPTR1 registers.                                                                         |

|                      | All calls are made through a common interface "USER_CALL" at the address FFF0h.                                                                       |

|                      | The jump at the USER_CALL must be done by LCALL instruction to be able to come-<br>back in the application.                                           |

|                      | Before jump at the USER_CALL, the bit ENBOOT in AUXR1 register must be set.                                                                           |

| Constraints          | The interrupts are not disabled by the bootloader.                                                                                                    |

|                      | Interrupts must be disabled by user prior to jump to the USER_CALL, then re-enabled when returning.                                                   |

|                      | Interrupts must also be disabled before accessing EEPROM Data then re-enabled after.                                                                  |

MEL

The user must take care of hardware watchdog before launching a Flash operation.

| Command              | R1  | Α             | DPTR0                            | DPTR1 | Returned Value           | Command Effect                                        |

|----------------------|-----|---------------|----------------------------------|-------|--------------------------|-------------------------------------------------------|

| READ MANUF ID        | 00h | XXh           | 0000h                            | XXh   | ACC = Manufacturer<br>Id | Read Manufacturer identifier                          |

| READ DEVICE ID1      | 00h | XXh           | 0001h                            | XXh   | ACC = Device Id 1        | Read Device identifier 1                              |

| READ DEVICE ID2      | 00h | XXh           | 0002h                            | XXh   | ACC = Device Id 2        | Read Device identifier 2                              |

| READ DEVICE ID3      | 00h | XXh           | 0003h                            | XXh   | ACC = Device Id 3        | Read Device identifier 3                              |

|                      | 01h |               | DPH = 00h                        | 00h   | ACC = DPH                | Erase block 0                                         |

|                      |     |               | DPH = 20h                        |       |                          | Erase block 1                                         |

| ERASE BLOCK          |     | XXh           | DPH = 40h                        |       |                          | Erase block 2                                         |

|                      |     |               | DPH = 80h                        |       |                          | Erase block 3                                         |

|                      |     |               | DPH = C0h                        |       |                          | Erase block 4                                         |

| PROGRAM DATA<br>BYTE | 02h | Vaue to write | Address of<br>byte to<br>program | XXh   | ACC = 0: DONE            | Program up one data byte in the on-chip flash memory. |

## Table 76. API Call Summary

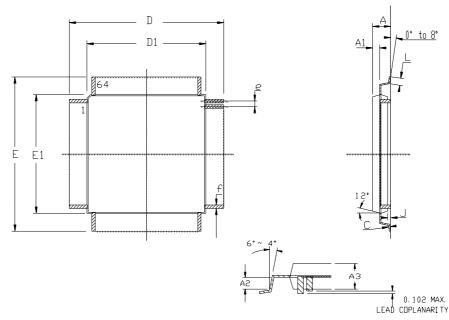

## VQFP64

|    | м        | м      | IN        | СН       |  |

|----|----------|--------|-----------|----------|--|

|    | Min      | Max    | Min       | Max      |  |

| А  | -        | 1.60   | _         | . 063    |  |

| A1 | Ο.       | 64 REF | . 0       | .025 REF |  |

| A2 | 0.       | 64 REF | . 0       | 25 REF   |  |

| A3 | 1.35     | 1.45   | . 053     | . 057    |  |

| D  | 11.75    | 12.25  | . 463     | . 483    |  |

| D1 | 9.90     | 10.10  | . 390     | . 398    |  |

| E  | 11.75    | 12.25  | . 463     | . 483    |  |

| E1 | 9.90     | 10.10  | . 390     | . 398    |  |

| J  | 0.05     | -      | . 002     | -        |  |

| L  | 0.45     | 0,75   | . 018     | .030     |  |

| e  | 0.50 BSC |        | .0197 BSC |          |  |

| f  | 0.2      | 5 BSC  | . 01      | 0 BSC    |  |