Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| betans                     |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 120MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | -                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 24K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                               |

| Data Converters            | A/D 8x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-LQFP                                                                   |

| Supplier Device Package    | 80-LQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc4072fbd80e     |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 32-bit ARM Cortex-M4 microcontroller

| -             |            | 1         | -          |                        |     |          |       |     |      |     |        |            |     |          |

|---------------|------------|-----------|------------|------------------------|-----|----------|-------|-----|------|-----|--------|------------|-----|----------|

| Type number   | Flash (kB) | SRAM (kB) | EEPROM (B) | EMC bus<br>width (bit) | LCD | Ethernet | USB   | CAN | UART | QEI | SD/MMC | Comparator | FPU | Package  |

| LPC4078FBD144 | 512        | 96        | 4032       | 8                      | no  | yes      | H/O/D | 2   | 5    | yes | yes    | yes        | yes | LQFP144  |

| LPC4078FBD100 | 512        | 96        | 4032       | -                      | no  | yes      | H/O/D | 2   | 5    | yes | yes    | yes        | yes | LQFP100  |

| LPC4078FBD80  | 512        | 96        | 4032       | -                      | no  | yes      | H/O/D | 2   | 5    | yes | no     | yes        | yes | LQFP80   |

| LPC4076       |            |           |            |                        |     |          |       |     |      |     |        |            |     |          |

| LPC4076FET180 | 256        | 80        | 2048       | 16                     | no  | yes      | H/O/D | 2   | 5    | yes | yes    | yes        | yes | TFBGA180 |

| LPC4076FBD144 | 256        | 80        | 2048       | 8                      | no  | yes      | H/O/D | 2   | 5    | yes | yes    | yes        | yes | LQFP144  |

| LPC4074       |            |           |            |                        |     |          |       |     |      |     |        |            |     |          |

| LPC4074FBD144 | 128        | 40        | 2048       | -                      | no  | no       | D     | 2   | 4    | no  | no     | no         | no  | LQFP144  |

| LPC4074FBD80  | 128        | 40        | 2048       | -                      | no  | no       | D     | 2   | 4    | no  | no     | no         | no  | LQFP80   |

| LPC4072       |            |           |            |                        |     |          |       |     |      |     |        |            |     | ·        |

| LPC4072FET80  | 64         | 24        | 2048       | -                      | no  | no       | D     | 2   | 4    | no  | no     | no         | no  | TFBGA80  |

| LPC4072FBD80  | 64         | 24        | 2048       | -                      | no  | no       | D     | 2   | 4    | no  | no     | no         | no  | LQFP80   |

#### Table 2. Ordering options ...continued

onductors N.V. 2017. All rights reserved. 19 of 140

Rev. 3 — 11 January 2017

F

Table 3.

Pin description ...continued

Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, comparator pins) and <u>Table 5</u> (EMC pins).

| 3X_7X                                                                     | Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 | Pin LQFP100 | Pin LQFP80 | Pin TFBGA80 |     | Reset state <u>[1]</u> | Type <sup>[2]</sup> | Description                                                                                                                                                                                 |

|---------------------------------------------------------------------------|--------|-------------|---------------|---------------|-------------|-------------|------------|-------------|-----|------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                           | P0[23] | 18          | H1            | F5            | 13          | 9           | -          | -           | [5] | I; PU                  | I/O                 | P0[23] — General purpose digital input/output pin.                                                                                                                                          |

|                                                                           |        |             |               |               |             |             |            |             |     |                        | I                   | <b>ADC0_IN[0]</b> — A/D converter 0, input 0. When configured as an ADC input, the digital function of the pin must be disabled.                                                            |

| All inf                                                                   |        |             |               |               |             |             |            |             |     |                        | I/O                 | <b>I2S_RX_SCK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>I</i> <sup>2</sup> S-bus specification.                    |

| ormatic                                                                   |        |             |               |               |             |             |            |             |     |                        | I                   | T3_CAP0 — Capture input for Timer 3, channel 0.                                                                                                                                             |

| on prov                                                                   | P0[24] | 16          | G2            | E1            | 11          | 8           | -          | -           | [5] | I; PU                  | I/O                 | P0[24] — General purpose digital input/output pin.                                                                                                                                          |

| ided in this docu                                                         |        |             |               |               |             |             |            |             |     |                        | 1                   | <b>ADC0_IN[1]</b> — A/D converter 0, input 1. When configured as an ADC input, the digital function of the pin must be disabled.                                                            |

| All information provided in this document is subject to legal disclaimers |        |             |               |               |             |             |            |             |     |                        | I/O                 | <b>I2S_RX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>I</i> <sup>2</sup> S-bus specification.                |

| o legal                                                                   |        |             |               |               |             |             |            |             |     |                        | I                   | T3_CAP1 — Capture input for Timer 3, channel 1.                                                                                                                                             |

| disclair                                                                  | P0[25] | 14          | F1            | E4            | 10          | 7           | 7          | D1          | [5] | I; PU                  | I/O                 | P0[25] — General purpose digital input/output pin.                                                                                                                                          |

| ners.                                                                     |        |             |               |               |             |             |            |             |     |                        | 1                   | <b>ADC0_IN[2]</b> — A/D converter 0, input 2. When configured as an ADC input, the digital function of the pin must be disabled.                                                            |

| © NXF                                                                     |        |             |               |               |             |             |            |             |     |                        | I/O                 | <b>I2S_RX_SDA</b> — Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> <i>S</i> - <i>bus specification</i> . |

| © NXP Semico                                                              |        |             |               |               |             |             |            |             |     |                        | 0                   | U3_TXD — Transmitter output for UART3.                                                                                                                                                      |

**NXP Semiconductors**

32-LPC408x/7x

| <u>-</u>      |  |

|---------------|--|

| t arm         |  |

| Cortex-M4     |  |

| microcontroll |  |

Table 3.

Pin description ...continued

Image: Section 2...continued

Image: Section 2...continued

Image: Section 2...continued

Image: Section 2....continued

I

| (_7X                                                                     | Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 | Pin LQFP100 | Pin LQFP80 | Pin TFBGA80 |     | Reset state <u>[1]</u> | Type <sup>[2]</sup> | Description                                                            |

|--------------------------------------------------------------------------|--------|-------------|---------------|---------------|-------------|-------------|------------|-------------|-----|------------------------|---------------------|------------------------------------------------------------------------|

|                                                                          | P1[20] | 70          | U7            | K6            | 49          | 34          | 27         | J5          | [3] | I; PU                  | I/O                 | P1[20] — General purpose digital input/output pin.                     |

|                                                                          |        |             |               |               |             |             |            |             |     |                        | 0                   | <b>USB_TX_DP1</b> — D+ transmit data for USB port 1 (OTG transceiver). |

|                                                                          |        |             |               |               |             |             |            |             |     |                        | 0                   | PWM1[2] — Pulse Width Modulator 1, channel 2 output.                   |

|                                                                          |        |             |               |               |             |             |            |             |     |                        | I                   | <b>QEI_PHA</b> — Quadrature Encoder Interface PHA input.               |

| All ir                                                                   |        |             |               |               |             |             |            |             |     |                        | I                   | MC_FB0 — Motor control PWM channel 0 feedback input.                   |

| format                                                                   |        |             |               |               |             |             |            |             |     |                        | I/O                 | SSP0_SCK — Serial clock for SSP0.                                      |

| ion pro                                                                  |        |             |               |               |             |             |            |             |     |                        | 0                   | LCD_VD[6] — LCD data.                                                  |

| vided ir                                                                 |        |             |               |               |             |             |            |             |     |                        | 0                   | LCD_VD[10] — LCD data.                                                 |

| n this d                                                                 | P1[21] | 72          | R8            | N6            | 50          | 35          | -          | -           | [3] | I; PU                  | I/O                 | P1[21] — General purpose digital input/output pin.                     |

| All information provided in this document is subject to legal disclaimen |        |             |               |               |             |             |            |             |     |                        | 0                   | <b>USB_TX_DM1</b> — D– transmit data for USB port 1 (OTG transceiver). |

| subjec                                                                   |        |             |               |               |             |             |            |             |     |                        | 0                   | <b>PWM1[3]</b> — Pulse Width Modulator 1, channel 3 output.            |

| t to lega                                                                |        |             |               |               |             |             |            |             |     |                        | I/O                 | SSP0_SSEL — Slave Select for SSP0.                                     |

| al discla                                                                |        |             |               |               |             |             |            |             |     |                        | Ι                   | <b>MC_ABORT</b> — Motor control PWM, active low fast abort.            |

| aimers.                                                                  |        |             |               |               |             |             |            |             |     |                        | -                   | R — Function reserved.                                                 |

|                                                                          |        |             |               |               |             |             |            |             |     |                        | 0                   | LCD_VD[7] — LCD data.                                                  |

|                                                                          |        |             |               |               |             |             |            |             |     |                        | 0                   | LCD_VD[11] — LCD data.                                                 |

Product data sheet

Rev. 3 11 January 2017

© NXP Semiconductors N.V. 2017. All rights reserved. 26 of 140

**NXP Semiconductors**

32-bit ARM Cortex-M4 microcontroller

LPC408x/7x

#### Pin description ... continued

Table 3.

Pin description ...continued

Image: Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, comparator pins) and <u>Table 5</u> (EMC pins).

| <sup>98X_7X</sup><br>duct data sheet                                                                 | Symbol          | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 | Pin LQFP100 | Pin LQFP80 | Pin TFBGA80 |     | Reset state <u>[1]</u> | Type <sup>[2]</sup> | Description                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------|-----------------|-------------|---------------|---------------|-------------|-------------|------------|-------------|-----|------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                      | P2[0] to P2[31] |             |               |               |             |             |            |             |     |                        | I/O                 | <b>Port 2:</b> Port 2 is a 32 bit I/O port with individual direction controls for each bit. The operation of port 1 pins depends upon the pin function selected via the pin connect block. |

|                                                                                                      | P2[0]           | 154         | B17           | D12           | 107         | 75          | 60         | B10         | [3] | I; PU                  | I/O                 | P2[0] — General purpose digital input/output pin.                                                                                                                                          |

|                                                                                                      |                 |             |               |               |             |             |            |             |     |                        | 0                   | <b>PWM1[1]</b> — Pulse Width Modulator 1, channel 1 output.                                                                                                                                |

| A                                                                                                    |                 |             |               |               |             |             |            |             |     |                        | 0                   | <b>U1_TXD</b> — Transmitter output for UART1.                                                                                                                                              |

| All information provided in this document is subject to legal disclaimen<br>Rev. 3 — 11 January 2017 |                 |             |               |               |             |             |            |             |     |                        | -                   | R — Function reserved.                                                                                                                                                                     |

| R<br>R                                                                                               |                 |             |               |               |             |             |            |             |     |                        | -                   | R — Function reserved.                                                                                                                                                                     |

| Rev. 3                                                                                               |                 |             |               |               |             |             |            |             |     |                        | -                   | R — Function reserved.                                                                                                                                                                     |

| in this                                                                                              |                 |             |               |               |             |             |            |             |     |                        | -                   | R — Function reserved.                                                                                                                                                                     |

| 11 J                                                                                                 |                 |             |               |               |             |             |            |             |     |                        | 0                   | LCD_PWR — LCD panel power enable.                                                                                                                                                          |

| s document is subject to legs 11 January 2017                                                        | P2[1]           | 152         | E14           | C14           | 106         | 74          | 59         | B8          | [3] | I; PU                  | I/O                 | P2[1] — General purpose digital input/output pin.                                                                                                                                          |

| subjec                                                                                               |                 |             |               |               |             |             |            |             |     |                        | 0                   | PWM1[2] — Pulse Width Modulator 1, channel 2 output.                                                                                                                                       |

| 2017                                                                                                 |                 |             |               |               |             |             |            |             |     |                        | I                   | U1_RXD — Receiver input for UART1.                                                                                                                                                         |

| al disc                                                                                              |                 |             |               |               |             |             |            |             |     |                        | -                   | R — Function reserved.                                                                                                                                                                     |

| laimers                                                                                              |                 |             |               |               |             |             |            |             |     |                        | -                   | R — Function reserved.                                                                                                                                                                     |

|                                                                                                      |                 |             |               |               |             |             |            |             |     |                        | -                   | R — Function reserved.                                                                                                                                                                     |

|                                                                                                      |                 |             |               |               |             |             |            |             |     |                        | -                   | R — Function reserved.                                                                                                                                                                     |

|                                                                                                      |                 |             |               |               |             |             |            |             |     |                        | 0                   | LCD_LE — Line end signal.                                                                                                                                                                  |

| ©<br>z                                                                                               | P2[2]           | 150         | D15           | E11           | 105         | 73          | 58         | B9          | [3] | I; PU                  | I/O                 | P2[2] — General purpose digital input/output pin.                                                                                                                                          |

| IXP Se                                                                                               |                 |             |               |               |             |             |            |             |     |                        | 0                   | PWM1[3] — Pulse Width Modulator 1, channel 3 output.                                                                                                                                       |

| micono                                                                                               |                 |             |               |               |             |             |            |             |     |                        | I                   | U1_CTS — Clear to Send input for UART1.                                                                                                                                                    |

| fuctors                                                                                              |                 |             |               |               |             |             |            |             |     |                        | 0                   | T2_MAT3 — Match output for Timer 2, channel 3.                                                                                                                                             |

| N.V. 2                                                                                               |                 |             |               |               |             |             |            |             |     |                        | -                   | R — Function reserved.                                                                                                                                                                     |

| © NXP Semiconductors N.V. 2017. All rights reserved<br>31 of 140                                     |                 |             |               |               |             |             |            |             |     |                        | 0                   | TRACEDATA[3] — Trace data, bit 3.                                                                                                                                                          |

| 1 rights                                                                                             |                 |             |               |               |             |             |            |             |     |                        | -                   | R — Function reserved.                                                                                                                                                                     |

| of 140                                                                                               |                 |             |               |               |             |             |            |             |     |                        | 0                   | LCD_DCLK — LCD panel clock.                                                                                                                                                                |

Product data sheet

#### 7.11.1 Features

- Dynamic memory interface support including single data rate SDRAM.

- Asynchronous static memory device support including RAM, ROM, and flash, with or without asynchronous page mode.

- Low transaction latency.

- Read and write buffers to reduce latency and to improve performance.

- 8/16/32 data and 16/20/26 address lines wide static memory support.

- 16 bit and 32 bit wide chip select SDRAM memory support.

- Static memory features include:

- Asynchronous page mode read.

- Programmable Wait States.

- Bus turnaround delay.

- Output enable and write enable delays.

- Extended wait.

- Four chip selects for synchronous memory and four chip selects for static memory devices.

- Power-saving modes dynamically control EMC\_CKE and EMC\_CLK outputs to SDRAMs.

- Dynamic memory self-refresh mode controlled by software.

- Controller supports 2048 (A0 to A10), 4096 (A0 to A11), and 8192 (A0 to A12) row address synchronous memory parts. That is typical 512 MB, 256 MB, and 128 MB parts, with 4, 8, 16, or 32 data bits per device.

- Separate reset domains allow the for auto-refresh through a chip reset if desired.

Note: Synchronous static memory devices (synchronous burst mode) are not supported.

### 7.12 General purpose DMA controller

The GPDMA is an AMBA AHB compliant peripheral allowing selected peripherals to have DMA support.

The GPDMA enables peripheral-to-memory, memory-to-peripheral, peripheral-to-peripheral, and memory-to-memory transactions. The source and destination areas can each be either a memory region or a peripheral and can be accessed through the AHB master. The GPDMA controller allows data transfers between the various on-chip SRAM areas and supports the SD/MMC card interface, all SSPs, the I<sup>2</sup>S, all UARTs, the A/D Converter, and the D/A Converter peripherals. DMA can also be triggered by selected timer match conditions. Memory-to-memory transfers and transfers to or from GPIO are supported.

#### 7.12.1 Features

- Eight DMA channels. Each channel can support an unidirectional transfer.

- 16 DMA request lines.

56 of 140

The I<sup>2</sup>S-bus specification defines a 3-wire serial bus using one data line, one clock line, and one word select signal. The basic I<sup>2</sup>S connection has one master, which is always the master, and one slave. The I<sup>2</sup>S interface on the LPC408x/7x provides a separate transmit and receive channel, each of which can operate as either a master or a slave.

#### 7.26.1 Features

- The interface has separate input/output channels each of which can operate in master or slave mode.

- Capable of handling 8-bit, 16-bit, and 32-bit word sizes.

- Mono and stereo audio data supported.

- The sampling frequency can range from 16 kHz to 48 kHz (16, 22.05, 32, 44.1, 48) kHz.

- Configurable word select period in master mode (separately for I<sup>2</sup>S input and output).

- Two 8 word FIFO data buffers are provided, one for transmit and one for receive.

- Generates interrupt requests when buffer levels cross a programmable boundary.

- Two DMA requests, controlled by programmable buffer levels. These are connected to the GPDMA block.

- Controls include reset, stop and mute options separately for I<sup>2</sup>S input and I<sup>2</sup>S output.

#### 7.27 CAN controller and acceptance filters

The LPC408x/7x contain one CAN controller with two channels.

The Controller Area Network (CAN) is a serial communications protocol which efficiently supports distributed real-time control with a very high level of security. Its domain of application ranges from high-speed networks to low cost multiplex wiring.

The CAN block is intended to support multiple CAN buses simultaneously, allowing the device to be used as a gateway, switch, or router between two of CAN buses in industrial or automotive applications.

Each CAN controller has a register structure similar to the NXP SJA1000 and the PeliCAN Library block, but the 8-bit registers of those devices have been combined in 32-bit words to allow simultaneous access in the ARM environment. The main operational difference is that the recognition of received Identifiers, known in CAN terminology as Acceptance Filtering, has been removed from the CAN controllers and centralized in a global Acceptance Filter.

#### 7.27.1 Features

- Dual-channel CAN controller and bus.

- Data rates to 1 Mbit/s on each bus.

- 32-bit register and RAM access.

- Compatible with CAN specification 2.0B, ISO 11898-1.

- Global Acceptance Filter recognizes 11-bit and 29-bit receive identifiers for all CAN buses.

- Acceptance Filter can provide FullCAN-style automatic reception for selected Standard Identifiers.

LPC408X 7X

#### 7.36.4.4 Deep power-down mode

The Deep power-down mode can only be entered from the RTC block. In Deep power-down mode, power is shut off to the entire chip with the exception of the RTC module and the RESET pin.

To optimize power conservation, the user has the additional option of turning off or retaining power to the 32 kHz oscillator. It is also possible to use external circuitry to turn off power to the on-chip regulator via the  $V_{DD(REG)(3V3)}$  pins and/or the I/O power via the  $V_{DD(3V3)}$  pins after entering Deep Power-down mode. Power must be restored before device operation can be restarted.

The LPC408x/7x can wake up from Deep power-down mode via the  $\overline{\text{RESET}}$  pin or an alarm match event of the RTC.

#### 7.36.4.5 Wake-up Interrupt Controller (WIC)

The WIC allows the CPU to automatically wake up from any enabled priority interrupt that can occur while the clocks are stopped in Deep-sleep, Power-down, and Deep power-down modes.

The WIC works in connection with the Nested Vectored Interrupt Controller (NVIC). When the CPU enters Deep-sleep, Power-down, or Deep power-down mode, the NVIC sends a mask of the current interrupt situation to the WIC. This mask includes all of the interrupts that are both enabled and of sufficient priority to be serviced immediately. With this information, the WIC simply notices when one of the interrupts has occurred and then it wakes up the CPU.

The WIC eliminates the need to periodically wake up the CPU and poll the interrupts resulting in additional power savings.

#### 7.36.5 Peripheral power control

A power control for peripherals feature allows individual peripherals to be turned off if they are not needed in the application, resulting in additional power savings.

#### 7.36.6 Power domains

The LPC408x/7x provide two independent power domains that allow the bulk of the device to have power removed while maintaining operation of the RTC and the backup registers.

On the LPC408x/7x, I/O pads are powered by  $V_{DD(3V3)}$ , while  $V_{DD(REG)(3V3)}$  powers the on-chip voltage regulator which in turn provides power to the CPU and most of the peripherals.

Depending on the LPC408x/7x application, a design can use two power options to manage power consumption.

The first option assumes that power consumption is not a concern and the design ties the  $V_{DD(3V3)}$  and  $V_{DD(REG)(3V3)}$  pins together. This approach requires only one 3.3 V power supply for both pads, the CPU, and peripherals. While this solution is simple, it does not support powering down the I/O pad ring "on the fly" while keeping the CPU and peripherals alive.

LPC408X 7X

#### 32-bit ARM Cortex-M4 microcontroller

#### Table 8.Thermal characteristics

$V_{DD} = 3.0$  V to 3.6 V;  $T_{amb} = -40$  °C to +85 °C unless otherwise specified;

| Symbol              | Parameter                       | Conditions | Min | Тур | Max | Unit |

|---------------------|---------------------------------|------------|-----|-----|-----|------|

| T <sub>j(max)</sub> | maximum junction<br>temperature |            | -   | -   | 125 | °C   |

#### Table 9. Thermal resistance (LQFP packages)

$T_{amb} = -40$  °C to +85 °C unless otherwise specified.

|     |                                     | Thermal resistar | nce value (°C/W): ±15 % |         |

|-----|-------------------------------------|------------------|-------------------------|---------|

|     |                                     | LQFP80           | LQFP144                 | LQFP208 |

| θја |                                     |                  |                         |         |

|     | JEDEC (4.5 in × 4 in)               |                  |                         |         |

|     | 0 m/s                               | 41               | 31                      | 27      |

|     | 1 m/s                               | 35               | 28                      | 25      |

|     | 2.5 m/s                             | 32               | 26                      | 24      |

|     | Single-layer (4.5 in $\times$ 3 in) |                  |                         |         |

|     | 0 m/s                               | 61               | 43                      | 35      |

|     | 1 m/s                               | 47               | 35                      | 31      |

|     | 2.5 m/s                             | 43               | 33                      | 29      |

| өјс |                                     | 7.8              | 9.2                     | 10.5    |

| θjb |                                     | 11.6             | 13.5                    | 15.2    |

#### Table 10. Thermal resistance value (TFBGA packages)

$T_{amb} = -40$  °C to +85 °C unless otherwise specified.

|     |                         | Thermal resistance | ce value (°C/W): ±15 % |

|-----|-------------------------|--------------------|------------------------|

|     |                         | TFBGA180           | TFBGA208               |

| өја |                         |                    |                        |

|     | JEDEC (4.5 in × 4 in)   |                    |                        |

|     | 0 m/s                   | 47                 | 43                     |

|     | 1 m/s                   | 39                 | 37                     |

|     | 2.5 m/s                 | 35                 | 33                     |

|     | 8-layer (4.5 in × 3 in) |                    |                        |

|     | 0 m/s                   | 39                 | 37                     |

|     | 1 m/s                   | 35                 | 33                     |

|     | 2.5 m/s                 | 31                 | 30                     |

| өјс |                         | 8.5                | 7.4                    |

| θjb |                         | 13                 | 16                     |

#### 32-bit ARM Cortex-M4 microcontroller

| Symbol                    | Parameter                                  | Conditions                                                      |                  | Min                            | Typ[1]                    | Max                     | Unit |

|---------------------------|--------------------------------------------|-----------------------------------------------------------------|------------------|--------------------------------|---------------------------|-------------------------|------|

| Standard po               | ort pins, RESET                            |                                                                 |                  |                                |                           |                         |      |

| IIL                       | LOW-level input current                    | V <sub>I</sub> = 0 V; on-chip pull-up resistor disabled         |                  | -                              | 0.5                       | 10                      | nA   |

| I <sub>IH</sub>           | HIGH-level input<br>current                | $V_I = V_{DD(3V3)}$ ; on-chip<br>pull-down resistor<br>disabled |                  | -                              | 0.5                       | 10                      | nA   |

| VI                        | input voltage                              | pin configured to provide<br>a digital function                 | [15][16]<br>[17] | 0                              | -                         | 5.0                     | V    |

| Vo                        | output voltage                             | output active                                                   |                  | 0                              | -                         | V <sub>DD(3V3)</sub>    | V    |

| V <sub>IH</sub>           | HIGH-level input voltage                   |                                                                 |                  | 0.7V <sub>DD(3V3)</sub>        | -                         | -                       | V    |

| V <sub>IL</sub>           | LOW-level input voltage                    |                                                                 |                  | -                              | -                         | 0.3V <sub>DD(3V3)</sub> | V    |

| V <sub>hys</sub>          | hysteresis voltage                         |                                                                 |                  | 0.4                            | -                         | -                       | V    |

| V <sub>OH</sub>           | HIGH-level output voltage                  | $I_{OH} = -4 \text{ mA}$                                        |                  | V <sub>DD(3V3)</sub> -<br>0.45 | -                         | -                       | V    |

| V <sub>OL</sub>           | LOW-level output voltage                   | I <sub>OL</sub> = 4 mA                                          |                  | -                              | -                         | 0.45                    | V    |

| I <sub>OH</sub>           | HIGH-level output current                  | $V_{OH} = V_{DD(3V3)} - 0.4 V$                                  |                  | -4                             | -                         | -                       | mA   |

| I <sub>OL</sub>           | LOW-level output current                   | V <sub>OL</sub> = 0.4 V                                         |                  | 4                              | -                         | -                       | mA   |

| I <sub>OHS</sub>          | HIGH-level short-circuit<br>output current | V <sub>OH</sub> = 0 V                                           | [18]             | -                              | -                         | -50                     | mA   |

| I <sub>OLS</sub>          | LOW-level short-circuit<br>output current  | $V_{OL} = V_{DD(3V3)}$                                          | [18]             | -                              | -                         | 60                      | mA   |

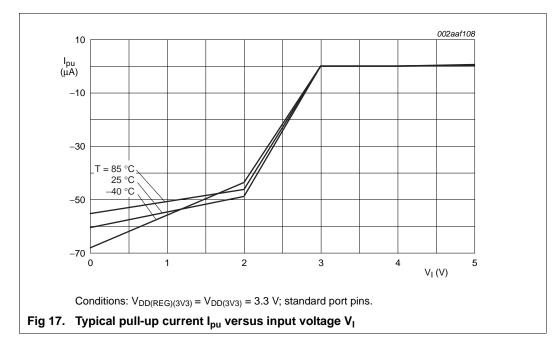

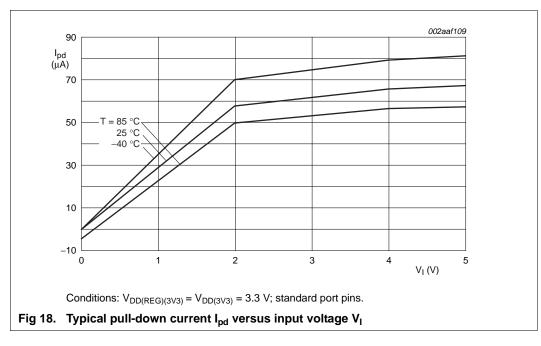

| I <sub>pd</sub>           | pull-down current                          | V <sub>I</sub> = 5 V                                            |                  | 10                             | 50                        | 150                     | μΑ   |

| I <sub>pu</sub>           | pull-up current                            | $V_{I} = 0 V$                                                   |                  | -15                            | -50                       | -85                     | μΑ   |

|                           |                                            | $V_{DD(3V3)} < V_{I} < 5 V$                                     |                  | 0                              | 0                         | 0                       | μΑ   |

| I <sup>2</sup> C-bus pins | s (P0[27] and P0[28])                      |                                                                 |                  |                                |                           |                         |      |

| V <sub>IH</sub>           | HIGH-level input<br>voltage                |                                                                 |                  | 0.7V <sub>DD(3V3)</sub>        | -                         | -                       | V    |

| V <sub>IL</sub>           | LOW-level input voltage                    |                                                                 |                  | -                              | -                         | 0.3V <sub>DD(3V3)</sub> | V    |

| V <sub>hys</sub>          | hysteresis voltage                         |                                                                 |                  | -                              | $0.05 \times V_{DD(3V3)}$ | -                       | V    |

| V <sub>OL</sub>           | LOW-level output voltage                   | I <sub>OLS</sub> = 3 mA                                         |                  | -                              | -                         | 0.4                     | V    |

| ILI                       | input leakage current                      | $V_{I} = V_{DD(3V3)}$                                           | [19]             | -                              | 2                         | 4                       | μΑ   |

|                           |                                            | V <sub>I</sub> = 5 V                                            |                  | -                              | 10                        | 22                      | μΑ   |

| USB pins                  |                                            |                                                                 |                  |                                |                           |                         |      |

| I <sub>OZ</sub>           | OFF-state output current                   | 0 V < V <sub>I</sub> < 3.3 V                                    | [20]             | -                              | -                         | ±10                     | μA   |

| V <sub>BUS</sub>          | bus supply voltage                         |                                                                 | [20]             | -                              | -                         | 5.25                    | V    |

| V <sub>DI</sub>           | differential input sensitivity voltage     | (D+) - (D-)                                                     | [20]             | 0.2                            | -                         | -                       | V    |

### Table 11. Static characteristics ... continued

#### 32-bit ARM Cortex-M4 microcontroller

89 of 140

#### 32-bit ARM Cortex-M4 microcontroller

| Symbol                | Parameter <sup>[1]</sup>        | Conditions <sup>[1]</sup>           |               | Min                                                                                  | Тур                                                                                                        | Max                                                                                                        | Unit |

|-----------------------|---------------------------------|-------------------------------------|---------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|

| t <sub>am</sub>       | memory access<br>time           | RD <sub>5</sub>                     | <u>[4][3]</u> | WAITOEN + 1) ×                                                                       | (WAITRD –<br>WAITOEN + 1) ×                                                                                | (WAITRD –<br>WAITOEN + 1) ×                                                                                | ns   |

| 4                     | data input hold time            |                                     | [5][3]        | T <sub>cy(clk)</sub> – 9.6<br>–5.0                                                   | T <sub>cy(clk)</sub> – 13.2                                                                                | T <sub>cy(clk)</sub> – 20.2                                                                                |      |

| t <sub>h(D)</sub>     | data input hold time            | RD <sub>6</sub>                     | [3][3]        |                                                                                      | -7.2                                                                                                       | -                                                                                                          | ns   |

| t <sub>CSHBLSH</sub>  | CS HIGH to BLS<br>HIGH time     | PB = 1                              |               | 2.7                                                                                  | 3.4                                                                                                        | 4.9                                                                                                        | ns   |

| t <sub>CSHOEH</sub>   | CS HIGH to OE<br>HIGH time      |                                     | [3]           | 2.4                                                                                  | 3.1                                                                                                        | 4.2                                                                                                        | ns   |

| t <sub>oehanv</sub>   | OE HIGH to address invalid time |                                     | [3]           | 0.77                                                                                 | 1.2                                                                                                        | 1.86                                                                                                       | ns   |

| t <sub>deact</sub>    | deactivation time               | RD <sub>7</sub>                     | [3]           | -                                                                                    | -4.3                                                                                                       | -6.1                                                                                                       | ns   |

|                       | le parameters <sup>[2]</sup>    |                                     |               |                                                                                      |                                                                                                            |                                                                                                            |      |

| t <sub>CSLAV</sub>    | CS LOW to address valid time    | WR <sub>1</sub>                     |               | 3.3                                                                                  | 4.3                                                                                                        | 6.1                                                                                                        | ns   |

| t <sub>CSLDV</sub>    | CS LOW to data valid time       | WR <sub>2</sub>                     |               | 3.4                                                                                  | 4.8                                                                                                        | 6.6                                                                                                        | ns   |

| t <sub>CSLWEL</sub>   | CS LOW to WE<br>LOW time        | WR <sub>3</sub> ; PB =1             | [3]           | $2.6 + T_{cy(clk)} \times$<br>(1 + WAITWEN)                                          | $3.3 + T_{cy(clk)} \times$<br>(1 + WAITWEN)                                                                | $4.6 + T_{cy(clk)} \times$<br>(1 + WAITWEN)                                                                | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS<br>LOW time       | WR <sub>4</sub> ; PB = 1            | [3]           | 2.7                                                                                  | 3.5                                                                                                        | 4.9                                                                                                        | ns   |

| t <sub>WELWEH</sub>   | WE LOW to WE<br>HIGH time       | WR <sub>5</sub> ; PB =1             | [3]           | $\begin{array}{l} (WAITWR - \\ WAITWEN + 1) \times \\ T_{cy(clk)} - 2.3 \end{array}$ | $\begin{array}{l} (WAITWR - \\ WAITWEN + 1) \times \\ T_{cy(clk)} - 2.8 \end{array}$                       | $\begin{array}{l} (WAITWR - \\ WAITWEN + 1) \times \\ T_{cy(clk)} - 3.8 \end{array}$                       | ns   |

| t <sub>BLSLBLSH</sub> | BLS LOW to BLS<br>HIGH time     | PB = 1                              | [3]           | $\begin{array}{l} (WAITWR-\\ WAITWEN + 3) \times \\ T_{cy(clk)} - 2.8 \end{array}$   | $\begin{array}{l} (\text{WAITWR}-\\ \text{WAITWEN + 3)}\times\\ \text{T}_{\text{cy(clk)}}-3.5 \end{array}$ | $\begin{array}{l} (\text{WAITWR}-\\ \text{WAITWEN + 3)}\times\\ \text{T}_{\text{cy(clk)}}-5.0 \end{array}$ | ns   |

| t <sub>WEHDNV</sub>   | WE HIGH to data invalid time    | WR <sub>6</sub> ; PB =1             | [3]           | 3.1 + T <sub>cy(clk)</sub>                                                           | 4.3 + T <sub>cy(clk)</sub>                                                                                 | 5.8 + T <sub>cy(clk)</sub>                                                                                 | ns   |

| t <sub>WEHEOW</sub>   | WE HIGH to end of write time    | WR <sub>7</sub> ; PB = 1            | <u>[6][3]</u> | $T_{cy(clk)} - 2.6$                                                                  | $T_{cy(clk)} - 3.4$                                                                                        | $T_{cy(clk)} - 4.6$                                                                                        | ns   |

| t <sub>BLSHDNV</sub>  | BLS HIGH to data invalid time   | PB = 1                              |               | 3.4                                                                                  | 4.8                                                                                                        | 6.6                                                                                                        | ns   |

| t <sub>WEHANV</sub>   | WE HIGH to address invalid time | PB = 1                              | [3]           | 3.0 + T <sub>cy(clk)</sub>                                                           | 3.8 + T <sub>cy(clk)</sub>                                                                                 | 5.3 + T <sub>cy(clk)</sub>                                                                                 | ns   |

| t <sub>deact</sub>    | deactivation time               | WR <sub>8</sub> ; PB = 0; PB =<br>1 | [3]           | -3.3                                                                                 | -4.3                                                                                                       | -6.1                                                                                                       | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS<br>LOW            | WR <sub>9</sub> ; PB = 0            | [3]           | 2.7 + T <sub>cy(clk)</sub> ×<br>(1 + WAITWEN)                                        | 3.5 + T <sub>cy(clk)</sub> ×<br>(1 + WAITWEN)                                                              | 4.9 + T <sub>cy(clk)</sub> ×<br>(1 + WAITWEN)                                                              | ns   |

| t <sub>BLSLBLSH</sub> | BLS LOW to BLS<br>HIGH time     | WR <sub>10</sub> ; PB = 0           | [3]           | $\begin{array}{l} (WAITWR - \\ WAITWEN + 3) \times \\ T_{cy(clk)} - 2.8 \end{array}$ | $\begin{array}{l} (WAITWR-\\ WAITWEN + 3)\times\\ T_{cy(clk)}-3.5 \end{array}$                             | $\begin{array}{l} (\text{WAITWR}-\\ \text{WAITWEN + 3)}\times\\ \text{T}_{\text{cy(clk)}}-5.0 \end{array}$ | ns   |

| t <sub>BLSHEOW</sub>  | BLS HIGH to end of write time   | WR <sub>11</sub> ; PB = 0           | <u>[6][3]</u> | $3.3 + T_{cy(clk)}$                                                                  | $4.4 + T_{cy(clk)}$                                                                                        | $6.1 + T_{cy(clk)}$                                                                                        | ns   |

| t <sub>BLSHDNV</sub>  | BLS HIGH to data invalid time   | WR <sub>12</sub> ; PB = 0           | [3]           | 3.4 + T <sub>cy(clk)</sub>                                                           | 4.8 + T <sub>cy(clk)</sub>                                                                                 | $6.6 + T_{cy(clk)}$                                                                                        | ns   |

Table 15. Dynamic characteristics: Static external memory interface ... continued

[1] Parameters are shown as  $RD_n$  or  $WD_n$  in Figure 19 as indicated in the Conditions column.

**Table 16.** Dynamic characteristics: Dynamic external memory interface, read strategy bits (RD bits) = 00  $C_L = 30 \text{ pF}$ ,  $T_{amb} = -40 \text{ °C}$  to 85 °C,  $V_{DD(3V3)} = 3.0 \text{ V}$  to 3.6 V. Values guaranteed by design.  $t_{fbdly}$  is programmable delay value for the feedback clock that controls input data sampling;  $t_{clk0dly}$  is programmable delay value for the EMC\_CLKOUT0 output;  $t_{clk1dly}$  is programmable delay value for the EMC\_CLKOUT1 output.

| Symbol               | Parameter                              |       | Min                                                                           | Тур                                                                           | Max                        | Unit |

|----------------------|----------------------------------------|-------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------|------|

| Common t             | o read and write cycles                |       |                                                                               |                                                                               | I                          | I    |

| T <sub>cy(clk)</sub> | clock cycle time                       | [1]   | 12.5                                                                          | -                                                                             | -                          | ns   |

| t <sub>d(SV)</sub>   | chip select valid delay time           | [2]   | -                                                                             | t <sub>clkndly</sub> + 3.5                                                    | t <sub>clk0dly</sub> + 5.0 | ns   |

| t <sub>h(S)</sub>    | chip select hold time                  | [2]   | t <sub>clkndly</sub> - 1.0                                                    | t <sub>clkndly</sub> - 1.2                                                    | -                          | ns   |

| t <sub>d(RASV)</sub> | row address strobe valid delay time    | [2]   | -                                                                             | t <sub>clkndly</sub> + 3.6                                                    | t <sub>clkndly</sub> + 5.0 | ns   |

| t <sub>h(RAS)</sub>  | row address strobe hold time           | [2]   | t <sub>clkndly</sub> - 0.8                                                    | t <sub>clkndly</sub> - 0.9                                                    | -                          | ns   |

| t <sub>d(CASV)</sub> | column address strobe valid delay time | [2]   | -                                                                             | t <sub>clkndly</sub> + 3.4                                                    | t <sub>clkndly</sub> + 4.9 | ns   |

| t <sub>h(CAS)</sub>  | column address strobe hold time        | [2]   | t <sub>clkndly</sub> - 0.9                                                    | t <sub>clkndly</sub> - 1.0                                                    | -                          | ns   |

| t <sub>d(WV)</sub>   | write valid delay time                 | [2]   | -                                                                             | t <sub>clkndly</sub> + 4.1                                                    | t <sub>clkndly</sub> + 6.0 | ns   |

| t <sub>h(W)</sub>    | write hold time                        | [2]   | t <sub>clkndly</sub> - 0.9                                                    | t <sub>clkndly</sub> - 0.7                                                    |                            | ns   |

| t <sub>d(AV)</sub>   | address valid delay time               | [2]   | -                                                                             | t <sub>clkndly</sub> + 4.6                                                    | t <sub>clkndly</sub> + 6.8 | ns   |

| t <sub>h(A)</sub>    | address hold time                      | [2]   | t <sub>clkndly</sub> - 1.1                                                    | t <sub>clkndly</sub> - 1.2                                                    | -                          | ns   |

| Read cycle           | e parameters when EMC_CLKOUT           | 0 use | d                                                                             |                                                                               |                            |      |

| t <sub>su(D)</sub>   | data input set-up time                 |       | 5.6 - t <sub>fbdly</sub>                                                      | 4.5 - t <sub>fbdly</sub>                                                      | -                          | ns   |

| t <sub>h(D)</sub>    | data input hold time                   |       | -2.2 + $t_{fbdly}$                                                            | -2.9 + t <sub>fbdly</sub>                                                     | -                          | ns   |

| Read cycle           | e parameters when EMC_CLKOUT           | 1 use | d                                                                             | 1                                                                             | 1                          |      |

| t <sub>su(D)</sub>   | data input set-up time                 |       | 5.6 - $t_{fbdly}$ + ( $t_{clk1dly}$<br>- $t_{clk0dly}$ )                      | 4.5 - $t_{fbdly}$ + ( $t_{clk1dly}$<br>- $t_{clk0dly}$ )                      | -                          | ns   |

| t <sub>h(D)</sub>    | data input hold time                   |       | -2.2 + t <sub>fbdly</sub> -<br>(t <sub>clk1dly</sub> - t <sub>clk0dly</sub> ) | -2.9 + t <sub>fbdly</sub> -<br>(t <sub>clk1dly</sub> - t <sub>clk0dly</sub> ) | -                          | ns   |

| Write cycle          | e parameters                           |       |                                                                               |                                                                               |                            |      |

| t <sub>d(QV)</sub>   | data output valid delay time           | [2]   | -                                                                             | t <sub>clkndly</sub> + 5.4                                                    | t <sub>clkndly</sub> + 7.8 | ns   |

| t <sub>h(Q)</sub>    | data output hold time                  | [2]   | t <sub>clkndly</sub> – 0.4                                                    | t <sub>clkndly</sub>                                                          | -                          | ns   |

[1] Refers to SDRAM clock signal EMC\_CLKOUTn where n = 0 and 1.

[2] t<sub>clkndly</sub> represents t<sub>clk0dly</sub> when EMC\_CLKOUT0 clocks SDRAM. t<sub>clkndly</sub> represents t<sub>clk1dly</sub> when EMC\_CLKOUT1 clocks SDRAM.

#### Table 17. Dynamic characteristics: Dynamic external memory interface, read strategy bits (RD bits) = 01

$C_L = 30 \text{ pF}, T_{amb} = -40 \text{ }^{\circ}\text{C} \text{ to } 85 \text{ }^{\circ}\text{C}, V_{DD(3V3)} = 3.0 \text{ V to } 3.6 \text{ V}.$  Values guaranteed by design.  $t_{cmddly}$  is programmable delay value for EMC command outputs in command delayed mode;  $t_{fbdly}$  is programmable delay value for the feedback clock that controls input data sampling;  $t_{clk0dly}$  is programmable delay value for the EMC\_CLKOUT0 output;  $t_{clk1dly}$  is programmable delay value for the EMC\_CLKOUT0 output;  $t_{clk1dly}$  is programmable delay value for the EMC\_CLKOUT1 output.

| Symbol                                                           | Parameter                    |     | Min                       | Тур                       | Max                        | Unit |  |  |

|------------------------------------------------------------------|------------------------------|-----|---------------------------|---------------------------|----------------------------|------|--|--|

| For RD = 1 t <sub>clk0dly</sub> = 0 and t <sub>clk1dly</sub> = 0 |                              |     |                           |                           |                            |      |  |  |

| Common to                                                        | read and write cycles        |     |                           |                           |                            |      |  |  |

| T <sub>cy(clk)</sub>                                             | clock cycle time             | [1] | 12.5                      | -                         | -                          | ns   |  |  |

| t <sub>d(SV)</sub>                                               | chip select valid delay time |     | -                         | t <sub>cmddly</sub> + 6.8 | t <sub>cmddly</sub> + 10.4 | ns   |  |  |

| t <sub>h(S)</sub>                                                | chip select hold time        |     | t <sub>cmddly</sub> + 1.2 | t <sub>cmddly</sub> + 2.1 | -                          | ns   |  |  |

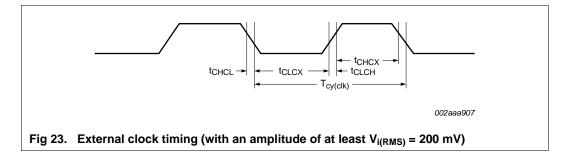

#### 11.3 External clock

#### Table 19. Dynamic characteristic: external clock (see Figure 40)

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}; V_{DD(3V3)} \text{ over specified ranges.}$

| Symbol               | Parameter            | Min                      | Typ[2] | Max  | Unit |

|----------------------|----------------------|--------------------------|--------|------|------|

| f <sub>osc</sub>     | oscillator frequency | 1                        | -      | 25   | MHz  |

| T <sub>cy(clk)</sub> | clock cycle time     | 40                       | -      | 1000 | ns   |

| t <sub>CHCX</sub>    | clock HIGH time      | $T_{cy(clk)} \times 0.4$ | -      | -    | ns   |

| t <sub>CLCX</sub>    | clock LOW time       | $T_{cy(clk)} \times 0.4$ | -      | -    | ns   |

| t <sub>CLCH</sub>    | clock rise time      | -                        | -      | 5    | ns   |

| t <sub>CHCL</sub>    | clock fall time      | -                        | -      | 5    | ns   |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

#### 11.4 Internal oscillators

#### Table 20. Dynamic characteristic: internal oscillators

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}; 2.7 \text{ V} \le V_{DD(3V3)} \le 3.6 \text{ V}.^{[1]}$

| Symbol               | Parameter                        | Min   | Typ <u>[2]</u> | Max   | Unit |

|----------------------|----------------------------------|-------|----------------|-------|------|

| f <sub>osc(RC)</sub> | internal RC oscillator frequency | 11.88 | 12             | 12.12 | MHz  |

| f <sub>i(RTC)</sub>  | RTC input frequency              | -     | 32.768         | -     | kHz  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

### 11.5 I/O pins

#### Table 21. Dynamic characteristic: I/O pins<sup>[1]</sup>

$T_{amb} = -40 \text{ }^{\circ}\text{C} \text{ to } +85 \text{ }^{\circ}\text{C}; V_{DD(3V3)} \text{ over specified ranges.}$

| Symbol         | Parameter | Conditions               | Min | Тур | Max | Unit |

|----------------|-----------|--------------------------|-----|-----|-----|------|

| t <sub>r</sub> | rise time | pin configured as output | 3.0 | -   | 5.0 | ns   |

| t <sub>f</sub> | fall time | pin configured as output | 2.5 | -   | 5.0 | ns   |

[1] Applies to standard port pin. For details, see the LPC408x/7x IBIS model available on the NXP website.

#### 32-bit ARM Cortex-M4 microcontroller

### 11.7 I<sup>2</sup>C-bus

#### Table 23. Dynamic characteristic: I<sup>2</sup>C-bus pins<sup>[1]</sup>

| $T_{amb} = -40$ | °C to | +85 | °C.[2] |

|-----------------|-------|-----|--------|

|-----------------|-------|-----|--------|

| Symbol              | Parameter      |               | Conditions                  | Min                   | Max | Unit |

|---------------------|----------------|---------------|-----------------------------|-----------------------|-----|------|

| f <sub>SCL</sub>    | SCL clock      |               | Standard-mode               | 0                     | 100 | kHz  |

|                     | frequency      |               | Fast-mode                   | 0                     | 400 | kHz  |

|                     |                |               | Fast-mode Plus              | 0                     | 1   | MHz  |

| t <sub>f</sub>      | fall time      | [4][5][6][7]  | of both SDA and SCL signals | -                     | 300 | ns   |

|                     |                | Standard-mode |                             |                       |     |      |

|                     |                |               | Fast-mode                   | $20 + 0.1 \times C_b$ | 300 | ns   |

|                     |                |               | Fast-mode Plus              | -                     | 120 | ns   |

| t <sub>LOW</sub>    | LOW period of  |               | Standard-mode               | 4.7                   | -   | μS   |

|                     | the SCL clock  |               | Fast-mode                   | 1.3                   | -   | μS   |

|                     |                |               | Fast-mode Plus              | 0.5                   | -   | μS   |

| t <sub>HIGH</sub>   | HIGH period of |               | Standard-mode               | 4.0                   | -   | μS   |

|                     | the SCL clock  |               | Fast-mode                   | 0.6                   | -   | μS   |

|                     |                |               | Fast-mode Plus              | 0.26                  | -   | μS   |

| t <sub>HD;DAT</sub> | data hold time | [3][4][8]     | Standard-mode               | 0                     | -   | μS   |

|                     |                |               | Fast-mode                   | 0                     | -   | μS   |

|                     |                |               | Fast-mode Plus              | 0                     | -   | μS   |

| t <sub>SU;DAT</sub> | data set-up    | [9][10]       | Standard-mode               | 250                   | -   | ns   |

|                     | time           |               | Fast-mode                   | 100                   | -   | ns   |

|                     |                |               | Fast-mode Plus              | 50                    | -   | ns   |

[1] See the I<sup>2</sup>C-bus specification UM10204 for details.

[2] Parameters are valid over operating temperature range unless otherwise specified.

- [3] tHD;DAT is the data hold time that is measured from the falling edge of SCL; applies to data in transmission and the acknowledge.

- [4] A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the  $V_{IH}(min)$  of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- [5]  $C_b$  = total capacitance of one bus line in pF.

- [6] The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

- [7] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

- [8] The maximum t<sub>HD;DAT</sub> could be 3.45 μs and 0.9 μs for Standard-mode and Fast-mode but must be less than the maximum of t<sub>VD;DAT</sub> or t<sub>VD;ACK</sub> by a transition time (see *UM10204*). This maximum must only be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

- [9] tSU;DAT is the data set-up time that is measured with respect to the rising edge of SCL; applies to data in transmission and the acknowledge.

- [10] A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system but the requirement  $t_{SU;DAT}$  = 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{r(max)} + t_{SU;DAT} = 1000 + 250 = 1250$  ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time.

#### 32-bit ARM Cortex-M4 microcontroller

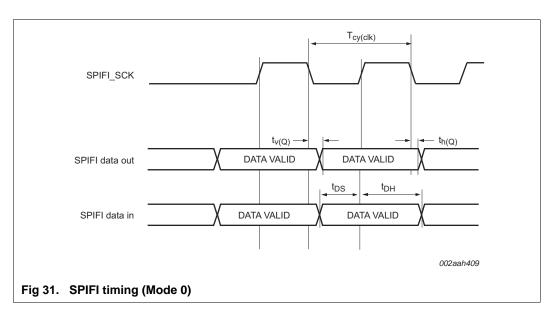

#### 11.11 SPIFI

#### Table 27. Dynamic characteristics: SPIFI

$T_{amb} = -40$  °C to 85 °C; 3.0 V  $\leq V_{DD(3V3)} \leq$  3.6 V;  $C_L = 30$  pF. Values guaranteed by design.

| Symbol               | Parameter              | Min  | Max | Unit |

|----------------------|------------------------|------|-----|------|

| T <sub>cy(clk)</sub> | clock cycle time       | 11.8 | -   | ns   |

| t <sub>DS</sub>      | data set-up time       | 4.8  | -   | ns   |

| t <sub>DH</sub>      | data hold time         | 0    | -   | ns   |

| t <sub>v(Q)</sub>    | data output valid time | -    | 8.8 | ns   |

| t <sub>h(Q)</sub>    | data output hold time  | 3    | -   | ns   |