# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 120MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | -                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 24K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                               |

| Data Converters            | A/D 8x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TFBGA                                                                  |

| Supplier Device Package    | 80-TFBGA (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc4072fet80k     |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 32-bit ARM Cortex-M4 microcontroller

32-bit ARM Cortex-M4 microcontroller LPC408x/7x

#### Table 3. Pin description ... continued

Not all functions are available on all parts. See Table 2 (Ethernet, USB, LCD, QEI, SD/MMC, comparator pins) and Table 5 (EMC pins).

| X_7X                                                                      | Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 | Pin LQFP100 | Pin LQFP80 | Pin TFBGA80 |     | Reset state <u>[1]</u> | Type <sup>[2]</sup>                                                                                                                                                                   | Description                                                                                                                                                                  |

|---------------------------------------------------------------------------|--------|-------------|---------------|---------------|-------------|-------------|------------|-------------|-----|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                           | P0[8]  | 160         | A15           | C12           | 111         | 77          | 62         | A10         | [4] | I; IA                  | I/O                                                                                                                                                                                   | P0[8] — General purpose digital input/output pin.                                                                                                                            |

|                                                                           |        |             |               |               |             |             |            |             |     | I/O                    | <b>I2S_TX_WS</b> — $I^2$ S Transmit word select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>I</i> <sup>2</sup> S-bus specification. |                                                                                                                                                                              |

|                                                                           |        |             |               |               |             |             |            |             |     |                        | I/O                                                                                                                                                                                   | SSP1_MISO — Master In Slave Out for SSP1.                                                                                                                                    |

| All                                                                       |        |             |               |               |             |             |            |             |     |                        | 0                                                                                                                                                                                     | T2_MAT2 — Match output for Timer 2, channel 2.                                                                                                                               |

| informa                                                                   |        |             |               |               |             |             |            |             |     |                        | 1                                                                                                                                                                                     | <b>RTC_EV1</b> — Event input 1 to Event Monitor/Recorder.                                                                                                                    |

| ation pr                                                                  |        |             |               |               |             |             |            |             |     |                        | I                                                                                                                                                                                     | CMP1_IN[3] — Comparator 1, input 3.                                                                                                                                          |

| ovided                                                                    |        |             |               |               |             |             |            |             |     |                        | -                                                                                                                                                                                     | R — Function reserved.                                                                                                                                                       |

| in this                                                                   |        |             |               |               |             |             |            |             |     |                        | 0                                                                                                                                                                                     | LCD_VD[16] — LCD data.                                                                                                                                                       |

| docum                                                                     | P0[9]  | 158         | C14           | A13           | 109         | 76          | 61         | A9          | [4] | I; IA                  | I/O                                                                                                                                                                                   | P0[9] — General purpose digital input/output pin.                                                                                                                            |

| All information provided in this document is subject to legal disclaimers |        |             |               |               |             |             |            |             |     |                        | I/O                                                                                                                                                                                   | <b>I2S_TX_SDA</b> — I <sup>2</sup> S transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $l^2$ S-bus specification. |

| legal d                                                                   |        |             |               |               |             |             |            |             |     |                        | I/O                                                                                                                                                                                   | SSP1_MOSI — Master Out Slave In for SSP1.                                                                                                                                    |

| lisclaim                                                                  |        |             |               |               |             |             |            |             |     |                        | 0                                                                                                                                                                                     | T2_MAT3 — Match output for Timer 2, channel 3.                                                                                                                               |

| ers.                                                                      |        |             |               |               |             |             |            |             |     |                        | I                                                                                                                                                                                     | RTC_EV2 — Event input 2 to Event Monitor/Recorder.                                                                                                                           |

|                                                                           |        |             |               |               |             |             |            |             |     |                        | I                                                                                                                                                                                     | CMP1_IN[2] — Comparator 1, input 2.                                                                                                                                          |

|                                                                           |        |             |               |               |             |             |            |             |     |                        | -                                                                                                                                                                                     | R — Function reserved.                                                                                                                                                       |

|                                                                           |        |             |               |               |             |             |            |             |     |                        | 0                                                                                                                                                                                     | LCD_VD[17] — LCD data.                                                                                                                                                       |

Product data sheet C408×

5

Rev. 3 — 11 January 2017

» NXP Semiconductors N.V. 2017. All rights reserved. 14 of 140

32-bit ARM Cortex-M4 microcontroller LPC408x/7x

Table 3.

Pin description ...continued

Not all functions are available on all parts. See <a href="mailto:Table 2">Table 2</a> (Ethernet, USB, LCD, QEI, SD/MMC, comparator pins) and <a href="mailto:Table 5">Table 5</a> (EMC pins).

| IX_7X                                                                     | Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 | Pin LQFP100 | Pin LQFP80 | Pin TFBGA80 |                                                                                                                                      | Reset state <u>[1]</u> | Type <sup>[2]</sup> | Description                                                                                                                      |

|---------------------------------------------------------------------------|--------|-------------|---------------|---------------|-------------|-------------|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                                                                           | P0[20] | 120         | M17           | K14           | 83          | 58          | -          | -           | [3]                                                                                                                                  | I; PU                  | I/O                 | P0[20] — General purpose digital input/output pin.                                                                               |

|                                                                           |        |             |               |               |             |             |            | 0           | <b>U1_DTR</b> — Data Terminal Ready output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART1. |                        |                     |                                                                                                                                  |

|                                                                           |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | I/O                 | <b>SD_CMD</b> — Command line for SD card interface.                                                                              |

| All infor                                                                 |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | I/O                 | <b>I2C1_SCL</b> — I <sup>2</sup> C1 clock input/output (this pin does not use a specialized I2C pad).                            |

| rmation                                                                   |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | -                   | R — Function reserved.                                                                                                           |

| provid                                                                    |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | -                   | R — Function reserved.                                                                                                           |

| ed in th                                                                  |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | -                   | R — Function reserved.                                                                                                           |

| iis docu                                                                  |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | 0                   | LCD_VD[14] — LCD data.                                                                                                           |

| iment i                                                                   | P0[21] | 118         | M16           | K11           | 82          | 57          | -          | -           | [3]                                                                                                                                  | I; PU                  | I/O                 | <b>P0[21]</b> — General purpose digital input/output pin.                                                                        |

| s subje                                                                   |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | Ι                   | <b>U1_RI</b> — Ring Indicator input for UART1.                                                                                   |

| All information provided in this document is subject to legal disclaimers |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | 0                   | <b>SD_PWR</b> — Power Supply Enable for external SD card power supply.                                                           |

| lisclaimers.                                                              |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | 0                   | <b>U4_OE</b> — RS-485/EIA-485 output enable signal for UART4.                                                                    |

|                                                                           |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | I                   | CAN_RD1 — CAN1 receiver input.                                                                                                   |

|                                                                           |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | I/O                 | <b>U4_SCLK</b> — USART 4 clock input or output in synchronous mode.                                                              |

| ©<br>N                                                                    | P0[22] | 116         | N17           | L14           | 80          | 56          | 44         | H10         | [6]                                                                                                                                  | I; PU                  | I/O                 | P0[22] — General purpose digital input/output pin.                                                                               |

| © NXP Semiconductors N.V. 2017. All rights reserved                       |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | 0                   | <b>U1_RTS</b> — Request to Send output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART1. |

| tors N.                                                                   |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | I/O                 | <b>SD_DAT[0]</b> — Data line 0 for SD card interface.                                                                            |

| V. 2017. All                                                              |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | 0                   | <b>U4_TXD</b> — Transmitter output for USART4 (input/output in smart card mode).                                                 |

| rights r                                                                  |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | 0                   | CAN_TD1 — CAN1 transmitter output.                                                                                               |

| eserve                                                                    |        |             |               |               |             |             |            |             |                                                                                                                                      |                        | 0                   | SPIFI_CLK — Clock output for SPIFI.                                                                                              |

LPC408X Product data sheet

Rev. 3 11 January 2017

Semiconductors N.V. 2017. All rights reserved. 25 of 140

Rev. 3 — 11 January 2017

5

#### Table 3. Pin description ... continued

Not all functions are available on all parts. See Table 2 (Ethernet, USB, LCD, QEI, SD/MMC, comparator pins) and Table 5 (EMC pins).

| X_7X                                                                      | Symbol | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 | Pin LQFP100 | Pin LQFP80 | Pin TFBGA80 |     | Reset state <sup>[1]</sup> | Type <sup>[2]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------|--------|-------------|---------------|---------------|-------------|-------------|------------|-------------|-----|----------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                           | P1[18] | 66          | P7            | L5            | 46          | 32          | 25         | K4          | [3] | I; PU                      | I/O                 | P1[18] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                     |

| All information provided in this document is subject to legal disclaimers |        |             |               |               |             |             |            |             |     |                            | 0                   | <b>USB_UP_LED1</b> — It is LOW when the device is<br>configured (non-control endpoints enabled), or when the<br>host is enabled and has detected a device on the bus. It is<br>HIGH when the device is not configured, or when host is<br>enabled and has not detected a device on the bus, or<br>during global suspend. It transitions between LOW and<br>HIGH (flashes) when the host is enabled and detects<br>activity on the bus. |

| provic                                                                    |        |             |               |               |             |             |            |             |     |                            | 0                   | <b>PWM1[1]</b> — Pulse Width Modulator 1, channel 1 output.                                                                                                                                                                                                                                                                                                                                                                            |

| led in t                                                                  |        |             |               |               |             |             |            |             |     |                            | I                   | T1_CAP0 — Capture input for Timer 1, channel 0.                                                                                                                                                                                                                                                                                                                                                                                        |

| his doc                                                                   |        |             |               |               |             |             |            |             |     |                            | -                   | R — Function reserved.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ument                                                                     |        |             |               |               |             |             |            |             |     |                            | I/O                 | SSP1_MISO — Master In Slave Out for SSP1.                                                                                                                                                                                                                                                                                                                                                                                              |

| is subj                                                                   | P1[19] | 68          | U6            | P5            | 47          | 33          | 26         | J4          | [3] | I; PU                      | I/O                 | P1[19] — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                                                                                     |

| ect to legal                                                              |        |             |               |               |             |             |            |             |     |                            | 0                   | <b>USB_TX_E1</b> — Transmit Enable signal for USB port 1 (OTG transceiver).                                                                                                                                                                                                                                                                                                                                                            |

| disclair                                                                  |        |             |               |               |             |             |            |             |     |                            | 0                   | <b>USB_PPWR1</b> — Port Power enable signal for USB port 1.                                                                                                                                                                                                                                                                                                                                                                            |

| ners.                                                                     |        |             |               |               |             |             |            |             |     |                            | I                   | T1_CAP1 — Capture input for Timer 1, channel 1.                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                           |        |             |               |               |             |             |            |             |     |                            | 0                   | MC_0A — Motor control PWM channel 0, output A.                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                           |        |             |               |               |             |             |            |             |     |                            | I/O                 | SSP1_SCK — Serial clock for SSP1.                                                                                                                                                                                                                                                                                                                                                                                                      |

| © NXP                                                                     |        |             |               |               |             |             |            |             |     |                            | 0                   | <b>U2_OE</b> — RS-485/EIA-485 output enable signal for UART2.                                                                                                                                                                                                                                                                                                                                                                          |

32-bit ARM Cortex-M4 microcontroller

LPC408x/7x

32-bit ARM Cortex-M4 microcontroller LPC408x/7x

Table 3.

Pin description ...continued

Not all functions are available on all parts. See <a href="mailto:Table 2">Table 2</a> (Ethernet, USB, LCD, QEI, SD/MMC, comparator pins) and <a href="mailto:Table 5">Table 5</a> (EMC pins).

| Symbol   | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 | Pin LQFP100 | Pin LQFP80 | Pin TFBGA80 |                        | Reset state <u>[1]</u> | Type <sup>[2]</sup>                                                                                  | Description                                                                                                                      |  |

|----------|-------------|---------------|---------------|-------------|-------------|------------|-------------|------------------------|------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| P1[29]   | 92          | U14           | N10           | 64          | 45          | 36         | K8          | [3]                    | I; PU                  | I/O                                                                                                  | P1[29] — General purpose digital input/output pin.                                                                               |  |

|          |             |               |               |             |             |            |             |                        |                        | I/O                                                                                                  | <b>USB_SDA1</b> — USB port 1 I <sup>2</sup> C serial data (OTG transceiver).                                                     |  |

|          |             |               |               |             |             |            |             |                        |                        | I                                                                                                    | <b>PWM1_CAP1</b> — Capture input for PWM1, channel 1.                                                                            |  |

|          |             |               |               |             |             |            |             |                        |                        | 0                                                                                                    | T0_MAT1 — Match output for Timer 0, channel 1.                                                                                   |  |

| ≥<br>5   |             |               |               |             |             |            |             |                        |                        | 0                                                                                                    | MC_2B — Motor control PWM channel 2, output B.                                                                                   |  |

|          |             |               |               |             |             |            | 0           |                        | 0                      | <b>U4_TXD</b> — Transmitter output for USART4 (input/output in smart card mode).                     |                                                                                                                                  |  |

|          |             |               |               |             | 0           |            | 0           | LCD_VD[15] — LCD data. |                        |                                                                                                      |                                                                                                                                  |  |

|          |             |               |               |             |             |            |             |                        |                        | 0                                                                                                    | LCD_VD[23] — LCD data.                                                                                                           |  |

| P1[30]   | 42          | P2            | K3            | 30          | 21          | 18         | J2          | [5]                    | I; PU                  | I/O                                                                                                  | P1[30] — General purpose digital input/output pin.                                                                               |  |

|          |             |               |               |             |             |            |             |                        |                        | I                                                                                                    | <b>USB_PWRD2</b> — Power Status for USB port 2.                                                                                  |  |

|          |             |               |               |             |             |            |             |                        |                        | I                                                                                                    | <b>USB_VBUS</b> — Monitors the presence of USB bus power.                                                                        |  |

|          |             |               |               |             |             |            |             |                        |                        |                                                                                                      | This signal must be HIGH for USB reset to occur.                                                                                 |  |

| P1[30]   |             |               |               |             |             |            |             |                        |                        | I                                                                                                    | <b>ADC0_IN[4]</b> — A/D converter 0, input 4. When configured as an ADC input, the digital function of the pin must be disabled. |  |

|          |             |               |               |             |             |            |             |                        |                        | I/O                                                                                                  | <b>I2C0_SDA</b> — I <sup>2</sup> C0 data input/output (this pin does not use a specialized I2C pad.                              |  |

|          |             |               |               |             |             |            |             |                        |                        | 0                                                                                                    | <b>U3_OE</b> — RS-485/EIA-485 output enable signal for UART3.                                                                    |  |

| § P1[31] | 40          | P1            | K2            | 28          | 20          | 17         | H2          | [5]                    | I; PU                  | I/O                                                                                                  | P1[31] — General purpose digital input/output pin.                                                                               |  |

|          |             |               |               |             |             |            |             |                        |                        | I                                                                                                    | <b>USB_OVRCR2</b> — Over-Current status for USB port 2.                                                                          |  |

|          |             |               |               |             |             |            |             |                        |                        | I/O                                                                                                  | SSP1_SCK — Serial Clock for SSP1.                                                                                                |  |

| P1[31]   |             |               |               |             |             |            |             |                        |                        | I                                                                                                    | <b>ADC0_IN[5]</b> — A/D converter 0, input 5. When configured as an ADC input, the digital function of the pin must be disabled. |  |

|          |             |               |               |             |             |            |             |                        | I/O                    | <b>I2C0_SCL</b> — I <sup>2</sup> C0 clock input/output (this pin does not use a specialized I2C pad. |                                                                                                                                  |  |

LPC408X Product data sheet

Rev. 3

— 11 January 2017

32-bit ARM Cortex-M4 microcontroller LPC408x/7x

## Pin description ... continued

Table 3.

Pin description ...continued

Image: Not all functions are available on all parts. See <u>Table 2</u> (Ethernet, USB, LCD, QEI, SD/MMC, comparator pins) and <u>Table 5</u> (EMC pins).

| Symbol                                         | Pin LQFP208 | Ball TFBGA208 | Ball TFBGA180 | Pin LQFP144 | Pin LQFP100 | Pin LQFP80 | Pin TFBGA80 |     | Reset state[1] | Type <sup>[2]</sup> | Description                                         |

|------------------------------------------------|-------------|---------------|---------------|-------------|-------------|------------|-------------|-----|----------------|---------------------|-----------------------------------------------------|

| P3[9]                                          | 199         | C5            | A4            | -           | -           | -          | -           | [3] | I; PU          | I/O                 | P3[9] — General purpose digital input/output pin.   |

|                                                |             |               |               |             |             |            |             |     |                | I/O                 | <b>EMC_D[9]</b> — External memory data line 9.      |

| P3[10]                                         | 205         | B2            | B3            | -           | -           | -          | -           | [3] | I; PU          | I/O                 | P3[10] — General purpose digital input/output pin.  |

|                                                |             |               |               |             |             |            |             |     |                | I/O                 | EMC_D[10] — External memory data line 10.           |

| P3[11]                                         | 208         | D5            | B2            | -           | -           | -          | -           | [3] | I; PU          | I/O                 | P3[11] — General purpose digital input/output pin.  |

|                                                |             |               |               |             |             |            |             |     |                | I/O                 | <b>EMC_D[11]</b> — External memory data line 11.    |

| P3[12]<br>P3[13]<br>P3[14]<br>P3[15]<br>P3[16] | 1           | D4            | A1            | -           | -           | -          | -           | [3] | I; PU          | I/O                 | P3[12] — General purpose digital input/output pin.  |

| _                                              |             |               |               |             |             |            |             |     |                | I/O                 | <b>EMC_D[12]</b> — External memory data line 12.    |

| P3[13]                                         | 7           | C1            | C1            | -           | -           | -          | -           | [3] | I; PU          | I/O                 | P3[13] — General purpose digital input/output pin.  |

|                                                |             |               |               |             |             |            |             |     |                | I/O                 | EMC_D[13] — External memory data line 13.           |

| P3[14]                                         | 21          | H2            | F1            | -           | -           | -          | -           | [3] | I; PU          | I/O                 | P3[14] — General purpose digital input/output pin.  |

|                                                |             |               |               |             |             |            |             |     |                | I/O                 | EMC_D[14] — External memory data line 14.           |

| P3[15]                                         | 28          | M1            | G4            | -           | -           | -          | -           | [3] | I; PU          | I/O                 | P3[15] — General purpose digital input/output pin.  |

|                                                |             |               |               |             |             |            |             |     |                | I/O                 | EMC_D[15] — External memory data line 15.           |

| P3[16]                                         | 137         | F17           | -             | -           | -           | -          | -           | [3] | I; PU          | I/O                 | P3[16] — General purpose digital input/output pin.  |

|                                                |             |               |               |             |             |            |             |     |                | I/O                 | EMC_D[16] — External memory data line 16.           |

|                                                |             |               |               |             |             |            |             |     |                | 0                   | <b>PWM0[1]</b> — Pulse Width Modulator 0, output 1. |

|                                                |             |               |               |             |             |            |             |     |                | 0                   | U1_TXD — Transmitter output for UART1.              |

| P3[17]                                         | 143         | F15           | -             | -           | -           | -          | -           | [3] | I; PU          | I/O                 | P3[17] — General purpose digital input/output pin.  |

|                                                |             |               |               |             |             |            |             |     |                | I/O                 | EMC_D[17] — External memory data line 17.           |

| -                                              |             |               |               |             |             |            |             |     |                | 0                   | PWM0[2] — Pulse Width Modulator 0, output 2.        |

|                                                |             |               |               |             |             |            |             |     |                | I                   | U1_RXD — Receiver input for UART1.                  |

| P3[18]                                         | 151         | C15           | -             | -           | -           | -          | -           | [3] | I; PU          | I/O                 | P3[18] — General purpose digital input/output pin.  |

|                                                |             |               |               |             |             |            |             |     |                | I/O                 | EMC_D[18] — External memory data line 18.           |

|                                                |             |               |               |             |             |            |             |     |                | 0                   | PWM0[3] — Pulse Width Modulator 0, output 3.        |

|                                                |             |               |               |             |             |            |             |     |                | I                   | U1_CTS — Clear to Send input for UART1.             |

— 11 January 2017

Rev. 3

40 of 140

Product data sheet

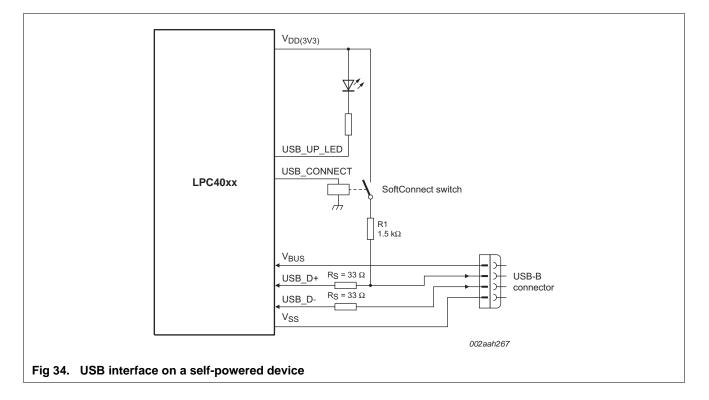

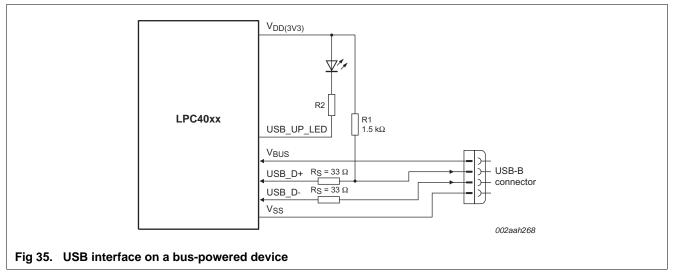

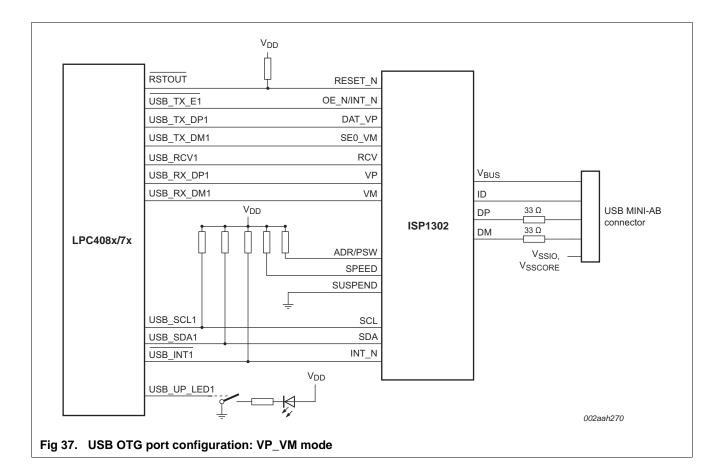

# 7.16 USB interface

Remark: The USB Device/Host/OTG controller is available on parts LPC4088/78/76. The USB Device-only controller is available on part LPC4074/72.

The Universal Serial Bus (USB) is a 4-wire bus that supports communication between a host and one or more (up to 127) peripherals. The host controller allocates the USB bandwidth to attached devices through a token-based protocol. The bus supports hot plugging and dynamic configuration of the devices. All transactions are initiated by the host controller.

See Section 13.1 for details on typical USB interfacing solutions.

#### 7.16.1 **USB** device controller

The device controller enables 12 Mbit/s data exchange with a USB host controller. It consists of a register interface, serial interface engine, endpoint buffer memory, and a DMA controller. The serial interface engine decodes the USB data stream and writes data to the appropriate endpoint buffer. The status of a completed USB transfer or error condition is indicated via status registers. An interrupt is also generated if enabled. When enabled, the DMA controller transfers data between the endpoint buffer and the USB RAM.

# 7.16.1.1 Features

- Fully compliant with USB 2.0 Specification (full speed).

- Supports 32 physical (16 logical) endpoints with a 4 kB endpoint buffer RAM.

- Supports Control, Bulk, Interrupt and Isochronous endpoints.

- Scalable realization of endpoints at run time.

- Endpoint Maximum packet size selection (up to USB maximum specification) by software at run time.

- Supports SoftConnect and GoodLink features.

- While USB is in the Suspend mode, the LPC408x/7x can enter one of the reduced power modes and wake up on USB activity.

- Supports DMA transfers with all on-chip SRAM blocks on all non-control endpoints.

- Allows dynamic switching between CPU-controlled and DMA modes.

- Double buffer implementation for Bulk and Isochronous endpoints.

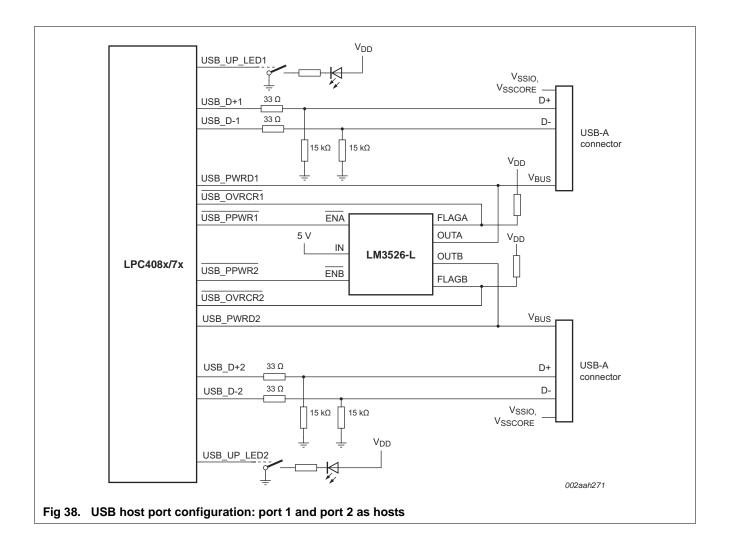

# 7.16.2 USB host controller

The host controller enables full- and low-speed data exchange with USB devices attached to the bus. It consists of register interface, serial interface engine and DMA controller. The register interface complies with the Open Host Controller Interface (OHCI) specification.

#### 7.16.2.1 Features

- OHCI compliant.

- Two downstream ports.

- Supports per-port power switching.

# 7.36.3 Wake-up timer

The LPC408x/7x begin operation at power-up and when awakened from Power-down mode by using the 12 MHz IRC oscillator as the clock source. This allows chip operation to resume quickly. If the main oscillator or the PLL is needed by the application, software will need to enable these features and wait for them to stabilize before they are used as a clock source.

When the main oscillator is initially activated, the wake-up timer allows software to ensure that the main oscillator is fully functional before the processor uses it as a clock source and starts to execute instructions. This is important at power on, all types of reset, and whenever any of the aforementioned functions are turned off for any reason. Since the oscillator and other functions are turned off during Power-down mode, any wake-up of the processor from Power-down mode makes use of the wake-up Timer.

The wake-up timer monitors the crystal oscillator to check whether it is safe to begin code execution. When power is applied to the chip, or when some event caused the chip to exit Power-down mode, some time is required for the oscillator to produce a signal of sufficient amplitude to drive the clock logic. The amount of time depends on many factors, including the rate of  $V_{DD(3V3)}$  ramp (in the case of power on), the type of crystal and its electrical characteristics (if a quartz crystal is used), as well as any other external circuitry (e.g., capacitors), and the characteristics of the oscillator itself under the existing ambient conditions.

# 7.36.4 Power control

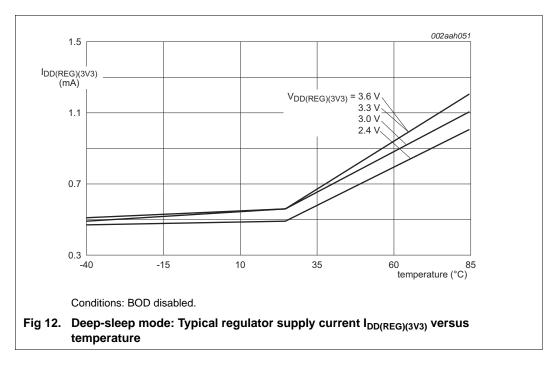

The LPC408x/7x support a variety of power control features. There are four special modes of processor power reduction: Sleep mode, Deep-sleep mode, Power-down mode, and Deep power-down mode. The CPU clock rate may also be controlled as needed by changing clock sources, reconfiguring PLL values, and/or altering the CPU clock divider value. This allows a trade-off of power versus processing speed based on application requirements. In addition, the peripheral power control allows shutting down the clocks to individual on-chip peripherals, allowing fine tuning of power consumption by eliminating all dynamic power use in any peripherals that are not required for the application. Each of the peripherals has its own clock divider which provides even better power control.

The integrated PMU (Power Management Unit) automatically adjusts internal regulators to minimize power consumption during Sleep, Deep-sleep, Power-down, and Deep power-down modes.

The LPC408x/7x also implement a separate power domain to allow turning off power to the bulk of the device while maintaining operation of the RTC and a small set of registers for storing data during any of the power-down modes.

## 7.36.4.1 Sleep mode

When Sleep mode is entered, the clock to the core is stopped. Resumption from the Sleep mode does not need any special sequence other than re-enabling the clock to the ARM core.

In Sleep mode, execution of instructions is suspended until either a Reset or interrupt occurs. Peripheral functions continue operation during Sleep mode and may generate interrupts to cause the processor to resume execution. Sleep mode eliminates dynamic power used by the processor itself, memory systems and related controllers, and internal buses.

## 7.36.4.4 Deep power-down mode

The Deep power-down mode can only be entered from the RTC block. In Deep power-down mode, power is shut off to the entire chip with the exception of the RTC module and the RESET pin.

To optimize power conservation, the user has the additional option of turning off or retaining power to the 32 kHz oscillator. It is also possible to use external circuitry to turn off power to the on-chip regulator via the  $V_{DD(REG)(3V3)}$  pins and/or the I/O power via the  $V_{DD(3V3)}$  pins after entering Deep Power-down mode. Power must be restored before device operation can be restarted.

The LPC408x/7x can wake up from Deep power-down mode via the  $\overline{\text{RESET}}$  pin or an alarm match event of the RTC.

## 7.36.4.5 Wake-up Interrupt Controller (WIC)

The WIC allows the CPU to automatically wake up from any enabled priority interrupt that can occur while the clocks are stopped in Deep-sleep, Power-down, and Deep power-down modes.

The WIC works in connection with the Nested Vectored Interrupt Controller (NVIC). When the CPU enters Deep-sleep, Power-down, or Deep power-down mode, the NVIC sends a mask of the current interrupt situation to the WIC. This mask includes all of the interrupts that are both enabled and of sufficient priority to be serviced immediately. With this information, the WIC simply notices when one of the interrupts has occurred and then it wakes up the CPU.

The WIC eliminates the need to periodically wake up the CPU and poll the interrupts resulting in additional power savings.

## 7.36.5 Peripheral power control

A power control for peripherals feature allows individual peripherals to be turned off if they are not needed in the application, resulting in additional power savings.

## 7.36.6 Power domains

The LPC408x/7x provide two independent power domains that allow the bulk of the device to have power removed while maintaining operation of the RTC and the backup registers.

On the LPC408x/7x, I/O pads are powered by  $V_{DD(3V3)}$ , while  $V_{DD(REG)(3V3)}$  powers the on-chip voltage regulator which in turn provides power to the CPU and most of the peripherals.

Depending on the LPC408x/7x application, a design can use two power options to manage power consumption.

The first option assumes that power consumption is not a concern and the design ties the  $V_{DD(3V3)}$  and  $V_{DD(REG)(3V3)}$  pins together. This approach requires only one 3.3 V power supply for both pads, the CPU, and peripherals. While this solution is simple, it does not support powering down the I/O pad ring "on the fly" while keeping the CPU and peripherals alive.

LPC408X 7X

## 32-bit ARM Cortex-M4 microcontroller

| Symbol                | Parameter                                                    | Conditions                       |      | Min  | Typ <u>[1]</u> | Max  | Unit |

|-----------------------|--------------------------------------------------------------|----------------------------------|------|------|----------------|------|------|

| V <sub>CM</sub>       | differential common<br>mode voltage range                    | includes V <sub>DI</sub> range   |      | 0.8  | -              | 2.5  | V    |

| V <sub>th(rs)se</sub> | single-ended receiver<br>switching threshold<br>voltage      |                                  | [20] | 0.8  | -              | 2.0  | V    |

| V <sub>OL</sub>       | LOW-level output<br>voltage for<br>low-/full-speed           | $R_L$ of 1.5 k $\Omega$ to 3.6 V | [20] | -    | -              | 0.18 | V    |

| V <sub>OH</sub>       | HIGH-level output<br>voltage (driven) for<br>low-/full-speed | $R_L$ of 15 k $\Omega$ to GND    | [20] | 2.8  | -              | 3.5  | V    |

| C <sub>trans</sub>    | transceiver capacitance                                      | pin to GND                       | [20] | -    | -              | 20   | pF   |

| Oscillator pi         | ns (see <u>Section 13.2</u> )                                | +                                |      |      | ŧ              | ŧ    |      |

| V <sub>i(XTAL1)</sub> | input voltage on pin<br>XTAL1                                |                                  |      | -0.5 | 1.8            | 1.95 | V    |

| V <sub>o(XTAL2)</sub> | output voltage on pin<br>XTAL2                               |                                  |      | -0.5 | 1.8            | 1.95 | V    |

| V <sub>i(RTCX1)</sub> | input voltage on pin<br>RTCX1                                |                                  |      | -0.5 | -              | 3.6  | V    |

| V <sub>o(RTCX2)</sub> | output voltage on pin<br>RTCX2                               |                                  |      | -0.5 | -              | 3.6  | V    |

#### **Table 11.** Static characteristics ... continued $T_{amb} = -40$ °C to +85 °C, unless otherwise specified.

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2] For USB operation 3.0 V  $\leq$  V<sub>DD((3V3)</sub>  $\leq$  3.6 V. Guaranteed by design.

- [3]  $V_{DDA}$  and VREFP should be tied to  $V_{DD(3V3)}$  if the ADC and DAC are not used.

- [4] The RTC typically fails when  $V_{i(VBAT)}$  drops below 1.6 V.

- [5]  $V_{DD(REG)(3V3)} = 3.3 \text{ V}$ ;  $T_{amb} = 25 \text{ °C}$  for all power consumption measurements.

- [6] Boost control bits in the PBOOST register set to 0x0 (see LPC408x/7x User manual).

- [7] Boost control bits in the PBOOST register set to 0x3 (see LPC408x/7x User manual).

- [8] IRC running at 12 MHz; main oscillator and PLL disabled; PCLK = CCLK/4.

- [9] BOD disabled.

- [10] On pin VBAT;  $V_{DD(REG)(3V3)} = V_{DD(3V3)} = V_{DDA} = 0$ ;  $T_{amb} = 25 \text{ °C}$ .

- [11] On pin VBAT;  $V_{DD(REG)(3V3)} = V_{DD(3V3)} = V_{DDA} = 3.3 \text{ V}$ ;  $T_{amb} = 25 \text{ °C}$ .

- [12] All internal pull-ups disabled. All pins configured as output and driven LOW. V<sub>DD(3V3)</sub> = 3.3 V; T<sub>amb</sub> = 25 °C.

- [13]  $V_{DDA} = 3.3 \text{ V}; T_{amb} = 25 \text{ °C}.$

- [14]  $V_{i(VREFP)} = 3.3 \text{ V}; T_{amb} = 25 \text{ °C}.$

- [15] Including voltage on outputs in 3-state mode.

- [16]  $V_{DD(3V3)}$  supply voltages must be present.

- [17] 3-state outputs go into 3-state mode in Deep power-down mode.

- [18] Allowed as long as the current limit does not exceed the maximum current allowed by the device.

- [19] To  $V_{\text{SS}}.$

- $\label{eq:20} \mbox{[20]} \ \ 3.0 \ \mbox{V} \leq \mbox{V}_{DD(3V3)} \leq 3.6 \ \mbox{V}.$

Product data sheet

© NXP Semiconductors N.V. 2017. All rights reserved.

# 32-bit ARM Cortex-M4 microcontroller

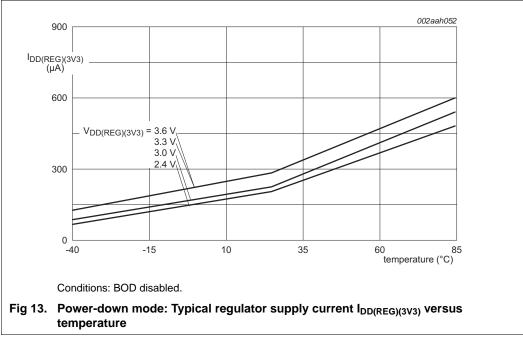

# **10.1** Power consumption

# 32-bit ARM Cortex-M4 microcontroller

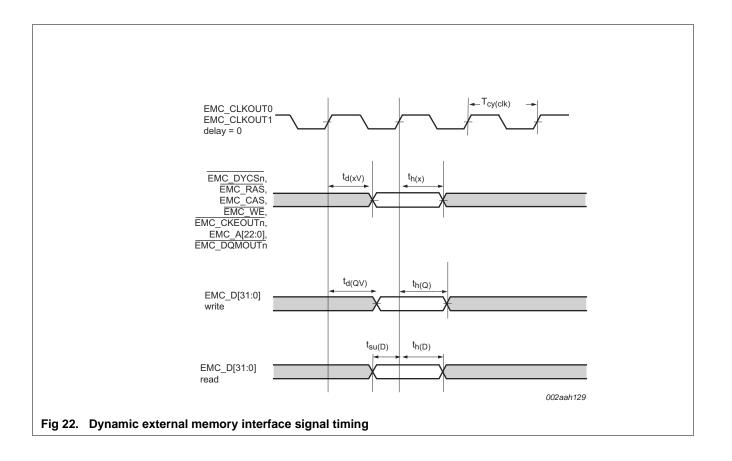

**Table 17. Dynamic characteristics: Dynamic external memory interface, read strategy bits (RD bits) = 01** ...continued  $C_L = 30 \text{ pF}$ ,  $T_{amb} = -40 \degree \text{C}$  to 85  $\degree \text{C}$ ,  $V_{DD(3V3)} = 3.0 \text{ V}$  to 3.6 V. Values guaranteed by design.  $t_{cmddly}$  is programmable delay value for EMC command outputs in command delayed mode;  $t_{fbdly}$  is programmable delay value for the feedback clock that controls input data sampling;  $t_{clk0dly}$  is programmable delay value for the EMC\_CLKOUT0 output;  $t_{clk1dly}$  is programmable delay value for the EMC\_CLKOUT1 output.

| Symbol               | Parameter                              | Min                       | Тур                       | Max                        | Unit |

|----------------------|----------------------------------------|---------------------------|---------------------------|----------------------------|------|

| t <sub>d(RASV)</sub> | row address strobe valid delay time    | -                         | t <sub>cmddly</sub> + 6.8 | t <sub>cmddly</sub> + 10.4 | ns   |

| t <sub>h(RAS)</sub>  | row address strobe hold time           | t <sub>cmddly</sub> + 2.3 | t <sub>cmddly</sub> + 4.3 | -                          | ns   |

| t <sub>d(CASV)</sub> | column address strobe valid delay time | -                         | t <sub>cmddly</sub> + 6.7 | t <sub>cmddly</sub> + 10.2 | ns   |

| t <sub>h(CAS)</sub>  | column address strobe hold time        | t <sub>cmddly</sub> + 2.2 | t <sub>cmddly</sub> + 4.1 | -                          | ns   |

| t <sub>d(WV)</sub>   | write valid delay time                 | -                         | t <sub>cmddly</sub> + 7.1 | t <sub>cmddly</sub> + 10.9 | ns   |

| t <sub>h(W)</sub>    | write hold time                        | t <sub>cmddly</sub> + 1.5 | t <sub>cmddly</sub> + 2.7 | -                          | ns   |

| t <sub>d(AV)</sub>   | address valid delay time               | -                         | t <sub>cmddly</sub> + 7.7 | t <sub>cmddly</sub> + 11.9 | ns   |

| t <sub>h(A)</sub>    | address hold time                      | t <sub>cmddly</sub> + 1.0 | t <sub>cmddly</sub> + 1.8 | -                          | ns   |

| Read cycle           | parameters                             |                           |                           |                            |      |

| t <sub>su(D)</sub>   | data input set-up time                 | 5.6 - t <sub>fbdly</sub>  | 4.5 - t <sub>fbdly</sub>  | -                          | ns   |

| t <sub>h(D)</sub>    | data input hold time                   | $-2.2 + t_{fbdly}$        | -2.9 + $t_{fbdly}$        | -                          | ns   |

| Write cycle          | parameters                             |                           |                           |                            |      |

| t <sub>d(QV)</sub>   | data output valid delay time           | -                         | t <sub>cmddly</sub> + 8.7 | t <sub>cmddly</sub> + 13.1 | ns   |

| t <sub>h(Q)</sub>    | data output hold time                  | t <sub>cmddly</sub> + 1.0 | t <sub>cmddly</sub> + 2.0 | -                          | ns   |

[1] Refers to SDRAM clock signal EMC\_CLKOUTn where n = 0 and 1.

LPC408X\_7X

# LPC408x/7x

# 32-bit ARM Cortex-M4 microcontroller

# Table 18. Dynamic characteristics: Dynamic external memory interface programmable clock delays (CMDDLY, FBCLKDLY, CLKOUT0DLY and CLKOUT1DLY)

$T_{amb} = -40 \,^{\circ}$ C to 85  $^{\circ}$ C,  $V_{DD(3V3)} = 3.0 \,$ V to 3.6 V.Values guaranteed by design.  $t_{cmddly}$  is programmable delay value for EMC command outputs in command delayed mode;  $t_{fbdly}$  is programmable delay value for the feedback clock that controls input data sampling;  $t_{clk0dly}$  is programmable delay value for the EMC\_CLKOUT0 output;  $t_{clk1dly}$  is programmable delay value for the EMC\_CLKOUT1 output.

| Symbols                                                                                | Parameter  | Five bit value for each delay in EMCDLYCTL <sup>[1]</sup> | Min | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------|------------|-----------------------------------------------------------|-----|-----|------|------|

| t <sub>cmddly</sub> , t <sub>fbdly</sub> , t <sub>clk0dly</sub> , t <sub>clk1dly</sub> | delay time | b00000                                                    | 0.0 | 0.0 | 0.0  | ns   |

|                                                                                        |            | b00001                                                    | 0.1 | 0.1 | 0.2  | ns   |

|                                                                                        |            | b00010                                                    | 0.2 | 0.3 | 0.5  | ns   |

|                                                                                        |            | b00011                                                    | 0.3 | 0.4 | 0.7  | ns   |

|                                                                                        |            | b00100                                                    | 0.5 | 0.8 | 1.3  | ns   |

|                                                                                        |            | b00101                                                    | 0.6 | 0.9 | 1.5  | ns   |

|                                                                                        |            | b00110                                                    | 0.7 | 1.1 | 1.8  | ns   |

|                                                                                        |            | b00111                                                    | 0.8 | 1.2 | 2.0  | ns   |

|                                                                                        |            | b01000                                                    | 1.2 | 1.8 | 2.9  | ns   |

|                                                                                        |            | b01001                                                    | 1.3 | 1.9 | 3.1  | ns   |

|                                                                                        |            | b01010                                                    | 1.4 | 2.0 | 3.4  | ns   |

|                                                                                        |            | b01011                                                    | 1.5 | 2.1 | 3.6  | ns   |

|                                                                                        |            | b01100                                                    | 1.7 | 2.6 | 4.2  | ns   |

|                                                                                        |            | b01101                                                    | 1.8 | 2.7 | 4.4  | ns   |

|                                                                                        |            | b01110                                                    | 1.9 | 2.9 | 4.7  | ns   |

|                                                                                        |            | b01111                                                    | 2.0 | 3.0 | 4.9  | ns   |

|                                                                                        |            | b10000                                                    | 2.4 | 3.7 | 6.0  | ns   |

|                                                                                        |            | b10001                                                    | 2.5 | 3.8 | 6.2  | ns   |

|                                                                                        |            | b10010                                                    | 2.6 | 4.0 | 6.5  | ns   |

|                                                                                        |            | b10011                                                    | 2.7 | 4.1 | 6.7  | ns   |

|                                                                                        |            | b10100                                                    | 2.9 | 4.5 | 7.3  | ns   |

|                                                                                        |            | b10101                                                    | 3.0 | 4.6 | 7.5  | ns   |

|                                                                                        |            | b10110                                                    | 3.1 | 4.8 | 7.8  | ns   |

|                                                                                        |            | b10111                                                    | 3.2 | 4.9 | 8.0  | ns   |

|                                                                                        |            | b11000                                                    | 3.6 | 5.4 | 8.9  | ns   |

|                                                                                        |            | b11001                                                    | 3.7 | 5.5 | 9.1  | ns   |

|                                                                                        |            | b11010                                                    | 3.8 | 5.7 | 9.4  | ns   |

|                                                                                        |            | b11011                                                    | 3.9 | 5.8 | 9.6  | ns   |

|                                                                                        |            | b11100                                                    | 4.1 | 6.2 | 10.2 | ns   |

|                                                                                        |            | b11101                                                    | 4.2 | 6.3 | 10.4 | ns   |

|                                                                                        |            | b11110                                                    | 4.3 | 6.6 | 10.7 | ns   |

|                                                                                        |            | b11111                                                    | 4.4 | 6.7 | 10.9 | ns   |

[1] The programmable delay blocks are controlled by the EMCDLYCTL register in the EMC register block. All delay times are incremental delays for each element starting from delay block 0. See the *LPC408x/7x user manual* for details.

# LPC408x/7x

# 32-bit ARM Cortex-M4 microcontroller

# LPC408x/7x

# 32-bit ARM Cortex-M4 microcontroller

LPC408X\_7X

# 32-bit ARM Cortex-M4 microcontroller

LPC408X\_7X

## 32-bit ARM Cortex-M4 microcontroller

**NXP Semiconductors**

# 19. Legal information

# 19.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

# 19.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

# 19.3 Disclaimers