Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 21                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 13x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-WFQFN Exposed Pad                                           |

| Supplier Device Package    | 24-QFN (4x4)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f316-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F310/1/2/3/4/5/6/7

| 18.2.3.High-Speed Output Mode                  | 208 |

|------------------------------------------------|-----|

| 18.2.4. Frequency Output Mode                  | 209 |

| 18.2.5.8-Bit Pulse Width Modulator Mode        |     |

| 18.2.6.16-Bit Pulse Width Modulator Mode       | 211 |

| 18.3.Watchdog Timer Mode                       | 212 |

| 18.3.1.Watchdog Timer Operation                |     |

| 18.3.2.Watchdog Timer Usage                    | 213 |

| 18.4.Register Descriptions for PCA             |     |

| 19. Revision Specific Behavior                 |     |

| 19.1.Revision Identification                   |     |

| 19.2.Reset Behavior                            | 221 |

| 19.2.1.Weak Pullups on GPI <u>O P</u> ins      | 221 |

| 19.2.2.V <sub>DD</sub> Monitor and the RST Pin |     |

| 19.3.PCA Counter                               |     |

| 20. C2 Interface                               |     |

| 20.1.C2 Interface Registers                    |     |

| -                                              | 225 |

| -                                              | 226 |

|                                                | 228 |

|                                                |     |

# List of Figures

| 1. | System Overview                                                           |    |

|----|---------------------------------------------------------------------------|----|

|    | Figure 1.1. C8051F310 Block Diagram                                       | 19 |

|    | Figure 1.2. C8051F311 Block Diagram                                       | 20 |

|    | Figure 1.3. C8051F312 Block Diagram                                       | 21 |

|    | Figure 1.4. C8051F313 Block Diagram                                       | 22 |

|    | Figure 1.5. C8051F314 Block Diagram                                       | 23 |

|    | Figure 1.6. C8051F315 Block Diagram                                       |    |

|    | Figure 1.7. C8051F316 Block Diagram                                       | 25 |

|    | Figure 1.8. C8051F317 Block Diagram                                       | 26 |

|    | Figure 1.9. Comparison of Peak MCU Execution Speeds                       |    |

|    | Figure 1.10. On-Chip Clock and Reset                                      |    |

|    | Figure 1.11. On-Board Memory Map                                          | 29 |

|    | Figure 1.12. Development/In-System Debug Diagram                          |    |

|    | Figure 1.13. Digital Crossbar Diagram                                     |    |

|    | Figure 1.14. PCA Block Diagram                                            |    |

|    | Figure 1.15. 10-Bit ADC Block Diagram                                     |    |

|    | Figure 1.16. Comparator0 Block Diagram                                    |    |

| 2. | Absolute Maximum Ratings                                                  |    |

| 3. | Global DC Electrical Characteristics                                      |    |

| 4. | Pinout and Package Definitions                                            |    |

|    | Figure 4.1. LQFP-32 Pinout Diagram (Top View)                             | 41 |

|    | Figure 4.2. LQFP-32 Package Diagram                                       | 42 |

|    | Figure 4.3. QFN-28 Pinout Diagram (Top View)                              | 43 |

|    | Figure 4.4. QFN-28 Package Drawing                                        | 44 |

|    | Figure 4.5. Typical QFN-28 Landing Diagram                                | 45 |

|    | Figure 4.6. QFN-28 Solder Paste Recommendation                            | 46 |

|    | Figure 4.7. QFN-24 Pinout Diagram (Top View)                              | 47 |

|    | Figure 4.8. QFN-24 Package Drawing                                        | 48 |

|    | Figure 4.9. Typical QFN-24 Landing Diagram                                | 49 |

|    | Figure 4.10. QFN-24 Solder Paste Recommendation                           | 50 |

| 5. | 10-Bit ADC (ADC0, C8051F310/1/2/3/6 only)                                 |    |

|    | Figure 5.1. ADC0 Functional Block Diagram                                 |    |

|    | Figure 5.2. Typical Temperature Sensor Transfer Function                  |    |

|    | Figure 5.3. Temperature Sensor Error with 1-Point Calibration             |    |

|    | Figure 5.4. 10-Bit ADC Track and Conversion Example Timing                |    |

|    | Figure 5.5. ADC0 Equivalent Input Circuits                                |    |

|    | Figure 5.6. ADC Window Compare Example: Right-Justified Single-Ended Data |    |

|    | Figure 5.7. ADC Window Compare Example: Left-Justified Single-Ended Data  |    |

|    | Figure 5.8. ADC Window Compare Example: Right-Justified Differential Data |    |

|    | Figure 5.9. ADC Window Compare Example: Left-Justified Differential Data  | 64 |

| 6. | Voltage Reference (C8051F310/1/2/3/6 only)                                |    |

|    | Figure 6.1. Voltage Reference Functional Block Diagram                    | 67 |

# 4. Pinout and Package Definitions

|                 | Pin Numbers |           |         |                                                                                                                                        |                                                                                                                                                                                                         |

|-----------------|-------------|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name            | 'F310/2/4   | 'F311/3/5 | 'F316/7 | Туре                                                                                                                                   | Description                                                                                                                                                                                             |

| V <sub>DD</sub> | 4           | 4         | 4       |                                                                                                                                        | Power Supply Voltage.                                                                                                                                                                                   |

| GND             | 3           | 3         | 3       |                                                                                                                                        | Ground.                                                                                                                                                                                                 |

| RST/            | 5           | 5         | 5       | D I/O Device Reset. Open-drain output of internal PC external source can initiate a system reset by o this pin low for at least 10 µs. |                                                                                                                                                                                                         |

| C2CK            |             |           |         | D I/O                                                                                                                                  | Clock signal for the C2 Debug Interface.                                                                                                                                                                |

| P3.0/           |             |           |         | D I/O                                                                                                                                  | Port 3.0. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| C2D             | 6           | 6         | 6       | D I/O                                                                                                                                  | Bi-directional data signal for the C2 Debug Interface.                                                                                                                                                  |

| P0.0/           |             |           |         | D I/O                                                                                                                                  | Port 0.0. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| VREF            | 2           | 2         | 2       | A In                                                                                                                                   | External VREF input. ('F310/1/2/3 only)                                                                                                                                                                 |

| P0.1            | 1           | 1         | 1       | D I/O                                                                                                                                  | Port 0.1. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| P0.2/           |             |           |         | D I/O                                                                                                                                  | Port 0.2. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| XTAL1           | 32          | 28        | 24      | A In                                                                                                                                   | External Clock Input. This pin is the external oscillator return for a crystal or resonator.                                                                                                            |

| P0.3/           |             |           |         | D I/O                                                                                                                                  | Port 0.3. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| XTAL2           | 31          | 27        | 23      | A Out or<br>D In                                                                                                                       | External Clock Output. For an external crystal or reso-<br>nator, this pin is the excitation driver. This pin is the<br>external clock input for CMOS, capacitor, or RC oscil-<br>lator configurations. |

| P0.4            | 30          | 26        | 22      | D I/O                                                                                                                                  | Port 0.4. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| P0.5            | 29          | 25        | 21      | D I/O                                                                                                                                  | Port 0.5. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| P0.6/<br>CNVSTR | 28          | 24        | 20      |                                                                                                                                        | Port 0.6. See <b>Section 13</b> for a complete description.<br>ADC0 External Convert Start Input. ('F310/1/2/3 only)                                                                                    |

| P0.7            | 27          | 23        | 19      | D I/O                                                                                                                                  | Port 0.7. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| P1.0            | 26          | 22        | 18      | D I/O or<br>A In                                                                                                                       | Port 1.0. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| P1.1            | 25          | 21        | 17      | D I/O or<br>A In                                                                                                                       | Port 1.1. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| P1.2            | 24          | 20        | 16      | D I/O or<br>A In                                                                                                                       | Port 1.2. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| P1.3            | 23          | 19        | 15      | D I/O or<br>A In                                                                                                                       | Port 1.3. See <b>Section 13</b> for a complete description.                                                                                                                                             |

| P1.4            | 22          | 18        | 14      | D I/O or<br>A In                                                                                                                       | Port 1.4. See <b>Section 13</b> for a complete description.                                                                                                                                             |

### Table 4.1. Pin Definitions for the C8051F31x

| Name | Pin Numbers |           | Turne   | Description      |                                                             |

|------|-------------|-----------|---------|------------------|-------------------------------------------------------------|

| Name | 'F310/2/4   | 'F311/3/5 | 'F316/7 | Туре             | Description                                                 |

| P1.5 | 21          | 17        | 13      | D I/O or<br>A In | Port 1.5. See <b>Section 13</b> for a complete description. |

| P1.6 | 20          | 16        |         | D I/O or<br>A In | Port 1.6. See <b>Section 13</b> for a complete description. |

| P1.7 | 19          | 15        |         | D I/O or<br>A In | Port 1.7. See <b>Section 13</b> for a complete description. |

| P2.0 | 18          | 14        | 12      | D I/O or<br>A In | Port 2.0. See <b>Section 13</b> for a complete description. |

| P2.1 | 17          | 13        | 11      | D I/O or<br>A In | Port 2.1. See <b>Section 13</b> for a complete description. |

| P2.2 | 16          | 12        | 10      | D I/O or<br>A In | Port 2.2. See <b>Section 13</b> for a complete description. |

| P2.3 | 15          | 11        | 9       | D I/O or<br>A In | Port 2.3. See <b>Section 13</b> for a complete description. |

| P2.4 | 14          | 10        | 8       | D I/O or<br>A In | Port 2.4. See <b>Section 13</b> for a complete description. |

| P2.5 | 13          | 9         | 7       | D I/O or<br>A In | Port 2.5. See <b>Section 13</b> for a complete description. |

| P2.6 | 12          | 8         |         | D I/O or<br>A In | Port 2.6. See <b>Section 13</b> for a complete description. |

| P2.7 | 11          | 7         |         | D I/O or<br>A In | Port 2.7. See <b>Section 13</b> for a complete description. |

| P3.1 | 7           |           |         | D I/O or<br>A In | Port 3.1. See <b>Section 13</b> for a complete description. |

| P3.2 | 8           |           |         | D I/O or<br>A In | Port 3.2. See <b>Section 13</b> for a complete description. |

| P3.3 | 9           |           |         | D I/O or<br>A In | Port 3.3. See <b>Section 13</b> for a complete description. |

| P3.4 | 10          |           |         | D I/O or<br>A In | Port 3.4. See <b>Section 13</b> for a complete description. |

Table 4.1. Pin Definitions for the C8051F31x (Continued)

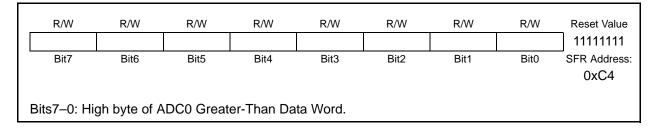

#### 5.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

#### SFR Definition 5.7. ADC0GTH: ADC0 Greater-Than Data High Byte

#### SFR Definition 5.8. ADC0GTL: ADC0 Greater-Than Data Low Byte

| R/W                                               | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |

|---------------------------------------------------|------|------|------|------|------|------|------|--------------|

|                                                   |      |      |      |      |      |      |      | 11111111     |

| Bit7                                              | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|                                                   |      |      |      |      |      |      |      | 0xC3         |

|                                                   |      |      |      |      |      |      |      |              |

| Bits7–0: Low byte of ADC0 Greater-Than Data Word. |      |      |      |      |      |      |      |              |

| R/W               | R/W                                                                                                                                                | R/W                                                                                           | R/W          | R/W     | R/W   | R/W   | R/W  | Reset Value  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------|---------|-------|-------|------|--------------|--|

|                   |                                                                                                                                                    |                                                                                               |              | REFSL   | TEMPE | BIASE |      | 00000000     |  |

| Bit7              | Bit6                                                                                                                                               | Bit5                                                                                          | Bit4         | Bit3    | Bit2  | Bit1  | Bit0 | SFR Address: |  |

|                   |                                                                                                                                                    |                                                                                               |              |         |       |       |      | 0xD1         |  |

| Bits7–4:<br>Bit3: | UNUSED. Read = 0000b; Write = don't care.<br>REFSL: Voltage Reference Select.<br>This bit selects the source for the internal voltage reference.   |                                                                                               |              |         |       |       |      |              |  |

|                   |                                                                                                                                                    | 0: VREF input pin used as voltage reference.<br>1: V <sub>DD</sub> used as voltage reference. |              |         |       |       |      |              |  |

| Bit2:             | TEMPE: Temperature Sensor Enable Bit.<br>0: Internal Temperature Sensor off.<br>1: Internal Temperature Sensor on.                                 |                                                                                               |              |         |       |       |      |              |  |

| Bit1:             | BIASE: Internal Analog Bias Generator Enable Bit. (Must be '1' if using ADC).<br>0: Internal Bias Generator off.<br>1: Internal Bias Generator on. |                                                                                               |              |         |       |       |      |              |  |

| Bit0:             | UNUSED. R                                                                                                                                          | ead = 0b. V                                                                                   | Vrite = don' | t care. |       |       |      |              |  |

### Table 6.1. External Voltage Reference Circuit Electrical Characteristics

$V_{DD}$  = 3.0 V; -40 to +85 °C unless otherwise specified

| Parameter           | Conditions                              | Min | Тур | Max             | Units |

|---------------------|-----------------------------------------|-----|-----|-----------------|-------|

| Input Voltage Range |                                         | 0   |     | V <sub>DD</sub> | V     |

| Input Current       | Sample Rate = 200 ksps;<br>VREF = 3.0 V |     | 12  |                 | μA    |

| Register       | Address          | Description                                        | Page |

|----------------|------------------|----------------------------------------------------|------|

| SFRs are liste | ed in alphabetic | al order. All undefined SFR locations are reserved |      |

| ACC            | 0xE0             | Accumulator                                        | 92   |

| ADC0CF         | 0xBC             | ADC0 Configuration                                 | 59   |

| ADC0CN         | 0xE8             | ADC0 Control                                       | 60   |

| ADC0GTH        | 0xC4             | ADC0 Greater-Than Compare High                     | 61   |

| ADC0GTL        | 0xC3             | ADC0 Greater-Than Compare Low                      | 61   |

| ADC0H          | 0xBE             | ADC0 High                                          | 59   |

| ADC0L          | 0xBD             | ADC0 Low                                           | 59   |

| ADC0LTH        | 0xC6             | ADC0 Less-Than Compare Word High                   | 62   |

| ADC0LTL        | 0xC5             | ADC0 Less-Than Compare Word Low                    | 62   |

| AMX0N          | 0xBA             | AMUX0 Negative Channel Select                      | 58   |

| AMX0P          | 0xBB             | AMUX0 Positive Channel Select                      | 57   |

| В              | 0xF0             | B Register                                         | 93   |

| CKCON          | 0x8E             | Clock Control                                      | 193  |

| CLKSEL         | 0xA9             | Clock Select                                       | 123  |

| CPT0CN         | 0x9B             | Comparator0 Control                                | 72   |

| CPT0MD         | 0x9D             | Comparator0 Mode Selection                         | 74   |

| CPT0MX         | 0x9F             | Comparator0 MUX Selection                          | 73   |

| CPT1CN         | 0x9A             | Comparator1 Control                                | 75   |

| CPT1MD         | 0x9C             | Comparator1 Mode Selection                         | 77   |

| CPT1MX         | 0x9E             | Comparator1 MUX Selection                          | 76   |

| DPH            | 0x83             | Data Pointer High                                  | 91   |

| DPL            | 0x82             | Data Pointer Low                                   | 90   |

| EIE1           | 0xE6             | Extended Interrupt Enable 1                        | 99   |

| EIP1           | 0xF6             | Extended Interrupt Priority 1                      | 100  |

| EMI0CN         | 0xAA             | External Memory Interface Control                  | 119  |

| FLKEY          | 0xB7             | Flash Lock and Key                                 | 117  |

| FLSCL          | 0xB6             | Flash Scale                                        | 117  |

| IE             | 0xA8             | Interrupt Enable                                   | 97   |

| IP             | 0xB8             | Interrupt Priority                                 | 98   |

| IT01CF         | 0xE4             | INT0/INT1 Configuration                            | 101  |

| OSCICL         | 0xB3             | Internal Oscillator Calibration                    | 122  |

| OSCICN         | 0xB2             | Internal Oscillator Control                        | 122  |

| OSCXCN         | 0xB1             | External Oscillator Control                        | 125  |

| P0             | 0x80             | Port 0 Latch                                       | 136  |

| POMDIN         | 0xF1             | Port 0 Input Mode Configuration                    | 136  |

| POMDOUT        | 0xA4             | Port 0 Output Mode Configuration                   | 137  |

| POSKIP         | 0xD4             | Port 0 Skip                                        | 137  |

| P1             | 0x90             | Port 1 Latch                                       | 138  |

| P1MDIN         | 0xF2             | Port 1 Input Mode Configuration                    | 138  |

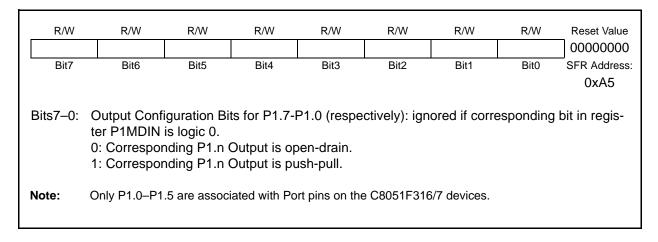

| P1MDOUT        | 0xA5             | Port 1 Output Mode Configuration                   | 139  |

| P1SKIP         | 0xD5             | Port 1 Skip                                        | 139  |

| P2             | 0xA0             | Port 2 Latch                                       | 140  |

| P2MDIN         | 0xF3             | Port 2 Input Mode Configuration                    | 140  |

| P2MDOUT        | 0xA6             | Port 2 Output Mode Configuration                   | 141  |

# Table 8.3. Special Function Registers

#### 8.3.2. External Interrupts

The /INT0 and /INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The IN0PL (/INT0 Polarity) and IN1PL (/INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (**Section "17.1. Timer 0 and Timer 1" on page 187**) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | INOPL /INT0 Interrupt |                              |

|-----|-----------------------|------------------------------|

| 1   | 0                     | Active low, edge sensitive   |

| 1   | 1                     | Active high, edge sensitive  |

| 0   | 0                     | Active low, level sensitive  |

| 0   | 1                     | Active high, level sensitive |

| IT1 | IN1PL | /INT1 Interrupt              |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

/INT0 and /INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 8.11). Note that /INT0 and /INT0 Port pin assignments are independent of any Crossbar assignments. /INT0 and /INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to /INT0 and/or /INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see **Section** "13.1. Priority Crossbar Decoder" on page 131 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the /INT0 and /INT1 external interrupts, respectively. If an /INT0 or /INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

#### 8.3.3. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP or EIP1) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 8.4.

#### 8.3.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 5 system clock cycles: 1 clock cycle to detect the interrupt and 4 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 18 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 4 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

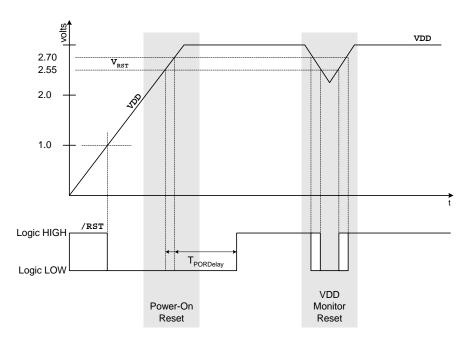

### 9.1. Power-On Reset

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>DD</sub> settles above V<sub>RST</sub>. An additional delay occurs before the device is released from reset; the delay decreases as the V<sub>DD</sub> ramp time increases (V<sub>DD</sub> ramp time is defined as how fast V<sub>DD</sub> ramps from 0 V to V<sub>RST</sub>). Figure 9.2. plots the power-on and V<sub>DD</sub> monitor reset timing. For valid ramp times (less than 1 ms), the power-on reset delay (T<sub>PORDelav</sub>) is typically less than 0.3 ms.

Note: The maximum  $V_{DD}$  ramp time is 1 ms; slower ramp times may cause the device to be released from reset before  $V_{DD}$  reaches the  $V_{RST}$  level.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> monitor is disabled following a power-on reset.

Figure 9.2. Power-On and V<sub>DD</sub> Monitor Reset Timing

### 9.2. Power-Fail Reset / V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the RST pin low and hold the CIP-51 in a reset state (see Figure 9.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads '1', the data may no longer be valid. The  $V_{DD}$  monitor is disabled after power-on resets; however its defined state (enabled/disabled) is not altered by

# C8051F310/1/2/3/4/5/6/7

|         |   |   |   | F         | °0          |        |   |   |   | P1 |   |           |             |        |   |   |   | P2        |             |   |   |                     |   |   |

|---------|---|---|---|-----------|-------------|--------|---|---|---|----|---|-----------|-------------|--------|---|---|---|-----------|-------------|---|---|---------------------|---|---|

|         |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| PIN I/O | 0 | 1 | 2 | 3         | 4           | 5      | 6 | 7 | 0 | 1  | 2 | 3         | 4           | 5      | 6 | 7 | 0 | 1         | 2           | 3 | 4 | 5                   | 6 |   |

| ТХО     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| RX0     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| SCK     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| MISO    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| MOSI    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| NSS*    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| SDA     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| SCL     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| CP0     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| CP0A    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| CP1     |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   | able                |   |   |

| CP1A    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   | avail               |   |   |

| SYSCLK  |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   | Signals Unavailable |   |   |

| CEX0    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   | nals                |   |   |

| CEX1    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   | Sigi                |   |   |

| CEX2    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| CEX3    |   |   |   |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| CEX4    | 1 |   | 1 |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   | 1 |                     |   |   |

| ECI     | 1 |   | 1 |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| ТО      | 1 |   | 1 |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   |   |

| T1      |   |   | 1 |           |             |        |   |   |   |    |   |           |             |        |   |   |   |           |             |   |   |                     |   | ] |

|         | 0 | 0 | 1 | 1<br>P0SK | 0<br>IP[0:7 | 0<br>1 | 0 | 0 | 0 | 0  | 0 | 0<br>P1SK | 0<br>IP[0:7 | 0<br>1 | 0 | 0 | 0 | 0<br>P2SK | 0<br>IP[0:3 | 0 |   |                     |   | - |

SF Signals Special Function Signals are not assigned by the Crossbar. When these signals are enabled, the Crossbar must be manually configured to skip their corresponding port pins.

\*Note: NSS is only pinned out in 4-wire SPI mode.

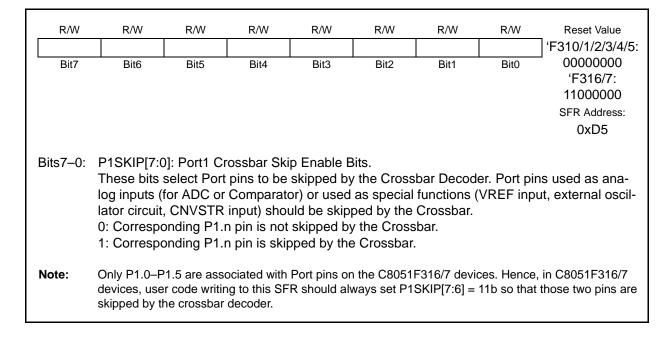

Note: P1.6,P1.7,P2.6,P2.7 only available on the C8051F310/1/2/3/4/5; P1SKIP[7:6] should always be set to 11b for the C8051F316/7 devices.

#### Figure 13.4. Crossbar Priority Decoder with Crystal Pins Skipped

Registers XBR0 and XBR1 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when the UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. Standard Port I/Os appear contiguously after the prioritized functions have been assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, pending the state of the NSS-MD1-NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

#### SFR Definition 13.9. P1MDOUT: Port1 Output Mode

### SFR Definition 13.10. P1SKIP: Port1 Skip

| SFR Definit | ion 13.15. | P3: Port3 |

|-------------|------------|-----------|

| •••••       |            |           |

| R/W      | R/W<br>P3.6                                                                                                                   | R/W<br>P3.5                                                              | R/W<br>P3.4                                | R/W<br>P3.3                  | R/W<br>P3.2 | R/W<br>P3.1 | R/W<br>P3.0     | Reset Value     |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------|------------------------------|-------------|-------------|-----------------|-----------------|--|--|--|--|

| Bit7     | Bit6                                                                                                                          | Bit5                                                                     | Bit4                                       | Bit3                         | Bit2        | Bit1        | Bit0 SFR Addres |                 |  |  |  |  |

|          |                                                                                                                               |                                                                          |                                            |                              |             | (bit        | t addressable)  | 0xB0            |  |  |  |  |

| Bits7–0: | P3.[7:0]<br>Write - Outpu<br>0: Logic Low<br>1: Logic High<br>Read - Alwa<br>pin when cou<br>0: P3.n pin is<br>1: P3.n pin is | o Output.<br>n Output (hi<br>ys reads '1'<br>nfigured as<br>s logic low. | gh impedar<br>if selected<br>digital input | nce if corres<br>as analog i |             |             | ,               | eads Port       |  |  |  |  |

| Note:    | Only P3.0–P3<br>Port pin on C8                                                                                                |                                                                          |                                            | •                            | 051F310/2/4 | devices; On | ly P3.0 is ass  | sociated with a |  |  |  |  |

# SFR Definition 13.16. P3MDIN: Port3 Input Mode

| R/W                  | R/W                                                                                           | R/W                                                | R/W                                        | R/W                                        | R/W                          | R/W         | R/W           | Reset Value          |

|----------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------|--------------------------------------------|------------------------------|-------------|---------------|----------------------|

| -                    | -                                                                                             | -                                                  |                                            |                                            |                              |             |               | 11111111             |

| Bit7                 | Bit6                                                                                          | Bit5                                               | Bit4                                       | Bit3                                       | Bit2                         | Bit1        | Bit0          | SFR Address:<br>0xF4 |

| Bits7–5:<br>Bits4–0: | UNUSED. Re<br>Input Configu<br>Port pins cor<br>receiver disa<br>0: Correspon<br>1: Correspon | uration Bits<br>nfigured as<br>bled.<br>nding P3.n | for P3.4–P<br>analog inpu<br>pin is config | 3.0 (respec<br>uts have the<br>gured as an | eir weak pull<br>analog inpu | ut.         | driver, and   | digital              |

| Note:                | Only P3.0–P3<br>Port pin on C8                                                                |                                                    |                                            |                                            | 3051F310/2/4                 | devices; Or | nly P3.0 is a | ssociated with       |

# SFR Definition 13.17. P3MDOUT: Port3 Output Mode

| R     | /W<br>-                                                                                                                                                                                                                                                                                                              | R/W<br>-                       | R/W<br>- | R/W  | R/W  | R/W         | R/W         | R/W           | Reset Value<br>00000000 |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------|------|------|-------------|-------------|---------------|-------------------------|--|--|--|--|

| В     | it7                                                                                                                                                                                                                                                                                                                  | Bit6                           | Bit5     | Bit4 | Bit3 | Bit2        | Bit1        | Bit0          | SFR Address:<br>0xA7    |  |  |  |  |

|       | <ul> <li>Bits7–5: UNUSED. Read = 000b; Write - don't care.</li> <li>Bits4–0: Output Configuration Bits for P3.4–P3.0 (respectively): ignored if corresponding bit in register P3MDIN is logic 0.</li> <li>0: Corresponding P3.n Output is open-drain.</li> <li>1: Corresponding P3.n Output is push-pull.</li> </ul> |                                |          |      |      |             |             |               |                         |  |  |  |  |

| Note: |                                                                                                                                                                                                                                                                                                                      | Only P3.0–P3<br>Port pin on C8 |          |      |      | 051F310/2/4 | devices; On | ly P3.0 is as | sociated with a         |  |  |  |  |

### Table 13.1. Port I/O DC Electrical Characteristics

$V_{DD}$  = 2.7 to 3.6 V, -40 to +85 °C unless otherwise specified

| Parameters            | Conditions                                   | Min                   | Тур            | Max | Units |

|-----------------------|----------------------------------------------|-----------------------|----------------|-----|-------|

|                       | I <sub>OH</sub> = −3 mA, Port I/O push-pull  | V <sub>DD</sub> – 0.7 | —              |     |       |

| Output High Voltage   | I <sub>OH</sub> = −10 μA, Port I/O push-pull | V <sub>DD</sub> – 0.1 | —              | —   | V     |

|                       | I <sub>OH</sub> = –10 mA, Port I/O push-pull | _                     | $V_{DD} - 0.8$ | —   |       |

|                       | I <sub>OL</sub> = 8.5 mA                     | —                     | —              | 0.6 |       |

| Output Low Voltage    | I <sub>OL</sub> = 10 μA                      | —                     | —              | 0.1 | V     |

|                       | I <sub>OL</sub> = 25 mA                      | —                     | 1.0            | _   |       |

| Input High Voltage    |                                              | 2.0                   | —              | _   | V     |

| Input Low Voltage     |                                              |                       | —              | 0.8 | V     |

| Input Lookago Current | Weak Pullup Off                              | —                     | —              | ±1  |       |

| Input Leakage Current | Weak Pullup On, V <sub>IN</sub> = 0 V        | —                     | 25             | 40  | μA    |

#### 14.4. Using the SMBus

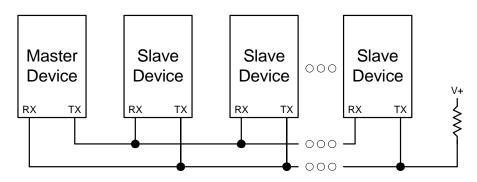

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

SMBus interrupts are generated for each data byte or slave address that is transferred. When transmitting, this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data, this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. See **Section "14.5. SMBus Transfer Modes" on page 157** for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in **Section "14.4.2. SMB0CN Control Register" on page 153**; Table 14.4 provides a quick SMB0CN decoding reference.

SMBus configuration options include:

- Timeout detection (SCL Low Timeout and/or Bus Free Timeout)

- SDA setup and hold time extensions

- Slave event enable/disable

- Clock source selection

These options are selected in the SMB0CF register, as described in **Section "14.4.1. SMBus Configura**tion Register" on page 150.

| R/W      | R/W                                                                                                                                                                              | R            | R/W         | R/W           | R/W          | R/W           | R/W          | Reset Value  |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|---------------|--------------|---------------|--------------|--------------|--|--|--|--|

| ENSMB    | INH                                                                                                                                                                              | BUSY         | EXTHOLD     | SMBTOE        | SMBFTE       | SMBCS1        | SMBCS0       | 00000000     |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                                             | Bit5         | Bit4        | Bit3          | Bit2         | Bit1          | Bit0         | -            |  |  |  |  |

|          |                                                                                                                                                                                  |              |             |               |              |               | SFR Address  | : 0xC1       |  |  |  |  |

|          |                                                                                                                                                                                  |              |             |               |              |               |              |              |  |  |  |  |

| Bit7:    | ENSMB: SM                                                                                                                                                                        |              |             |               |              |               |              |              |  |  |  |  |

|          | This bit enab                                                                                                                                                                    |              |             | is interface. | When enal    | bled, the int | erface cons  | tantly mon-  |  |  |  |  |

|          | itors the SD/                                                                                                                                                                    |              |             |               |              |               |              |              |  |  |  |  |

|          | 0: SMBus in<br>1: SMBus in                                                                                                                                                       |              |             |               |              |               |              |              |  |  |  |  |

| Bit6:    | INH: SMBus                                                                                                                                                                       |              |             |               |              |               |              |              |  |  |  |  |

| Dito.    | When this bi                                                                                                                                                                     |              |             |               | not genera   | ate an interr | unt when sl  | ave events   |  |  |  |  |

|          | occur. This e                                                                                                                                                                    |              |             |               |              |               |              |              |  |  |  |  |

|          | not affected.                                                                                                                                                                    | •            |             | CITIZ de cia  |              | buo. maoto    |              |              |  |  |  |  |

|          | 0: SMBus SI                                                                                                                                                                      | ave Mode     | enabled.    |               |              |               |              |              |  |  |  |  |

|          | 1: SMBus SI                                                                                                                                                                      | ave Mode i   | nhibited.   |               |              |               |              |              |  |  |  |  |

| Bit5:    | BUSY: SMB                                                                                                                                                                        |              |             |               |              |               |              |              |  |  |  |  |

|          | This bit is se                                                                                                                                                                   |              |             |               | ansfer is in | progress. It  | is cleared t | o logic 0    |  |  |  |  |

|          | when a STO                                                                                                                                                                       |              |             |               |              | _             |              |              |  |  |  |  |

| Bit4:    | EXTHOLD:                                                                                                                                                                         |              | •           |               |              |               | •            |              |  |  |  |  |

|          | This bit cont                                                                                                                                                                    |              |             |               | •            | to Table 14.  | .2.          |              |  |  |  |  |

|          | 0: SDA Exte                                                                                                                                                                      |              |             |               |              |               |              |              |  |  |  |  |

| Bit3:    | 1: SDA Extended Setup and Hold Times enabled.<br>SMBTOE: SMBus SCL Timeout Detection Enable.                                                                                     |              |             |               |              |               |              |              |  |  |  |  |

| DILJ.    | This bit enab                                                                                                                                                                    |              |             |               |              | 1 the SMB     | us forces Ti | mer 3 to     |  |  |  |  |

|          | reload while                                                                                                                                                                     |              |             |               |              |               |              |              |  |  |  |  |

|          |                                                                                                                                                                                  |              |             |               |              |               |              |              |  |  |  |  |

|          | figured in split mode (T3SPLIT is set), only the high byte of Timer 3 is held in reload while SCL is high. Timer 3 should be programmed to generate interrupts at 25 ms, and the |              |             |               |              |               |              |              |  |  |  |  |

|          | Timer 3 inter                                                                                                                                                                    |              |             |               |              |               |              |              |  |  |  |  |

| Bit2:    | SMBFTE: SI                                                                                                                                                                       |              |             |               |              |               |              |              |  |  |  |  |

|          | When this bi                                                                                                                                                                     |              |             |               | nsidered fre | ee if SCL an  | d SDA rem    | ain high for |  |  |  |  |

|          | more than 1                                                                                                                                                                      |              |             |               |              |               |              |              |  |  |  |  |

| Bits1–0: | SMBCS1-SM                                                                                                                                                                        |              |             |               |              |               |              |              |  |  |  |  |

|          | These two b                                                                                                                                                                      |              |             |               |              | •             |              | Bus bit      |  |  |  |  |

|          | rate. The se                                                                                                                                                                     | lected devic | ce snould b | e conligured  | according    | to Equation   | 1 14.1.      |              |  |  |  |  |

|          | SMBCS1                                                                                                                                                                           | SMBCS0       | SM          | Bus Clock     | Source       |               |              |              |  |  |  |  |

|          | 0                                                                                                                                                                                | 0            | -           | Timer 0 Ove   | rflow        |               |              |              |  |  |  |  |

|          | 0                                                                                                                                                                                | 1            | -           | Timer 1 Ove   | rflow        |               |              |              |  |  |  |  |

|          | 1                                                                                                                                                                                | 0            | Timer       | 2 High Byte   | e Overflow   |               |              |              |  |  |  |  |

|          |                                                                                                                                                                                  |              |             | 2 Low Byte    |              |               |              |              |  |  |  |  |

# SFR Definition 14.1. SMB0CF: SMBus Clock/Configuration

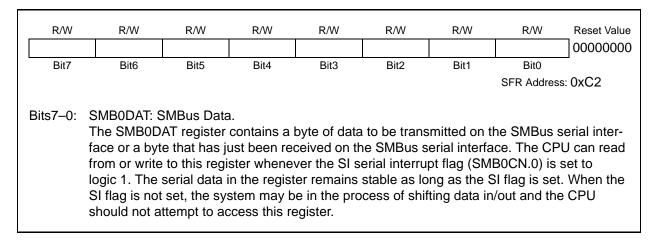

#### 14.4.3. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

#### SFR Definition 14.3. SMB0DAT: SMBus Data

# C8051F310/1/2/3/4/5/6/7

| Valu<br>Valu<br>Mode<br>Slave Transmitter<br>0010<br>0100<br>0100<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0100<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>Galaria<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>00000<br>0000<br>0000<br>00000<br>0000<br>0000<br>0000<br>0000<br>000 | es F             | Read  | ł       |     |                                                                   |                                                                  | /alue<br>Vritte |     |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|---------|-----|-------------------------------------------------------------------|------------------------------------------------------------------|-----------------|-----|-----|

| Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Status<br>Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                                               | Typical Response Options                                         | STA             | STO | ACK |

| er.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  | 0     | 0       | 0   | A slave byte was transmitted;<br>NACK received.                   | No action required (expecting STOP condition).                   | 0               | 0   | х   |