Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 21                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 13x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                            |

| Supplier Device Package    | 24-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f316-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 7. | Comparators                                                                                             |     |

|----|---------------------------------------------------------------------------------------------------------|-----|

|    | Figure 7.1. Comparator0 Functional Block Diagram                                                        | 69  |

|    | Figure 7.2. Comparator1 Functional Block Diagram                                                        | 70  |

|    | Figure 7.3. Comparator Hysteresis Plot                                                                  | 71  |

| 8. | CIP-51 Microcontroller                                                                                  |     |

|    | Figure 8.1. CIP-51 Block Diagram                                                                        |     |

|    | Figure 8.2. Memory Map                                                                                  | 85  |

| 9. | Reset Sources                                                                                           |     |

|    | Figure 9.1. Reset Sources                                                                               |     |

|    | Figure 9.2. Power-On and V <sub>DD</sub> Monitor Reset Timing                                           | 106 |

| 10 | Flash Memory                                                                                            |     |

|    | Figure 10.1. Flash Program Memory Map                                                                   | 113 |

|    | External RAM                                                                                            |     |

| 12 | Oscillators                                                                                             | 404 |

|    | Figure 12.1. Oscillator Diagram                                                                         |     |

| 40 | Figure 12.2. 32.768 kHz External Crystal Example                                                        | 120 |

| 13 | . Port Input/Output                                                                                     | 120 |

|    | Figure 13.1. Port I/O Functional Block Diagram                                                          |     |

|    | Figure 13.2. Port I/O Cell Block Diagram<br>Figure 13.3. Crossbar Priority Decoder with No Pins Skipped |     |

|    | Figure 13.4. Crossbar Priority Decoder with Crystal Pins Skipped                                        |     |

| 14 | SMBus                                                                                                   | 152 |

|    | Figure 14.1. SMBus Block Diagram                                                                        | 145 |

|    | Figure 14.2. Typical SMBus Configuration                                                                | 146 |

|    | Figure 14.3. SMBus Transaction                                                                          | 147 |

|    | Figure 14.4. Typical SMBus SCL Generation                                                               |     |

|    | Figure 14.5. Typical Master Transmitter Sequence                                                        |     |

|    | Figure 14.6. Typical Master Receiver Sequence                                                           |     |

|    | Figure 14.7. Typical Slave Receiver Sequence                                                            |     |

|    | Figure 14.8. Typical Slave Transmitter Sequence                                                         |     |

| 15 | .UĂRTO                                                                                                  |     |

|    | Figure 15.1. UART0 Block Diagram                                                                        | 163 |

|    | Figure 15.2. UARTO Baud Rate Logic                                                                      | 164 |

|    | Figure 15.3. UART Interconnect Diagram                                                                  |     |

|    | Figure 15.4. 8-Bit UART Timing Diagram                                                                  |     |

|    | Figure 15.5. 9-Bit UART Timing Diagram                                                                  | 166 |

|    | Figure 15.6. UART Multi-Processor Mode Interconnect Diagram                                             | 167 |

| 16 | Enhanced Serial Peripheral Interface (SPI0)                                                             |     |

|    | Figure 16.1. SPI Block Diagram                                                                          |     |

|    | Figure 16.2. Multiple-Master Mode Connection Diagram                                                    |     |

|    | Figure 16.3. 3-Wire Single Master and Slave Mode Connection Diagram                                     |     |

|    | Figure 16.4. 4-Wire Single Master and Slave Mode Connection Diagram                                     |     |

|    | Figure 16.5. Master Mode Data/Clock Timing                                                              |     |

|    | Figure 16.6. Slave Mode Data/Clock Timing (CKPHA = 0)                                                   |     |

|    | Figure 16.7. Slave Mode Data/Clock Timing (CKPHA = 1)                                                   | 179 |

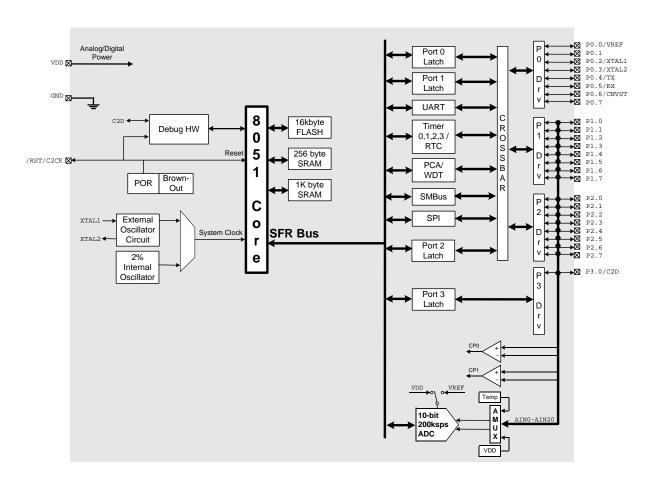

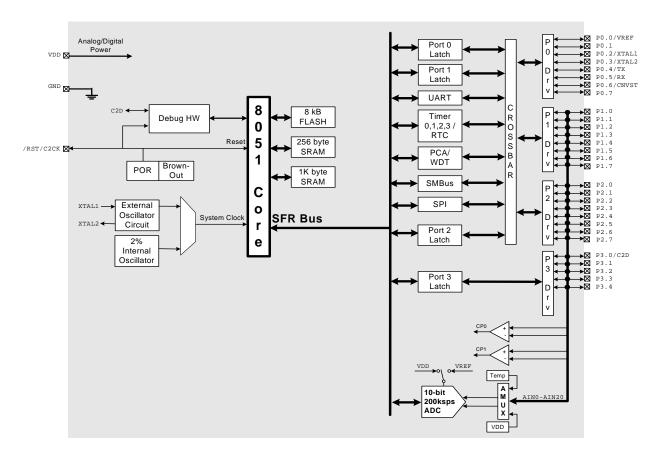

# C8051F310/1/2/3/4/5/6/7

Figure 1.2. C8051F311 Block Diagram

Figure 1.3. C8051F312 Block Diagram

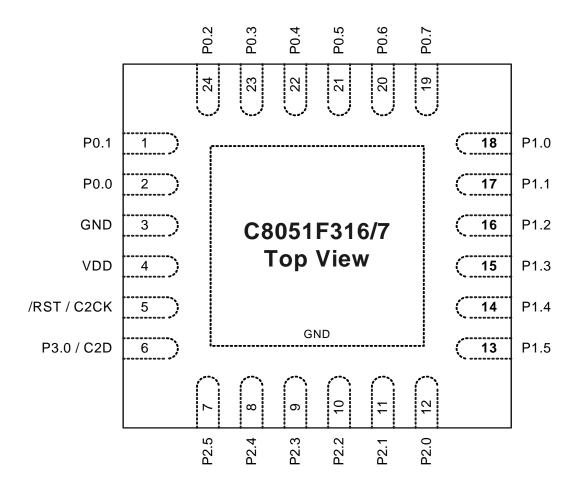

Figure 4.7. QFN-24 Pinout Diagram (Top View)

# SFR Definition 5.1. AMX0P: AMUX0 Positive Channel Select

| R       | R                         | R                         | R/W                      | R/W                 | R/W       | R/W    | R/W    | Reset Value |

|---------|---------------------------|---------------------------|--------------------------|---------------------|-----------|--------|--------|-------------|

| -       | -                         | -                         | AMX0P4                   | AMX0P3              | AMX0P2    | AMX0P1 | AMX0P0 | 0000000     |

| Bit7    | Bit6                      | Bit5                      | Bit4                     | Bit3                | Bit2      | Bit1   | Bit0   | SFR Addres  |

|         |                           |                           |                          |                     |           |        |        | 0xBB        |

|         |                           |                           |                          |                     |           |        |        |             |

|         | UNUSED. Re<br>AMX0P4–0: / |                           |                          |                     |           |        |        |             |

| 0154-0. |                           |                           | osilive input            | Selection           |           |        |        |             |

|         | AMX0P4                    | -0                        | ADC                      | 0 Positive          | Input     |        |        |             |

|         | 00000                     |                           |                          | P1.0                | •         |        |        |             |

|         | 00001                     |                           |                          | P1.1                |           |        |        |             |

|         | 00010                     | )                         |                          | P1.2                |           |        |        |             |

|         | 00011                     |                           |                          | P1.3                |           |        |        |             |

|         | 00100                     |                           |                          | P1.4                |           |        |        |             |

|         | 00101                     |                           |                          | P1.5                |           |        |        |             |

|         | 00110                     |                           |                          | P1.6 <sup>(1)</sup> |           |        |        |             |

|         | 00111                     |                           |                          | P1.7 <sup>(1)</sup> |           |        |        |             |

|         | 01000                     | )                         |                          | P2.0                |           |        |        |             |

|         | 01001                     |                           |                          | P2.1                |           |        |        |             |

|         | 01010                     |                           |                          | P2.2                |           |        |        |             |

|         | 01011                     |                           |                          | P2.3                |           |        |        |             |

|         | 01100                     |                           |                          | P2.4                |           |        |        |             |

|         | 01101                     |                           |                          | P2.5                |           |        |        |             |

|         | 01110                     |                           |                          | P2.6 <sup>(1)</sup> |           |        |        |             |

|         | 01111                     |                           |                          | P2.7 <sup>(1)</sup> |           |        |        |             |

|         | 10000                     |                           |                          | P3.0                |           |        |        |             |

|         | 10001 <sup>()</sup>       | 2)                        |                          | P3.1 <sup>(2)</sup> |           |        |        |             |

|         | 10010 <sup>()</sup>       | 2)                        |                          | P3.2 <sup>(2)</sup> |           |        |        |             |

|         | 10011 <sup>(2</sup>       | 2)                        |                          | P3.3 <sup>(2)</sup> |           |        |        |             |

|         | 10100 <sup>()</sup>       |                           |                          | P3.4 <sup>(2)</sup> |           |        |        |             |

|         | 10101–11                  |                           |                          | RESERVED            | )         |        |        |             |

|         | 11110                     |                           |                          | Temp Senso          | or        |        |        |             |

|         | 11111                     |                           |                          | V <sub>DD</sub>     |           |        |        |             |

|         | Notes:                    |                           |                          |                     |           |        |        |             |

|         | 1. Only a                 |                           | 8051F310/1/2             |                     | tion      |        |        |             |

|         |                           |                           | 28051F316/7              |                     |           |        |        |             |

|         |                           | pplies to C<br>F311/3/6/7 | 8051F310/2; :<br>devices | selection RE        | SERVED ON |        |        |             |

|         | 00001                     |                           |                          |                     |           |        |        |             |

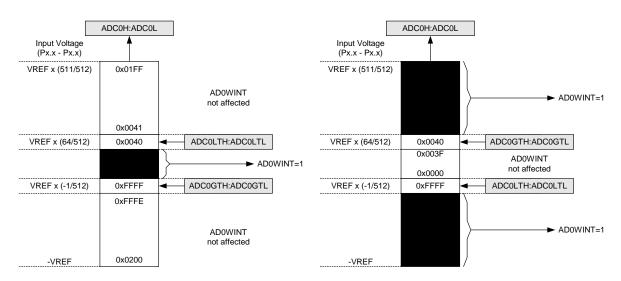

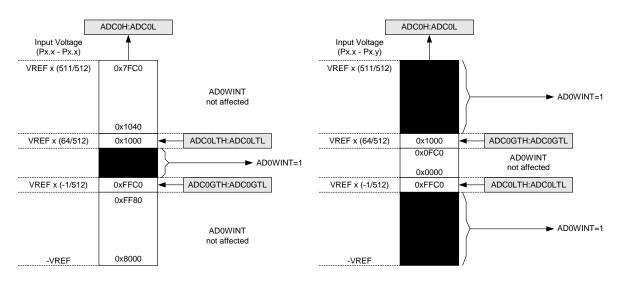

#### 5.4.2. Window Detector In Differential Mode

Figure 5.8 shows two example window comparisons for right-justified, differential data, with ADC0LTH:ADC0LTL = 0x0040 (+64d) and ADC0GTH:ADC0GTH = 0xFFFF (-1d). In differential mode, the measurable voltage between the input pins is between -VREF and VREF\*(511/512). Output codes are represented as 10-bit 2's complement signed integers. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0xFFFF (-1d) < ADC0H:ADC0L < 0x0040 (64d)). In the right example, an AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0xFFFF (-1d) or ADC0H:ADC0L > 0x0040 (+64d)). Figure 5.9 shows an example using left-justified data with the same comparison values.

Figure 5.8. ADC Window Compare Example: Right-Justified Differential Data

Figure 5.9. ADC Window Compare Example: Left-Justified Differential Data

| Register      | Address     | Description                     | Page |

|---------------|-------------|---------------------------------|------|

| TMR2L         | 0xCC        | Timer/Counter 2 Low             | 198  |

| TMR2RLH       | 0xCB        | Timer/Counter 2 Reload High     | 198  |

| TMR2RLL       | 0xCA        | Timer/Counter 2 Reload Low      | 198  |

| TMR3CN        | 0x91        | Timer/Counter 3Control          | 201  |

| TMR3H         | 0x95        | Timer/Counter 3 High            | 202  |

| TMR3L         | 0x94        | Timer/Counter 3Low              | 202  |

| TMR3RLH       | 0x93        | Timer/Counter 3 Reload High     | 202  |

| TMR3RLL       | 0x92        | Timer/Counter 3 Reload Low      | 202  |

| VDM0CN        | 0xFF        | V <sub>DD</sub> Monitor Control | 107  |

| XBR1          | 0xE2        | Port I/O Crossbar Control 1     | 135  |

| XBR0          | 0xE1        | Port I/O Crossbar Control 0     | 134  |

| 0x84-0x86, 0x | x96-0x97,   |                                 |      |

| 0xAB-0xAF, 0  | )xB4, 0xB9, |                                 |      |

| 0xBF, 0xC7, 0 | 0xC9, 0xCE, | Reserved                        |      |

| 0xCF, 0xD2, 0 |             |                                 |      |

| 0xDF, 0xE3, 0 | 0xE5, 0xF5  |                                 |      |

## Table 8.3. Special Function Registers (Continued)

#### 8.2.7. Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic 1. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

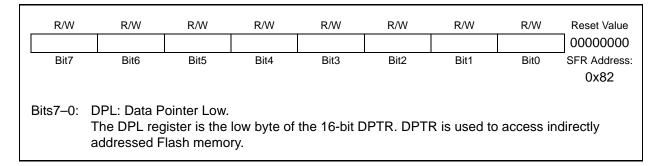

#### SFR Definition 8.1. DPL: Data Pointer Low Byte

any other reset source. For example, if the  $V_{DD}$  monitor is enabled and a software reset is performed, the  $V_{DD}$  monitor will still be enabled after the reset.

**Important Note:** The  $V_{DD}$  monitor must be enabled before it is selected as a reset source. Selecting the  $V_{DD}$  monitor as a reset source before it is enabled and stabilized may cause a system reset. The procedure for configuring the  $V_{DD}$  monitor as a reset source is shown below:

- Step 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDM0CN = '1').

- Step 2. Wait for the V<sub>DD</sub> monitor to stabilize (see Table 9.1 for the V<sub>DD</sub> Monitor turn-on time). Note: This delay should be omitted if software contains routines that erase or write Flash memory.

- Step 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = '1').

See Figure 9.2 for  $V_{DD}$  monitor timing; note that the reset delay is not incurred after a  $V_{DD}$  monitor reset. See Table 9.1 for complete electrical characteristics of the  $V_{DD}$  monitor.

| SFR Definition 9.1. VDM0CN: | V <sub>DD</sub> Monitor Control |

|-----------------------------|---------------------------------|

|-----------------------------|---------------------------------|

| R/W      | R                                                                                                                           | R                                                                                                                  | R                                                        | R                                        | R                            | R            | R    | Reset Value |

|----------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------|------------------------------|--------------|------|-------------|

|          |                                                                                                                             |                                                                                                                    |                                                          | Reserved                                 |                              |              |      | Variable    |

| Bit7     | Bit6                                                                                                                        | Bit5                                                                                                               | Bit4                                                     | Bit3                                     | Bit2                         | Bit1         | Bit0 | J vanabio   |

| Diti     | SFR Address: 0xFF                                                                                                           |                                                                                                                    |                                                          |                                          |                              |              |      |             |

| Bit7:    |                                                                                                                             |                                                                                                                    |                                                          |                                          |                              |              |      |             |

| Bit6:    | 0: $V_{DD}$ Monit<br>1: $V_{DD}$ Monit<br>$V_{DD}$ STAT: $V$<br>This bit indic<br>0: $V_{DD}$ is at o<br>1: $V_{DD}$ is abo | tor Disabled<br>for Enabled<br>f <sub>DD</sub> Status.<br>ates the cu<br>for below the<br>pove the V <sub>DD</sub> | I.<br>rrent power<br>V <sub>DD</sub> monit<br>monitor th | supply stat<br>tor threshold<br>reshold. | us (V <sub>DD</sub> Mo<br>d. | onitor outpu | t).  |             |

| Bits5–0: | Reserved. R                                                                                                                 | ead = Varia                                                                                                        | ble. Write =                                             | don't care                               |                              |              |      |             |

# 9.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 9.1 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

# SFR Definition 9.2. RSTSRC: Reset Source

| R     | R                            | R/W                 | R/W          | R                        | R/W                     | R/W           | R                      | Reset Valu  |

|-------|------------------------------|---------------------|--------------|--------------------------|-------------------------|---------------|------------------------|-------------|

| -     | FERROR                       | CORSEF              | SWRSF        | WDTRSF                   | MCDRSF                  | PORSF         | PINRSF                 | Variable    |

| Bit7  | Bit6                         | Bit5                | Bit4         | Bit3                     | Bit2                    | Bit1          | Bit0                   |             |

|       |                              |                     |              |                          |                         |               | SFR Address            | :0xEF       |

|       |                              |                     |              |                          |                         |               |                        |             |

| Bit7: | UNUSED. R                    | $aad = 0 M_{\rm H}$ | rito - don't | ooro                     |                         |               |                        |             |

| Bit6: | FERROR: FI                   |                     |              | care.                    |                         |               |                        |             |

|       | 0: Source of                 |                     |              | lash read/w              | rite/erase er           | ror           |                        |             |

|       | 1: Source of                 |                     |              |                          |                         |               |                        |             |

| Bit5: | CORSEF: Co                   |                     |              |                          |                         |               |                        |             |

|       | 0: Read: Sou                 | •                   |              |                          | -                       | : Compara     | tor0 is not a          | reset       |

|       | source.                      |                     |              |                          |                         |               |                        |             |

|       | 1: Read: Sou                 | urce of last        | reset was (  | Comparator               | 0. Write: Co            | omparator0    | is a reset s           | ource       |

|       | (active-low).                |                     |              |                          |                         |               |                        |             |

| Bit4: | SWRSF: Sof                   |                     |              |                          |                         |               |                        |             |

|       | 0: Read: Sou                 |                     |              |                          |                         |               |                        |             |

| Bit3: | 1: Read: Sou<br>WDTRSF: W    |                     |              |                          | KOF DIL WI              | ite: Forces   | a system re            | eset.       |

| ກເວ.  | 0: Source of                 | -                   |              | -                        |                         |               |                        |             |

|       | 1: Source of                 |                     |              |                          | •                       |               |                        |             |

| Bit2: | MCDRSF: M                    |                     |              |                          |                         |               |                        |             |

|       | 0: <b>Read:</b> Sou          | -                   |              | -                        | g Clock Det             | ector timed   | out. Write: N          | lissing     |

|       | Clock Detect                 |                     |              |                          | 0                       |               |                        | 0           |

|       | 1: Read: Sou                 | urce of last        | reset was a  | a Missing C              | lock Detecto            | or timeout.   | Write: Miss            | ing Clock   |

|       | Detector ena                 |                     |              | -                        | clock condit            | ion is dete   | cted.                  |             |

| Bit1: | PORSF: Pov                   |                     |              | •                        |                         |               |                        |             |

|       | This bit is se               |                     |              |                          |                         |               |                        |             |

|       | monitor as a                 |                     |              | -                        |                         | _             |                        | is enable   |

|       | and stabilize                |                     |              |                          |                         |               |                        |             |

|       | 0: Read: Las                 | st reset was        | not a pow    | er-on or V <sub>DI</sub> | <sub>C</sub> monitor re | set. Write:   | V <sub>DD</sub> monito | or is not a |

|       | reset source                 |                     |              |                          |                         |               |                        |             |

|       | 1: Read: Las                 |                     |              |                          | nitor reset; a          | all other res | set flags inde         | eterminate  |

|       | Write: V <sub>DD</sub> r     |                     |              | ce.                      |                         |               |                        |             |

| BitO: | PINRSF: HW                   |                     | · ·          | _                        |                         |               |                        |             |

|       | 0: Source of                 |                     |              |                          |                         |               |                        |             |

|       | 1: Source of                 | last reset w        | /as RST pii  | า.                       |                         |               |                        |             |

| Note: | For bits that a read-modify- |                     |              |                          |                         |               |                        |             |

#### 10.1.3. Flash Write Procedure

Flash bytes are programmed by software with the following sequence:

- Step 1. Disable interrupts (recommended).

- Step 2. Erase the 512-byte Flash page containing the target location, as described in **Section 10.1.2**.

- Step 3. Set the PSWE bit (register PSCTL).

- Step 4. Clear the PSEE bit (register PSCTL).

- Step 5. Write the first key code to FLKEY: 0xA5.

- Step 6. Write the second key code to FLKEY: 0xF1.

- Step 7. Using the MOVX instruction, write a single data byte to the desired location within the 512 byte sector.

Steps 5–7 must be repeated for each byte to be written. After Flash writes are complete, PSWE should be cleared so that MOVX instructions do not target program memory.

#### **Table 10.1. Flash Electrical Characteristics**

| Parameter                   | Conditions                        | Min    | Тур   | Max | Units       |

|-----------------------------|-----------------------------------|--------|-------|-----|-------------|

| Flash Size                  | C8051F310/1/6/7                   | 16384* | _     |     | bytes       |

|                             | C8051F312/3/4/5                   | 8192   | _     |     | Dytes       |

| Endurance                   |                                   | 20 k   | 100 k |     | Erase/Write |

| Erase Cycle Time            | 25 MHz System Clock               | 10     | 15    | 20  | ms          |

| Write Cycle Time            | 25 MHz System Clock               | 40     | 55    | 70  | μs          |

| Note: 512 bytes at location | ons 0x3E00 (C8051F310/1) are rese | rved.  |       |     | •           |

$V_{DD} = 2.7$  to 3.6 V; -40 to +85 °C unless otherwise specified.

#### 10.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. Note: MOVX read instructions always target XRAM.

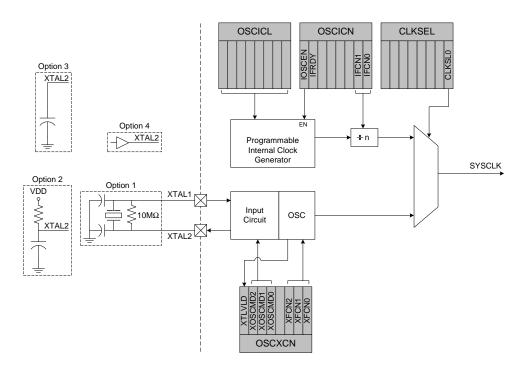

# 12. Oscillators

C8051F31x devices include a programmable internal oscillator and an external oscillator drive circuit. The internal oscillator can be enabled/disabled and calibrated using the OSCICN and OSCICL registers, as shown in Figure 12.1. The system clock can be sourced by the external oscillator circuit, the internal oscillator, or a scaled version of the internal oscillator. The internal oscillator's electrical specifications are given in Table 12.1 on page 123.

Figure 12.1. Oscillator Diagram

# 12.1. Programmable Internal Oscillator

All C8051F31x devices include a programmable internal oscillator that defaults as the system clock after a system reset. The internal oscillator period can be programmed via the OSCICL register as defined by SFR Definition 12.1 OSCICL is factor calibrated to obtain a 24.5 MHz frequency.

Electrical specifications for the precision internal oscillator are given in Table 12.1 on page 123. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN. The divide value defaults to 8 following a reset.

# SFR Definition 13.5. P0MDOUT: Port0 Output Mode

| R/W      | R/W                                                        | R/W                        | R/W          | R/W           | R/W            | R/W           | R/W          | Reset Value 00000000 |

|----------|------------------------------------------------------------|----------------------------|--------------|---------------|----------------|---------------|--------------|----------------------|

| Bit7     | Bit6                                                       | Bit5                       | Bit4         | Bit3          | Bit2           | Bit1          | Bit0         | SFR Address:<br>0xA4 |

| Bits7–0: | Output Confi<br>ter P0MDIN<br>0: Correspor<br>1: Correspor | is logic 0.<br>Inding P0.n | Output is op | pen-drain.    | ectively): igr | nored if corr | espondinę    | g bit in regis-      |

| Note:    | When SDA an<br>P0MDOUT.                                    | d SCL appe                 | ar on any of | the Port I/O, | each are ope   | en-drain rega | rdless of th | ne value of          |

# SFR Definition 13.6. P0SKIP: Port0 Skip

| R/W  | R/W                             | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |

|------|---------------------------------|------|------|------|------|------|------|--------------|

|      |                                 |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6                            | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |                                 |      |      |      |      |      |      | 0xD4         |

|      | These bits se<br>log inputs (fo |      |      |      |      |      |      |              |

#### 14.3.2. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I2C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 14.3.3. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMB0CF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to overflow after 25 ms (and SMBTOE set), the Timer 3 interrupt service routine can be used to reset (disable and re-enable) the SMBus in the event of an SCL low timeout.

#### 14.3.4. SCL High (SMBus Free) Timeout

The SMBus specification stipulates that if the SCL and SDA lines remain high for more that 50  $\mu$ s, the bus is designated as free. When the SMBFTE bit in SMB0CF is set, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods. If the SMBus is waiting to generate a Master START, the START will be generated following this timeout. Note that a clock source is required for free timeout detection, even in a slave-only implementation.

|                                     |                              |                      | Freq                             | uency: 22.1184        | MHz                                 |      | Frequency: 22.1184 MHz           |  |  |  |  |  |  |  |  |

|-------------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|--|--|--|--|--|--|--|--|

|                                     | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload Value<br>(hex) |  |  |  |  |  |  |  |  |

|                                     | 230400                       | 0.00%                | 96                               | SYSCLK                | XX                                  | 1    | 0xD0                             |  |  |  |  |  |  |  |  |

|                                     | 115200                       | 0.00%                | 192                              | SYSCLK                | XX                                  | 1    | 0xA0                             |  |  |  |  |  |  |  |  |

|                                     | 57600                        | 0.00%                | 384                              | SYSCLK                | XX                                  | 1    | 0x40                             |  |  |  |  |  |  |  |  |

| С<br>С.                             | 28800                        | 0.00%                | 768                              | SYSCLK / 12           | 00                                  | 0    | 0xE0                             |  |  |  |  |  |  |  |  |

| ( from<br>Osc.                      | 14400                        | 0.00%                | 1536                             | SYSCLK / 12           | 00                                  | 0    | 0xC0                             |  |  |  |  |  |  |  |  |

| 2Lk<br>nal                          | 9600                         | 0.00%                | 2304                             | SYSCLK / 12           | 00                                  | 0    | 0xA0                             |  |  |  |  |  |  |  |  |

| 'SC<br>ter                          | 2400                         | 0.00%                | 9216                             | SYSCLK / 48           | 10                                  | 0    | 0xA0                             |  |  |  |  |  |  |  |  |

| SYSCLK<br>External                  | 1200                         | 0.00%                | 18432                            | SYSCLK / 48           | 10                                  | 0    | 0x40                             |  |  |  |  |  |  |  |  |

|                                     | 230400                       | 0.00%                | 96                               | EXTCLK / 8            | 11                                  | 0    | 0xFA                             |  |  |  |  |  |  |  |  |

| E                                   | 115200                       | 0.00%                | 192                              | EXTCLK / 8            | 11                                  | 0    | 0xF4                             |  |  |  |  |  |  |  |  |

| <ul><li>froi</li><li>Osc.</li></ul> | 57600                        | 0.00%                | 384                              | EXTCLK / 8            | 11                                  | 0    | 0xE8                             |  |  |  |  |  |  |  |  |

| <u> </u>                            | 28800                        | 0.00%                | 768                              | EXTCLK / 8            | 11                                  | 0    | 0xD0                             |  |  |  |  |  |  |  |  |

| SYSCL<br>Internal                   | 14400                        | 0.00%                | 1536                             | EXTCLK / 8            | 11                                  | 0    | 0xA0                             |  |  |  |  |  |  |  |  |

| SY<br>Inte                          | 9600                         | 0.00%                | 2304                             | EXTCLK / 8            | 11                                  | 0    | 0x70                             |  |  |  |  |  |  |  |  |

# Table 15.3. Timer Settings for Standard Baud RatesUsing an External 22.1184 MHz Oscillator

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in Section 17.1.

| Table 15.4. Timer Settings for Standard Baud Rates |

|----------------------------------------------------|

| Using an External 18.432 MHz Oscillator            |

|                              | Frequency: 18.432 MHz        |                      |                                  |                       |                                     |      |                                  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | 0.00%                | 80                               | SYSCLK                | XX                                  | 1    | 0xD8                             |

| SYSCLK from<br>External Osc. | 115200                       | 0.00%                | 160                              | SYSCLK                | XX                                  | 1    | 0xB0                             |

|                              | 57600                        | 0.00%                | 320                              | SYSCLK                | XX                                  | 1    | 0x60                             |

|                              | 28800                        | 0.00%                | 640                              | SYSCLK / 4            | 01                                  | 0    | 0xB0                             |

|                              | 14400                        | 0.00%                | 1280                             | SYSCLK / 4            | 01                                  | 0    | 0x60                             |

|                              | 9600                         | 0.00%                | 1920                             | SYSCLK / 12           | 00                                  | 0    | 0xB0                             |

|                              | 2400                         | 0.00%                | 7680                             | SYSCLK / 48           | 10                                  | 0    | 0xB0                             |

| Ϋ́́                          | 1200                         | 0.00%                | 15360                            | SYSCLK / 48           | 10                                  | 0    | 0x60                             |

| SYSCLK from<br>Internal Osc. | 230400                       | 0.00%                | 80                               | EXTCLK / 8            | 11                                  | 0    | 0xFB                             |

|                              | 115200                       | 0.00%                | 160                              | EXTCLK / 8            | 11                                  | 0    | 0xF6                             |

|                              | 57600                        | 0.00%                | 320                              | EXTCLK / 8            | 11                                  | 0    | 0xEC                             |

|                              | 28800                        | 0.00%                | 640                              | EXTCLK / 8            | 11                                  | 0    | 0xD8                             |

|                              | 14400                        | 0.00%                | 1280                             | EXTCLK / 8            | 11                                  | 0    | 0xB0                             |

| SY<br>Int                    | 9600                         | 0.00%                | 1920                             | EXTCLK / 8            | 11                                  | 0    | 0x88                             |

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in Section 17.1.

# C8051F310/1/2/3/4/5/6/7

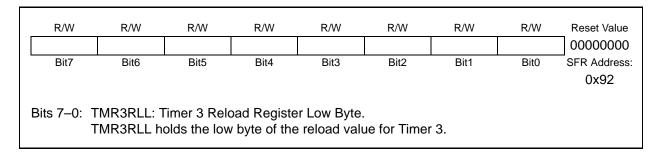

# SFR Definition 17.14. TMR3RLL: Timer 3 Reload Register Low Byte

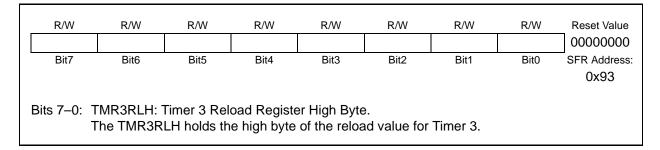

# SFR Definition 17.15. TMR3RLH: Timer 3 Reload Register High Byte

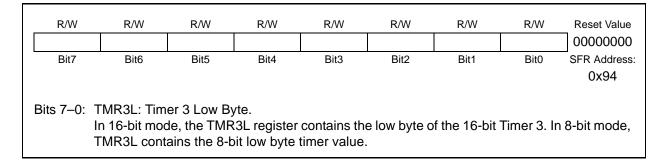

# SFR Definition 17.16. TMR3L: Timer 3 Low Byte

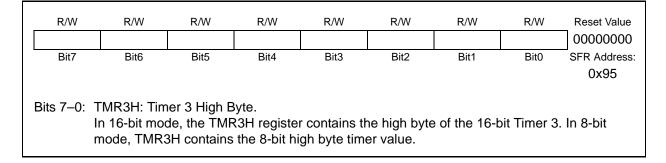

# SFR Definition 17.17. TMR3H Timer 3 High Byte

## 18.2. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: Edge-triggered Capture, Software Timer, High Speed Output, Frequency Output, 8-Bit Pulse Width Modulator, or 16-Bit Pulse Width Modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation.

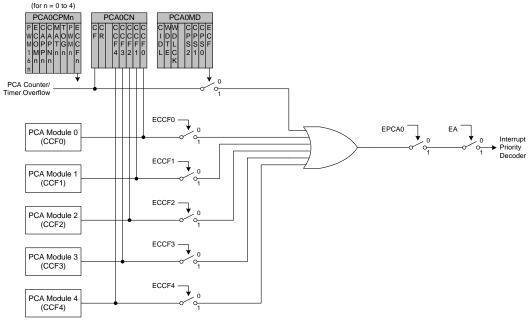

Table 18.2 summarizes the bit settings in the PCA0CPMn registers used to select the PCA capture/compare module's operating modes. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt. Note: PCA0 interrupts must be globally enabled before individual CCFn interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1. See Figure 18.3 for details on the PCA interrupt configuration.

| PWM16    | ECOM   | CAPP | CAPN | MAT | TOG | PWM | ECCF | Operation Mode                                |

|----------|--------|------|------|-----|-----|-----|------|-----------------------------------------------|

| Х        | Х      | 1    | 0    | 0   | 0   | 0   | Х    | Capture triggered by positive edge<br>on CEXn |

| Х        | Х      | 0    | 1    | 0   | 0   | 0   | Х    | Capture triggered by negative edge on CEXn    |

| Х        | Х      | 1    | 1    | 0   | 0   | 0   | Х    | Capture triggered by transition on<br>CEXn    |

| Х        | 1      | 0    | 0    | 1   | 0   | 0   | Х    | Software Timer                                |

| Х        | 1      | 0    | 0    | 1   | 1   | 0   | Х    | High Speed Output                             |

| Х        | 1      | 0    | 0    | Х   | 1   | 1   | Х    | Frequency Output                              |

| 0        | 1      | 0    | 0    | Х   | 0   | 1   | Х    | 8-Bit Pulse Width Modulator                   |

| 1        | 1      | 0    | 0    | Х   | 0   | 1   | Х    | 16-Bit Pulse Width Modulator                  |

| X = Don' | t Care |      |      |     |     |     |      |                                               |

# Table 18.2. PCA0CPM Register Settings for PCA Capture/Compare Modules

#### 18.2.3. High-Speed Output Mode

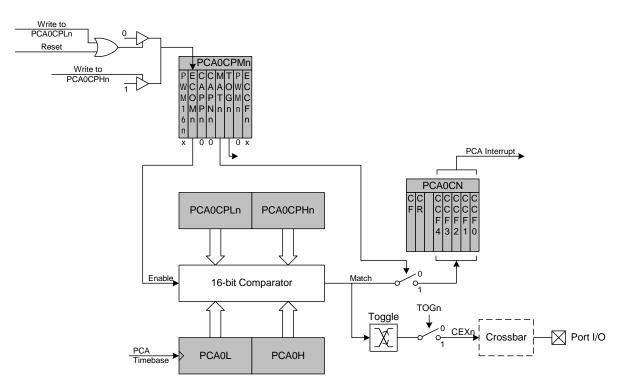

In High Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn) Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 18.6. PCA High Speed Output Mode Diagram

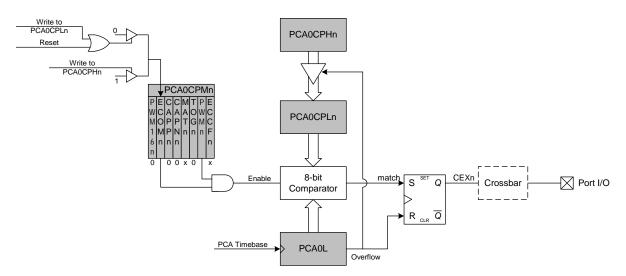

#### 18.2.5. 8-Bit Pulse Width Modulator Mode

Each module can be used independently to generate a pulse width modulated (PWM) output on its associated CEXn pin. The frequency of the output is dependent on the timebase for the PCA counter/timer. The duty cycle of the PWM output signal is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 18.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register enables 8-Bit Pulse Width Modulator mode. The duty cycle for 8-Bit PWM Mode is given by Equation 18.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

### Equation 18.2. 8-Bit PWM Duty Cycle

$DutyCycle = \frac{(256 - PCA0CPHn)}{256}$

Using Equation 18.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to '0'.

Figure 18.8. PCA 8-Bit PWM Mode Diagram

| System Clock (Hz)      | PCA0CPL4 | Timeout Interval (ms) |

|------------------------|----------|-----------------------|

| 24,500,000             | 255      | 32.1                  |

| 24,500,000             | 128      | 16.2                  |

| 24,500,000             | 32       | 4.1                   |

| 18,432,000             | 255      | 42.7                  |

| 18,432,000             | 128      | 21.5                  |

| 18,432,000             | 32       | 5.5                   |

| 11,059,200             | 255      | 71.1                  |

| 11,059,200             | 128      | 35.8                  |

| 11,059,200             | 32       | 9.2                   |

| 3,062,500 <sup>2</sup> | 255      | 257                   |

| 3,062,500 <sup>2</sup> | 128      | 129.5                 |

| 3,062,500 <sup>2</sup> | 32       | 33.1                  |

| 32,000                 | 255      | 24576                 |

| 32,000                 | 128      | 12384                 |

| 32,000                 | 32       | 3168                  |

# Table 18.3. Watchdog Timer Timeout Intervals<sup>1</sup>

value of 0x00 at the update time.

2. Internal oscillator reset frequency.

# 20. C2 Interface

C8051F31x devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. See the C2 Interface Specification for details on the C2 protocol.

# 20.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

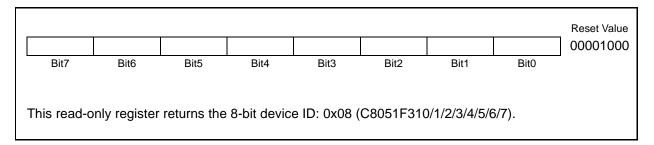

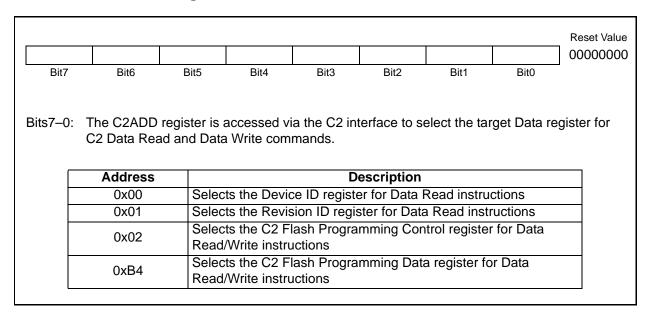

# C2 Register Definition 20.1. C2ADD: C2 Address

# C2 Register Definition 20.2. DEVICEID: C2 Device ID