Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                            |

| Peripherals                | POR, PWM, WDT                                                  |

| Number of I/O              | 21                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 24-WFQFN Exposed Pad                                           |

| Supplier Device Package    | 24-QFN (4x4)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f317-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

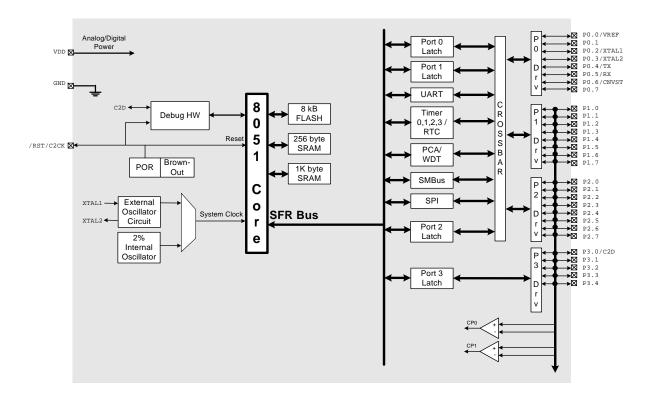

Figure 1.5. C8051F314 Block Diagram

### 5.3. Modes of Operation

ADC0 has a maximum conversion speed of 200 ksps. The ADC0 conversion clock is a divided version of the system clock, determined by the AD0SC bits in the ADC0CF register (system clock divided by (AD0SC + 1) for  $0 \le AD0SC \le 31$ ).

### 5.3.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2-0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a '1' to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 1 overflow

- 5. A rising edge on the CNVSTR input signal (pin P0.6)

- 6. A Timer 3 overflow

Writing a '1' to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). Note: When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. Note that when Timer 2 or Timer 3 overflows are used as the conversion source, Low Byte overflows are used if Timer 2/3 is in 8-bit mode; High byte overflows are used if Timer 2/3 is in 16-bit mode. See **Section "17. Timers" on page 187** for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.6. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.6 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.6, set to '1' Bit6 in register P0SKIP. See **Section "13. Port Input/Output" on page 129** for details on Port I/O configuration.

NOTES:

| R/W      | R/W                                           | R/W                                                           | R/W                                                                                                 | R/W                                                | R/W                          | R/W      | R/W    | Reset Value |  |  |  |  |

|----------|-----------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------|----------|--------|-------------|--|--|--|--|

| -        | -                                             | <b>CP0RIE</b>                                                 | CP0FIE                                                                                              | -                                                  | -                            | CP0MD1   | CP0MD0 | 0000001     |  |  |  |  |

| Bit7     | Bit6                                          | Bit5                                                          | Bit4                                                                                                | Bit3                                               | Bit2                         | Bit1     | Bit0   | SFR Addres  |  |  |  |  |

|          |                                               |                                                               |                                                                                                     |                                                    |                              |          |        | 0x9D        |  |  |  |  |

| 3its7–6: | UNUSED. F                                     | Read = $00b$ .                                                | Write = dor                                                                                         | i't care.                                          |                              |          |        |             |  |  |  |  |

| Bit5:    | CP0RIE: Co                                    | omparator R                                                   | ising-Edge                                                                                          | Interrupt En                                       | able.                        |          |        |             |  |  |  |  |

|          | 0: Compara                                    |                                                               |                                                                                                     |                                                    |                              |          |        |             |  |  |  |  |

|          | 1: Compara                                    | •                                                             | • •                                                                                                 |                                                    |                              |          |        |             |  |  |  |  |

| Bit4:    |                                               | •                                                             | • •                                                                                                 |                                                    | able.                        |          |        |             |  |  |  |  |

|          |                                               | •                                                             | CP0FIE: Comparator Falling-Edge Interrupt Enable.<br>0: Comparator falling-edge interrupt disabled. |                                                    |                              |          |        |             |  |  |  |  |

|          | 1: Comparator falling-edge interrupt enabled. |                                                               |                                                                                                     |                                                    |                              |          |        |             |  |  |  |  |

|          | 1: Compara                                    | •                                                             | •                                                                                                   |                                                    |                              |          |        |             |  |  |  |  |

| Bits1–0: |                                               | tor falling-ed                                                | dge interrup                                                                                        | t enabled.                                         | t                            |          |        |             |  |  |  |  |

| Bits1–0: | CP0MD1-C                                      | tor falling-eo<br>P0MD0: Co                                   | dge interrup<br>mparator0 l                                                                         | t enabled.<br>Mode Selec                           |                              |          |        |             |  |  |  |  |

| Bits1–0: |                                               | tor falling-eo<br>P0MD0: Co                                   | dge interrup<br>mparator0 l                                                                         | t enabled.<br>Mode Selec                           |                              |          |        |             |  |  |  |  |

| Bits1–0: | CP0MD1-C                                      | tor falling-eo<br>P0MD0: Co                                   | dge interrup<br>mparator0 l                                                                         | t enabled.<br>Mode Selec<br>e for Compa            |                              | ne (TYP) | ٦      |             |  |  |  |  |

| Bits1–0: | CP0MD1–C<br>These bits s                      | tor falling-ed<br>POMD0: Co<br>select the re                  | dge interrup<br>omparator0 l<br>sponse time                                                         | t enabled.<br>Mode Selec<br>e for Compa<br>CP0 Res | rator0.                      | . ,      | -      |             |  |  |  |  |

| Bits1–0: | CP0MD1–C<br>These bits s                      | tor falling-ed<br>POMD0: Co<br>select the re<br><b>CP0MD1</b> | dge interrup<br>omparator0 l<br>sponse time<br><b>CP0MD0</b>                                        | t enabled.<br>Mode Selec<br>e for Compa<br>CP0 Res | rator0.<br><b>sponse Tir</b> | . ,      | ]      |             |  |  |  |  |

| Bits1–0: | CP0MD1–C<br>These bits s<br>Mode              | tor falling-ed<br>POMD0: Co<br>select the re<br>CPOMD1<br>0   | dge interrup<br>omparator0 l<br>sponse time<br><b>CP0MD0</b><br>0                                   | t enabled.<br>Mode Selec<br>e for Compa<br>CP0 Res | rator0.<br><b>sponse Tir</b> | . ,      |        |             |  |  |  |  |

| R/W      | R                                      | R/W    | R/W    | R/W           | R/W           | R/W          | R/W        | Reset Value  |  |  |  |

|----------|----------------------------------------|--------|--------|---------------|---------------|--------------|------------|--------------|--|--|--|

| CP1EN    | CP10UT                                 | CP1RIF | CP1FIF | CP1HYP1       | CP1HYP0       | CP1HYN1      | CP1HYN0    | 00000000     |  |  |  |

| Bit7     | Bit6                                   | Bit5   | Bit4   | Bit3          | Bit2          | Bit1         | Bit0       | SFR Address: |  |  |  |

|          | 0x9A                                   |        |        |               |               |              |            |              |  |  |  |

|          |                                        |        |        |               |               |              |            |              |  |  |  |

| Bit7:    | ··· •································· |        |        |               |               |              |            |              |  |  |  |

|          | 0: Comparat                            |        |        |               |               |              |            |              |  |  |  |

| Dito     | 1: Comparat                            |        |        |               |               |              |            |              |  |  |  |

| Bit6:    | CP1OUT: Co                             |        |        | ate Flag.     |               |              |            |              |  |  |  |

|          | 0: Voltage or                          |        |        |               |               |              |            |              |  |  |  |

| D:45     | 1: Voltage or                          |        |        |               |               |              |            |              |  |  |  |

| Bit5:    | CP1RIF: Co                             |        |        |               |               | aa thia flag | waa laat a | loorod       |  |  |  |

|          | 0: No Compa                            |        |        |               |               | ce this hag  | was last c | leared.      |  |  |  |

| Bit4:    | 1: Comparat                            | -      | -      | •             |               |              |            |              |  |  |  |

| DIL4.    | CP1FIF: Cor                            |        |        |               |               | an thin flag |            | loorod       |  |  |  |

|          | 0: No Comparat                         |        |        |               |               | ice this hay | was last ( | leareu.      |  |  |  |

| Bits3-2: | 1: Comparat<br>CP1HYP1–0               | -      | -      | •             |               | c.           |            |              |  |  |  |

| DII53-2. | 00: Positive                           |        |        | le riysteresi |               | 5.           |            |              |  |  |  |

|          | 00: Positive                           |        |        |               |               |              |            |              |  |  |  |

|          | 10: Positive                           | •      |        |               |               |              |            |              |  |  |  |

|          | 11: Positive I                         |        |        |               |               |              |            |              |  |  |  |

| Bits1–0: | CP1HYN1-0                              |        |        | ive Hysteres  | sis Control B | its          |            |              |  |  |  |

| Ditor 0. | 00: Negative                           | •      | -      | •             |               | 110.         |            |              |  |  |  |

|          | 01: Negative                           |        |        |               |               |              |            |              |  |  |  |

|          | 10: Negative                           |        |        |               |               |              |            |              |  |  |  |

|          | 11: Negative                           |        |        |               |               |              |            |              |  |  |  |

|          |                                        |        |        |               |               |              |            |              |  |  |  |

|          |                                        |        |        |               |               |              |            |              |  |  |  |

### SFR Definition 7.4. CPT1CN: Comparator1 Control

| Mnemonic           | Description                              | Bytes | Clock<br>Cycles |

|--------------------|------------------------------------------|-------|-----------------|

| ORL A, direct      | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri         | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data       | OR immediate to A                        | 2     | 2               |

| ORL direct, A      | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data  | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn          | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct      | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri         | Exclusive-OR indirect RAM to A           | 1     | 2               |

| XRL A, #data       | Exclusive-OR immediate to A              | 2     | 2               |

| XRL direct, A      | Exclusive-OR A to direct byte            | 2     | 2               |

| XRL direct, #data  | Exclusive-OR immediate to direct byte    | 3     | 3               |

| CLR A              | Clear A                                  | 1     | 1               |

| CPL A              | Complement A                             | 1     | 1               |

| RL A               | Rotate A left                            | 1     | 1               |

| RLC A              | Rotate A left through Carry              | 1     | 1               |

| RR A               | Rotate A right                           | 1     | 1               |

| RRC A              | Rotate A right through Carry             | 1     | 1               |

| SWAP A             | Swap nibbles of A                        | 1     | 1               |

|                    | Data Transfer                            |       |                 |

| MOV A, Rn          | Move Register to A                       | 1     | 1               |

| MOV A, direct      | Move direct byte to A                    | 2     | 2               |

| MOV A, @Ri         | Move indirect RAM to A                   | 1     | 2               |

| MOV A, #data       | Move immediate to A                      | 2     | 2               |

| MOV Rn, A          | Move A to Register                       | 1     | 1               |

| MOV Rn, direct     | Move direct byte to Register             | 2     | 2               |

| MOV Rn, #data      | Move immediate to Register               | 2     | 2               |

| MOV direct, A      | Move A to direct byte                    | 2     | 2               |

| MOV direct, Rn     | Move Register to direct byte             | 2     | 2               |

| MOV direct, direct | Move direct byte to direct byte          | 3     | 3               |

| MOV direct, @Ri    | Move indirect RAM to direct byte         | 2     | 2               |

| MOV direct, #data  | Move immediate to direct byte            | 3     | 3               |

| MOV @Ri, A         | Move A to indirect RAM                   | 1     | 2               |

| MOV @Ri, direct    | Move direct byte to indirect RAM         | 2     | 2               |

| MOV @Ri, #data     | Move immediate to indirect RAM           | 2     | 2               |

| MOV DPTR, #data16  | Load DPTR with 16-bit constant           | 3     | 3               |

| MOVC A, @A+DPTR    | Move code byte relative DPTR to A        | 1     | 3               |

| MOVC A, @A+PC      | Move code byte relative PC to A          | 1     | 3               |

| MOVX A, @Ri        | Move external data (8-bit address) to A  | 1     | 3               |

| MOVX @Ri, A        | Move A to external data (8-bit address)  | 1     | 3               |

| MOVX A, @DPTR      | Move external data (16-bit address) to A | 1     | 3               |

| MOVX @DPTR, A      | Move A to external data (16-bit address) | 1     | 3               |

| PUSH direct        | Push direct byte onto stack              | 2     | 2               |

| POP direct         | Pop direct byte from stack               | 2     | 2               |

| XCH A, Rn          | Exchange Register with A                 | 1     | 1               |

| XCH A, direct      | Exchange direct byte with A              | 2     | 2               |

### Table 8.1. CIP-51 Instruction Set Summary (Continued)

|       | DAM            |               |                |                |               |            |               |              |

|-------|----------------|---------------|----------------|----------------|---------------|------------|---------------|--------------|

| R/W   | R/W<br>PSPI0   | R/W<br>PT2    | R/W<br>PS0     | R/W<br>PT1     | R/W<br>PX1    | R/W<br>PT0 | R/W<br>PX0    | Reset Value  |

| -     |                |               |                |                |               |            |               |              |

| Bit7  | Bit6           | Bit5          | Bit4           | Bit3           | Bit2          | Bit1       | Bit0          | SFR Address: |

|       |                |               |                |                |               | (bi        | t addressable | e) 0xB8      |

| Bit7: | UNUSED. R      | ead – 1 W     | rite – don't i | care           |               |            |               |              |

| Bit6: | PSPI0: Seria   |               |                |                | rupt Priority |            |               |              |

| Bito. | This bit sets  | •             |                | · /            | rupt i nonty  | Control.   |               |              |

|       | 0: SPI0 inter  |               |                |                |               |            |               |              |

|       | 1: SPI0 inter  |               |                |                |               |            |               |              |

| Bit5: | PT2: Timer 2   | •             | • • •          |                |               |            |               |              |

| 2.101 | This bit sets  |               |                |                | t.            |            |               |              |

|       | 0: Timer 2 in  |               |                |                |               |            |               |              |

|       | 1: Timer 2 in  |               |                |                |               |            |               |              |

| Bit4: | PS0: UARTO     |               |                |                |               |            |               |              |

|       | This bit sets  |               |                |                | t.            |            |               |              |

|       | 0: UART0 int   | terrupts se   | t to low prior | ity level.     |               |            |               |              |

|       | 1: UART0 int   | terrupts se   | t to high pric | ority level.   |               |            |               |              |

| Bit3: | PT1: Timer 1   | Interrupt I   | Priority Cont  | rol.           |               |            |               |              |

|       | This bit sets  | the priority  | of the Time    | r 1 interrup   | t.            |            |               |              |

|       | 0: Timer 1 in  | terrupts se   | t to low prio  | rity level.    |               |            |               |              |

|       | 1: Timer 1 in  | terrupts se   | t to high prio | ority level.   |               |            |               |              |

| Bit2: | PX1: Externa   | al Interrupt  | 1 Priority C   | ontrol.        |               |            |               |              |

|       | This bit sets  | the priority  | of the Exte    | rnal Interruj  | ot 1 interrup | ot.        |               |              |

|       | 0: External Ir |               |                |                |               |            |               |              |

|       | 1: External Ir | nterrupt 1 s  | set to high p  | riority level. |               |            |               |              |

| Bit1: | PT0: Timer 0   | ) Interrupt I | Priority Cont  | rol.           |               |            |               |              |

|       | This bit sets  |               |                |                | t.            |            |               |              |

|       | 0: Timer 0 in  |               |                |                |               |            |               |              |

|       | 1: Timer 0 in  | •             | • •            |                |               |            |               |              |

| Bit0: | PX0: Externa   |               |                |                |               |            |               |              |

|       | This bit sets  |               |                |                | ot 0 interrup | ot.        |               |              |

|       | 0: External Ir |               |                |                |               |            |               |              |

|       | 1: External Ir | nterrupt 0 s  | set to high p  | riority level. |               |            |               |              |

### SFR Definition 8.8. IP: Interrupt Priority

### 8.4.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100  $\mu$ sec.

| R/W                                                                                                             | R/W            | R/W            | R/W          | R/W            | R/W          | R/W           | R/W           | Reset Value  |  |  |

|-----------------------------------------------------------------------------------------------------------------|----------------|----------------|--------------|----------------|--------------|---------------|---------------|--------------|--|--|

| GF5                                                                                                             | GF4            | GF3            | GF2          | GF1            | GF0          | STOP          | IDLE          | 00000000     |  |  |

| Bit7                                                                                                            | Bit6           | Bit5           | Bit4         | Bit3           | Bit2         | Bit1          | Bit0          | SFR Address: |  |  |

|                                                                                                                 |                |                |              |                |              |               |               | 0x87         |  |  |

|                                                                                                                 |                |                |              |                |              |               |               |              |  |  |

| Bits7–2: GF5–GF0: General Purpose Flags 5–0.<br>These are general purpose flags for use under software control. |                |                |              |                |              |               |               |              |  |  |

|                                                                                                                 | -              |                | -            | r use under    | software c   | ontrol.       |               |              |  |  |

| Bit1:                                                                                                           | STOP: Stop     |                |              |                |              |               |               |              |  |  |

|                                                                                                                 | Setting this b | •              |              | •              |              | t will always | be read a     | s 0.         |  |  |

|                                                                                                                 | 1: CPU goes    | •              | •            | nal oscillato  | r stopped).  |               |               |              |  |  |

| Bit0:                                                                                                           | IDLE: Idle M   | ode Select.    |              |                |              |               |               |              |  |  |

|                                                                                                                 | Setting this b | bit will place | e the CIP-51 | in Idle mod    | de. This bit | will always   | be read as    | s 0.         |  |  |

|                                                                                                                 | 1: CPU goes    | s into Idle m  | ode. (Shuts  | s off clock to | CPU, but o   | clock to Tim  | iers, Interru | upts, Serial |  |  |

|                                                                                                                 | Ports, and A   | nalog Perip    | herals are s | still active.) |              |               |               |              |  |  |

|                                                                                                                 |                |                |              |                |              |               |               |              |  |  |

### SFR Definition 8.12. PCON: Power Control

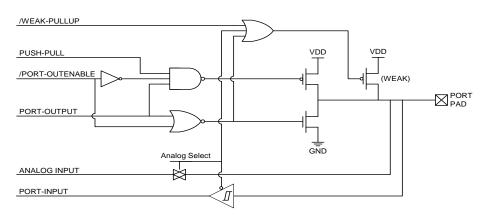

Figure 13.2. Port I/O Cell Block Diagram

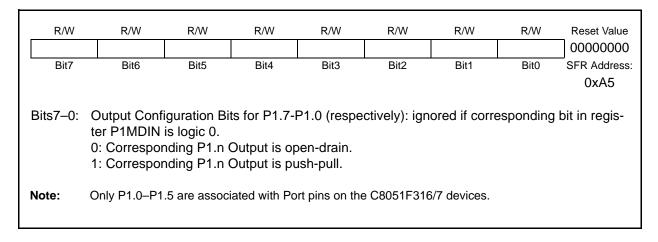

### SFR Definition 13.9. P1MDOUT: Port1 Output Mode

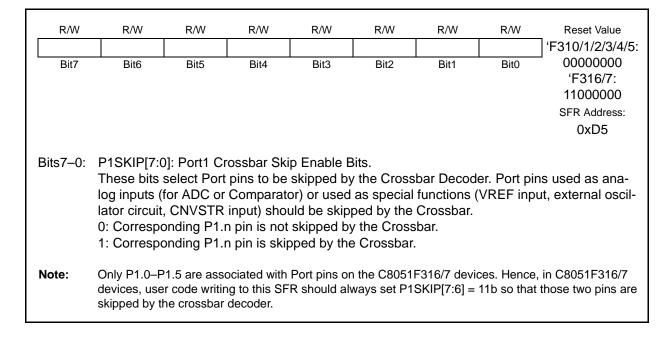

### SFR Definition 13.10. P1SKIP: Port1 Skip

| R/W      | R/W                        | R         | R/W                            | R/W          | R/W          | R/W          | R/W           | Reset Value  |

|----------|----------------------------|-----------|--------------------------------|--------------|--------------|--------------|---------------|--------------|

| ENSME    | 3 INH                      | BUSY      | EXTHOLD                        | SMBTOE       | SMBFTE       | SMBCS1       | SMBCS0        | 00000000     |

| Bit7     | Bit6                       | Bit5      | Bit4                           | Bit3         | Bit2         | Bit1         | Bit0          | _            |

|          |                            |           |                                |              |              |              | SFR Address   | : 0xC1       |

| D'/7     |                            |           | L.                             |              |              |              |               |              |

| Bit7:    | ENSMB: SM                  |           | ie.<br>es the SMBu             | o intorfago  | When one     | blad tha int | orfood oond   | toptlymon    |

|          | itors the SD/              |           |                                | s interface. | when ena     | olea, the m  | enace cons    | lanuy mon-   |

|          | 0: SMBus in                |           |                                |              |              |              |               |              |

|          | 1: SMBus in                |           |                                |              |              |              |               |              |

| Bit6:    | INH: SMBus                 | Slave Inh | ibit.                          |              |              |              |               |              |

|          |                            |           | ogic 1, the S                  |              |              |              |               |              |

|          |                            |           | removes the                    | SMBus slav   | ve from the  | bus. Maste   | r Mode inte   | rrupts are   |

|          | not affected.              |           |                                |              |              |              |               |              |

|          | 0: SMBus SI<br>1: SMBus SI |           |                                |              |              |              |               |              |

| Bit5:    | BUSY: SMB                  |           |                                |              |              |              |               |              |

| Dito:    |                            |           | by hardware                    | when a tra   | ansfer is in | progress. It | is cleared t  | o logic 0    |

|          |                            |           | imeout is ser                  |              |              |              |               | 0            |

| Bit4:    |                            |           | tup and Hold                   |              |              |              |               |              |

|          |                            |           | DA setup and                   |              | •            | to Table 14. | .2.           |              |

|          |                            |           | p and Hold T                   |              |              |              |               |              |

| Bit3:    |                            |           | p and Hold T<br>_ Timeout De   |              |              |              |               |              |

| Dito.    |                            |           | ow timeout de                  |              |              | 1 the SMB    | us forces Tir | mer 3 to     |

|          |                            |           | gh and allows                  |              | •            |              |               |              |

|          |                            |           | 3SPLIT is se                   |              |              |              |               |              |

|          |                            |           | hould be prog                  |              |              |              |               | l the        |

| DVA      |                            | •         | ce routine sho                 |              |              | munication.  |               |              |

| Bit2:    |                            |           | e Timeout De                   |              |              |              |               | ain hinh far |

|          |                            |           | ogic 1, the bu<br>clock source |              | nsidered ire | e il SCL an  | a SDA lema    | ain nigh ior |

| Bits1–0: |                            |           | MBus Clock S                   |              | ection.      |              |               |              |

|          |                            |           | he SMBus clo                   |              |              | sed to gene  | rate the SM   | IBus bit     |

|          |                            |           | ice should be                  |              |              | -            |               |              |

### SFR Definition 14.1. SMB0CF: SMBus Clock/Configuration

| SMBCS1 | SMBCS0 | SMBus Clock Source         |

|--------|--------|----------------------------|

| 0      | 0      | Timer 0 Overflow           |

| 0      | 1      | Timer 1 Overflow           |

| 1      | 0      | Timer 2 High Byte Overflow |

| 1      | 1      | Timer 2 Low Byte Overflow  |

### 14.4.2. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information (see SFR Definition 14.2). The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER and TXMODE indicate the master/slave state and transmit/receive modes, respectively.

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a '1' to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a '1' to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 14.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

Table 14.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 14.4 for SMBus status decoding using the SMB0CN register.

|                | Frequency: 24.5 MHz          |                      |                                  |                       |                                     |      |                                  |  |  |  |

|----------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|--|--|--|

|                | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload Value<br>(hex) |  |  |  |

|                | 230400                       | -0.32%               | 106                              | SYSCLK                | XX                                  | 1    | 0xCB                             |  |  |  |

|                | 115200                       | -0.32%               | 212                              | SYSCLK                | XX                                  | 1    | 0x96                             |  |  |  |

|                | 57600                        | 0.15%                | 426                              | SYSCLK                | XX                                  | 1    | 0x2B                             |  |  |  |

| from<br>Ssc.   | 28800                        | -0.32%               | 848                              | SYSCLK / 4            | 01                                  | 0    | 0x96                             |  |  |  |

| < froi<br>Osc. | 14400                        | 0.15%                | 1704                             | SYSCLK / 12           | 00                                  | 0    | 0xB9                             |  |  |  |

|                | 9600                         | -0.32%               | 2544                             | SYSCLK / 12           | 00                                  | 0    | 0x96                             |  |  |  |

| SYSCL          | 2400                         | -0.32%               | 10176                            | SYSCLK / 48           | 10                                  | 0    | 0x96                             |  |  |  |

| SY<br>Int      | 1200                         | 0.15%                | 20448                            | SYSCLK / 48           | 10                                  | 0    | 0x2B                             |  |  |  |

# Table 15.1. Timer Settings for Standard Baud RatesUsing the Internal Oscillator

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in **Section 17.1**.

# Table 15.2. Timer Settings for Standard Baud RatesUsing an External 25 MHz Oscillator

|                      |                              |                      | Fre                              | quency: 25.0 M        | lHz                                 |      |                                  |

|----------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|

|                      | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload Value<br>(hex) |

|                      | 230400                       | -0.47%               | 108                              | SYSCLK                | XX                                  | 1    | 0xCA                             |

|                      | 115200                       | 0.45%                | 218                              | SYSCLK                | XX                                  | 1    | 0x93                             |

|                      | 57600                        | -0.01%               | 434                              | SYSCLK                | XX                                  | 1    | 0x27                             |

| from<br>Osc.         | 28800                        | 0.45%                | 872                              | SYSCLK / 4            | 01                                  | 0    | 0x93                             |

|                      | 14400                        | -0.01%               | 1736                             | SYSCLK/4              | 01                                  | 0    | 0x27                             |

| XLK<br>Jal           | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                  | 0    | 0x5D                             |

| SYSCLK<br>External   | 2400                         | 0.45%                | 10464                            | SYSCLK / 48           | 10                                  | 0    | 0x93                             |

| S ≺                  | 1200                         | -0.01%               | 20832                            | SYSCLK / 48           | 10                                  | 0    | 0x27                             |

| ε.                   | 57600                        | -0.47%               | 432                              | EXTCLK / 8            | 11                                  | 0    | 0xE5                             |

| < from<br>Osc.       | 28800                        | -0.47%               | 864                              | EXTCLK / 8            | 11                                  | 0    | 0xCA                             |

|                      | 14400                        | 0.45%                | 1744                             | EXTCLK / 8            | 11                                  | 0    | 0x93                             |

| SYSCLK<br>Internal C | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                  | 0    | 0x5D                             |

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in Section 17.1.

|                                     |                              |                      | Freq                             | uency: 22.1184        | MHz                                 |      |                                  |

|-------------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|

|                                     | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload Value<br>(hex) |

|                                     | 230400                       | 0.00%                | 96                               | SYSCLK                | XX                                  | 1    | 0xD0                             |

|                                     | 115200                       | 0.00%                | 192                              | SYSCLK                | XX                                  | 1    | 0xA0                             |

|                                     | 57600                        | 0.00%                | 384                              | SYSCLK                | XX                                  | 1    | 0x40                             |

| С<br>С.                             | 28800                        | 0.00%                | 768                              | SYSCLK / 12           | 00                                  | 0    | 0xE0                             |

| ( from<br>Osc.                      | 14400                        | 0.00%                | 1536                             | SYSCLK / 12           | 00                                  | 0    | 0xC0                             |

| 2Lk<br>nal                          | 9600                         | 0.00%                | 2304                             | SYSCLK / 12           | 00                                  | 0    | 0xA0                             |

| 'SC<br>ter                          | 2400                         | 0.00%                | 9216                             | SYSCLK / 48           | 10                                  | 0    | 0xA0                             |

| SYSCLK<br>External                  | 1200                         | 0.00%                | 18432                            | SYSCLK / 48           | 10                                  | 0    | 0x40                             |

|                                     | 230400                       | 0.00%                | 96                               | EXTCLK / 8            | 11                                  | 0    | 0xFA                             |

| E                                   | 115200                       | 0.00%                | 192                              | EXTCLK / 8            | 11                                  | 0    | 0xF4                             |

| <ul><li>froi</li><li>Osc.</li></ul> | 57600                        | 0.00%                | 384                              | EXTCLK / 8            | 11                                  | 0    | 0xE8                             |

| <u> </u>                            | 28800                        | 0.00%                | 768                              | EXTCLK / 8            | 11                                  | 0    | 0xD0                             |

| SYSCL<br>Internal                   | 14400                        | 0.00%                | 1536                             | EXTCLK / 8            | 11                                  | 0    | 0xA0                             |

| SY<br>Inte                          | 9600                         | 0.00%                | 2304                             | EXTCLK / 8            | 11                                  | 0    | 0x70                             |

# Table 15.3. Timer Settings for Standard Baud RatesUsing an External 22.1184 MHz Oscillator

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in Section 17.1.

| Table 15.4. Timer Settings for Standard Baud Rates |

|----------------------------------------------------|

| Using an External 18.432 MHz Oscillator            |

|                                | Frequency: 18.432 MHz        |                      |                                  |                       |                                     |      |                                  |  |  |  |

|--------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|--|--|--|

|                                | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |  |  |  |

|                                | 230400                       | 0.00%                | 80                               | SYSCLK                | XX                                  | 1    | 0xD8                             |  |  |  |

|                                | 115200                       | 0.00%                | 160                              | SYSCLK                | XX                                  | 1    | 0xB0                             |  |  |  |

|                                | 57600                        | 0.00%                | 320                              | SYSCLK                | XX                                  | 1    | 0x60                             |  |  |  |

| from<br>Osc.                   | 28800                        | 0.00%                | 640                              | SYSCLK / 4            | 01                                  | 0    | 0xB0                             |  |  |  |

| ( fro<br>Os                    | 14400                        | 0.00%                | 1280                             | SYSCLK / 4            | 01                                  | 0    | 0x60                             |  |  |  |

| CLK<br>nal                     | 9600                         | 0.00%                | 1920                             | SYSCLK / 12           | 00                                  | 0    | 0xB0                             |  |  |  |

| SYSCLK<br>External (           | 2400                         | 0.00%                | 7680                             | SYSCLK / 48           | 10                                  | 0    | 0xB0                             |  |  |  |

| Ϋ́́                            | 1200                         | 0.00%                | 15360                            | SYSCLK / 48           | 10                                  | 0    | 0x60                             |  |  |  |

| SYSCLK from<br>Internal Osc.   | 230400                       | 0.00%                | 80                               | EXTCLK / 8            | 11                                  | 0    | 0xFB                             |  |  |  |

|                                | 115200                       | 0.00%                | 160                              | EXTCLK / 8            | 11                                  | 0    | 0xF6                             |  |  |  |

|                                | 57600                        | 0.00%                | 320                              | EXTCLK / 8            | 11                                  | 0    | 0xEC                             |  |  |  |

|                                | 28800                        | 0.00%                | 640                              | EXTCLK / 8            | 11                                  | 0    | 0xD8                             |  |  |  |

| SYSCL <sup>k</sup><br>Internal | 14400                        | 0.00%                | 1280                             | EXTCLK / 8            | 11                                  | 0    | 0xB0                             |  |  |  |

| SY<br>Int                      | 9600                         | 0.00%                | 1920                             | EXTCLK / 8            | 11                                  | 0    | 0x88                             |  |  |  |

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in Section 17.1.

### 16.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

### 16.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

### 16.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

### 16.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

### 16.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

- NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 16.2, Figure 16.3, and Figure 16.4 for typical connection diagrams of the various operational modes. Note that the setting of NSSMD bits affects the pinout of the device. When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "13. Port Input/Output" on page 129 for general purpose port I/O and crossbar information.

### 17.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

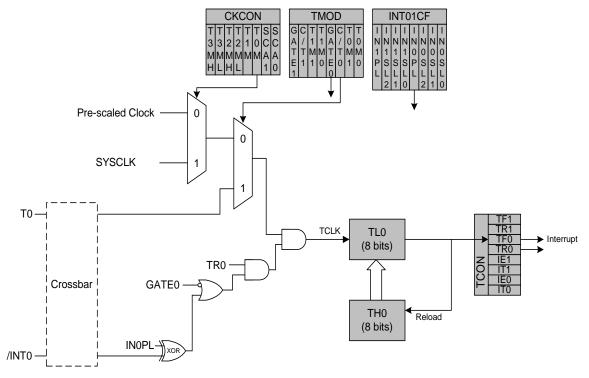

### 17.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal /INT0 is active as defined by bit IN0PL in register IT01CF (see **Section "8.3.2. External Interrupts" on page 95** for details on the external input signals /INT0 and /INT1).

Figure 17.2. T0 Mode 2 Block Diagram

| SFR Definition | 17.1. | TCON: | Timer | Control |

|----------------|-------|-------|-------|---------|

|----------------|-------|-------|-------|---------|

| R/W   | R/W                                                                                                                                                                                        | R/W          | R/W          | R/W          | R/W            | R/W          | R/W           | Reset Valu   |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|----------------|--------------|---------------|--------------|--|--|--|--|

| TF1   | TR1                                                                                                                                                                                        | TF0          | TR0          | IE1          | IT1            | IE0          | IT0           | 0000000      |  |  |  |  |

| Bit7  | Bit6                                                                                                                                                                                       | Bit5         | Bit4         | Bit3         | Bit2           | Bit1         | Bit0          | SFR Addre    |  |  |  |  |

|       |                                                                                                                                                                                            |              |              |              |                | (bi          | t addressable | e) 0x88      |  |  |  |  |

|       |                                                                                                                                                                                            |              |              |              |                |              |               |              |  |  |  |  |

| Sit7: | TF1: Timer 1                                                                                                                                                                               |              | -            |              | flan ann ba    |              |               | h            |  |  |  |  |

|       | Set by hardware when Timer 1 overflows. This flag can be cleared by software but is auto matically cleared when the CPU vectors to the Timer 1 interrupt service routine.                  |              |              |              |                |              |               |              |  |  |  |  |

|       |                                                                                                                                                                                            |              |              | ctors to the | i imer i int   | errupt servi | ce routine    | •            |  |  |  |  |

|       | 0: No Timer<br>1: Timer 1 ha                                                                                                                                                               |              |              |              |                |              |               |              |  |  |  |  |

| Bit6: | TR1: Timer 1                                                                                                                                                                               |              |              |              |                |              |               |              |  |  |  |  |

| nio.  | 0: Timer 1 di                                                                                                                                                                              |              | 101.         |              |                |              |               |              |  |  |  |  |

|       | 1: Timer 1 er                                                                                                                                                                              |              |              |              |                |              |               |              |  |  |  |  |

| Bit5: | TF0: Timer 0                                                                                                                                                                               |              | Flag         |              |                |              |               |              |  |  |  |  |

|       | Set by hardw                                                                                                                                                                               |              | -            | rflows. This | s flag can be  | e cleared by | / software    | but is auto  |  |  |  |  |

|       | matically clea                                                                                                                                                                             |              |              |              |                |              |               |              |  |  |  |  |

|       | 0: No Timer (                                                                                                                                                                              |              |              |              |                |              |               |              |  |  |  |  |

|       | 1: Timer 0 ha                                                                                                                                                                              | as overflow  | ed.          |              |                |              |               |              |  |  |  |  |

| Bit4: | TR0: Timer C                                                                                                                                                                               | Run Conti    | rol.         |              |                |              |               |              |  |  |  |  |

|       | 0: Timer 0 di                                                                                                                                                                              | sabled.      |              |              |                |              |               |              |  |  |  |  |

|       | 1: Timer 0 er                                                                                                                                                                              | nabled.      |              |              |                |              |               |              |  |  |  |  |

| Bit3: | IE1: External                                                                                                                                                                              | •            |              |              |                |              |               |              |  |  |  |  |

|       | This flag is s                                                                                                                                                                             |              |              |              |                |              |               |              |  |  |  |  |

|       | cleared by software but is automatically cleared when the CPU vectors to the External Inter                                                                                                |              |              |              |                |              |               |              |  |  |  |  |

|       | rupt 1 service routine if IT1 = 1. When IT1 = 0, this flag is set to '1' when /INT1 is active as                                                                                           |              |              |              |                |              |               |              |  |  |  |  |

|       | defined by bit IN1PL in register IT01CF (see SFR Definition 8.11).                                                                                                                         |              |              |              |                |              |               |              |  |  |  |  |

| Bit2: | IT1: Interrupt 1 Type Select.                                                                                                                                                              |              |              |              |                |              |               |              |  |  |  |  |

|       | This bit selects whether the configured /INT1 interrupt will be edge or level sensitive. /INT is configured active low or high by the IN1PL bit in the IT01CF register (see SFR Definition |              |              |              |                |              |               |              |  |  |  |  |

|       | 8.11).                                                                                                                                                                                     | active low   | or high by t |              |                | ICF registe  | el (See SF    |              |  |  |  |  |

|       | 0: /INT1 is le                                                                                                                                                                             | vel triggere | hd           |              |                |              |               |              |  |  |  |  |

|       | 1: /INT1 is ed                                                                                                                                                                             |              |              |              |                |              |               |              |  |  |  |  |

| Bit1: | IE0: External                                                                                                                                                                              | 0 00         |              |              |                |              |               |              |  |  |  |  |

| Ditt: | This flag is s                                                                                                                                                                             | •            |              | n edae/leve  | el of type de  | fined by IT( | ) is detecte  | ed. It can b |  |  |  |  |

|       | cleared by so                                                                                                                                                                              |              |              |              |                |              |               |              |  |  |  |  |

|       | rupt 0 service                                                                                                                                                                             |              |              |              |                |              |               |              |  |  |  |  |

|       | defined by bi                                                                                                                                                                              |              |              |              |                |              |               |              |  |  |  |  |

| BitO: | IT0: Interrupt                                                                                                                                                                             | t 0 Type Se  | lect.        |              |                |              |               |              |  |  |  |  |

|       | This bit selec                                                                                                                                                                             |              |              |              |                |              |               |              |  |  |  |  |

|       | is configured                                                                                                                                                                              | active low   | or high by t | he IN0PL b   | oit in registe | r IT01CF (s  | ee SFR D      | efinition    |  |  |  |  |

|       | 8.11).                                                                                                                                                                                     |              |              |              |                |              |               |              |  |  |  |  |

|       | 0: /INT0 is le                                                                                                                                                                             |              |              |              |                |              |               |              |  |  |  |  |

|       | 1: /INT0 is ed                                                                                                                                                                             |              |              |              |                |              |               |              |  |  |  |  |

|       |                                                                                                                                                                                            | dge triggere | ea.          |              |                |              |               |              |  |  |  |  |

### 18. Programmable Counter Array

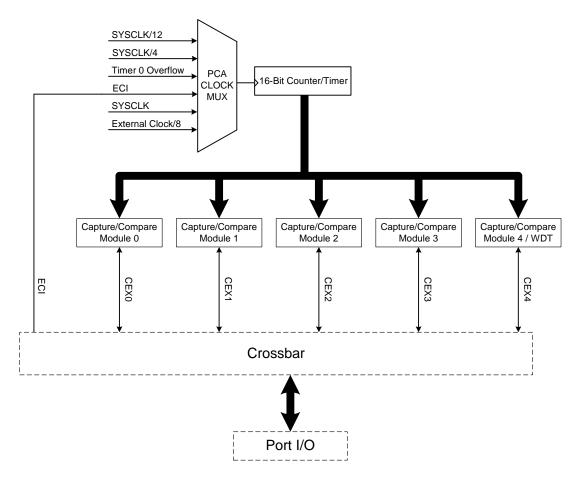

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and five 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled (See Section "13.1. Priority Crossbar Decoder" on page 131 for details on configuring the Crossbar). The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM (each mode is described in Section "18.2. Capture/Compare Modules" on page 205). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 18.1

**Important Note:** The PCA Module 4 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See **Section 18.3** for details.

Figure 18.1. PCA Block Diagram

### 18.4. Register Descriptions for PCA

Following are detailed descriptions of the special function registers related to the operation of the PCA.

| R/W      | R/W                                                                                                                                                                                  | R/W         | R/W           | R/W           | R/W          | R/W           | R/W           | Reset Value  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|---------------|--------------|---------------|---------------|--------------|--|--|--|

| CF       | CR                                                                                                                                                                                   |             | CCF4          | CCF3          | CCF2         | CCF1          | CCF0          | 00000000     |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                 | Bit5        | Bit4          | Bit3          | Bit2         | Bit1          | Bit0          | SFR Address  |  |  |  |

|          |                                                                                                                                                                                      |             |               |               |              | (bi           | t addressable | ) 0xD8       |  |  |  |

|          |                                                                                                                                                                                      |             |               |               |              |               |               |              |  |  |  |

| Bit7:    | CF: PCA Co                                                                                                                                                                           |             |               | 0             |              | 。 ===         | -             |              |  |  |  |

|          | Set by hardw                                                                                                                                                                         |             |               |               |              |               |               |              |  |  |  |

|          | Counter/Tim                                                                                                                                                                          |             | · · ·         | •             |              |               |               |              |  |  |  |

|          | to the PCA in<br>must be clear                                                                                                                                                       | •           |               | . This dillis | not automa   | alically clea | red by hard   | ware and     |  |  |  |

| Bit6:    | CR: PCA Co                                                                                                                                                                           |             |               | ol            |              |               |               |              |  |  |  |

| Bito.    | This bit enab                                                                                                                                                                        |             |               |               | her          |               |               |              |  |  |  |

|          | 0: PCA Cour                                                                                                                                                                          |             |               |               |              |               |               |              |  |  |  |