Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                             |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 21                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                            |

| Supplier Device Package    | 24-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f317-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F310/1/2/3/4/5/6/7

| 8.3.4. Interrupt Latency                                           | 95  |

|--------------------------------------------------------------------|-----|

| 8.3.5. Interrupt Register Descriptions                             |     |

| 8.4. Power Management Modes                                        |     |

| 8.4.1. Idle Mode                                                   |     |

| 8.4.2. Stop Mode                                                   |     |

| 9. Reset Sources                                                   |     |

| 9.1. Power-On Reset                                                | 106 |

| 9.2. Power-Fail Reset / V <sub>DD</sub> Monitor                    | 106 |

| 9.3. External Reset                                                |     |

| 9.4. Missing Clock Detector Reset                                  | 108 |

| 9.5. Comparator0 Reset                                             | 108 |

| 9.6. PCA Watchdog Timer Reset                                      | 108 |

| 9.7. Flash Error Reset                                             | 108 |

| 9.8. Software Reset                                                | 108 |

| 10. Flash Memory                                                   |     |

| 10.1.Programming The Flash Memory                                  |     |

| 10.1.1.Flash Lock and Key Functions                                |     |

| 10.1.2.Flash Erase Procedure                                       |     |

| 10.1.3.Flash Write Procedure                                       |     |

| 10.2.Non-volatile Data Storage                                     |     |

| 10.3.Security Options                                              | 113 |

| 10.4.Flash Write and Erase Guidelines                              | 115 |

| 10.4.1.V <sub>DD</sub> Maintenance and the V <sub>DD</sub> Monitor | 115 |

| 10.4.2.PSWE Maintenance                                            |     |

| 10.4.3.System Clock                                                |     |

| 11. External RAM<br>12. Oscillators                                |     |

| 12.1.Programmable Internal Oscillator                              |     |

| 12.2.External Oscillator Drive Circuit                             | 121 |

| 12.3.System Clock Selection                                        |     |

| 12.4.External Crystal Example                                      |     |

| 12.5.External RC Example                                           |     |

| 12.6.External Capacitor Example                                    |     |

| 13. Port Input/Output                                              |     |

| 13.1.Priority Crossbar Decoder                                     |     |

| 13.2.Port I/O Initialization                                       |     |

| 13.3.General Purpose Port I/O                                      |     |

| 14. SMBus                                                          |     |

| 14.1.Supporting Documents                                          |     |

| 14.2.SMBus Configuration                                           |     |

| 14.3.SMBus Operation                                               |     |

| 14.3.1.Arbitration                                                 |     |

| 14.3.2.Clock Low Extension                                         | 148 |

| 14.3.3.SCL Low Timeout                                             |     |

| 14.3.4.SCL High (SMBus Free) Timeout                               | 148 |

| Ordering Part Number | MIPS (Peak) | Flash Memory | RAM  | Calibrated Internal 24.5 MHz Oscillator | SMBus/I2C    | Enhanced SPI | UART         | Timers (16-bit) | Programmable Counter Array | Digital Port I/Os | 10-bit 200 ksps ADC | Temperature Sensor | Analog Comparators | Lead-free (RoHS Compliant) | Package |

|----------------------|-------------|--------------|------|-----------------------------------------|--------------|--------------|--------------|-----------------|----------------------------|-------------------|---------------------|--------------------|--------------------|----------------------------|---------|

| C8051F310            | 25          | 16           | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$    | $\checkmark$               | 29                | $\checkmark$        | $\checkmark$       | 2                  | -                          | LQFP-32 |

| C8051F310-GQ         | 25          | 16           | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$    | $\checkmark$               | 29                | $\checkmark$        | $\checkmark$       | 2                  | $\checkmark$               | LQFP-32 |

| C8051F311            | 25          | 16           | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | ~            | $\checkmark$    | $\checkmark$               | 25                | $\checkmark$        | $\checkmark$       | 2                  | -                          | QFN-28  |

| C8051F311-GM         | 25          | 16           | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$    | $\checkmark$               | 25                | $\checkmark$        | $\checkmark$       | 2                  | $\checkmark$               | QFN-28  |

| C8051F312            | 25          | 8            | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$    | $\checkmark$               | 29                | ~                   | $\checkmark$       | 2                  | -                          | LQFP-32 |

| C8051F312-GQ         | 25          | 8            | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$    | $\checkmark$               | 29                | $\checkmark$        | $\checkmark$       | 2                  | $\checkmark$               | LQFP-32 |

| C8051F313            | 25          | 8            | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$    | $\checkmark$               | 25                | $\checkmark$        | $\checkmark$       | 2                  | -                          | QFN-28  |

| C8051F313-GM         | 25          | 8            | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | ~            | $\checkmark$    | $\checkmark$               | 25                | $\checkmark$        | $\checkmark$       | 2                  | $\checkmark$               | QFN-28  |

| C8051F314            | 25          | 8            | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$    | $\checkmark$               | 29                | -                   | -                  | 2                  | -                          | LQFP-32 |

| C8051F314-GQ         | 25          | 8            | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$    | $\checkmark$               | 29                | -                   | -                  | 2                  | $\checkmark$               | LQFP-32 |

| C8051F315            | 25          | 8            | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$    | $\checkmark$               | 25                | -                   | -                  | 2                  | -                          | QFN-28  |

| C8051F315-GM         | 25          | 8            | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | ~            | $\checkmark$    | $\checkmark$               | 25                | -                   | -                  | 2                  | $\checkmark$               | QFN-28  |

| C8051F316-GM         | 25          | 16           | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$    | $\checkmark$               | 21                | $\checkmark$        | $\checkmark$       | 2                  | $\checkmark$               | QFN-24  |

| C8051F317-GM         | 25          | 16           | 1280 | $\checkmark$                            | $\checkmark$ | $\checkmark$ | ~            | $\checkmark$    | $\checkmark$               | 21                | -                   | -                  | 2                  | $\checkmark$               | QFN-24  |

Table 1.1. Product Selection Guide

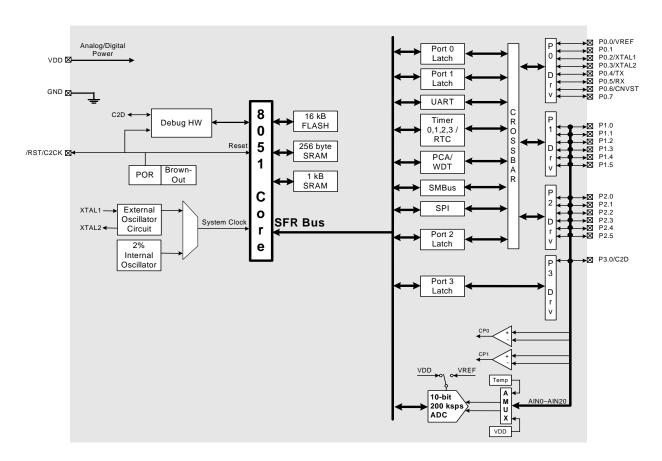

Figure 1.7. C8051F316 Block Diagram

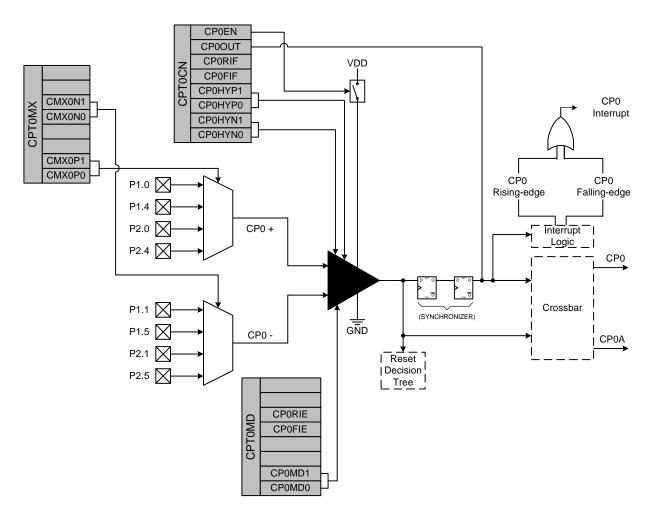

#### 1.8. Comparators

C8051F31x devices include two on-chip voltage comparators that are enabled/disabled and configured via user software. Port I/O pins may be configured as comparator inputs via a selection mux. Two comparator outputs may be routed to a Port pin if desired: a latched output and/or an unlatched (asynchronous) output. Comparator response time is programmable, allowing the user to select between high-speed and low-power modes. Positive and negative hysteresis are also configurable.

Comparator interrupts may be generated on rising, falling, or both edges. When in IDLE mode, these interrupts may be used as a "wake-up" source. Comparator0 may also be configured as a reset source. Figure 1.16 shows he Comparator0 block diagram.

Figure 1.16. Comparator0 Block Diagram

### Table 3.1. Global DC Electrical Characteristics (Continued)

-40°C to +85°C, 25 MHz System Clock unless otherwise specified.

| Parameter                                       | Conditions                                                  | Min                                                                                                                                                                                                                                                                                                                                                   | Тур      | Max  | Units  |

|-------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|--------|

| Digital Supply Current—CPU Inac                 | ctive (Idle Mode, not fetching instru                       | uctions                                                                                                                                                                                                                                                                                                                                               | from Fla | ish) |        |

| I <sub>DD</sub> (Note 3)                        | $V_{DD}$ = 3.0 V, F = 25 MHz                                |                                                                                                                                                                                                                                                                                                                                                       | 3.8      | 4.3  | mA     |

|                                                 | V <sub>DD</sub> = 3.0 V, F = 1 MHz                          | —                                                                                                                                                                                                                                                                                                                                                     | 0.20     | —    | mA     |

|                                                 | V <sub>DD</sub> = 3.0 V, F = 80 kHz                         | —                                                                                                                                                                                                                                                                                                                                                     | 16       | —    | μA     |

|                                                 | V <sub>DD</sub> = 3.6 V, F = 25 MHz                         | instructions from Flash)         —       3.8       4.3         —       0.20       —         —       16       —         —       16       —         —       4.8       5.3         —       44       —         25 °C       —       0.21       —       r         25 °C       —       0.15       —       r         25 °C       —       0.28       —       r | mA       |      |        |

| I <sub>DD</sub> Supply Sensitivity (Note 3,     | F = 25 MHz                                                  | —                                                                                                                                                                                                                                                                                                                                                     | 44       | _    | %/V    |

| Note 4)                                         | F = 1 MHz                                                   | _                                                                                                                                                                                                                                                                                                                                                     | 56       | _    | %/V    |

| I <sub>DD</sub> Frequency Sensitivity (Note 3,  | $V_{DD}$ = 3.0 V, F $\leq$ 1 MHz, T = 25 °C                 |                                                                                                                                                                                                                                                                                                                                                       | 0.21     |      | mA/MHz |

| Note 6)                                         | V <sub>DD</sub> = 3.0 V, F > 1 MHz, T = 25 °C               | —                                                                                                                                                                                                                                                                                                                                                     | 0.15     | _    | mA/MHz |

|                                                 | V <sub>DD</sub> = 3.6 V, F <u>&lt;</u> 1 MHz, T = 25 °C     | —                                                                                                                                                                                                                                                                                                                                                     | 0.28     |      | mA/MHz |

|                                                 | V <sub>DD</sub> = 3.6 V, F > 1 MHz, T = 25 °C               | _                                                                                                                                                                                                                                                                                                                                                     | 0.19     | _    | mA/MHz |

| Digital Supply Current<br>(Stop Mode, shutdown) | Oscillator not running,<br>V <sub>DD</sub> Monitor Disabled | _                                                                                                                                                                                                                                                                                                                                                     | < 0.1    | _    | μA     |

#### Notes:

- 1. Given in Table 9.1 on page 110.

- 2. SYSCLK must be at least 32 kHz to enable debugging.

- 3. Based on device characterization data, not production tested.

- 4. Active and Inactive I<sub>DD</sub> at voltages and frequencies other than those specified can be calculated using the I<sub>DD</sub> Supply Sensitivity. For example, if the V<sub>DD</sub> is 3.3 V instead of 3.0 V at 25 MHz: I<sub>DD</sub> = 7.8 mA typical at 3.0 V and f = 25 MHz. From this, I<sub>DD</sub> = 7.8 mA + 0.67 x (3.3 V 3.0 V) = 8 mA at 3.3 V and f = 25 MHz.

- 5. I<sub>DD</sub> can be estimated for frequencies ≤ 15 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> for > 15 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:

$V_{DD}$  = 3.0 V; F = 20 MHz,  $I_{DD}$  = 7.8 mA – (25 MHz – 20 MHz) x 0.21 mA/MHz = 6.75 mA.

Idle I<sub>DD</sub> can be estimated for frequencies ≤ 1 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate Idle I<sub>DD</sub> for > 1 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:

$V_{DD}$  = 3.0 V; F = 5 MHz, Idle I<sub>DD</sub> = 4.8 mA – (25 MHz – 5 MHz) x 0.15 mA/MHz = 1.8 mA.

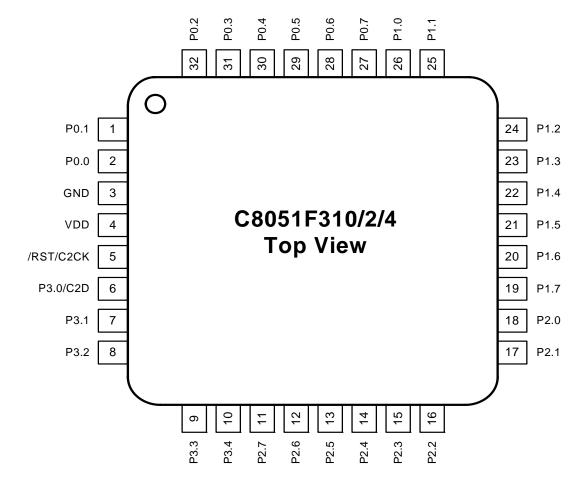

Figure 4.1. LQFP-32 Pinout Diagram (Top View)

| R/W      | R/W                                                                                                              | R/W           | R/W            | R/W            | R/W           | R/W           | R/W            | Reset Value  |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------|---------------|----------------|----------------|---------------|---------------|----------------|--------------|--|--|--|--|--|

| AD0EN    | AD0TM                                                                                                            | AD0INT        | AD0BUSY        | <b>AD0WINT</b> | AD0CM2        | AD0CM1        | AD0CM0         | 0000000      |  |  |  |  |  |

| Bit7     | Bit6                                                                                                             | Bit5          | Bit4           | Bit3           | Bit2          | Bit1          | Bit0           | SFR Addres   |  |  |  |  |  |

|          |                                                                                                                  |               |                |                |               | (bi           | t addressable) | 0xE8         |  |  |  |  |  |

| Bit7:    | AD0EN: AD0                                                                                                       | ^0 Enable I   | ⊇it            |                |               |               |                |              |  |  |  |  |  |

| JI(7.    | 0: ADC0 Dis                                                                                                      |               |                | ower shutd     | own           |               |                |              |  |  |  |  |  |

|          | 1: ADC0 End                                                                                                      |               |                |                |               | ersions.      |                |              |  |  |  |  |  |

| Bit6:    | ADOTM: AD                                                                                                        |               |                |                |               |               |                |              |  |  |  |  |  |

|          | 0: Normal Tr                                                                                                     | ack Mode:     | When ADC0      | ) is enabled,  | tracking is   | continuous    | unless a co    | nversion is  |  |  |  |  |  |

|          | in progress.                                                                                                     |               |                |                | -             |               |                |              |  |  |  |  |  |

|          | 1: Low-powe                                                                                                      |               |                |                |               | ) bits (see b | elow).         |              |  |  |  |  |  |

| Bit5:    | AD0INT: AD                                                                                                       |               |                |                |               |               |                |              |  |  |  |  |  |

|          | 0: ADC0 has                                                                                                      | •             |                |                | since the las | st time AD0   | NT was clea    | ared.        |  |  |  |  |  |

| 5:44     | 1: ADC0 has                                                                                                      |               |                | ersion.        |               |               |                |              |  |  |  |  |  |

| Bit4:    | AD0BUSY: A<br>Read:                                                                                              | ADC0 Busy     | Bit.           |                |               |               |                |              |  |  |  |  |  |

|          | 0: ADC0 con                                                                                                      | warsion is c  | omplete or     |                | n is not curr | ently in proc |                | JT is sat to |  |  |  |  |  |

|          | logic 1 on the                                                                                                   |               | •              |                |               |               |                | 11 13 361 10 |  |  |  |  |  |

|          | •                                                                                                                | U .           |                |                |               |               |                |              |  |  |  |  |  |

|          | 1: ADC0 conversion is in progress.<br>Write:                                                                     |               |                |                |               |               |                |              |  |  |  |  |  |

|          | 0: No Effect.                                                                                                    |               |                |                |               |               |                |              |  |  |  |  |  |

|          | 1: Initiates A                                                                                                   | DC0 Conve     | ersion if AD0  | CM2-0 = 00     | 0b            |               |                |              |  |  |  |  |  |

| Bit3:    | ADOWINT: A                                                                                                       |               | •              | •              | -             |               |                |              |  |  |  |  |  |

|          | 0: ADC0 Wir                                                                                                      |               |                |                |               | d since this  | flag was las   | t cleared.   |  |  |  |  |  |

|          | 1: ADC0 Wir                                                                                                      | •             |                |                |               |               |                |              |  |  |  |  |  |

| Bits2–0: | AD0CM2-0:                                                                                                        |               | t of Convers   | ion Mode S     | elect.        |               |                |              |  |  |  |  |  |

|          | When AD0T 000: ADC0 c                                                                                            |               | nitiated on a  | work write c   | f '1' to A DO |               |                |              |  |  |  |  |  |

|          | 000. ADC0 0<br>001: ADC0 0                                                                                       |               |                |                |               | 0031.         |                |              |  |  |  |  |  |

|          |                                                                                                                  |               |                |                |               |               |                |              |  |  |  |  |  |

|          | 010: ADC0 conversion initiated on overflow of Timer 2.<br>011: ADC0 conversion initiated on overflow of Timer 1. |               |                |                |               |               |                |              |  |  |  |  |  |

|          | 100: ADC0 c                                                                                                      |               |                |                |               | NVSTR.        |                |              |  |  |  |  |  |

|          | 101: ADC0 c                                                                                                      | conversion i  | nitiated on c  | overflow of T  | ïmer 3.       |               |                |              |  |  |  |  |  |

|          | 11x: Reserve                                                                                                     |               |                |                |               |               |                |              |  |  |  |  |  |

|          | When AD0T                                                                                                        |               |                |                |               |               |                |              |  |  |  |  |  |

|          | 000: Trackin                                                                                                     | g initiated o | on write of '1 | ' to AD0BUS    | SY and lasts  | s 3 SAR clo   | cks, followe   | d by con-    |  |  |  |  |  |

|          | version.                                                                                                         | a initiated a | n avarflavi a  | f Timer O er   | d looto 2 C   | AD alaaka f   | allowed by     |              |  |  |  |  |  |

|          | 001: Trackin<br>010: Trackin                                                                                     |               |                |                |               |               |                |              |  |  |  |  |  |

|          | 011: Tracking                                                                                                    |               |                |                |               |               |                |              |  |  |  |  |  |

|          | 100: ADC0 t                                                                                                      |               |                |                |               |               |                |              |  |  |  |  |  |

|          | edge.                                                                                                            |               |                | int input io i | ogio ion, co  |               |                | 9 0 0        |  |  |  |  |  |

|          | 101: Trackin                                                                                                     | a initiated o | on overflow o  | of Timer 3 ar  | 2 S atech h   | AR clocks. f  | ollowed by a   | conversion   |  |  |  |  |  |

|          |                                                                                                                  | g millatoa o  |                |                | 10 10313 5 01 |               | ••             | 00110013101  |  |  |  |  |  |

| R/W      | R              | R/W           | R/W        | R/W          | R/W           | R/W             | R/W        | Reset Value  |

|----------|----------------|---------------|------------|--------------|---------------|-----------------|------------|--------------|

| CP0EN    | CP0OUT         | <b>CP0RIF</b> | CP0FIF     | CP0HYP1      | CP0HYP0       | CP0HYN1         | CP0HYN0    | 00000000     |

| Bit7     | Bit6           | Bit5          | Bit4       | Bit3         | Bit2          | Bit1            | Bit0       | SFR Address: |

|          |                |               |            |              |               |                 |            | 0x9B         |

|          |                |               |            |              |               |                 |            |              |

| Bit7:    | CP0EN: Cor     | nparator0 E   | nable Bit. |              |               |                 |            |              |

|          | 0: Comparat    | or0 Disable   | d.         |              |               |                 |            |              |

|          | 1: Comparat    |               |            |              |               |                 |            |              |

| Bit6:    | CP0OUT: Co     |               |            | ate Flag.    |               |                 |            |              |

|          | 0: Voltage or  |               |            |              |               |                 |            |              |

|          | 1: Voltage or  |               |            |              |               |                 |            |              |

| Bit5:    | CPORIF: Co     |               |            |              |               |                 |            |              |

|          | 0: No Comp     |               | 0 0        |              |               | ice this flag   | was last c | leared.      |

| DitA     | 1: Comparat    | -             | -          | •            |               |                 |            |              |

| Bit4:    | CP0FIF: Co     |               |            |              |               | a a a thia flag |            |              |

|          | 0: No Comparat |               |            |              |               | nce this hag    | was last c | cieareo.     |

| Bits3-2: | CP0HYP1-0      |               |            |              |               | -               |            |              |

| Dit35-2. | 00: Positive   |               |            | errysteresis |               | 5.              |            |              |

|          | 01: Positive   |               |            |              |               |                 |            |              |

|          | 10: Positive   |               |            |              |               |                 |            |              |

|          | 11: Positive   |               |            |              |               |                 |            |              |

| Bits1–0: | CP0HYN1-0      |               |            | ve Hvsteres  | is Control Bi | its.            |            |              |

|          | 00: Negative   | •             | -          | •            |               |                 |            |              |

|          | 01: Negative   |               |            |              |               |                 |            |              |

|          | 10: Negative   | e Hysteresis  | = 10 mV.   |              |               |                 |            |              |

|          | 11: Negative   | Hysteresis    | = 20 mV.   |              |               |                 |            |              |

|          |                |               |            |              |               |                 |            |              |

## SFR Definition 7.1. CPT0CN: Comparator0 Control

#### 8.3.2. External Interrupts

The /INT0 and /INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The IN0PL (/INT0 Polarity) and IN1PL (/INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (**Section "17.1. Timer 0 and Timer 1" on page 187**) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | /INT0 Interrupt              |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | /INT1 Interrupt              |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

/INT0 and /INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 8.11). Note that /INT0 and /INT0 Port pin assignments are independent of any Crossbar assignments. /INT0 and /INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to /INT0 and/or /INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see **Section** "13.1. Priority Crossbar Decoder" on page 131 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the /INT0 and /INT1 external interrupts, respectively. If an /INT0 or /INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

#### 8.3.3. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP or EIP1) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 8.4.

#### 8.3.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 5 system clock cycles: 1 clock cycle to detect the interrupt and 4 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 18 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 4 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

| Interrupt Source Interrupt Priority<br>Vector Order Pending Flag |        | Bit addressable? | Cleared by HW?                                                                | Enable<br>Flag | Priority<br>Control |                    |                    |

|------------------------------------------------------------------|--------|------------------|-------------------------------------------------------------------------------|----------------|---------------------|--------------------|--------------------|

| Reset                                                            | 0x0000 | Тор              | None                                                                          | N/A            | N/A                 | Always<br>Enabled  | Always<br>Highest  |

| External Interrupt 0 (/INT0)                                     | 0x0003 | 0                | IE0 (TCON.1)                                                                  | Y              | Y                   | EX0 (IE.0)         | PX0 (IP.0)         |

| Timer 0 Overflow                                                 | 0x000B | 1                | TF0 (TCON.5)                                                                  | Y              | Y                   | ET0 (IE.1)         | PT0 (IP.1)         |

| External Interrupt 1 (/INT1)                                     | 0x0013 | 2                | IE1 (TCON.3)                                                                  | Y              | Y                   | EX1 (IE.2)         | PX1 (IP.2)         |

| Timer 1 Overflow                                                 | 0x001B | 3                | TF1 (TCON.7)                                                                  | Y              | Y                   | ET1 (IE.3)         | PT1 (IP.3)         |

| UART0                                                            | 0x0023 | 4                | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                                | Y              | Ν                   | ES0 (IE.4)         | PS0 (IP.4)         |

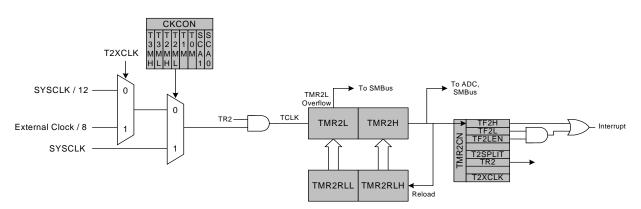

| Timer 2 Overflow                                                 | 0x002B | 5                | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                            | Y              | Ν                   | ET2 (IE.5)         | PT2 (IP.5)         |

| SPI0                                                             | 0x0033 | 6                | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN<br>(SPI0CN.4) | Y              | N                   | ESPI0<br>(IE.6)    | PSPI0<br>(IP.6)    |

| SMB0                                                             | 0x003B | 7                | SI (SMB0CN.0)                                                                 | Y              | Ν                   | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)  |

| RESERVED                                                         | 0x0043 | 8                | N/A                                                                           | N/A            | N/A                 | N/A                | N/A                |

| ADC0 Window Compare                                              | 0x004B | 9                | ADOWINT<br>(ADC0CN.3)                                                         | Y              | Ν                   | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2) |

| ADC0 Conversion<br>Complete                                      | 0x0053 | 10               | AD0INT<br>(ADC0CN.5)                                                          | Y              | Ν                   | EADC0<br>(EIE1.3)  | PADC0<br>(EIP1.3)  |

| Programmable Counter<br>Array                                    | 0x005B | 11               | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                              | Y              | Ν                   | EPCA0<br>(EIE1.4)  | PPCA0<br>(EIP1.4)  |

| Comparator0                                                      | 0x0063 | 12               | CP0FIF<br>(CPT0CN.4)<br>CP0RIF<br>(CPT0CN.5)                                  | N              | N                   | ECP0<br>(EIE1.5)   | PCP0<br>(EIP1.5)   |

| Comparator1                                                      | 0x006B | 13               | CP1FIF<br>(CPT1CN.4)<br>CP1RIF<br>(CPT1CN.5)                                  | N              | Ν                   | ECP1<br>(EIE1.6)   | PCP1<br>(EIP1.6)   |

| Timer 3 Overflow                                                 | 0x0073 | 14               | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                            | Ν              | Ν                   | ET3<br>(EIE1.7)    | PT3<br>(EIP1.7)    |

# Table 8.4. Interrupt Summary

| R/W   | R/W                        | R/W           | R/W           | R/W        | R/W           | R/W            | R/W   | Reset Value  |

|-------|----------------------------|---------------|---------------|------------|---------------|----------------|-------|--------------|

| PT3   | PCP1                       | PCP0          | PCP0          | PADC0      | PWADC0        | Reserved       | PSMB0 | 00000000     |

| Bit7  | Bit6                       | Bit5          | Bit4          | Bit3       | Bit2          | Bit1           | Bit0  | SFR Address: |

|       |                            |               |               |            |               |                |       | 0xF6         |

| Bit7: | PT3: Timer 3               | 8 Interrupt F | Priority Con  | trol       |               |                |       |              |

| Bitti | This bit sets              |               |               |            | ot.           |                |       |              |

|       | 0: Timer 3 in              |               |               |            | •••           |                |       |              |

|       | 1: Timer 3 in              |               |               |            |               |                |       |              |

| Bit6: | PCP1: Com                  | •             | • •           |            | ontrol.       |                |       |              |

|       | This bit sets              | · ·           | , ·           |            |               |                |       |              |

|       | 0: CP1 interi              |               |               |            |               |                |       |              |

|       | 1: CP1 inter               |               |               |            |               |                |       |              |

| Bit5: | PCP0: Com                  |               |               |            | ontrol.       |                |       |              |

|       | This bit sets              | the priority  | of the CP0    | interrupt. |               |                |       |              |

|       | 0: CP0 interi              | upt set to lo | ow priority I | evel.      |               |                |       |              |

|       | 1: CP0 inter               | upt set to h  | igh priority  | level.     |               |                |       |              |

| Bit4: | PPCA0: Pro                 | grammable     | Counter A     | rray (PCA0 | ) Interrupt P | riority Contro | ol.   |              |

|       | This bit sets              |               |               |            |               |                |       |              |

|       | 0: PCA0 inte               |               |               |            |               |                |       |              |

|       | 1: PCA0 inte               |               | • •           |            |               |                |       |              |

| Bit3: | PADC0 ADC                  |               |               |            |               |                |       |              |

|       | This bit sets              |               |               |            |               |                |       |              |

|       | 0: ADC0 Co                 |               | •             |            |               |                |       |              |

| DVA   | 1: ADC0 Co                 |               | •             |            | • •           |                |       |              |

| Bit2: | PWADC0: A                  |               | •             |            |               | ontrol.        |       |              |

|       | This bit sets              |               |               |            |               |                |       |              |

|       | 0: ADC0 Wir                |               |               |            |               |                |       |              |

| D:14. | 1: ADC0 Wir                |               |               |            | evel.         |                |       |              |

| Bit1: | RESERVED                   |               |               |            | trol          |                |       |              |

| Bit0: | PSMB0: SM<br>This bit sets | •             | , ·           |            |               |                |       |              |

|       | 0: SMB0 inte               |               |               |            |               |                |       |              |

|       | 1: SMB0 inte               |               |               |            |               |                |       |              |

|       |                            | mupt set to   | nigh phòn     | iy level.  |               |                |       |              |

# SFR Definition 8.10. EIP1: Extended Interrupt Priority 1

### SFR Definition 9.2. RSTSRC: Reset Source

| R     | R                            | R/W                 | R/W          | R                        | R/W                     | R/W           | R                      | Reset Valu  |

|-------|------------------------------|---------------------|--------------|--------------------------|-------------------------|---------------|------------------------|-------------|

| -     | FERROR                       | CORSEF              | SWRSF        | WDTRSF                   | MCDRSF                  | PORSF         | PINRSF                 | Variable    |

| Bit7  | Bit6                         | Bit5                | Bit4         | Bit3                     | Bit2                    | Bit1          | Bit0                   |             |

|       |                              |                     |              |                          |                         |               | SFR Address            | :0xEF       |

|       |                              |                     |              |                          |                         |               |                        |             |

| Bit7: | UNUSED. R                    | $aad = 0 M_{\rm H}$ | rito - don't | ooro                     |                         |               |                        |             |

| Bit6: | FERROR: FI                   |                     |              | care.                    |                         |               |                        |             |

|       | 0: Source of                 |                     |              | lash read/w              | rite/erase er           | ror           |                        |             |

|       | 1: Source of                 |                     |              |                          |                         |               |                        |             |

| Bit5: | CORSEF: Co                   |                     |              |                          |                         |               |                        |             |

|       | 0: Read: Sou                 | •                   |              |                          | -                       | : Compara     | tor0 is not a          | reset       |

|       | source.                      |                     |              |                          |                         |               |                        |             |

|       | 1: Read: Sou                 | urce of last        | reset was (  | Comparator               | 0. Write: Co            | omparator0    | is a reset s           | ource       |

|       | (active-low).                |                     |              |                          |                         |               |                        |             |

| Bit4: | SWRSF: Sof                   |                     |              |                          |                         |               |                        |             |

|       | 0: Read: Sou                 |                     |              |                          |                         |               |                        |             |

| Bit3: | 1: Read: Sou<br>WDTRSF: W    |                     |              |                          | KOF DIL WI              | ite: Forces   | a system re            | eset.       |

| ກເວ.  | 0: Source of                 | -                   |              | -                        |                         |               |                        |             |

|       | 1: Source of                 |                     |              |                          | •                       |               |                        |             |

| Bit2: | MCDRSF: M                    |                     |              |                          |                         |               |                        |             |

|       | 0: <b>Read:</b> Sou          | -                   |              | -                        | g Clock Det             | ector timed   | out. Write: N          | lissing     |

|       | Clock Detect                 |                     |              |                          | 0                       |               |                        | 0           |

|       | 1: Read: Sou                 | urce of last        | reset was a  | a Missing C              | lock Detecto            | or timeout.   | Write: Miss            | ing Clock   |

|       | Detector ena                 |                     |              | -                        | clock condit            | ion is dete   | cted.                  |             |

| Bit1: | PORSF: Pov                   |                     |              | •                        |                         |               |                        |             |

|       | This bit is se               |                     |              |                          |                         |               |                        |             |

|       | monitor as a                 |                     |              | -                        |                         | _             |                        | is enable   |

|       | and stabilize                |                     |              |                          |                         |               |                        |             |

|       | 0: Read: Las                 | st reset was        | not a pow    | er-on or V <sub>DI</sub> | <sub>C</sub> monitor re | set. Write:   | V <sub>DD</sub> monito | or is not a |

|       | reset source                 |                     |              |                          |                         |               |                        |             |

|       | 1: Read: Las                 |                     |              |                          | nitor reset; a          | all other res | set flags inde         | eterminate  |

|       | Write: V <sub>DD</sub> r     |                     |              | ce.                      |                         |               |                        |             |

| BitO: | PINRSF: HW                   |                     | · ·          | _                        |                         |               |                        |             |

|       | 0: Source of                 |                     |              |                          |                         |               |                        |             |

|       | 1: Source of                 | last reset w        | /as RST pii  | า.                       |                         |               |                        |             |

| Note: | For bits that a read-modify- |                     |              |                          |                         |               |                        |             |

| R/W   | R/W                                                                                     | R/W                      | R/W          | R/W          | R/W     | R/W   | R/W   | Reset Value  |  |  |  |

|-------|-----------------------------------------------------------------------------------------|--------------------------|--------------|--------------|---------|-------|-------|--------------|--|--|--|

| CP1AE | -                                                                                       | CP0AE                    | CP0E         | SYSCKE       | SMB0E   | SPI0E | URTOE | 00000000     |  |  |  |

| Bit7  | Bit6                                                                                    | Bit5                     | Bit4         | Bit3         | Bit2    | Bit1  | Bit0  | SFR Address: |  |  |  |

| Ditt  | Bito                                                                                    | Dito                     | DILT         | Dito         | DILZ    | BRI   | Dito  | 0xE1         |  |  |  |

|       |                                                                                         |                          |              |              |         |       |       |              |  |  |  |

| Bit7: | CP1AE: Cor                                                                              | nparator1 A              | synchrono    | us Output F  | nable   |       |       |              |  |  |  |

|       |                                                                                         | •                        |              |              |         |       |       |              |  |  |  |

|       | 0: Asynchronous CP1 unavailable at Port pin.<br>1: Asynchronous CP1 routed to Port pin. |                          |              |              |         |       |       |              |  |  |  |

| Bit6: | CP1E: Com                                                                               |                          |              |              |         |       |       |              |  |  |  |

|       | 0: CP1 unav                                                                             |                          | •            |              |         |       |       |              |  |  |  |

|       | 1: CP1 route                                                                            |                          |              |              |         |       |       |              |  |  |  |

| Bit5: | CP0AE: Cor                                                                              | nparator0 <sup>.</sup> A | synchrono    | us Output E  | nable   |       |       |              |  |  |  |

|       | 0: Asynchro                                                                             | nous CP0 u               | navailable   | at Port pin. |         |       |       |              |  |  |  |

|       | 1: Asynchronous CP0 routed to Port pin.                                                 |                          |              |              |         |       |       |              |  |  |  |

| Bit4: | CP0E: Comparator0 Output Enable                                                         |                          |              |              |         |       |       |              |  |  |  |

|       | 0: CP0 unavailable at Port pin.                                                         |                          |              |              |         |       |       |              |  |  |  |

|       | 1: CP0 route                                                                            | ed to Port pi            | n.           |              |         |       |       |              |  |  |  |

| Bit3: | SYSCKE: /SYSCLK Output Enable                                                           |                          |              |              |         |       |       |              |  |  |  |

|       | 0: /SYSCLK unavailable at Port pin.                                                     |                          |              |              |         |       |       |              |  |  |  |

|       | 1: /SYSCLK                                                                              |                          |              | oin.         |         |       |       |              |  |  |  |

| Bit2: | SMB0E: SMBus I/O Enable                                                                 |                          |              |              |         |       |       |              |  |  |  |

|       | 0: SMBus I/O unavailable at Port pins.                                                  |                          |              |              |         |       |       |              |  |  |  |

|       | 1: SMBus I/0                                                                            |                          | Port pins.   |              |         |       |       |              |  |  |  |

| Bit1: | SPI0E: SPI I                                                                            |                          |              |              |         |       |       |              |  |  |  |

|       | 0: SPI I/O ur                                                                           |                          | •            |              |         |       |       |              |  |  |  |

|       | 1: SPI I/O ro                                                                           |                          |              |              |         |       |       |              |  |  |  |

| Bit0: | URT0E: UA                                                                               |                          |              |              |         |       |       |              |  |  |  |

|       | 0: UART I/O                                                                             |                          |              |              |         |       |       |              |  |  |  |

|       | 1: UART TX                                                                              | 0, RX0 rout              | ed to Port p | oins P0.4 an | d P0.5. |       |       |              |  |  |  |

|       |                                                                                         |                          |              |              |         |       |       |              |  |  |  |

## SFR Definition 13.1. XBR0: Port I/O Crossbar Register 0

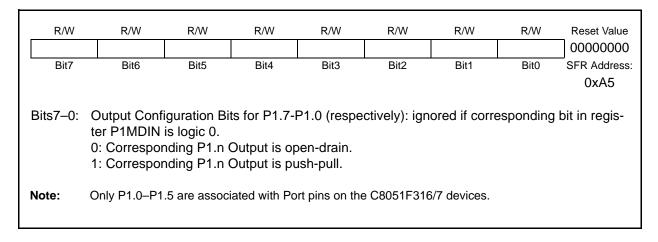

### SFR Definition 13.9. P1MDOUT: Port1 Output Mode

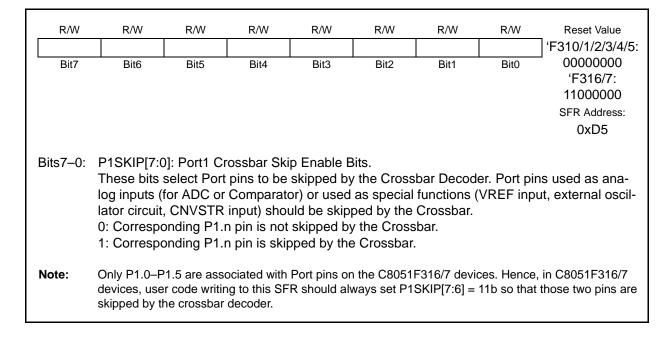

# SFR Definition 13.10. P1SKIP: Port1 Skip

# C8051F310/1/2/3/4/5/6/7

#### 16.6. SPI Special Function Registers

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following register definitions.

| R         | R/W                                                                                              | R/W          | R/W         | R            | R               | R             | R             | Reset Value    |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------|--------------|-------------|--------------|-----------------|---------------|---------------|----------------|--|--|--|

| SPIBSY    | MSTEN                                                                                            | CKPHA        | CKPOL       | SLVSEL       | NSSIN           | SRMT          | RXBMT         | 00000111       |  |  |  |

| Bit7      | Bit6                                                                                             | Bit5         | Bit4        | Bit3         | Bit2            | Bit1          | Bit0          |                |  |  |  |

|           |                                                                                                  |              |             |              |                 |               | SFR Address   | s: 0xA1        |  |  |  |

| <b>D-</b> |                                                                                                  |              |             |              |                 |               |               |                |  |  |  |

|           | SPIBSY: SP                                                                                       |              | • /         |              |                 | <b></b>       |               | ,              |  |  |  |

|           | This bit is se                                                                                   |              |             | transfer is  | in progress     | (Master or    | slave Mode    | e).            |  |  |  |

|           | MSTEN: Master Mode Enable.                                                                       |              |             |              |                 |               |               |                |  |  |  |

|           | 0: Disable m                                                                                     |              |             |              | e.              |               |               |                |  |  |  |

|           | 1: Enable ma                                                                                     |              | •           | s a master.  |                 |               |               |                |  |  |  |

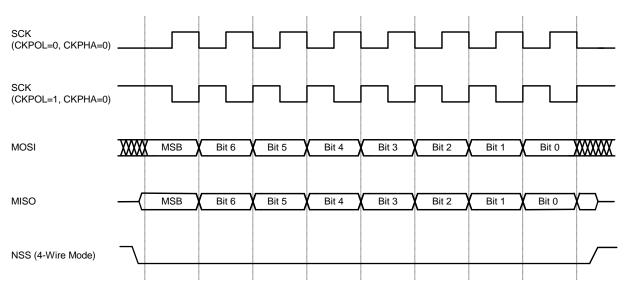

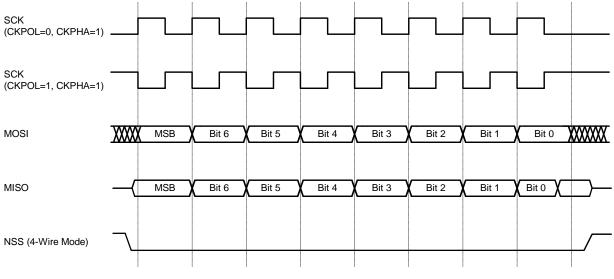

|           | CKPHA: SPI                                                                                       |              |             |              |                 |               |               |                |  |  |  |

|           | This bit cont                                                                                    |              |             |              |                 |               |               |                |  |  |  |

|           | 0: Data cent                                                                                     |              |             |              |                 |               |               |                |  |  |  |

|           | 1: Data centered on second edge of SCK period.*                                                  |              |             |              |                 |               |               |                |  |  |  |

|           | CKPOL: SPI0 Clock Polarity.                                                                      |              |             |              |                 |               |               |                |  |  |  |

|           | This bit controls the SPI0 clock polarity.                                                       |              |             |              |                 |               |               |                |  |  |  |

|           | 0: SCK line low in idle state.                                                                   |              |             |              |                 |               |               |                |  |  |  |

|           | 1: SCK line high in idle state.                                                                  |              |             |              |                 |               |               |                |  |  |  |

|           | SLVSEL: Sla                                                                                      |              |             |              |                 |               |               |                |  |  |  |

|           | This bit is set to logic 1 whenever the NSS pin is low indicating SPI0 is the selected slave. It |              |             |              |                 |               |               |                |  |  |  |

|           | is cleared to logic 0 when NSS is high (slave not selected). This bit does not indicate the      |              |             |              |                 |               |               |                |  |  |  |

|           | instantaneou                                                                                     |              |             |              |                 | ed version of | of the pin in | put.           |  |  |  |

|           | NSSIN: NSS Instantaneous Pin Input (read only).                                                  |              |             |              |                 |               |               |                |  |  |  |

|           | This bit mimics the instantaneous value that is present on the NSS port pin at the time that     |              |             |              |                 |               |               |                |  |  |  |

|           | the register is read. This input is not de-glitched.                                             |              |             |              |                 |               |               |                |  |  |  |

|           | SRMT: Shift                                                                                      |              |             |              |                 |               |               |                |  |  |  |

|           | This bit will be set to logic 1 when all data has been transferred in/out of the shift register, |              |             |              |                 |               |               |                |  |  |  |

|           | and there is no new information available to read from the transmit buffer or write to the       |              |             |              |                 |               |               |                |  |  |  |

|           | receive buffer. It returns to logic 0 when a data byte is transferred to the shift register from |              |             |              |                 |               |               |                |  |  |  |

|           | the transmit buffer or by a transition on SCK.                                                   |              |             |              |                 |               |               |                |  |  |  |

|           | NOTE: SRMT = 1 when in Master Mode.                                                              |              |             |              |                 |               |               |                |  |  |  |

| Bit 0:    | RXBMT: Red                                                                                       | ceive Buffer | Empty (Va   | lid in Slave | Mode, read      | only).        |               |                |  |  |  |

|           | This bit will be set to logic 1 when the receive buffer has been read and contains no new        |              |             |              |                 |               |               |                |  |  |  |

|           | information. If there is new information available in the receive buffer that has not been read, |              |             |              |                 |               |               |                |  |  |  |

|           | this bit will return to logic 0.                                                                 |              |             |              |                 |               |               |                |  |  |  |

|           | NOTE: RXB                                                                                        | MT = 1 whe   | en in Maste | r Mode.      |                 |               |               |                |  |  |  |

|           |                                                                                                  |              |             |              |                 |               |               |                |  |  |  |

|           |                                                                                                  |              |             |              |                 |               |               | ata on MISO is |  |  |  |

|           | sampled one                                                                                      |              |             |              | bit, to provide | e maximum :   | settling time | for the slave  |  |  |  |

|           | device. See T                                                                                    | able 16.1 10 | uming parar | neters.      |                 |               |               |                |  |  |  |

#### SFR Definition 16.1. SPI0CFG: SPI0 Configuration

# SFR Definition 16.2. SPI0CN: SPI0 Control

| R/W<br>SPIF | R/W<br>WCOL                                                                                                                                                                                                                                                                                                                                                                         | R/W<br>MODF                                                                                        | R/W<br>RXOVRN                                                                         | R/W<br>NSSMD1                                                               | R/W                                            | R<br>TXBMT                | R/W<br>SPIEN                | Reset Value<br>00000110 |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------|---------------------------|-----------------------------|-------------------------|--|--|

| Bit7        | Bit6                                                                                                                                                                                                                                                                                                                                                                                | Bit5                                                                                               | Bit4                                                                                  | Bit3                                                                        | Bit2                                           | Bit1                      | Bit0                        | Bit                     |  |  |

|             |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                    |                                                                                       |                                                                             |                                                |                           | SFR Addres                  | Addressable<br>s: 0xF8  |  |  |

| Bit 7:      | SPIF: SPI0 I<br>This bit is se<br>setting this b<br>automatically                                                                                                                                                                                                                                                                                                                   | t to logic 1<br>it causes th                                                                       | by hardwar<br>ne CPU to v                                                             | ector to the                                                                | SPI0 interru                                   | upt service               |                             |                         |  |  |

| Bit 6:      | automatically cleared by hardware. It must be cleared by software.<br>WCOL: Write Collision Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI0 interrupt) to indicate a write to<br>the SPI0 data register was attempted while a data transfer was in progress. It must be<br>cleared by software.                                                               |                                                                                                    |                                                                                       |                                                                             |                                                |                           |                             |                         |  |  |