Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betans                     |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                                    |

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 24MHz                                                                                  |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, UART/USART                                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                             |

| Number of I/O              | 36                                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | 128 x 8                                                                                |

| RAM Size                   | 256 x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                            |

| Data Converters            | -                                                                                      |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

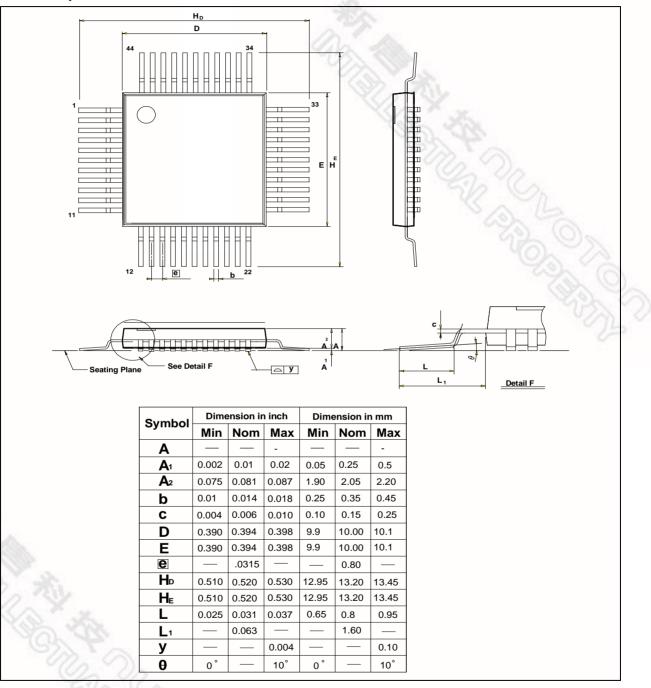

| Package / Case             | 44-BQFP                                                                                |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/n79e352afg |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5. PIN DESCRIPTIONS

| SYMBOL       | Alternate<br>Function 1 | Alternate<br>function 2 | Туре       | DESCRIPTIONS                                                                                                                                                                                                                                                                                                                       |

|--------------|-------------------------|-------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĒĀ           |                         |                         | I          | <b>EXTERNAL ACCESS ENABLE</b> : This pin forces the processor to execute out of external ROM. It should be kept high to access internal ROM. The ROM address and data will not be present on the bus if $\overline{EA}$ pin is high and the program counter is within internal ROM area. Otherwise they will be present o the bus. |

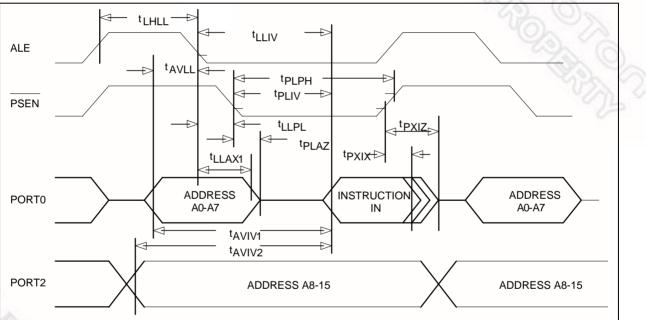

| PSEN         |                         |                         | 0          | PROGRAM STORE ENABLE: PSEN enables the external ROM data onto the Port 0 address/data bud during fetch and MOVC operations. When internal                                                                                                                                                                                          |

|              |                         |                         |            | ROM access is performed, no PSEN strobe signal outputs from this pin.                                                                                                                                                                                                                                                              |

| ALE          |                         |                         | 0          | <b>ADDRESS LATCH ENABLE</b> : ALE is used to enable<br>the address latch that separates the address from<br>the data on Port 0.                                                                                                                                                                                                    |

| XTAL1        | P5.1                    |                         | I/O        | <b>CRYSTAL1</b> : This is the crystal oscillator input. This pin may be driven by an external clock or configurable i/o pin, P5.1.                                                                                                                                                                                                 |

| XTAL2        | P5.0                    |                         | I/O        | <b>CRYSTAL2</b> : This is the crystal oscillator output. It is the inversion of XTAL1. Also a configurable i/o pin, P5.0.                                                                                                                                                                                                          |

| VDD          |                         |                         | Р          | <b>POWER SUPPLY</b> : Supply voltage for operation.                                                                                                                                                                                                                                                                                |

| VSS          |                         |                         | Р          | GROUND: Ground potential.                                                                                                                                                                                                                                                                                                          |

| RST          |                         |                         |            | <b>RESET:</b> A high on this pin for two machine cycles while the oscillator is running resets the device.                                                                                                                                                                                                                         |

| P0.0         | KB0                     | AD0                     | I/O        | PORT0:                                                                                                                                                                                                                                                                                                                             |

| P0.1         | KB1                     | AD1                     | I/O        | Support 4 mode output and 2 mode input.                                                                                                                                                                                                                                                                                            |

| P0.2         | KB2<br>KB3              | AD2<br>AD3              | I/O<br>I/O | Multifunction pins for AD0-7and KB0-7.                                                                                                                                                                                                                                                                                             |

| P0.3<br>P0.4 | KB3<br>KB4              | AD3<br>AD4              | 1/O<br>1/O |                                                                                                                                                                                                                                                                                                                                    |

| P0.4         | KB4<br>KB5              | AD4<br>AD5              | 1/O        | -                                                                                                                                                                                                                                                                                                                                  |

| P0.6         | KB6                     | AD6                     | 1/O        |                                                                                                                                                                                                                                                                                                                                    |

| P0.7         | KB7                     | AD7                     | I/O        |                                                                                                                                                                                                                                                                                                                                    |

| P1.0         | 42.                     | T2                      | I/O        | PORT1:                                                                                                                                                                                                                                                                                                                             |

| P1.1         | 20                      | T2EX                    | I/O        |                                                                                                                                                                                                                                                                                                                                    |

| P1.2         | 5 40                    | SDA                     | I/O        | Support 4 mode output and 2 mode input.                                                                                                                                                                                                                                                                                            |

| P1.3         | 20                      | SCL                     | I/O        | Multifunction pins for SDA & SCL (I2C), T2, T2EX                                                                                                                                                                                                                                                                                   |

| P1.4         | VA                      | PWM0                    | I/O        | and PWM0-1.                                                                                                                                                                                                                                                                                                                        |

| P1.5         |                         | PWM1                    | I/O        | _                                                                                                                                                                                                                                                                                                                                  |

| P1.6         | ICPDAT                  | Reg                     | I/O        | _                                                                                                                                                                                                                                                                                                                                  |

| P1.7         | ICPCLK                  | AM                      | I/O        |                                                                                                                                                                                                                                                                                                                                    |

|   |     | $\overline{\text{INT0}}$ . This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the inverse of the pin. |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | IT0 | Interrupt 0 Type Control: Set/cleared by software to specify falling edge/ low level triggered external inputs.                                                                           |

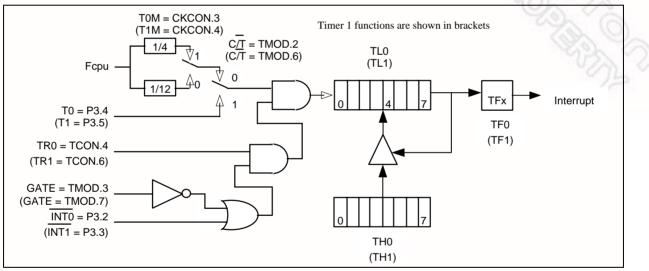

### TIMER MODE CONTROL

| Bit: | 7      | 6   | 5  | 4  | 3      | 2   | 1  | 0  |

|------|--------|-----|----|----|--------|-----|----|----|

|      | GATE   | C/T | M1 | MO | GATE   | C/T | M1 | MO |

|      | TIMER1 |     |    |    | TIMER0 | A S | 2  |    |

### Mnemonic: TMOD

Address: 89h

| BIT | NAME | FUNCTION                                                                                                                                                                                                                                                     |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | GATE | Gating control: When this bit is set, Timer/counter 1 is enabled only while the $\overline{INT1}$ pin is high and the TR1 control bit is set. When cleared, the $\overline{INT1}$ pin has no effect, and Timer 1 is enabled whenever TR1 control bit is set. |

| 6   | C/T  | Timer or Counter Select: When clear, Timer 1 is incremented by the internal clock. When set, the timer counts falling edges on the T1 pin.                                                                                                                   |

| 5   | M1   | Timer 1 mode select bit 1. See table below.                                                                                                                                                                                                                  |

| 4   | MO   | Timer 1 mode select bit 0. See table below.                                                                                                                                                                                                                  |

| 3   | GATE | Gating control: When this bit is set, Timer/counter 0 is enabled only while the $\overline{INT0}$ pin is high and the TR0 control bit is set. When cleared, the $\overline{INT0}$ pin has no effect, and Timer 0 is enabled whenever TR0 control bit is set. |

| 2   | C/T  | Timer or Counter Select: When clear, Timer 0 is incremented by the internal clock. When set, the timer counts falling edges on the T0 pin.                                                                                                                   |

| 1   | M1   | Timer 0 mode select bit 1. See table below.                                                                                                                                                                                                                  |

| 0   | MO   | Timer 0 mode select bit 0. See table below.                                                                                                                                                                                                                  |

### M1, M0: Mode Select bits:

| M1 | MO | MODE                                                                                                                                                                                                |

|----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | Mode 0: 8-bit timer/counter TLx serves as 5-bit pre-scale.                                                                                                                                          |

| 0  | 1  | Mode 1: 16-bit timer/counter, no pre-scale.                                                                                                                                                         |

| 1  | 0  | Mode 2: 8-bit timer/counter with auto-reload from THx.                                                                                                                                              |

| 1  | 1  | Mode 3: (Timer 0) TL0 is an 8-bit timer/counter controlled by the standard Timer0 control bits. TH0 is an 8-bit timer only controlled by Timer1 control bits. (Timer 1) Timer/Counter 1 is stopped. |

## TIMER 0 LSB

| Bit: | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

|      | TL0.7 | TL0.6 | TL0.5 | TL0.4 | TL0.3 | TL0.2 | TL0.1 | TL0.0 |

Mnemonic: TL0

Address: 8Ah

- 24 -

# nuvoTon

| 2-1<br>0 | CPTF0         | Reserved<br>External i |               | e 0 interrupt               | flag. It can b | e cleared by | v software.  |           |

|----------|---------------|------------------------|---------------|-----------------------------|----------------|--------------|--------------|-----------|

| PORT     | 1             |                        |               |                             |                |              |              |           |

| Bit:     | <b>-</b><br>7 | 6                      | 5             | 4                           | 3              | 2            | 1            | 0         |

|          | -             | -                      | -             | -                           | P4.3           | P4.2         | P4.1         | P4.0      |

| Mnem     | onic: P4      |                        |               |                             | N.             | X            | A            | ddress:   |

| BIT      | NAME          | FUNCTIO                | N             |                             | X              | Ya T         | 2            |           |

| 7~4      | -             | Reserved               | d.            |                             |                | - m          | 5            |           |

| 3~0      | P4.3~0        |                        |               | onal I/O por<br>on (SETB or |                | al pull-ups. | Port 4 can i | not use   |

| INTER    |               | BLE                    |               |                             |                |              | ~200         | 6         |

| Bit:     | 7             | 6                      | 5             | 4                           | 3              | 2            | 1 76         | 0         |

|          | EA            | -                      | ET2           | ES                          | ET1            | EX1          | ET0          | EX0       |

| Mnem     | onic: IE      |                        |               |                             |                |              | A            | ddress:   |

| BIT      | NAME          | FUNCTIO                | N             |                             |                |              |              | 0         |

| 7        | EA            | Global er              | nable. Enabl  | e/Disable all               | interrupts.    |              |              |           |

| 6        | -             | Reserved               | ł.            |                             |                |              |              |           |

| 5        | ET2           | Enable T               | imer 2 interi | upt.                        |                |              |              |           |

| 4        | ES            | Enable S               | erial Port 0  | interrupt.                  |                |              |              |           |

| 3        | ET1           | Enable T               | imer 1 interi | upt.                        |                |              |              |           |

| 2        | EX1           | Enable e               | xternal inter | rupt 1.                     |                |              |              |           |

| 1        | ET0           | Enable T               | imer 0 interi | upt.                        |                |              |              |           |

| 0        | EX0           | Enable e               | xternal inter | rupt 0.                     |                |              |              |           |

| SLAVI    |               | S                      |               |                             |                |              |              |           |

| Bit:     | 7             | 6                      | 5             | 4                           | 3              | 2            | 1            | 0         |

|          | SADDR.7       | SADDR.6                | SADDR.5       | SADDR.4                     | SADDR.3        | SADDR.2      | SADDR.1      | SADD      |

| Mnem     | onic: SADD    | R                      |               |                             |                |              | A            | ddress:   |

| BIT      | NAME          | FUNCTIO                | N             |                             |                |              |              |           |

| 7~0      | SADDR         |                        |               | be programr<br>ave process  |                |              | adcast addre | ess for s |

| PORT     |               | "On                    |               |                             |                |              |              |           |

| Bit:     | 7             | 6                      | 5             | 4                           | 3              | 2            | 1            | 0         |

|          | P3.7          | P3.6                   | P3.5          | P3.4                        | P3.3           | P3.2         | P3.1         | P3.0      |

|          |               |                        |               |                             |                |              | A            |           |

# nuvoTon

5

|        | I2CLK.7     | I2CLK.6                                                                                                                                                                                                      | I2CLK.5                                                              | I2CLK.4                                                                      | I2CLK.3                                     | I2CLK.2                      | I2CLK.1                 | I2CLK.0       |  |  |

|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------|------------------------------|-------------------------|---------------|--|--|

| Mnem   | onic: I2CLK | ,<br>                                                                                                                                                                                                        |                                                                      |                                                                              | Re                                          |                              | A                       | Address: BE   |  |  |

| BIT    | NAME        | FUNCT                                                                                                                                                                                                        | ION                                                                  |                                                                              | 21-1                                        |                              |                         |               |  |  |

| 7-0    | 12CLK.[7    | ':0] The I2                                                                                                                                                                                                  | C clock rate                                                         | e bits.                                                                      | 123                                         | <u></u>                      |                         |               |  |  |

| I2C TI |             | NTER REGIS                                                                                                                                                                                                   | STER                                                                 |                                                                              |                                             |                              |                         |               |  |  |

| Bit:   | 7           | 6                                                                                                                                                                                                            | 5                                                                    | 4                                                                            | 3                                           | 2                            | 1                       | 0             |  |  |

|        | -           | -                                                                                                                                                                                                            | -                                                                    | -                                                                            | - 3                                         | ENTI                         | DIV4                    | TIF           |  |  |

| Mnem   | onic: I2TIM | ER                                                                                                                                                                                                           |                                                                      |                                                                              |                                             | 1992                         | F                       | Address: BF   |  |  |

| BIT    | NAME        | FUNCTIC                                                                                                                                                                                                      | N                                                                    |                                                                              |                                             | ~ (I)                        | 2 VD                    |               |  |  |

| 7~3    | -           | Reserved                                                                                                                                                                                                     | J.                                                                   |                                                                              |                                             | 3                            | he                      | 26            |  |  |

| I      |             | Enable I2                                                                                                                                                                                                    | C 14-bits T                                                          | imer Counte                                                                  | r:                                          |                              |                         |               |  |  |

| _      |             | 0: Disable                                                                                                                                                                                                   | e 14-bits Ti                                                         | mer Counter                                                                  | count.                                      |                              |                         |               |  |  |

| 2      | ENTI        | 1: Enable 14-bits Timer Counter count. After enable ENTI and ENSI, the 14-bit counter will be counted. When SI flag of I2C is set, the counter will stop to count and 14-bits Timer Counter will be cleared. |                                                                      |                                                                              |                                             |                              |                         |               |  |  |

|        |             | I2C Time                                                                                                                                                                                                     | I2C Timer Counter clock source divide function:                      |                                                                              |                                             |                              |                         |               |  |  |

| 1      | DIV4        | 0: The 14                                                                                                                                                                                                    | 0: The 14-bits Timer Counter source clock is F <sub>CPU</sub> clock. |                                                                              |                                             |                              |                         |               |  |  |

|        |             | 1: The 14-bits Timer Counter source clock is divided by 4.                                                                                                                                                   |                                                                      |                                                                              |                                             |                              |                         |               |  |  |

|        |             | The I2C                                                                                                                                                                                                      | The I2C Timer Counter count flag:                                    |                                                                              |                                             |                              |                         |               |  |  |

|        |             | 0: The 14                                                                                                                                                                                                    | 0: The 14-bits Timer Counter is not overflow.                        |                                                                              |                                             |                              |                         |               |  |  |

| 0      | TIF         | ENSI                                                                                                                                                                                                         | = [1,1]) the                                                         | r Counter is<br>e SI must b<br>outine will be                                | e cleared. I                                | f I2C interru                | upt is enable           | ed. The I20   |  |  |

| I2C C  | ONTROL R    | EGISTER                                                                                                                                                                                                      |                                                                      |                                                                              |                                             |                              |                         |               |  |  |

| Bit:   | 7           | 6                                                                                                                                                                                                            | 5                                                                    | 4                                                                            | 3                                           | 2                            | 1                       | 0             |  |  |

|        | -           | ENSI                                                                                                                                                                                                         | STA                                                                  | STO                                                                          | SI                                          | AA                           | -                       | -             |  |  |

| Mnem   | onic: I2CON | 1                                                                                                                                                                                                            | •                                                                    |                                                                              |                                             |                              | ŀ                       | Address: C0   |  |  |

| BIT    | NAME        | FUNCTI                                                                                                                                                                                                       | ON                                                                   |                                                                              |                                             |                              |                         |               |  |  |

| 7      | 1           | Reserve                                                                                                                                                                                                      | d.                                                                   |                                                                              |                                             |                              |                         |               |  |  |

| 6      | ENSI        | impec<br>addre<br>forcec                                                                                                                                                                                     | lance state<br>ssed slave<br>I to "0". No                            | erial Functio<br>. SDA and S<br>mode or it<br>other bits a<br>ain I/O ports. | SCL input si<br>is not addi<br>re affected. | gnals are ig<br>ressable, an | nored, I2C<br>d STO bit | is not in the |  |  |

1: Enable I2C Serial Function. The P1.2 and P1.3 port latches must be to logic 1.

STA

STA

O: The STA bit is reset, no START condition or repeated START condition will

# nuvoTon

|               | -          | NVMADD<br>R.6                                                       | NVMADD<br>R.5                                                                                                                                                                                                                                                                                                                              | NVMADD<br>R.4                                     | NVMADD<br>R.3                              | NVMADD<br>R.2                                  | NVMADD<br>R.1                                                                | NVMADD<br>R.0              |  |  |

|---------------|------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------|----------------------------|--|--|

| Mnem          | onic: NVMA | DDR                                                                 |                                                                                                                                                                                                                                                                                                                                            |                                                   | No.                                        |                                                | Ad                                                                           | ddress: C6h                |  |  |

| BIT           | NAME       | FU                                                                  | FUNCTION                                                                                                                                                                                                                                                                                                                                   |                                                   |                                            |                                                |                                                                              |                            |  |  |

| 7             | -          | Re                                                                  | served                                                                                                                                                                                                                                                                                                                                     |                                                   | CO.                                        | Sec. 1                                         |                                                                              |                            |  |  |

| 6~0           | NVMADDF    | R.[6:0] Th                                                          | e NVM addre                                                                                                                                                                                                                                                                                                                                | ess:                                              | N/                                         | NY.                                            |                                                                              |                            |  |  |

|               |            |                                                                     | e register ir<br>mory space.                                                                                                                                                                                                                                                                                                               |                                                   | M data me                                  | emory addre                                    | ess on On-                                                                   | Chip code                  |  |  |

| ТІМЕГ         | D ACCESS   |                                                                     |                                                                                                                                                                                                                                                                                                                                            |                                                   |                                            | -m                                             | 5                                                                            |                            |  |  |

| Bit:          | 7          | 6                                                                   | 5                                                                                                                                                                                                                                                                                                                                          | 4                                                 | 3                                          | 2                                              | 1. 0                                                                         | 0                          |  |  |

|               | TA.7       | TA.6                                                                | TA.5                                                                                                                                                                                                                                                                                                                                       | TA.4                                              | TA.3                                       | TA.2                                           | TA.1                                                                         | TA.0                       |  |  |

| Mnem          | ionic: TA  |                                                                     |                                                                                                                                                                                                                                                                                                                                            |                                                   |                                            |                                                | Ad                                                                           | ddress: C7h                |  |  |

| BIT           | NAME       | FUNCTIO                                                             | N                                                                                                                                                                                                                                                                                                                                          |                                                   |                                            |                                                | 0                                                                            | 20                         |  |  |

|               |            |                                                                     | Timed Access register:<br>Timed Access register controls the access to protected bits. To access<br>otected bits, the user must first write AAH to the TA. This must be immediately<br>lowed by a write of 55H to TA. Now a window is opened in the protected bits<br>three machine cycles, during which the user can write to these bits. |                                                   |                                            |                                                |                                                                              |                            |  |  |

| 7-0           | TA.[7:0]   | The Time<br>protected<br>followed                                   | ed Access r<br>bits, the use<br>by a write of                                                                                                                                                                                                                                                                                              | er must first<br>55H to TA.                       | write AAH to<br>Now a wino                 | o the TA. Th<br>dow is opene                   | is must be in<br>ed in the pro                                               | mmediately<br>otected bits |  |  |

|               | TA.[7:0]   | The Time<br>protected<br>followed<br>for three                      | ed Access r<br>bits, the use<br>by a write of                                                                                                                                                                                                                                                                                              | er must first<br>55H to TA.                       | write AAH to<br>Now a wino                 | o the TA. Th<br>dow is opene                   | is must be in<br>ed in the pro                                               | mmediately<br>otected bits |  |  |

|               |            | The Time<br>protected<br>followed<br>for three                      | ed Access r<br>bits, the use<br>by a write of                                                                                                                                                                                                                                                                                              | er must first<br>55H to TA.                       | write AAH to<br>Now a wino                 | o the TA. Th<br>dow is opene                   | is must be in<br>ed in the pro                                               | mmediately<br>otected bits |  |  |

| TIMEF         | R 2 CONTRO | The Time<br>protected<br>followed<br>for three                      | ed Access r<br>bits, the use<br>by a write of<br>machine cyc                                                                                                                                                                                                                                                                               | er must first<br>55H to TA.<br>les, during w      | write AAH to<br>Now a wind<br>hich the use | o the TA. Th<br>dow is open<br>er can write t  | is must be in<br>ed in the pro<br>o these bits.                              | mmediately<br>otected bits |  |  |

| TIMEF<br>Bit: | 7<br>7     | The Timprotected<br>followed<br>for three<br><b>DL</b><br>6<br>EXF2 | ed Access r<br>bits, the use<br>by a write of<br>machine cyc                                                                                                                                                                                                                                                                               | er must first<br>55H to TA.<br>les, during w<br>4 | write AAH to<br>Now a wino<br>hich the use | o the TA. Th<br>dow is opene<br>er can write t | is must be in<br>ed in the pro-<br>o these bits.<br>1<br>$C / \overline{T2}$ | nmediately<br>ptected bits |  |  |

|   |       | I ONCTION                                                                                                                                                                                                                                                                                                                                                                    |

|---|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |       | Timer 2 overflow flag:                                                                                                                                                                                                                                                                                                                                                       |

| 7 | TF2   | Timer 2 overflow flag: This bit is set when Timer 2 overflows. It is also set when<br>the count is equal to the capture register in down count mode. It can be set only<br>if RCLK and TCLK are both 0. It is cleared only by software. Software can also<br>set or clear this bit.                                                                                          |

| 6 | EXF2  | Timer 2 External Flag: A negative transition on the T2EX pin (P1.1) or timer 2 overflow will cause this flag to set based on the CP/ $\overline{RL2}$ , EXEN2 and DCEN bits. If set by a negative transition, this flag must be cleared by software. Setting this bit in software or detection of a negative transition on T2EX pin will force a timer interrupt if enabled. |

|   | and 4 | Receive Clock Flag: This bit determines the serial port time-base when receiving                                                                                                                                                                                                                                                                                             |

| 5 | RCLK  | data in serial modes 1 or 3. If it is 0, then timer 1 overflow is used for baud rate generation, otherwise timer 2 overflow is used. Setting this bit forces timer 2 in baud rate generator mode.                                                                                                                                                                            |

|   |       | - 40 -                                                                                                                                                                                                                                                                                                                                                                       |

|   | No.   | 7 TF2<br>6 EXF2                                                                                                                                                                                                                                                                                                                                                              |

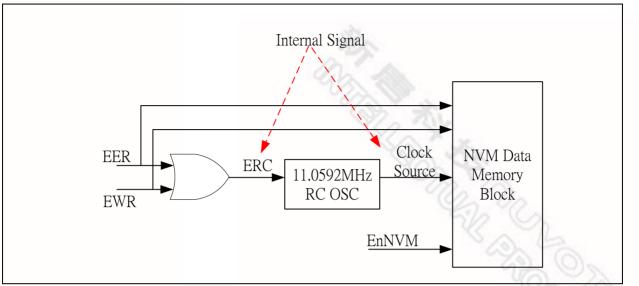

|     |       | 1: Set this bit to write NVM bytes and program counter will halt at this instruction.<br>After write is finished, program counter will kept next instruction then executed. |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | EnNVM | To enable read NVM data memory area.                                                                                                                                        |

|     |       | 0: To disable the MOVX instruction to read NVM data memory.                                                                                                                 |

|     |       | 1: To enable the MOVX instruction to read NVM data memory, the External RAM or AUX-RAM will be disabled.                                                                    |

| 4-0 | -     | Reserved                                                                                                                                                                    |

#### NVM DATA

| Bit: | 7            | 6            | 5            | 4            | 3           | 2            | 10           | 0            |

|------|--------------|--------------|--------------|--------------|-------------|--------------|--------------|--------------|

|      | NVMDAT.<br>7 | NVMDAT.<br>6 | NVMDAT.<br>5 | NVMDAT.<br>4 | NVMDAT<br>3 | NVMDAT.<br>2 | NVMDAT.<br>1 | NVMDAT.<br>0 |

|      | 1            | 0            | 5            | 4            | 3           | 2            | Sall         | 0            |

#### Mnemonic: NVMDATA

| BIT | NAME         | FUNCTION                                                               |

|-----|--------------|------------------------------------------------------------------------|

| 7~0 | NVMDAT.[7:0] | The NVM data write register. The read NVM data is by MOVC instruction. |

#### **PROGRAM STATUS WORD**

|      | 01701 |    |    |     |     |    |    |   |

|------|-------|----|----|-----|-----|----|----|---|

| Bit: | 7     | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|      | CY    | AC | F0 | RS1 | RS0 | OV | F1 | Р |

|      |       |    |    |     |     |    |    |   |

#### Mnemonic: PSW

Address: D0h

Address: CFh

| BIT | NAME    | FUNCTION                                                                                                                                          |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|     | СҮ      | Carry flag:                                                                                                                                       |

| 7   |         | Set for an arithmetic operation which results in a carry being generated from the ALU. It is also used as the accumulator for the bit operations. |

| 6   | AC      | Auxiliary carry:                                                                                                                                  |

|     | AC      | Set when the previous operation resulted in a carry from the high order nibble.                                                                   |

| E   | F0      | User flag 0:                                                                                                                                      |

| 5   |         | The General purpose flag that can be set or cleared by the user.                                                                                  |

| 4~3 | RS1~RS0 | Register bank select bits.                                                                                                                        |

| 0 2 | ov      | Overflow flag:                                                                                                                                    |

| 2   |         | Set when a carry was generated from the seventh bit but not from the 8th bit as a result of the previous operation, or vice-versa.                |

| 1   | F1      | User Flag 1:                                                                                                                                      |

|     | En l    | The General purpose flag that can be set or cleared by the user software.                                                                         |

| 0   |         | Parity flag:                                                                                                                                      |

| 0   | P       | Set/cleared by hardware to indicate odd/even number of 1's in the accumulator.                                                                    |

RS.1-0: Register Bank Selection Bits:

# nuvoTon

|      | PCAPH      | PBOH      | -           | PWDIH             | -          | -               | PKBH            | PI2H         |  |

|------|------------|-----------|-------------|-------------------|------------|-----------------|-----------------|--------------|--|

| Mnem | onic: IP1H |           |             |                   | *          |                 |                 | Address: F7h |  |

| BIT  | NAME       | FUNCTIC   | N           | 1                 | 25         | ~               |                 |              |  |

| 7    | PCAPH      | 1: To set | interrupt h | igh priority of   | Input Ca   | oture 0 as hig  | hest priority l | evel.        |  |

| 6    | РВОН       | 1: To set | interrupt h | igh priority of   | Brownou    | t is highest p  | riority level.  |              |  |

| 5    | -          | Reserved  |             |                   |            | XAX             | 36              |              |  |

| 4    | PWDIH      | 1: To set | interrupt h | igh priority of   | Watchdo    | g is highest p  | priority level. |              |  |

| 3~2  | -          | Reserved  |             |                   |            | 20              | 20              |              |  |

| 1    | РКВН       | 1: To set | interrupt h | igh priority of   | Keypad i   | s highest pric  | ority level.    | A.           |  |

| 0    | PI2H       | 1: To set | interrupt h | igh priority of   | I2C is hig | hest priority   | level.          | The          |  |

| NTER |            | RITY 1    |             |                   |            |                 | 2               | 6            |  |

| Bit: | 7          | 6         | 5           | 4                 | 3          | 2               | 1 1             | 0 0          |  |

|      | PCAP       | PBO       | -           | PWDI              | -          | -               | PKB             | Pl2          |  |

| Vnem | onic: IP1  |           |             |                   |            |                 |                 | Address: F8h |  |

| BIT  | NAME       | FUNCTIO   | N           |                   |            |                 |                 | 00           |  |

| 7    | PCAP       | 1: To set | interrupt p | priority of Input | Capture    | 0 as higher p   | oriority level. | 6            |  |

| 6    | РВО        | 1: To set | interrupt p | priority of Brow  | nout is h  | igher priority  | level.          |              |  |

| 5    | -          | Reserved  |             |                   |            |                 |                 |              |  |

| 4    | PWDI       | 1: To set | interrupt p | priority of Wate  | hdog is l  | nigher priority | v level.        |              |  |

| 3~2  | -          | Reserved  |             |                   |            |                 |                 |              |  |

|      |            |           | Reserved.   |                   |            |                 |                 |              |  |

|     | NAME | FUNCTION                                                                  |

|-----|------|---------------------------------------------------------------------------|

| 7   | PCAP | 1: To set interrupt priority of Input Capture 0 as higher priority level. |

| 6   | PBO  | 1: To set interrupt priority of Brownout is higher priority level.        |

| 5   | -    | Reserved.                                                                 |

| 4   | PWDI | 1: To set interrupt priority of Watchdog is higher priority level.        |

| 3~2 | -    | Reserved.                                                                 |

| 1   | PKB  | 1: To set interrupt priority of Keypad is higher priority level.          |

| 0   | PI2  | 1: To set interrupt priority of I2C is higher priority level.             |

|     |      |                                                                           |

### 9. INSTRUCTION

The N79E352(R) executes all the instructions of the standard 8052 family. The operation of these instructions, their effect on the flag bits and the status bits is exactly the same. However, timing of these instructions is different. The reason for this is two fold. Firstly, in the N79E352(R), each machine cycle consists of 4 clock periods, while in the standard 8052 it consists of 12 clock periods. Also, in the N79E352(R) there is only one fetch per machine cycle i.e. 4 clocks per fetch, while in the standard 8052 there can be two fetches per machine cycle, which works out to 6 clocks per fetch.

The advantage the N79E352(R) has is that since there is only one fetch per machine cycle, the number of machine cycles in most cases is equal to the number of operands that the instruction has. In case of jumps and calls there will be an additional cycle that will be needed to calculate the new address. But overall the N79E352(R) reduces the number of dummy fetches and wasted cycles, thereby improving efficiency as compared to the standard 8052.

| Instruction | Carry | Overflow | Auxiliary<br>Carry | Instruction | Carry | Overflow | Auxiliary<br>Carry |

|-------------|-------|----------|--------------------|-------------|-------|----------|--------------------|

| ADD         | Х     | Х        | Х                  | CLR C       | 0     | Vic      |                    |

| ADDC        | Х     | Х        | х                  | CPL C       | Х     | y-       | De 1               |

| SUBB        | Х     | Х        | Х                  | ANL C, bit  | Х     |          | 1. 105             |

| MUL         | 0     | Х        |                    | ANL C, bit  | Х     |          | Sis                |

| DIV         | 0     | Х        |                    | ORL C, bit  | Х     |          | 1                  |

| DA A        | Х     |          |                    | ORL C, bit  | Х     |          |                    |

| RRC A       | Х     |          |                    | MOV C, bit  | Х     |          |                    |

| RLC A       | Х     |          |                    | CJNE        | Х     |          |                    |

| SETB C      | 1     |          |                    |             |       |          |                    |

| Table 9- | -1: Instructions | that affect | Flag settings |

|----------|------------------|-------------|---------------|

|----------|------------------|-------------|---------------|

A "X" indicates that the modification is as per the result of instruction.

Instruction Timing for N79E352(R), continued

| Instruction        | HEX<br>Op-Code | Bytes | N79E352(R)<br>Machine<br>Cycles | N79E352(R)<br>Clock<br>Cycles | 8052<br>Clock<br>Cycles | N79E352(R) v<br>8052 Speed<br>Ratio |

|--------------------|----------------|-------|---------------------------------|-------------------------------|-------------------------|-------------------------------------|

| MOV R1, direct     | A9             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R2, direct     | AA             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R3, direct     | AB             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R4, direct     | AC             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R5, direct     | AD             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R6, direct     | AE             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R7, direct     | AF             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R0, #data      | 78             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R1, #data      | 79             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R2, #data      | 7A             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R3, #data      | 7B             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R4, #data      | 7C             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R5, #data      | 7D             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R6, #data      | 7E             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R7, #data      | 7F             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV @R0, A         | F6             | 1     | 1                               | 4                             | 12                      | 3                                   |

| MOV @R1, A         | F7             | 1     | 1                               | 4                             | 12                      | 3                                   |

| MOV @R0, direct    | A6             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV @R1, direct    | A7             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV @R0, #data     | 76             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV @R1, #data     | 77             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, A      | F5             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R0     | 88             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R1     | 89             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R2     | 8A             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R3     | 8B             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R4     | 8C             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R5     | 8D             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R6     | 8E             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R7     | 8F             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, @R0    | 86             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, @R1    | 87             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, direct | 85             | 3     | 3                               | 12                            | 24                      | 2                                   |

| MOV direct, #data  | 75             | 3     | 3                               | 12                            | 24                      | 2                                   |

| MOV DPTR, #data 16 | 90             | 3     | 3                               | 12                            | 24                      | 2                                   |

| MOVC A, @A+DPTR    | 93             | 1     | 2                               | 8                             | 24                      | 3                                   |

Instruction Timing for N79E352(R), continued

| Instruction       | HEX<br>Op-Code | Bytes | N79E352(R)<br>Machine<br>Cycles | N79E352(R)<br>Clock<br>Cycles | 8052<br>Clock<br>Cycles | N79E352(R) vs<br>8052 Speed<br>Ratio |

|-------------------|----------------|-------|---------------------------------|-------------------------------|-------------------------|--------------------------------------|

| MOVX A, @R0       | E2             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOVX A, @R1       | E3             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOVX A, @DPTR     | E0             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOVX @R0, A       | F2             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOVX @R1, A       | F3             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOVX @DPTR, A     | F0             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOV C, bit        | A2             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| MOV bit, C        | 92             | 2     | 2                               | 8                             | 24                      | 3                                    |

| ORL A, R0         | 48             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R1         | 49             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R2         | 4A             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R3         | 4B             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R4         | 4C             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R5         | 4D             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R6         | 4E             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R7         | 4F             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, @R0        | 46             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, @R1        | 47             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, direct     | 45             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| ORL A, #data      | 44             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| ORL direct, A     | 42             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| ORL direct, #data | 43             | 3     | 3                               | 12                            | 24                      | 2                                    |

| ORL C, bit        | 72             | 2     | 2                               | 8                             | 24                      | 3                                    |

| ORL C, /bit       | A0             | 2     | 2                               | 6                             | 24                      | 3                                    |

| PUSH direct       | C0             | 2     | 2                               | 8                             | 24                      | 3                                    |

| POP direct        | D0             | 2     | 2                               | 8                             | 24                      | 3                                    |

| RET               | 22             | 1     | 2                               | 8                             | 24                      | 3                                    |

| RETI              | 32             | 1     | 2                               | 8                             | 24                      | 3                                    |

| RL A              | 23             | 1     | 1                               | 4                             | 12                      | 3                                    |

| RLC A             | 33             | 1     | 1                               | 4                             | 12                      | 3                                    |