Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

⊡XFI

| Product Status             | Not For New Designs                                                                    |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 24MHz                                                                                  |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, UART/USART                                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                             |

| Number of I/O              | 38                                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | 128 x 8                                                                                |

| RAM Size                   | 256 x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                            |

| Data Converters            | -                                                                                      |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 48-LQFP                                                                                |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/n79e352alg |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5. PIN DESCRIPTIONS

| SYMBOL       | Alternate<br>Function 1 | Alternate<br>function 2 | Туре       | DESCRIPTIONS                                                                                                                                                                                                                                                                                                                       |

|--------------|-------------------------|-------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĒĀ           |                         |                         | I          | <b>EXTERNAL ACCESS ENABLE</b> : This pin forces the processor to execute out of external ROM. It should be kept high to access internal ROM. The ROM address and data will not be present on the bus if $\overline{EA}$ pin is high and the program counter is within internal ROM area. Otherwise they will be present o the bus. |

| PSEN         |                         |                         | 0          | PROGRAM STORE ENABLE: PSEN enables the external ROM data onto the Port 0 address/data bud during fetch and MOVC operations. When internal                                                                                                                                                                                          |

|              |                         |                         |            | ROM access is performed, no PSEN strobe signal outputs from this pin.                                                                                                                                                                                                                                                              |

| ALE          |                         |                         | 0          | <b>ADDRESS LATCH ENABLE</b> : ALE is used to enable<br>the address latch that separates the address from<br>the data on Port 0.                                                                                                                                                                                                    |

| XTAL1        | P5.1                    |                         | I/O        | <b>CRYSTAL1</b> : This is the crystal oscillator input. This pin may be driven by an external clock or configurable i/o pin, P5.1.                                                                                                                                                                                                 |

| XTAL2        | P5.0                    |                         | I/O        | <b>CRYSTAL2</b> : This is the crystal oscillator output. It is the inversion of XTAL1. Also a configurable i/o pin, P5.0.                                                                                                                                                                                                          |

| VDD          |                         |                         | Р          | <b>POWER SUPPLY</b> : Supply voltage for operation.                                                                                                                                                                                                                                                                                |

| VSS          |                         |                         | Р          | GROUND: Ground potential.                                                                                                                                                                                                                                                                                                          |

| RST          |                         |                         |            | <b>RESET:</b> A high on this pin for two machine cycles while the oscillator is running resets the device.                                                                                                                                                                                                                         |

| P0.0         | KB0                     | AD0                     | I/O        | PORT0:                                                                                                                                                                                                                                                                                                                             |

| P0.1         | KB1                     | AD1                     | I/O        | Support 4 mode output and 2 mode input.                                                                                                                                                                                                                                                                                            |

| P0.2         | KB2<br>KB3              | AD2<br>AD3              | I/O<br>I/O | Multifunction pins for AD0-7and KB0-7.                                                                                                                                                                                                                                                                                             |

| P0.3<br>P0.4 | KB3<br>KB4              | AD3<br>AD4              | 1/O<br>1/O |                                                                                                                                                                                                                                                                                                                                    |

| P0.4         | KB4<br>KB5              | AD4<br>AD5              | 1/O        | -                                                                                                                                                                                                                                                                                                                                  |

| P0.6         | KB6                     | AD6                     | 1/O        |                                                                                                                                                                                                                                                                                                                                    |

| P0.7         | KB7                     | AD7                     | I/O        |                                                                                                                                                                                                                                                                                                                                    |

| P1.0         | 42.                     | T2                      | I/O        | PORT1:                                                                                                                                                                                                                                                                                                                             |

| P1.1         | 20                      | T2EX                    | I/O        |                                                                                                                                                                                                                                                                                                                                    |

| P1.2         | 5 40                    | SDA                     | I/O        | Support 4 mode output and 2 mode input.                                                                                                                                                                                                                                                                                            |

| P1.3         | 20                      | SCL                     | I/O        | Multifunction pins for SDA & SCL (I2C), T2, T2EX                                                                                                                                                                                                                                                                                   |

| P1.4         | VA                      | PWM0                    | I/O        | and PWM0-1.                                                                                                                                                                                                                                                                                                                        |

| P1.5         |                         | PWM1                    | I/O        | _                                                                                                                                                                                                                                                                                                                                  |

| P1.6         | ICPDAT                  | Reg                     | I/O        | _                                                                                                                                                                                                                                                                                                                                  |

| P1.7         | ICPCLK                  | AM                      | I/O        |                                                                                                                                                                                                                                                                                                                                    |

## 6. FUNCTIONAL DESCRIPTION

N79E352(R) architecture consist of a 4T 8051 core controller surrounded by various registers, 8K bytes Flash EPROM, 256 bytes of RAM, 128 bytes NVM Data Flash EPROM; three timer/counters, one UART serial port, one I2C serial port, eight keyboard interrupt input, 2-channel PWM with 8-bit counter and Flash EPROM program by Writer.

## 6.1 On-Chip Flash EPROM

N79E352(R) includes one 8K bytes of main Flash EPROM for application program which need Writer to program the Flash EPROM.

## 6.2 I/O Ports

N79E352(R) has four 8-bit, one 4-bit port and one 2-bit port, with at least 36 I/O pins. All ports (except port 4) can be used as four outputs mode when it may set by PxM1.y and PxM2.y registers, it has strong pull-ups and pull-downs, and does not need any external pull-ups. Otherwise it can be used as general I/O port as open drain circuit. All ports can be used bi-directional and these are as I/O ports. These ports are not true I/O, but rather are pseudo-I/O ports. This is because these ports have strong pull-downs and weak pull-ups.

### 6.3 Serial I/O

N79E352(R) has one UART serial port that is functionally similar to the serial port of the original 8052 family. However the serial port on N79E352(R) can operate in different modes in order to obtain timing similarity as well. The Serial port has the enhanced features of Automatic Address recognition and Frame Error detection.

### 6.4 Timers

The device has total three 16-bit timers; two 16-bit timers that have functions similar to the timers of the 8052 family, and third timer is capable to function as timer and also provide capture support. When used as timers, user has a choice to set 12 or 4 clocks per count that emulates the timing of the original 8052. Each timer's count value is stored in two SFR locations that can be written or read by software. There are also some other SFRs associated with the timers that control their mode and operation.

### 6.5 Interrupts

The Interrupt structure in N79E352(R) is slightly different from that of the standard 8052. Due to the presence of additional features and peripherals, the number of interrupt sources and vectors has been increased.

### 6.6 Data Pointers

The original 8052 had only one 16-bit Data Pointer (DPL, DPH). In the N79E352(R), there is an additional 16-bit Data Pointer (DPL1, DPH1). This new Data Pointer uses two SFR locations which were unused in the original 8052. In addition there is an added instruction, DEC DPTR (op-code A5H), which helps in improving programming flexibility for the user.

## 6.7 Architecture

N79E352(R) is based on the standard 8052 device. It is built around an 8-bit ALU that uses internal registers for temporary storage and control of the peripheral devices. It can execute the standard 8052 NO TO C instruction set.

### 6.7.1 ALU

The ALU is the heart of the N79E352(R). It is responsible for the arithmetic and logical functions. It is also used in decision making, in case of jump instructions, and is also used in calculating jump addresses. The user cannot directly use the ALU, but the Instruction Decoder reads the op-code, decodes it, and sequences the data through the ALU and its associated registers to generate the required result. The ALU mainly uses the ACC which is a special function register (SFR) on the chip. Another SFR, namely B register is also used in Multiply and Divide instructions. The ALU generates several status signals which are stored in the Program Status Word register (PSW).

### 6.7.2 Accumulator

The Accumulator (ACC) is the primary register used in arithmetic, logical and data transfer operations in N79E352(R). Since the Accumulator is directly accessible by the CPU, most of the high speed instructions make use of the ACC as one argument.

### 6.7.3 B Register

This is an 8-bit register that is used as the second argument in the MUL and DIV instructions. For all other instructions it can be used simply as a general purpose register.

## 6.7.4 Program Status Word:

This is an 8-bit SFR that is used to store the status bits of the ALU. It holds the Carry flag, the Auxiliary Carry flag, General purpose flags, the Register Bank Select, the Overflow flag, and the Parity flag.

### 6.7.5 Scratch-pad RAM

N79E352(R) has a 256 bytes on-chip scratch-pad RAM. These can be used by the user for temporary storage during program execution. A certain section of this RAM is bit addressable, and can be directly addressed for this purpose.

### 6.7.6 Stack Pointer

N79E352(R) has an 8-bit Stack Pointer which points to the top of the Stack. This stack resides in the Scratch Pad RAM. Hence the size of the stack is limited by the size of this RAM.

### 6.8 Power Management

Like the standard 80C52, the N79E352(R) also has IDLE and POWER DOWN modes of operation. The N79E352(R) provides a new Economy mode which allow user to switch the internal clock rate divided by either 4, 64 or 1024. In the IDLE mode, the clock to the CPU core is stopped while the timers, serial ports and interrupts clock continue to operate. In the POWER DOWN mode, all the clock ar. are stopped and the chip operation is completely stopped. This is the lowest power consumption state.

- 12 -

|       | _          |          |          |          |          |          |          |          |          |                                   |

|-------|------------|----------|----------|----------|----------|----------|----------|----------|----------|-----------------------------------|

|       | FFH        |          |          |          |          | 3        | 5        |          |          |                                   |

|       |            |          |          |          | Indired  | ct RAN   | 1        |          |          |                                   |

|       | 80H<br>7FH |          |          |          | 19       | 12       | 1        |          |          |                                   |

|       | 7FH        |          |          |          |          |          |          |          |          |                                   |

|       |            |          |          |          | Direc    | t RAM    |          |          |          | 1                                 |

|       | 30H<br>2FH | 7F       | 7E       | 7D       | 7C       | 7B       | 7A       | 79       | 78       | 23                                |

|       | 2EH        | 77       | 76       | 75       | 74       | 73       | 72       | 71       | 70       | 2.0.                              |

|       | 2DH        | 6F       | 6E       | 6D       | 6C       | 6B       | 6A       | 69       | 68       | So Co                             |

|       | 2CH        |          | 66       | 65       | 64       | 63       | 62       | 61       | 60       | Sam.                              |

|       | 2BH        | 5F       | 5E       | 5D       | 5C       | 5B       | 5A       | 59       | 58       | 20 0                              |

|       | 2AH<br>29H | 57<br>4F | 56<br>4E | 55<br>4D | 54<br>4C | 53<br>4B | 52<br>4A | 51<br>49 | 50<br>48 | VO. VA                            |

|       | 29H<br>28H | 4F<br>47 | 4E<br>46 | 4D<br>45 | 40       | 4B<br>43 | 4A<br>42 | 49<br>41 | 48<br>40 | Yon G                             |

|       | 27H        | 3F       | 3E       | 3D       | 3C       | 3B       | 3A       | 39       | 38       | 62                                |

|       | 26H        | 37       | 36       | 35       | 34       | 33       | 32       | 31       | 30       |                                   |

|       | 25H        | 2F       | 2E       | 2D       | 2C       | 2B       | 2A       | 29       | 28       | 12                                |

|       | 24H        | 27       | 26       | 25       | 24       | 23       | 22       | 21       | 20       |                                   |

|       | 23H<br>22H | 1F<br>17 | 1E<br>16 | 1D<br>15 | 1C<br>14 | 1B<br>13 | 1A<br>12 | 19<br>11 | 18<br>10 |                                   |

|       | 22H<br>21H | 0F       | 0E       | 0D       | 0C       | 0B       | 0A       | 09       | 08       |                                   |

|       | 20H        | 07       | 06       | 05       | 04       | 03       | 02       | 01       | 00       |                                   |

|       | 1FH        |          |          |          | Baı      | nk 3     |          |          |          |                                   |

|       | 18H<br>17H |          |          |          |          |          |          |          |          |                                   |

|       | 10H<br>0FH |          |          |          | Bai      | nk 2     |          |          |          |                                   |

| ·     |            |          |          |          | Bai      | nk 1     |          |          |          |                                   |

|       | 08H<br>07H |          |          |          | Bai      | nk 0     |          |          |          |                                   |

| A. A. | 00H        |          |          |          |          | -        |          |          |          |                                   |

|       |            | Fiç      | gure     | 7-3: \$  | Scrat    | ch-pa    | ad R/    | ٩M       |          |                                   |

|       |            |          |          |          |          |          |          |          |          |                                   |

|       |            |          |          |          |          |          |          |          |          |                                   |

|       |            |          |          |          |          |          |          |          |          |                                   |

|       |            |          |          |          |          |          |          |          |          |                                   |

|       |            |          |          |          |          |          |          |          |          |                                   |

|       |            |          |          |          |          |          |          |          |          |                                   |

|       |            |          |          |          |          |          |          |          |          |                                   |

|       |            |          |          |          |          |          |          | Р        | ublica   | ution Release Date: Jul, 29, 2009 |

|       |            |          |          |          | - 15 -   | -        |          |          |          | Revision A06                      |

|       |            |          |          |          |          |          |          |          |          |                                   |

|       |            |          |          |          |          |          |          |          |          |                                   |

Figure 7-3: Scratch-pad RAM

# ηυνοτοη

## 8.2 SFR Detail Bit Descriptions

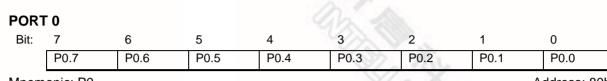

Mnemonic: P0

Address: 80h

Port 0 is an open-drain bi-directional I/O port. This port provides a multiplexed low order address/data bus during accesses to external memory. The ports also support alternate input function for Keyboard pins (KB0-7).

| BIT | NAME | FUNCTION                              | Sp Co.  |

|-----|------|---------------------------------------|---------|

| 7   | P0.7 | AD7 or KB7 or I/O pin by alternative. | X AL    |

| 6   | P0.6 | AD6 or KB6 or I/O pin by alternative. | ~~ O.   |

| 5   | P0.5 | AD5 or KB5 or I/O pin by alternative. |         |

| 4   | P0.4 | AD4 or KB4 or I/O pin by alternative. | ~~~ (O) |

| 3   | P0.3 | AD3 or KB3 or I/O pin by alternative. | S22     |

| 2   | P0.2 | AD2 or KB2 or I/O pin by alternative. | ~ (Y)_  |

| 1   | P0.1 | AD1 or KB1 or I/O pin by alternative. | 9       |

| 0   | P0.0 | AD0 or KB0 or I/O pin by alternative. |         |

Note: The initial value of the port is set by CONFIG0.PRHI bit. The default setting for CONFIG0.PRHI =1 which the alternative function output is turned on upon reset. If CONFIG0.PRHI is set to 0, the user has to write a 1 to port SFR to turn on the alternative function output.

### **STACK POINTER**

| Bit: | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

|      | SP.7 | SP.6 | SP.5 | SP.4 | SP.3 | SP.2 | SP.1 | SP.0 |

Mnemonic: SP

| Address: 81h |

|--------------|

|--------------|

Address: 82h

| BIT | NAME     | FUNCTION                                                                                                                                 |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | SP.[7:0] | The Stack Pointer stores the Scratch-pad RAM address where the stack begins.<br>In other words it always points to the top of the stack. |

### DATA POINTER LOW

| Bit: | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| NC   | DPL.7 | DPL.6 | DPL.5 | DPL.4 | DPL.3 | DPL.2 | DPL.1 | DPL.0 |

### Mnemonic: DPL

| BIT | NAME      | FUNCTION                                                       |

|-----|-----------|----------------------------------------------------------------|

| 7-0 | DPL.[7:0] | This is the low byte of the standard 8052 16-bit data pointer. |

|     |           | 23) (0)-                                                       |

### DATA POINTER HIGH

| Bit: | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|---|---|---|---|---|---|---|---|

|      |   |   |   |   |   |   |   |   |

### **TIMER 2 CAPTURE MSB**

| Bit: | 7            | 6                    | 5            | 4            | 3            | 2                         | 1            | 0            |  |  |  |  |

|------|--------------|----------------------|--------------|--------------|--------------|---------------------------|--------------|--------------|--|--|--|--|

|      | RCAP2H.<br>7 | RCAP2H.<br>6         | RCAP2H.<br>5 | RCAP2H.<br>4 | RCAP2H.<br>3 | RCAP2H.<br>2              | RCAP2H.<br>1 | RCAP2H.<br>0 |  |  |  |  |

| Mnen | nonic: RCAP  | 2H                   |              |              | SY 1         | N.S.                      | A            | ddress: CB   |  |  |  |  |

| BIT  | NAME         | FUNCTION             |              |              |              |                           |              |              |  |  |  |  |

|      |              | Timer 2 Capture MSB: |              |              |              |                           |              |              |  |  |  |  |

| 7-0  | RCAP2H       | capture m            | node. RCAP   |              | ised as the  | ue when a t<br>MSB of a 1 |              |              |  |  |  |  |

| TIME | R 2 LSB      | -                    |              |              |              | 3                         |              | 2            |  |  |  |  |

| Bit: | 7            | 6                    | 5            | 4            | 3            | 2                         | 100          | 0            |  |  |  |  |

|      | TL2.7        | TL2.6                | TL2.5        | TL2.4        | TL2.3        | TL2.2                     | TL2.1        | TL2.0        |  |  |  |  |

| Mnen | nonic: TL2   |                      |              |              |              |                           | A            | ddress: CC   |  |  |  |  |

| BIT  | NAME         | FUNCTIO              | N            |              |              |                           |              | CO.          |  |  |  |  |

| 7-0  | TL2          | Timer 2 L            | SB.          |              |              |                           |              | 0            |  |  |  |  |

| TIME | R 2 MSB      |                      |              |              |              |                           |              |              |  |  |  |  |

| Bit: | 7            | 6                    | 5            | 4            | 3            | 2                         | 1            | 0            |  |  |  |  |

|      | TH2.7        | TH2.6                | TH2.5        | TH2.4        | TH2.3        | TH2.2                     | TH2.1        | TH2.0        |  |  |  |  |

| Mnen | nonic: TH2   |                      |              |              |              |                           | А            | ddress: CD   |  |  |  |  |

| BIT  | NAME         | FUNCTIO              | N            |              |              |                           |              |              |  |  |  |  |

| 7-0  | TL2          | Timer 2 L            | SB.          |              |              |                           |              |              |  |  |  |  |

| NVM  | CONTROL      |                      |              |              |              |                           |              |              |  |  |  |  |

| Bit: | 7            | 6                    | 5            | 4            | 3            | 2                         | 1            | 0            |  |  |  |  |

|      | EER          | EWR                  | EnNVM        | -            | -            | -                         | -            | -            |  |  |  |  |

| Mnen | nonic: NVMC  | ON                   |              |              |              |                           | A            | ddress: CE   |  |  |  |  |

| BIT  | NAME         | FUNCTIO              | N            |              |              |                           |              |              |  |  |  |  |

| 7    | EER          | NVM pag              | e(n) erase b | pit:         |              |                           |              |              |  |  |  |  |

| BIT | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EER  | NVM page(n) erase bit:                                                                                                                                                                                                                                                                                                                                                                                                      |

| X B | 828  | 0: Without erase NVM page(n).                                                                                                                                                                                                                                                                                                                                                                                               |

|     |      | 1: Set this bit to erase page(n) of NVM. The NVM has <b>8</b> pages and each page have 16 bytes data memory. Initiate page select by programming NVMADDL registers, which will automatically enable page area. When user set this bit, the page erase process will begin and program counter will halt at this instruction. After the erase process is completed, program counter will continue executing next instruction. |

| 6   | EWR  | NVM data write bit:                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |      | 0: Without write NVM data.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |       | 1: Set this bit to write NVM bytes and program counter will halt at this instruction.<br>After write is finished, program counter will kept next instruction then executed. |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | EnNVM | To enable read NVM data memory area.                                                                                                                                        |

|     |       | 0: To disable the MOVX instruction to read NVM data memory.                                                                                                                 |

|     |       | 1: To enable the MOVX instruction to read NVM data memory, the External RAM or AUX-RAM will be disabled.                                                                    |

| 4-0 | -     | Reserved                                                                                                                                                                    |

### NVM DATA

| Bit: | 7            | 6            | 5            | 4            | 3           | 2            | 10           | 0            |

|------|--------------|--------------|--------------|--------------|-------------|--------------|--------------|--------------|

|      | NVMDAT.<br>7 | NVMDAT.<br>6 | NVMDAT.<br>5 | NVMDAT.<br>4 | NVMDAT<br>3 | NVMDAT.<br>2 | NVMDAT.<br>1 | NVMDAT.<br>0 |

|      | 1            | 0            | 5            | 4            | 3           | 2            | Sall         | 0            |

### Mnemonic: NVMDATA

| BIT | NAME         | FUNCTION                                                               |

|-----|--------------|------------------------------------------------------------------------|

| 7~0 | NVMDAT.[7:0] | The NVM data write register. The read NVM data is by MOVC instruction. |

### **PROGRAM STATUS WORD**

|      | 01701 |    |    |     |     |    |    |   |

|------|-------|----|----|-----|-----|----|----|---|

| Bit: | 7     | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|      | CY    | AC | F0 | RS1 | RS0 | OV | F1 | Р |

|      |       |    |    |     |     |    |    |   |

### Mnemonic: PSW

Address: D0h

Address: CFh

|  | BIT | NAME    | FUNCTION                                                                                                                                          |

|--|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|  |     |         | Carry flag:                                                                                                                                       |

|  | 7   | CY      | Set for an arithmetic operation which results in a carry being generated from the ALU. It is also used as the accumulator for the bit operations. |

|  | 6   | AC      | Auxiliary carry:                                                                                                                                  |

|  |     |         | Set when the previous operation resulted in a carry from the high order nibble.                                                                   |

|  | 5   | 5 F0    | User flag 0:                                                                                                                                      |

|  | 5   |         | The General purpose flag that can be set or cleared by the user.                                                                                  |

|  | 4~3 | RS1~RS0 | Register bank select bits.                                                                                                                        |

|  | 0 2 | ov      | Overflow flag:                                                                                                                                    |

|  | 2   |         | Set when a carry was generated from the seventh bit but not from the 8th bit as a result of the previous operation, or vice-versa.                |

|  | 1   | F1      | User Flag 1:                                                                                                                                      |

|  |     | En l    | The General purpose flag that can be set or cleared by the user software.                                                                         |

|  | 0   | Р       | Parity flag:                                                                                                                                      |

|  | 0   | F ~ ~ ~ | Set/cleared by hardware to indicate odd/even number of 1's in the accumulator.                                                                    |

RS.1-0: Register Bank Selection Bits:

Instruction Timing for N79E352(R), continued

| Instruction      | HEX<br>Op-Code | Bytes | N79E352(R)<br>Machine<br>Cycles | N79E352(R)<br>Clock<br>Cycles | 8052<br>Clock<br>Cycles | N79E352(R) v<br>8052 Speed<br>Ratio |

|------------------|----------------|-------|---------------------------------|-------------------------------|-------------------------|-------------------------------------|

| CLR A            | E4             | 1     | 190                             | 4                             | 12                      | 3                                   |

| CPL A            | F4             | 1     | 1 0                             | 4                             | 12                      | 3                                   |

| CLR C            | C3             | 1     | 1                               | 4                             | 12                      | 3                                   |

| CLR bit          | C2             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| CPL C            | B3             | 1     | 1                               | 4                             | 12                      | 3                                   |

| CPL bit          | B2             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| DEC A            | 14             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R0           | 18             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R1           | 19             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R2           | 1A             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R3           | 1B             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R4           | 1C             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R5           | 1D             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R6           | 1E             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R7           | 1F             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC @R0          | 16             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC @R1          | 17             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC direct       | 15             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| DEC DPTR         | A5             | 1     | 2                               | 8                             | -                       | -                                   |

| DIV AB           | 84             | 1     | 5                               | 20                            | 48                      | 2.4                                 |

| DA A             | D4             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DJNZ R0, rel     | D8             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R1, rel     | D9             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R5, rel     | DD             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R2, rel     | DA             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R3, rel     | DB             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R4, rel     | DC             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R6, rel     | DE             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R7, rel     | DF             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ direct, rel | D5             | 3     | 4                               | 16                            | 24                      | 1.5                                 |

| INC A            | 04             | 1     | 1                               | 4                             | 12                      | 3                                   |

| INC R0           | 08             | 1     | 1                               | 4                             | 12                      | 3                                   |

| INC R1           | 09             | 1     | 1                               | 4                             | 12                      | 3                                   |

| INC R2           | OA             | 1     | 1                               | 4                             | 12                      | 3                                   |

| INC R3           | OB             | 1     | 1                               | 4                             | 12                      | 3                                   |

| INC R4           | OC OC          | 1     | 1                               | 4                             | 12                      | 3                                   |

Instruction Timing for N79E352(R), continued

| Instruction       | HEX<br>Op-Code | Bytes | N79E352(R)<br>Machine<br>Cycles | N79E352(R)<br>Clock<br>Cycles | 8052<br>Clock<br>Cycles | N79E352(R) vs<br>8052 Speed<br>Ratio |

|-------------------|----------------|-------|---------------------------------|-------------------------------|-------------------------|--------------------------------------|

| SUBB A, R2        | 9A             | 1     | 192                             | 4                             | 12                      | 3                                    |

| SUBB A, R3        | 9B             | 1     | 1                               | 4                             | 12                      | 3                                    |

| SUBB A, R4        | 9C             | 1     | 1                               | 4                             | 12                      | 3                                    |

| SUBB A, R5        | 9D             | 1     | 1                               | 4                             | 12                      | 3                                    |

| SUBB A, R6        | 9E             | 1     | 1                               | 4                             | 12                      | 3                                    |

| SUBB A, R7        | 9F             | 1     | 1                               | 4                             | 12                      | 3                                    |

| SUBB A, @R0       | 96             | 1     | 1                               | 4                             | 12                      | 3                                    |

| SUBB A, @R1       | 97             | 1     | 1                               | 4                             | 12                      | 3                                    |

| SUBB A, direct    | 95             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| SUBB A, #data     | 94             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| XCH A, R0         | C8             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCH A, R1         | C9             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCH A, R2         | CA             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCH A, R3         | СВ             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCH A, R4         | СС             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCH A, R5         | CD             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCH A, R6         | CE             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCH A, R7         | CF             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCH A, @R0        | C6             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCH A, @R1        | C7             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCHD A, @R0       | D6             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCHD A, @R1       | D7             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XCH A, direct     | C5             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| XRL A, R0         | 68             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XRL A, R1         | 69             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XRL A, R2         | 6A             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XRL A, R3         | 6B             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XRL A, R4         | 6C             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XRL A, R5         | 6D             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XRL A, R6         | 6E             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XRL A, R7         | 6F             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XRL A, @R0        | 66             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XRL A, @R1        | 67             | 1     | 1                               | 4                             | 12                      | 3                                    |

| XRL A, direct     | 65             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| XRL A, #data      | 64             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| XRL direct, A     | 62             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| XRL direct, #data | 63             | 3     | 3                               | 12                            | 24                      | 2                                    |

## 9.1 Instruction Timing

### 9.2 MOVX Instruction

The N79E352(R), like the standard 8052, uses the MOVX instruction to access external Data Memory. This Data Memory includes both off-chip memory as well as memory mapped peripherals. While the results of the MOVX instruction are the same as in the standard 8052, the operation and the timing of the strobe signals have been modified in order to give the user much greater flexibility.

The MOVX instruction is of two types, the MOVX @Ri and MOVX @DPTR. In the MOVX @Ri, the address of the external data comes from two sources. The lower 8-bits of the address are stored in the Ri register of the selected working register bank. The upper 8-bits of the address come from the port 2 SFR. In the MOVX @DPTR type, the full 16-bit address is supplied by the Data Pointer.

Since the N79E352(R) has two Data Pointers, DPTR and DPTR1, the user has to select between the two by setting or clearing the DPS bit. The Data Pointer Select bit (DPS) is the LSB of the DPS SFR. which exists at location 86h. No other bits in this SFR have any effect, and they are set to 0. When DPS is 0, then DPTR is selected, and when set to 1, DPTR1 is selected. The user can switch between DPTR and DPTR1 by toggling the DPS bit. The guickest way to do this is by the INC instruction. The advantage of having two Data Pointers is most obvious while performing block move operations. The accompanying code shows how the use of two separate Data Pointers speeds up the execution time for code performing the same task.

### **Block Move with single Data Pointer:**

; SH and SL are the high and low bytes of Source Address

- ; DH and DL are the high and low bytes of Destination Address

- ; CNT is the number of bytes to be moved

|                                                                              | ,                                                                                  | Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cycles                                                                                      | of |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----|

| N79E3                                                                        | 52(R)                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                           |    |

| MOV<br>MOV<br>MOV<br>MOV<br>MOV                                              | R2, #CNT<br>R3, #SL<br>R4, #SH<br>R5, #DL<br>R6, #DH                               | ; Load R2 with the count value<br>; Save low byte of Source Address in R3<br>; Save high byte of Source address in R4<br>; Save low byte of Destination Address in R5<br>; Save high byte of Destination address in R6                                                                                                                                                                                                                                                                                                                                                                                                                                                           | #<br>2<br>2<br>2<br>2<br>2                                                                  |    |

| LOOP:<br>MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>MOV<br>DJNZ | DPL, R3<br>DPH, R4<br>A, @DPTR<br>DPTR<br>R3, DPL<br>R4, DPH<br>DPL, R5<br>DPH, R6 | <ul> <li>Load DPL with low byte of Source address</li> <li>Load DPH with high byte of Source address</li> <li>Get byte from Source to Accumulator</li> <li>Increment Source Address to next byte</li> <li>Save low byte of Source address in R3</li> <li>Save high byte of Source Address in R4</li> <li>Load low byte of Destination Address in DPL</li> <li>Load high byte of Destination Address in DPH</li> <li>Write data to destination</li> <li>Increment Destination Address</li> <li>Save low byte of new destination address in R52</li> <li>Save high byte of new destination address in R6</li> <li>Decrement count and do LOOP again if count &lt;&gt; 0</li> </ul> | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 |    |

executed now, then the reset Watchdog Timer instructions will not be executed at the required instants and Watchdog reset will occur.

The Watchdog Timer time-out selection will result in different time-out values depending on the clock speed. The reset will occur, when enabled, 512 clocks after the time-out has occurred.

| WD1 | WD0 | WATCHDOG<br>INTERVAL | NUMBER OF<br>CLOCKS | TIME<br>@ 20 KHZ |

|-----|-----|----------------------|---------------------|------------------|

| 0   | 0   | $2^{6}$              | 64                  | 3.2 mS           |

| 0   | 1   | $2^{9}$              | 512                 | 25.6 mS          |

| 1   | 0   | $2^{13}$             | 8192                | 409.6 mS         |

| 1   | 1   | $2^{15}$             | 32768               | 1638.4 mS        |

Table 14-1: Time-out values for the Watchdog timer.

The default Watchdog time-out is 2<sup>6</sup> clocks, which is the shortest time-out period. The EWRST, WDIF and WDCLR bits are protected by the Timed Access procedure. This prevents software from accidentally enabling or disabling the watchdog timer. More importantly, it makes it highly improbable that errant code can enable or disable the Watchdog Timer.

The security bit WDTCK is located at bit 7 of CONFIG0 register. This bit is for user to configure the clock source of watchdog timer either from the internal RC or from the uC clock.

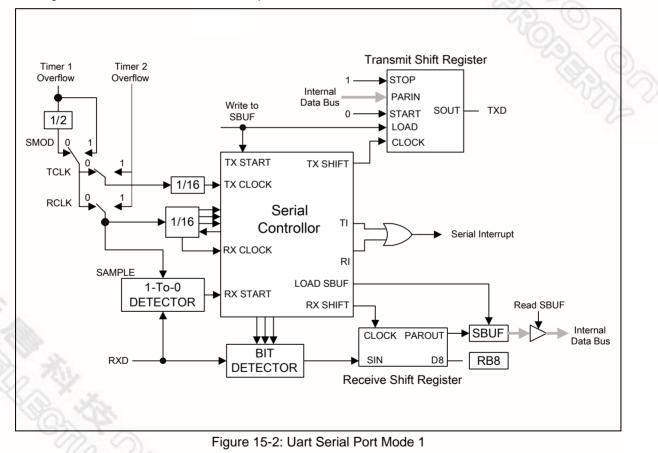

### **15. UART SERIAL PORT**

Serial port in the N79E352(R) is a full duplex port. The N79E352(R) provides the user with additional features such as the Frame Error Detection and the Automatic Address Recognition. The serial ports are capable of synchronous as well as asynchronous communication. In Synchronous mode the N79E352(R) generates the clock and operates in a half duplex mode. In the asynchronous mode, full duplex operation is available. This means that it can simultaneously transmit and receive data. The transmit register and the receive buffer are both addressed as SBUF Special Function Register. However any write to SBUF will be to the transmit register, while a read from SBUF will be from the receive buffer register. The serial port can operate in four different modes as described below.

### 15.1 Mode 0

This mode provides synchronous communication with external devices. In this mode serial data is transmitted and received on the RXD line. TXD is used to transmit the shift clock. The TxD clock is provided by the N79E352(R) whether the device is transmitting or receiving. This mode is therefore a half duplex mode of serial communication. In this mode, 8 bits are transmitted or received per frame. The LSB is transmitted/received first. The baud rate is fixed at 1/12 or 1/4 of the oscillator frequency. This baud rate is determined by the SM2 bit (SCON.5). When this bit is set to 0, then the serial port runs at 1/12 of the clock. When set to 1, the serial port runs at 1/4 of the clock. This additional facility of programmable baud rate in mode 0 is the only difference between the standard 8051 and the N79E352(R).

The functional block diagram is shown below. Data enters and leaves the Serial port on the RxD line. The TxD line is used to output the shift clock. The shift clock is used to shift data into and out of the N79E352(R) and the device at the other end of the line. Any instruction that causes a write to SBUF will start the transmission. The shift clock will be activated and data will be shifted out on the RxD pin till all 8 bits are transmitted. If SM2 = 1, then the data on RxD will appear 1 clock period before the falling edge of shift clock on TxD. The clock on TxD then remains low for 2 clock periods, and then goes high again. If SM2 = 0, the data on RxD will appear 3 clock periods before the falling edge of shift clock on TxD. The clock on TxD then remains low for 6 clock periods, and then goes high again. This ensures that at the receiving end the data on RxD line can either be clocked on the rising edge of the shift clock on TxD or latched when the TxD clock is low.

The 16 states of the counter effectively divide the bit time into 16 slices. The bit detection is done on a best of three basis. The bit detector samples the RxD pin, at the 8th, 9th and 10th counter states. By using a majority 2 of 3 voting system, the bit value is selected. This is done to improve the noise rejection feature of the serial port. If the first bit detected after the falling edge of RxD pin is not 0, then this indicates an invalid start bit, and the reception is immediately aborted. The serial port again looks for a falling edge in the RxD line. If a valid start bit is detected, then the rest of the bits are also detected and shifted into the SBUF.

After shifting in 8 data bits, there is one more shift to do, after which the SBUF and RB8 are loaded and RI is set. However certain conditions must be met before the loading and setting of RI can be done.

- 1. RI must be 0 and

- 2. Either SM2 = 0, or the received stop bit = 1.

If these conditions are met, then the stop bit goes to RB8, the 8 data bits go into SBUF and RI is set. Otherwise the received frame may be lost. After the middle of the stop bit, the receiver goes back to looking for a 1-to-0 transition on the RxD pin.

### 15.3 Mode 2

This mode uses a total of 11 bits in asynchronous full-duplex communication. The functional description is shown in the figure below. The frame consists of one start bit (0), 8 data bits (LSB first), a programmable 9th bit (TB8) and a stop bit (0). The 9th bit received is put into RB8. The baud rate is programmable to 1/32 or 1/64 of the oscillator frequency, which is determined by the SMOD bit in

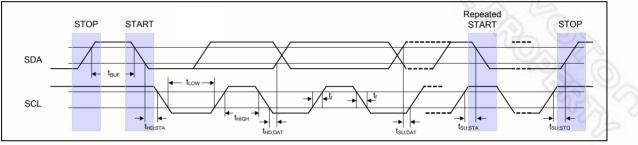

## **16. I2C SERIAL PORT**

The I2C bus uses two wires (SDA and SCL) to transfer information between devices connected to the bus. The main features of the bus are:

- Bidirectional data transfer between masters and slaves

- Multimaster bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

The I2C bus may be used for test and diagnostic purposes

Figure 16-1: I2C Bus Timing

The device's on-chip I2C logic provides the serial interface that meets the I2C bus standard mode specification. The I2C logic handles bytes transfer autonomously. It also keeps track of serial transfers, and a status register (I2STATUS) reflects the status of the I2C bus.

The I2C port, SCL and SDA are at P1.2 and P1.3. When the I/O pins are used as I2C port, user must set the pins to logic high in advance. When I2C port is enabled by setting ENS to high, the internal states will be controlled by I2CON and I2C logic hardware. Once a new status code is generated and stored in I2STATUS, the I2C interrupt flag (SI) will be set automatically. If both EA and EI2C are also in logic high, the I2C interrupt is requested. The 5 most significant bits of I2STATUS stores the internal state code, the lowest 3 bits are always zero and the content keeps stable until SI is cleared by software.

### 16.1 I2C Bus

The I2C bus is a serial I/O port, which supports all transfer modes from and to the I2C bus. The I2C port handles byte transfers autonomously. To enable this port, the bit ENSI in I2CON should be set to '1'. The CPU interfaces to the I2C port through the following six special function registers: I2CON (control register, C0H), I2STATUS (status register, BDH), I2DAT (data register, BCH), I2ADDR (address registers, C1H), I2CLK (clock rate register BEH) and I2TIMER (Timer counter register, BFH). The H/W interfaces to the I2C bus via two pins: SDA (P1.2, serial data line) and SCL (P1.3, serial clock line). Pull up resistor is needed for Pin P1.2 and P1.3 for I2C operation as these are 2 open drain pins (on I2C mode).

### 16.2 The I2C Control Registers:

The I2C has 1 control register (I2CON) to control the transmit/receive flow, 1 data register (I2DAT) to buffer the Tx/Rx data, 1 status register (I2STATUS) to catch the state of Tx/Rx, recognizable slave address register for slave mode use and 1 clock rate control block for master mode to generate the variable baud rate.

### 16.2.1 The Address Registers, I2ADDR

I2C port is equipped with one slave address register. The contents of the register are irrelevant when I2C is in master mode. In the slave mode, the seven most significant bits must be loaded with the MCU's own slave address. The I2C hardware will react if the contents of I2ADDR are matched with the received slave address.

The I2C ports support the "General Call" function. If the GC bit is set the I2C port1 hardware will respond to General Call address (00H). Clear GC bit to disable general call function.

When GC bit is set, the I2C is in Slave mode, it can be received the general call address by 00H after Master send general call address to I2C bus, then it will follow status of GC mode. If it is in Master mode, the AA bit must be cleared when it will send general call address of 00H to I2C bus.

### 16.2.2 The Data Register, I2DAT

This register contains a byte of serial data to be transmitted or a byte which has just been received. The CPU can read from or write to this 8-bit directly addressable SFR while it is not in the process of shifting a byte. This occurs when the bus is in a defined state and the serial interrupt flag (SI) is set. Data in I2DAT remains stable as long as SI bit is set. While data is being shifted out, data on the bus is simultaneously being shifted in; I2DAT always contains the last data byte present on the bus. Thus, in the event of arbitration lost, the transition from master transmitter to slave receiver is made with the correct data in I2DAT.

I2DAT and the acknowledge bit form a 9-bit shift register, the acknowledge bit is controlled by the hardware and cannot be accessed by the CPU. Serial data is shifted through the acknowledge bit into I2DAT on the rising edges of serial clock pulses on the SCL line. When a byte has been shifted into I2DAT, the serial data is available in I2DAT, and the acknowledge bit (ACK or NACK) is returned by the control logic during the ninth clock pulse. Serial data is shifted out from I2DAT on the falling edges of SCL clock pulses, and is shifted into I2DAT on the rising edges of SCL clock pulses.

| Str. | I2DAT.7 I2DAT.6 I2DAT. | 5 I2DAT.4 I2DA <sup>-</sup> | T.3 I2DAT.2 | I2DAT.1 I2DAT.0 |  |

|------|------------------------|-----------------------------|-------------|-----------------|--|

| 2.3  | •                      | shifting direction          | on 🚽        | •               |  |

| Ch S | 15                     |                             |             |                 |  |

|      |                        |                             |             |                 |  |

|      |                        |                             |             |                 |  |

|      |                        |                             |             |                 |  |

|      |                        |                             |             |                 |  |

|      |                        |                             |             |                 |  |

|      |                        |                             |             |                 |  |

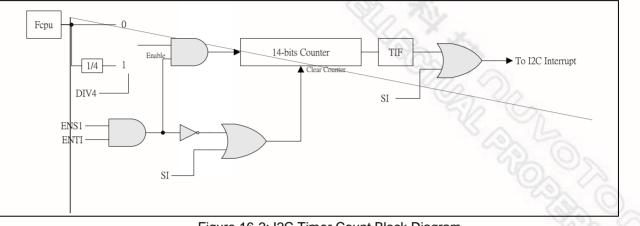

### 16.2.6 I2C Time-out Counter, I2Timerx

The I2C logic block provides a 14-bit timer-out counter that helps user to deal with bus pending problem. When SI is cleared user can set ENTI=1 to start the time-out counter. If I2C bus is pended too long to get any valid signal from devices on bus, the time-out counter overflows cause TIF=1 to request an I2C interrupt. The I2C interrupt is requested in the condition of either SI=1 or TIF=1. Flags SI and TIF must be cleared by software.

Figure 16-2: I2C Timer Count Block Diagram

## 16.3 Modes of Operation

The on-chip I2C ports support five operation modes, Master transmitter, Master receiver, Slave transmitter, Slave receiver, and GC call.

In a given application, I2C port may operate as a master or as a slave. In the slave mode, the I2C port hardware looks for its own slave address and the general call address. If one of these addresses is detected, and if the slave is willing to receive or transmit data from/to master(by setting the AA bit), acknowledge pulse will be transmitted out on the 9th clock, hence an interrupt is requested on both master and slave devices if interrupt is enabled. When the microcontroller wishes to become the bus master, the hardware waits until the bus is free before the master mode is entered so that a possible slave action is not interrupted. If bus arbitration is lost in the master mode, I2C port switches to the slave mode immediately and can detect its own slave address in the same serial transfer.

## 16.3.1 Master Transmitter Mode

Serial data output through SDA while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the data direction bit. In this case the data direction bit (R/W) will be logic 0, and it is represented by "W" in the flow diagrams. Thus the first byte transmitted is SLA+W. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

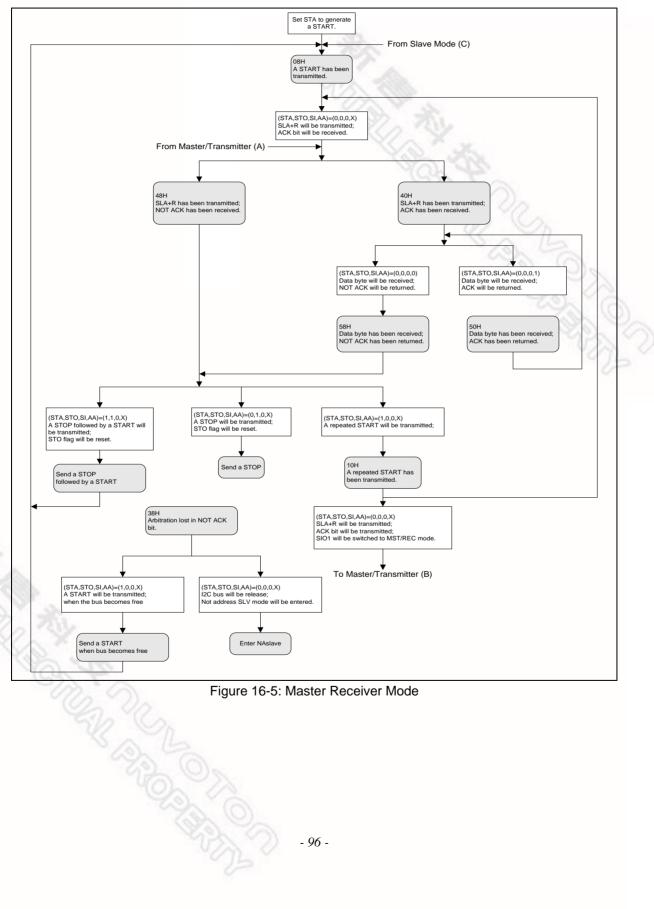

### 16.3.2 Master Receiver Mode

In this case the data direction bit (R/W) will be logic 1, and it is represented by "R" in the flow diagrams. Thus the first byte transmitted is SLA+R. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are output to indicate the beginning and end of a serial transfer.

## Preliminary N79E352/N79E352R Data Sheet

## nuvoTon

- 96 -

## **18. INTERRUPTS**

N79E352(R) has four priority level interrupts structure with 11 interrupt sources. Each of the interrupt sources has an individual priority bit, flag, interrupt vector and enable bit. In addition, the interrupts can be globally enabled or disabled.

### **18.1 Interrupt Sources**

The External Interrupts INT0 and INT1 can be either edge triggered or level triggered, programmable through bits IT0 and IT1 (SFR TCON). The bits IE0 and IE1 in TCON register are the flags which are checked to generate the interrupt. In the edge triggered mode, the INTx inputs are sampled in every machine cycle. If the sample is high in one cycle and low in the next, then a high to low transition is detected and the interrupts request flag IEx in TCON is set. The flag bit requests the interrupt. Since the external interrupts are sampled every machine cycle, they have to be held high or low for at least one complete machine cycle. The IEx flag is automatically cleared when the service routine is called. If the level triggered mode is selected, then the requesting source has to hold the pin low till the interrupt is serviced. The IEx flag will not be cleared by the hardware on entering the service routine. If the interrupt continues to be held low even after the service routine is completed, then the processor may acknowledge another interrupt request from the same source.

The Timer 0 and 1 Interrupts are generated by the TF0 and TF1 flags. These flags are set by the overflow in the Timer 0 and Timer 1. The TF0 and TF1 flags are automatically cleared by the hardware when the timer interrupt is serviced. The Watchdog timer can be used as a system monitor or a simple timer. In either case, when the time-out count is reached, the Watchdog Timer interrupt flag WDIF (WDCON.3) is set. If the interrupt is enabled by the enable bit EIE.4, then an interrupt will occur.

The timer 2 interrupt is generated through TF2 (timer 2 overflow/compare match). The hardware does not clear these flags when a timer 2 interrupt is executed.

The uart serial block can generate interrupt on reception or transmission. There are two interrupt sources from the uart block, which are obtained by the RI and TI bits in the SCON SFR. These bits are not automatically cleared by the hardware, and the user will have to clear these bits using software.

This device also provide an independent I2C serial port. When new I2C state is present in I2STATUS, the SI flag is set by hardware, and if EA and EI2 bits are both set, the I2C interrupt is requested. SI must be cleared by software.

Keyboard interrupt is generated when any of the keypad connected to P0 pins is pressed. Each keypad interrupt can be individually enabled or disabled. User will have to software clear the flag bit.

The input capture 0 interrupt is generated through CPTF0 flag. CPTF0 flag is set by input capture events. The hardware does not clear this flag when the capture interrupt is executed. Software has to clear the flag.

Brownout detect can cause brownout flag, BOF, to be asserted if power voltage drop below brownout voltage level. Interrupt will occur if BOI (AUXR1.5), EBO (EIE.6) and global interrupt enable are set.

| Source               | Vector Address | Source             | Vector Address |

|----------------------|----------------|--------------------|----------------|

| External Interrupt 0 | 0003H          | Timer 0 Overflow   | 000BH          |

| External Interrupt 1 | 0013H          | Timer 1 Overflow   | 001BH          |

| Serial Port          | 0023H          | Brownout Interrupt | 002BH          |

| I2C Interrupt        | 0033H          | KBI Interrupt      | 003BH          |

| Timer 2 Overflow     | 0043H          | -                  | 004BH          |

| Watchdog Timer       | 0053H          | -                  | 005BH          |

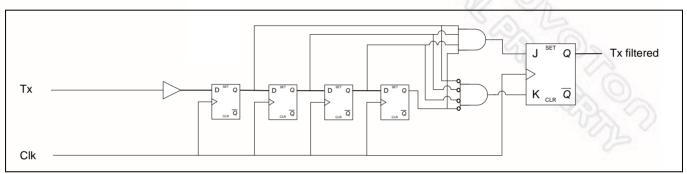

## **20. INPUT CAPTURE**