Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Not For New Designs                                                                    |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 24MHz                                                                                  |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, UART/USART                                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                             |

| Number of I/O              | 36                                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | 128 x 8                                                                                |

| RAM Size                   | 256 x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                            |

| Data Converters            | -                                                                                      |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

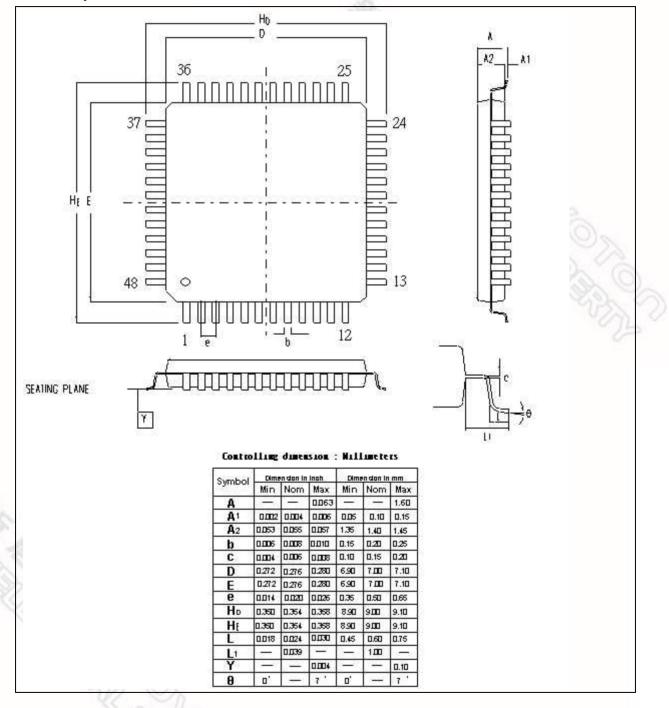

| Package / Case             | 44-LCC (J-Lead)                                                                        |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/n79e352apg |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

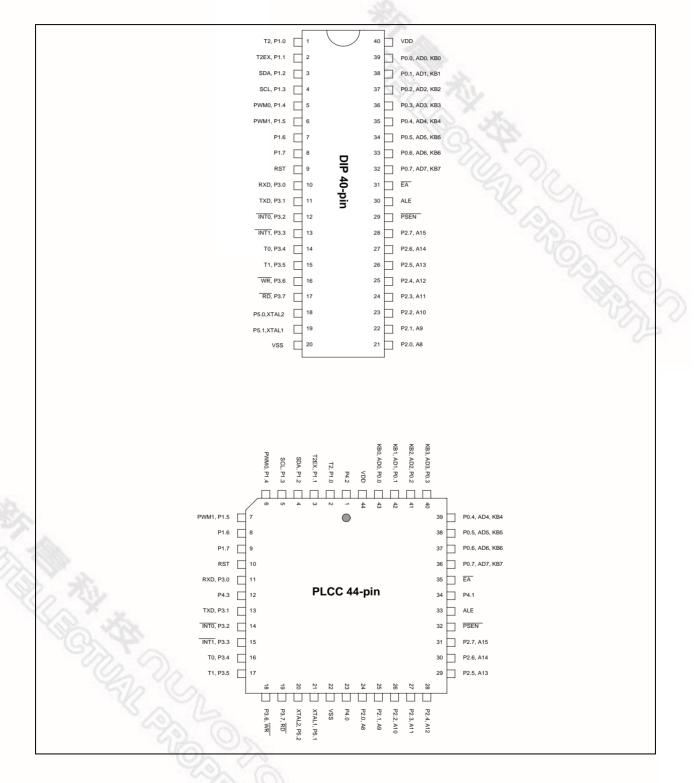

#### 4. PIN CONFIGURATIONS

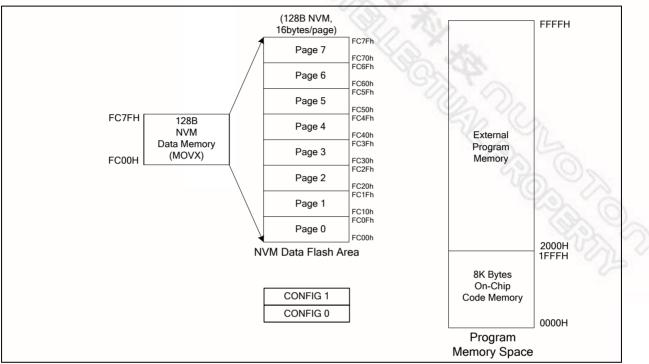

#### 7. MEMORY ORGANIZATION

N79E352(R) separates the memory into two separate sections, the Program Memory and the Data Memory. The Program Memory is used to store the instruction op-codes, while the Data Memory is used to store data or for memory mapped devices.

Figure 7-1: N79E352(R) Memory Map

#### 7.1 Program Memory (on-chip Flash)

The Program Memory on N79E352(R) can be up to 8K bytes long. All instructions are fetched for execution from this memory area. The MOVC instruction can also access this memory region.

## nuvoTon

|                                           | NAME                                                             | FUNCTIC                                                      | DN                                                                                |                                                 | 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -                                                      |                                                 |                                                                        |                         |

|-------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------|-------------------------|

| 7-0                                       | TL0.[7:0]                                                        | Timer 0 L                                                    | SB.                                                                               |                                                 | - AR                                                                                         |                                                 |                                                                        |                         |

| TIME                                      | R 1 LSB                                                          |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        |                         |

| Bit:                                      | 7                                                                | 6                                                            | 5                                                                                 | 4                                               | 3                                                                                            | 2                                               | 1                                                                      | 0                       |

|                                           | TL1.7                                                            | TL1.6                                                        | TL1.5                                                                             | TL1.4                                           | TL1.3                                                                                        | TL1.2                                           | TL1.1                                                                  | TL1.0                   |

| Mnem                                      | onic: TL1                                                        |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | Address: 8B             |

| BIT                                       | NAME                                                             | FUNCTIC                                                      | N                                                                                 |                                                 |                                                                                              | Top.                                            | 20                                                                     |                         |

| 7-0                                       | TL1.[7:0]                                                        | Timer 1 L                                                    | _SB.                                                                              |                                                 |                                                                                              | 277                                             | A                                                                      |                         |

| TIMEF                                     | R 0 MSB                                                          |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        |                         |

| Bit:                                      | 7                                                                | 6                                                            | 5                                                                                 | 4                                               | 3                                                                                            | 2                                               | 3/1                                                                    | 0                       |

|                                           | TH0.7                                                            | TH0.6                                                        | TH0.5                                                                             | TH0.4                                           | 4 TH0.3                                                                                      | TH0.2                                           | TH0.1                                                                  | TH0.0                   |

| Mnem                                      | onic: TH0                                                        |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | Address: 8              |

| BIT                                       | NAME                                                             | FUNCTIO                                                      | ON                                                                                |                                                 |                                                                                              |                                                 |                                                                        | 2020                    |

| 7-0                                       | TH0.[7:0]                                                        | Timer 0                                                      | MSB.                                                                              |                                                 |                                                                                              |                                                 |                                                                        | CO.                     |

| TIMEF                                     | R 1 MSB                                                          |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | 0                       |

| Bit:                                      | 7                                                                | 6                                                            | 5                                                                                 | 4                                               | 3                                                                                            | 2                                               | 1                                                                      | 0                       |

|                                           | TH1.7                                                            | TH1.6                                                        | TH1.5                                                                             | TH1.4                                           | 4 TH1.3                                                                                      | TH1.2                                           | TH1.1                                                                  | TH1.0                   |

|                                           |                                                                  |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        |                         |

| Mnem                                      | onic: TH1                                                        |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | Address: 8D             |

| Mnem<br>BIT                               | onic: TH1                                                        | FUNCTIO                                                      | DN                                                                                |                                                 |                                                                                              |                                                 |                                                                        | Address: 8D             |

|                                           |                                                                  | FUNCTIC                                                      |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | Address: 8D             |

| <b>BIT</b><br>7-0                         | <b>NAME</b><br>TH1.[7:0]                                         | Timer 1 I                                                    |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | Address: 8D             |

| <b>BIT</b><br>7-0                         | NAME                                                             | Timer 1 I                                                    |                                                                                   | 4                                               | 3                                                                                            | 2                                               | 1                                                                      | Address: 8D             |

| <b>BIT</b><br>7-0<br><b>CLOC</b>          | NAME<br>TH1.[7:0]                                                | Timer 1 I                                                    | MSB.                                                                              | 4<br>T1M                                        | 3<br>  TOM                                                                                   | 2<br>MD2                                        | 1<br>MD1                                                               |                         |

| BIT<br>7-0<br>CLOC<br>Bit:                | NAME<br>TH1.[7:0]<br>K CONTRO<br>7                               | Timer 1 I<br>6<br>WD0                                        | MSB.<br>5                                                                         |                                                 |                                                                                              |                                                 |                                                                        | 0                       |

| BIT<br>7-0<br>CLOC<br>Bit:                | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1                        | Timer 1 I<br>6<br>WD0                                        | MSB.<br>5<br>T2M                                                                  |                                                 |                                                                                              |                                                 |                                                                        | 0<br>MD0                |

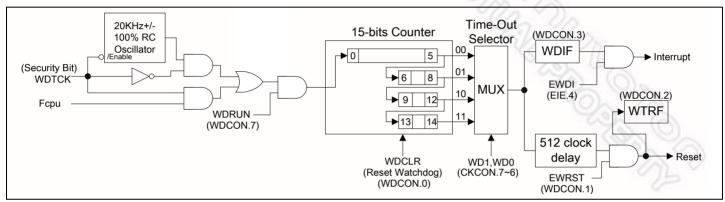

| BIT<br>7-0<br>CLOC<br>Bit:<br>Mnem        | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1<br>onic: CKCOI         | Timer 1 I<br>6<br>WD0<br>N<br>FUNCTIO<br>Watchdo<br>the wato | MSB.<br>5<br>T2M<br>DN<br>Dg timer mo                                             | T1M                                             |                                                                                              | MD2<br>bits determ                              | MD1                                                                    | 0<br>MD0<br>Address: 8E |

| BIT<br>7-0<br>CLOC<br>Bit:<br>Mnem        | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1<br>onic: CKCOI         | Timer 1 I<br>6<br>WD0<br>N<br>FUNCTIO<br>Watchdo<br>the wato | MSB.<br>5<br>T2M<br>DN<br>Dg timer mo                                             | T1M                                             | T0M<br>ct bits: These<br>our time-out op                                                     | MD2<br>bits determ<br>bitons the r              | MD1                                                                    | 0<br>MD0<br>Address: 8E |

| BIT<br>7-0<br>CLOC<br>Bit:<br>Mnem        | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1<br>onic: CKCOI         | Timer 1 I<br>6<br>WD0<br>N<br>FUNCTIO<br>Watchdo<br>the wato | MSB.<br>5<br>T2M<br>DN<br>Dg timer mo<br>chdog timer<br>an the interr             | T1M<br>ode sele<br>: In all fo                  | T0M<br>ct bits: These<br>our time-out op<br>-out period.                                     | MD2<br>bits determ<br>otions the re<br>e-out Re | MD1<br>nine the time<br>eset time-out                                  | 0<br>MD0<br>Address: 8E |

| BIT<br>7-0<br>CLOC<br>Bit:<br>Mnem<br>BIT | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1<br>onic: CKCOI<br>NAME | Timer 1 I<br>6<br>WD0<br>N<br>FUNCTIO<br>Watchdo<br>the wato | MSB.<br>5<br>T2M<br>DN<br>Dg timer mo<br>chdog timer<br>an the interr<br>WD1      | Dde sele<br>c. In all fo<br>upt time<br>WD0     | T0M<br>ct bits: These<br>our time-out op<br>-out period.<br>Interrupt time                   | MD2<br>bits determ<br>ptions the m<br>e-out Re  | MD1<br>nine the time<br>eset time-out<br>set time-out                  | 0<br>MD0<br>Address: 8E |

| BIT<br>7-0<br>CLOC<br>Bit:<br>Mnem<br>BIT | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1<br>onic: CKCOI<br>NAME | Timer 1 I<br>6<br>WD0<br>N<br>FUNCTIO<br>Watchdo<br>the wato | MSB.<br>5<br>T2M<br>DN<br>Dg timer mo<br>chdog timer<br>an the interr<br>WD1<br>0 | Dde sele<br>. In all fo<br>upt time<br>WD0<br>0 | T0M<br>ct bits: These<br>our time-out op<br>-out period.<br>Interrupt time<br>2 <sup>6</sup> | MD2<br>bits determ<br>ptions the m<br>e-out Re  | MD1<br>hine the time<br>eset time-out<br>set time-out<br>$2^{6} + 512$ | 0<br>MD0<br>Address: 8E |

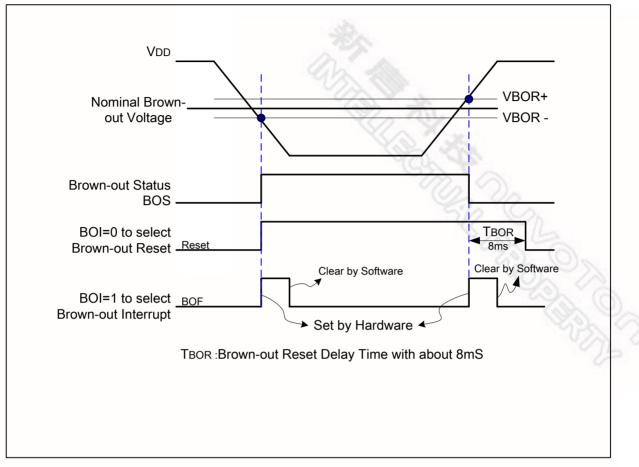

|     |         | Brownout                 | voltage sele           | ection bits, see below table.                                                                                 |

|-----|---------|--------------------------|------------------------|---------------------------------------------------------------------------------------------------------------|

|     |         | BOV.1                    | BOV.0                  | Brownout Voltage                                                                                              |

|     |         | 0                        | х                      | Brownout voltage is 2.6V                                                                                      |

| 2~1 | BOV.1~0 | 1                        | 0                      | Brownout voltage is 3.8V                                                                                      |

|     |         | 1                        | 1                      | Brownout voltage is 4.5V                                                                                      |

|     |         |                          |                        | red at all resets with the inverse values of bits CBOV.1-0 in is able to re-configure these bits after reset. |

|     |         | Brownout \$              | Status bit(R           | lead only)                                                                                                    |

| 0   | BOS     | 0: V <sub>DD</sub> is al | oove V <sub>BOR+</sub> | and the second                                                                                                |

|     |         | 1: V <sub>DD</sub> is be | elow V <sub>BOR-</sub> | 50 00                                                                                                         |

#### **CAPTURE CONTROL 0 REGISTER**

| Bit: | 7 | 6 | 5 | 4 | 3      | 2      | 100 | 0    |

|------|---|---|---|---|--------|--------|-----|------|

|      | - | - | - | - | CCT0.1 | CCT0.0 | -16 | D- 1 |

#### Mnemonic: CAPCON0

Address: A3h

| BIT | NAME      | FUNCTION                                    |

|-----|-----------|---------------------------------------------|

| 7-4 | -         | Reserved.                                   |

| 3-2 | CCT0[1:0] | Capture 0 edge select:                      |

|     |           | 00 : Rising edge trigger.                   |

|     |           | 01 : Falling edge trigger.                  |

|     |           | 10 : Either rising or falling edge trigger. |

|     |           | 11 : Reserved                               |

| 1-0 | -         | Reserved.                                   |

#### **CAPTURE CONTROL 1 REGISTER**

| Bit: | 7 | 6    | 5 | 4 | 3    | 2 | 1 | 0     |

|------|---|------|---|---|------|---|---|-------|

| S.   | 0 | TOCC | - | - | ENF0 | - | - | CPTF0 |

Mnemonic: CAPCON1

Address: A4h

| BIT | NAME | FUNCTION                                                          |

|-----|------|-------------------------------------------------------------------|

| 7   | 912  | Must be 0.                                                        |

| 6   | TOCC | Timer 0 Clear Counter bit.                                        |

|     | S.   | 0: Timer 0 is not clear when input capture/cap sensor trigger.    |

|     | ~    | 1: Timer 0 will be cleared when input capture/cap sensor trigger. |

| 5-4 | - 2  | Reserved.                                                         |

| 3   | ENF0 | Enable filter for capture input 0.                                |

## nuvoTon

5

|        | I2CLK.7     | I2CLK.6                                                                                                                                                              | I2CLK.5                                   | I2CLK.4                                                                      | I2CLK.3                                     | I2CLK.2                      | I2CLK.1                 | I2CLK.0       |

|--------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------|------------------------------|-------------------------|---------------|

| Mnem   | onic: I2CLK | ,<br>                                                                                                                                                                |                                           |                                                                              | Re                                          |                              | A                       | Address: BE   |

| BIT    | NAME        | FUNCT                                                                                                                                                                | ION                                       |                                                                              | 21-1                                        |                              |                         |               |

| 7-0    | 12CLK.[7    | ':0] The I2                                                                                                                                                          | C clock rate                              | e bits.                                                                      | 123                                         | <u></u>                      |                         |               |

| I2C TI |             | NTER REGIS                                                                                                                                                           | STER                                      |                                                                              |                                             |                              |                         |               |

| Bit:   | 7           | 6                                                                                                                                                                    | 5                                         | 4                                                                            | 3                                           | 2                            | 1                       | 0             |

|        | -           | -                                                                                                                                                                    | -                                         | -                                                                            | - 3                                         | ENTI                         | DIV4                    | TIF           |

| Mnem   | onic: I2TIM | ER                                                                                                                                                                   |                                           |                                                                              |                                             | 1992                         | F                       | Address: BF   |

| BIT    | NAME        | FUNCTIC                                                                                                                                                              | N                                         |                                                                              |                                             | ~ (I)                        | 2 VD                    |               |

| 7~3    | -           | Reserved                                                                                                                                                             | J.                                        |                                                                              |                                             | 3                            | he                      | 26            |

| I      |             | Enable I2                                                                                                                                                            | C 14-bits T                               | imer Counte                                                                  | r:                                          |                              |                         |               |

| _      |             | 0: Disable                                                                                                                                                           | e 14-bits Ti                              | mer Counter                                                                  | count.                                      |                              |                         |               |

| 2      | ENTI        | 1: Enable 14-bits Timer Counter count. After enable ENTI a counter will be counted. When SI flag of I2C is set, the count and 14-bits Timer Counter will be cleared. |                                           |                                                                              |                                             |                              |                         |               |

|        |             | I2C Time                                                                                                                                                             | r Counter c                               | lock source                                                                  | divide functi                               | on:                          |                         | 15            |

| 1      | DIV4        | 0: The 14                                                                                                                                                            | l-bits Timer                              | Counter sou                                                                  | irce clock is                               | F <sub>CPU</sub> clock.      |                         |               |

|        |             | 1: The 14                                                                                                                                                            | -bits Timer                               | Counter sou                                                                  | rce clock is                                | divided by 4                 | ŀ.                      |               |

|        |             | The I2C                                                                                                                                                              | Timer Cour                                | ter count flag                                                               | g:                                          |                              |                         |               |

|        |             | 0: The 14                                                                                                                                                            | -bits Timer                               | Counter is r                                                                 | ot overflow.                                |                              |                         |               |

| 0      | TIF         | ENSI                                                                                                                                                                 | = [1,1]) the                              | r Counter is<br>e SI must b<br>outine will be                                | e cleared. I                                | f I2C interru                | upt is enable           | ed. The I20   |

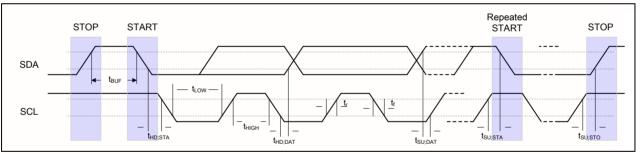

| I2C C  | ONTROL R    | EGISTER                                                                                                                                                              |                                           |                                                                              |                                             |                              |                         |               |

| Bit:   | 7           | 6                                                                                                                                                                    | 5                                         | 4                                                                            | 3                                           | 2                            | 1                       | 0             |

|        | -           | ENSI                                                                                                                                                                 | STA                                       | STO                                                                          | SI                                          | AA                           | -                       | -             |

| Mnem   | onic: I2CON | 1                                                                                                                                                                    | •                                         |                                                                              |                                             |                              | ŀ                       | Address: C0   |

| BIT    | NAME        | FUNCTI                                                                                                                                                               | ON                                        |                                                                              |                                             |                              |                         |               |

| 7      | 1           | Reserve                                                                                                                                                              | d.                                        |                                                                              |                                             |                              |                         |               |

| 6      | ENSI        | impec<br>addre<br>forcec                                                                                                                                             | lance state<br>ssed slave<br>I to "0". No | erial Functio<br>. SDA and S<br>mode or it<br>other bits a<br>ain I/O ports. | SCL input si<br>is not addi<br>re affected. | gnals are ig<br>ressable, an | nored, I2C<br>d STO bit | is not in the |

1: Enable I2C Serial Function. The P1.2 and P1.3 port latches must be to logic 1.

STA

STA

O: The STA bit is reset, no START condition or repeated START condition will

# nuvoTon

|               | -          | NVMADD<br>R.6                                                       | NVMADD<br>R.5                                                 | NVMADD<br>R.4                                     | NVMADD<br>R.3                              | NVMADD<br>R.2                                  | NVMADD<br>R.1                                                                | NVMADD<br>R.0              |

|---------------|------------|---------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------|--------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------|----------------------------|

| Mnem          | onic: NVMA | DDR                                                                 |                                                               |                                                   | No.                                        |                                                | Ad                                                                           | ddress: C6h                |

| BIT           | NAME       | FU                                                                  | NCTION                                                        | 9                                                 | 12 3                                       |                                                |                                                                              |                            |

| 7             | -          | Re                                                                  | served                                                        |                                                   | CO.                                        | Sec. 1                                         |                                                                              |                            |

| 6~0           | NVMADDF    | R.[6:0] Th                                                          | e NVM addre                                                   | ess:                                              | N/                                         | NY.                                            |                                                                              |                            |

|               |            |                                                                     | e register ir<br>mory space.                                  |                                                   | M data me                                  | emory addre                                    | ess on On-                                                                   | Chip code                  |

| ТІМЕГ         | D ACCESS   |                                                                     |                                                               |                                                   |                                            | -m                                             | 5                                                                            |                            |

| Bit:          | 7          | 6                                                                   | 5                                                             | 4                                                 | 3                                          | 2                                              | 25                                                                           | 0                          |

|               | TA.7       | TA.6                                                                | TA.5                                                          | TA.4                                              | TA.3                                       | TA.2                                           | TA.1                                                                         | TA.0                       |

| Mnem          | ionic: TA  |                                                                     |                                                               |                                                   |                                            |                                                | Ad                                                                           | ddress: C7h                |

| BIT           | NAME       | FUNCTIO                                                             | N                                                             |                                                   |                                            |                                                | 0                                                                            | 20                         |

|               |            |                                                                     | d Access re                                                   | gister:                                           |                                            |                                                | 0                                                                            | 20 (0                      |

| 7-0           | TA.[7:0]   | protected<br>followed                                               | ed Access re<br>bits, the use<br>by a write of<br>machine cyc | er must first<br>55H to TA.                       | write AAH to<br>Now a wino                 | o the TA. Th<br>dow is opene                   | is must be in<br>ed in the pro                                               | mmediately<br>otected bits |

|               | TA.[7:0]   | The Time<br>protected<br>followed<br>for three                      | ed Access r<br>bits, the use<br>by a write of                 | er must first<br>55H to TA.                       | write AAH to<br>Now a wino                 | o the TA. Th<br>dow is opene                   | is must be in<br>ed in the pro                                               | mmediately<br>otected bits |

|               |            | The Time<br>protected<br>followed<br>for three                      | ed Access r<br>bits, the use<br>by a write of                 | er must first<br>55H to TA.                       | write AAH to<br>Now a wino                 | o the TA. Th<br>dow is opene                   | is must be in<br>ed in the pro                                               | mmediately<br>otected bits |

| TIMEF         | R 2 CONTRO | The Time<br>protected<br>followed<br>for three                      | ed Access r<br>bits, the use<br>by a write of<br>machine cyc  | er must first<br>55H to TA.<br>les, during w      | write AAH to<br>Now a wind<br>hich the use | o the TA. Th<br>dow is open<br>er can write t  | is must be in<br>ed in the pro<br>o these bits.                              | mmediately<br>otected bits |

| TIMEF<br>Bit: | 7<br>7     | The Timprotected<br>followed<br>for three<br><b>DL</b><br>6<br>EXF2 | ed Access r<br>bits, the use<br>by a write of<br>machine cyc  | er must first<br>55H to TA.<br>les, during w<br>4 | write AAH to<br>Now a wino<br>hich the use | o the TA. Th<br>dow is opene<br>er can write t | is must be in<br>ed in the pro-<br>o these bits.<br>1<br>$C / \overline{T2}$ | nmediately<br>ptected bits |

|   |       | I ONCTION                                                                                                                                                                                                                                                                                                                                                                    |

|---|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |       | Timer 2 overflow flag:                                                                                                                                                                                                                                                                                                                                                       |

| 7 | TF2   | Timer 2 overflow flag: This bit is set when Timer 2 overflows. It is also set when<br>the count is equal to the capture register in down count mode. It can be set only<br>if RCLK and TCLK are both 0. It is cleared only by software. Software can also<br>set or clear this bit.                                                                                          |

| 6 | EXF2  | Timer 2 External Flag: A negative transition on the T2EX pin (P1.1) or timer 2 overflow will cause this flag to set based on the CP/ $\overline{RL2}$ , EXEN2 and DCEN bits. If set by a negative transition, this flag must be cleared by software. Setting this bit in software or detection of a negative transition on T2EX pin will force a timer interrupt if enabled. |

|   | and 4 | Receive Clock Flag: This bit determines the serial port time-base when receiving                                                                                                                                                                                                                                                                                             |

| 5 | RCLK  | data in serial modes 1 or 3. If it is 0, then timer 1 overflow is used for baud rate generation, otherwise timer 2 overflow is used. Setting this bit forces timer 2 in baud rate generator mode.                                                                                                                                                                            |

|   |       | - 40 -                                                                                                                                                                                                                                                                                                                                                                       |

|   | No.   | 7 TF2<br>6 EXF2                                                                                                                                                                                                                                                                                                                                                              |

## nuvoTon

|                             | PWM0.7                                    | PWM0.6                 | PWM0.5                                | PWM0.4         | PWM0.3                     | PWM0.2                     | PWM0.1      | PWM0.0      |

|-----------------------------|-------------------------------------------|------------------------|---------------------------------------|----------------|----------------------------|----------------------------|-------------|-------------|

| Vnem                        | onic: PWM0L                               | _                      |                                       |                |                            |                            | ŀ           | Address: DA |

| BIT                         | NAME                                      | FUNCTIO                | N                                     | 1              | n A                        | S                          |             |             |

| 7~0                         | PWM0                                      | PWM 0 L                | ow Bits Reg                           | gister.        | NA C                       |                            |             |             |

| PWM                         | 0 LOW BITS                                | REGISTE                | ર                                     |                |                            |                            |             |             |

| Bit:                        | 7                                         | 6                      | 5                                     | 4              | 3                          | 2                          | 1           | 0           |

|                             | PWM1.7                                    | PWM1.6                 | PWM1.5                                | PWM1.4         | PWM1.3                     | PWM1.2                     | PWM1.1      | PWM1.0      |

| Mnem                        | onic: PWM1L                               | -                      |                                       |                |                            |                            | 501         | Address: DE |

| BIT                         | NAME                                      | FUNCTIO                | N                                     |                |                            | Q                          | 5.40        | A           |

| 7~0                         | PWM1                                      | PWM 1 L                | ow Bits Re                            | gister.        |                            |                            | K~~         | n_          |

| PWM                         |                                           | REGISTER               | 1                                     |                |                            |                            | 22          | 6           |

| Bit:                        | 7                                         | 6                      | 5                                     | 4              | 3                          | 2                          | 1 7         | 0           |

|                             | PWMRUN                                    | -                      | -                                     | CLRPWM         | -                          | -                          | -           | 20 V        |

| Mnem                        | onic: PWMC                                | ON1                    |                                       |                |                            |                            | ļ           | Address: DC |

| BIT                         | NAME                                      | FUNCTIO                | N                                     |                |                            |                            |             | 00          |

| 7                           | PWMRUN                                    | 0: The PV              | VM is not ru                          | inning.        |                            |                            |             |             |

| 1                           | PWWRUN                                    | 1: The PV              | VM counter                            | is running.    |                            |                            |             |             |

| 6~5                         | -                                         | Reserved               |                                       |                |                            |                            |             |             |

| 4                           | CLRPWM                                    | 1: Clear 8             | -bit PWM c                            | ounter to 000  | DH.                        |                            |             |             |

| т                           |                                           | It is auton            | natically clea                        | ared by hard   | ware.                      |                            |             |             |

| 3~0                         | -                                         | Reserved               | l.                                    |                |                            |                            |             |             |

|                             | MULATOR                                   |                        |                                       |                |                            |                            |             |             |

| Bit:                        | 7                                         | 6                      | 5                                     | 4              | 3                          | 2                          | 1           | 0           |

|                             | ACC.7                                     | ACC.6                  | ACC.5                                 | ACC.4          | ACC.3                      | ACC.2                      | ACC.1       | ACC.0       |

|                             |                                           |                        |                                       |                |                            |                            | ŀ           | Address: E0 |

| Vnem                        | onic: ACC                                 | 1                      |                                       |                |                            |                            |             |             |

| Mnem<br>BIT                 | NAME                                      | FUNCTIO                | N                                     |                |                            |                            |             |             |

| 1000                        | [                                         |                        |                                       | r is the stand | dard 8052 a                | accumulator                |             |             |

| <b>BIT</b><br>7-0           | NAME<br>ACC                               | The A or A             | ACC registe                           | r is the stand | dard 8052 a                | accumulator                |             |             |

| <b>BIT</b><br>7-0           | NAME<br>ACC<br>I CAPTURE                  | The A or <i>J</i>      | ACC registe                           |                |                            |                            |             | 0           |

| BIT<br>7-0<br>INPUT<br>Bit: | NAME<br>ACC<br>F CAPTURE<br>7             | The A or <i>i</i><br>6 | ACC registe<br>EGISTER<br>5           | 4              | dard 8052 a<br>3<br>CCL0.3 | accumulator<br>2<br>CCL0.2 | 1<br>CCL0.1 | 0<br>CCL0.0 |

| BIT<br>7-0<br>INPUT<br>Bit: | NAME<br>ACC<br>F CAPTURE<br>7             | The A or <i>i</i><br>6 | ACC registe<br>EGISTER<br>5           | 4              | 3                          | 2                          | 1<br>CCL0.1 | CCL0.0      |

| BIT<br>7-0<br>INPUT<br>Bit: | NAME<br>ACC<br>T CAPTURE<br>7<br>CCL0.7 C | The A or <i>i</i><br>6 | ACC registe<br>EGISTER<br>5<br>CCL0.5 | 4              | 3                          | 2                          | 1<br>CCL0.1 | 1           |

| Bit:  | 7           | 6        | 5              | 4             | 3       | 2       | 1      | 0          |

|-------|-------------|----------|----------------|---------------|---------|---------|--------|------------|

|       | CCH0.7      | CCH0.6   | CCH0.5         | CCH0.4        | CCH0.3  | CCH0.2  | CCH0.1 | CCH0.0     |

| Mnem  | nonic: CCH0 | )        |                |               | april 1 |         |        | Address: E |

| BIT   | NAME        | FUNCT    | ION            |               | - ~ (Q) | N.      |        |            |

| 7-0   | CCH0        | Capture  | e 0 high byte  | э.            | 6       | CAX.    | 26     |            |

| IINTE |             |          | GISTER 1       |               |         | Val.    | 225    |            |

| Bit:  | 7           | 6        | 5              | 4             | 3       | 2       | 10     | 0          |

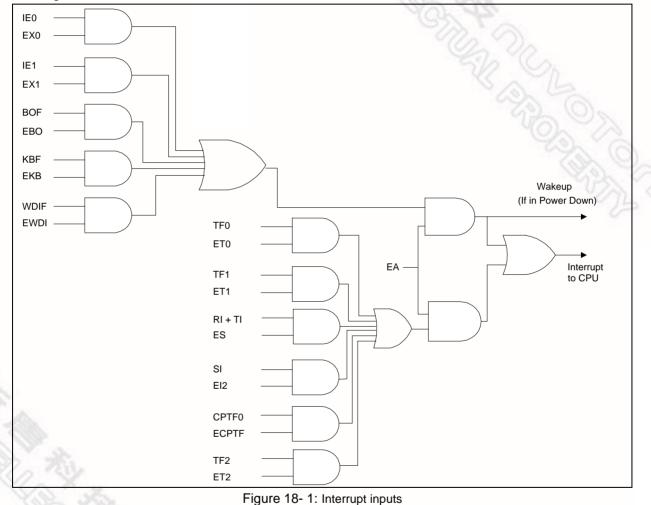

|       | ECPTF       | EBO      | -              | EWDI          | -       | - 0     | EKB    | El2        |

| Mnem  | nonic: EIE  |          |                |               |         | <u></u> | R X    | Address: E |

| BIT   | NAME        | FUNCT    | ION            |               |         |         | - 493  | 0.0        |

| 7     | ECPTF       | 0: Disa  | ble capture    | interrupt.    |         |         | -4     | 0          |

| 1     | ECPIF       | 1: Enal  | ble capture    | interrupt.    |         |         |        |            |

|       |             | Enable   | brownout in    | nterrupt.     |         |         |        | SS)        |

| 6     | EBO         | 0: Disa  | ble brownou    | ut interrupt. |         |         |        |            |

|       |             | 1: Enal  | ble brownou    | it interrupt. |         |         |        | 1.2        |

| 5     | -           | Reserv   | /ed.           |               |         |         |        |            |

| 4     | EWDI        | 0: Disa  | ble Watchd     | log Timer Int | errupt. |         |        |            |

| 4     |             | 1: Enal  | ble Watchdo    | og Timer Inte | errupt. |         |        |            |

| 3~2   | -           | Reserv   | ed.            |               |         |         |        |            |

| 1     | EKB         | 0: Disa  | ble Keypad     | Interrupt.    |         |         |        |            |

|       | END         | 1: Enal  | ble Keypad     | Interrupt.    |         |         |        |            |

| 0     | EI2         | 0: Disal | ble I2C Inter  | rrupt.        |         |         |        |            |

| 0     |             | 1: Enat  | ole I2C Inter  | rupt.         |         |         |        |            |

| KEYE  | BOARD LE    | VEL      |                |               |         |         |        |            |

| Bit:  |             | 6        | 5              | 4             | 3       | 2       | 1      | 0          |

|       | KBL.7       | KBL.6    | KBL.5          | 6 KBL.4       | KBL.3   | KBL.2   | KBL.1  | KBL.0      |

| Mnem  | nonic: KBL  |          |                |               |         |         |        | Address: E |

| BIT   | NAME        | FUNCT    | ION            |               |         |         |        |            |

| 1     | 22.0        | Keyboa   | rd trigger lev | vel.          |         |         |        |            |

| 7~0   | KBL.7~0     | 0: Low   | level trigger. | .x pin.       |         |         |        |            |

| 1~0   | NDL.7~0     | 1: High  | level trigger  | r on KBI.x pi | n.      |         |        |            |

|       |             | [x = 0-7 | Pa.            |               |         |         |        |            |

| PORT  | ГS SHMITT   | REGISTE  | RUN            |               |         |         |        |            |

| Bit:  | 7           | 6        | 5              | 4             | 3       | 2       | 1      | 0          |

Instruction Timing for N79E352(R), continued

| Instruction      | HEX<br>Op-Code | Bytes | N79E352(R)<br>Machine<br>Cycles | N79E352(R)<br>Clock<br>Cycles | 8052<br>Clock<br>Cycles | N79E352(R) v<br>8052 Speed<br>Ratio |

|------------------|----------------|-------|---------------------------------|-------------------------------|-------------------------|-------------------------------------|

| CLR A            | E4             | 1     | 190                             | 4                             | 12                      | 3                                   |

| CPL A            | F4             | 1     | 1 0                             | 4                             | 12                      | 3                                   |

| CLR C            | C3             | 1     | 1                               | 4                             | 12                      | 3                                   |

| CLR bit          | C2             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| CPL C            | B3             | 1     | 1                               | 4                             | 12                      | 3                                   |

| CPL bit          | B2             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| DEC A            | 14             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R0           | 18             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R1           | 19             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R2           | 1A             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R3           | 1B             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R4           | 1C             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R5           | 1D             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R6           | 1E             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC R7           | 1F             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC @R0          | 16             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC @R1          | 17             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DEC direct       | 15             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| DEC DPTR         | A5             | 1     | 2                               | 8                             | -                       | -                                   |

| DIV AB           | 84             | 1     | 5                               | 20                            | 48                      | 2.4                                 |

| DA A             | D4             | 1     | 1                               | 4                             | 12                      | 3                                   |

| DJNZ R0, rel     | D8             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R1, rel     | D9             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R5, rel     | DD             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R2, rel     | DA             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R3, rel     | DB             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R4, rel     | DC             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R6, rel     | DE             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ R7, rel     | DF             | 2     | 3                               | 12                            | 24                      | 2                                   |

| DJNZ direct, rel | D5             | 3     | 4                               | 16                            | 24                      | 1.5                                 |

| INC A            | 04             | 1     | 1                               | 4                             | 12                      | 3                                   |

| INC R0           | 08             | 1     | 1                               | 4                             | 12                      | 3                                   |

| INC R1           | 09             | 1     | 1                               | 4                             | 12                      | 3                                   |

| INC R2           | 0A             | 1     | 1                               | 4                             | 12                      | 3                                   |

| INC R3           | OB             | 1     | 1                               | 4                             | 12                      | 3                                   |

| INC R4           | OC             | 1     | 1                               | 4                             | 12                      | 3                                   |

Instruction Timing for N79E352(R), continued

| Instruction        | HEX<br>Op-Code | Bytes | N79E352(R)<br>Machine<br>Cycles | N79E352(R)<br>Clock<br>Cycles | 8052<br>Clock<br>Cycles | N79E352(R) v<br>8052 Speed<br>Ratio |

|--------------------|----------------|-------|---------------------------------|-------------------------------|-------------------------|-------------------------------------|

| MOV R1, direct     | A9             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R2, direct     | AA             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R3, direct     | AB             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R4, direct     | AC             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R5, direct     | AD             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R6, direct     | AE             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R7, direct     | AF             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R0, #data      | 78             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R1, #data      | 79             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R2, #data      | 7A             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R3, #data      | 7B             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R4, #data      | 7C             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R5, #data      | 7D             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R6, #data      | 7E             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV R7, #data      | 7F             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV @R0, A         | F6             | 1     | 1                               | 4                             | 12                      | 3                                   |

| MOV @R1, A         | F7             | 1     | 1                               | 4                             | 12                      | 3                                   |

| MOV @R0, direct    | A6             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV @R1, direct    | A7             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV @R0, #data     | 76             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV @R1, #data     | 77             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, A      | F5             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R0     | 88             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R1     | 89             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R2     | 8A             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R3     | 8B             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R4     | 8C             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R5     | 8D             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R6     | 8E             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, R7     | 8F             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, @R0    | 86             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, @R1    | 87             | 2     | 2                               | 8                             | 12                      | 1.5                                 |

| MOV direct, direct | 85             | 3     | 3                               | 12                            | 24                      | 2                                   |

| MOV direct, #data  | 75             | 3     | 3                               | 12                            | 24                      | 2                                   |

| MOV DPTR, #data 16 | 90             | 3     | 3                               | 12                            | 24                      | 2                                   |

| MOVC A, @A+DPTR    | 93             | 1     | 2                               | 8                             | 24                      | 3                                   |

Instruction Timing for N79E352(R), continued

| Instruction       | HEX<br>Op-Code | Bytes | N79E352(R)<br>Machine<br>Cycles | N79E352(R)<br>Clock<br>Cycles | 8052<br>Clock<br>Cycles | N79E352(R) vs<br>8052 Speed<br>Ratio |

|-------------------|----------------|-------|---------------------------------|-------------------------------|-------------------------|--------------------------------------|

| MOVX A, @R0       | E2             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOVX A, @R1       | E3             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOVX A, @DPTR     | E0             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOVX @R0, A       | F2             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOVX @R1, A       | F3             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOVX @DPTR, A     | F0             | 1     | 2 - 9                           | 8 - 36                        | 24                      | 3 - 0.66                             |

| MOV C, bit        | A2             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| MOV bit, C        | 92             | 2     | 2                               | 8                             | 24                      | 3                                    |

| ORL A, R0         | 48             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R1         | 49             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R2         | 4A             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R3         | 4B             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R4         | 4C             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R5         | 4D             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R6         | 4E             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, R7         | 4F             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, @R0        | 46             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, @R1        | 47             | 1     | 1                               | 4                             | 12                      | 3                                    |

| ORL A, direct     | 45             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| ORL A, #data      | 44             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| ORL direct, A     | 42             | 2     | 2                               | 8                             | 12                      | 1.5                                  |

| ORL direct, #data | 43             | 3     | 3                               | 12                            | 24                      | 2                                    |