Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                  |

| Core Processor             | 8051                                                                                    |

| Core Size                  | 8-Bit                                                                                   |

| Speed                      | 24MHz                                                                                   |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, UART/USART                                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                              |

| Number of I/O              | 38                                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                                            |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | 128 x 8                                                                                 |

| RAM Size                   | 256 x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                             |

| Data Converters            | -                                                                                       |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

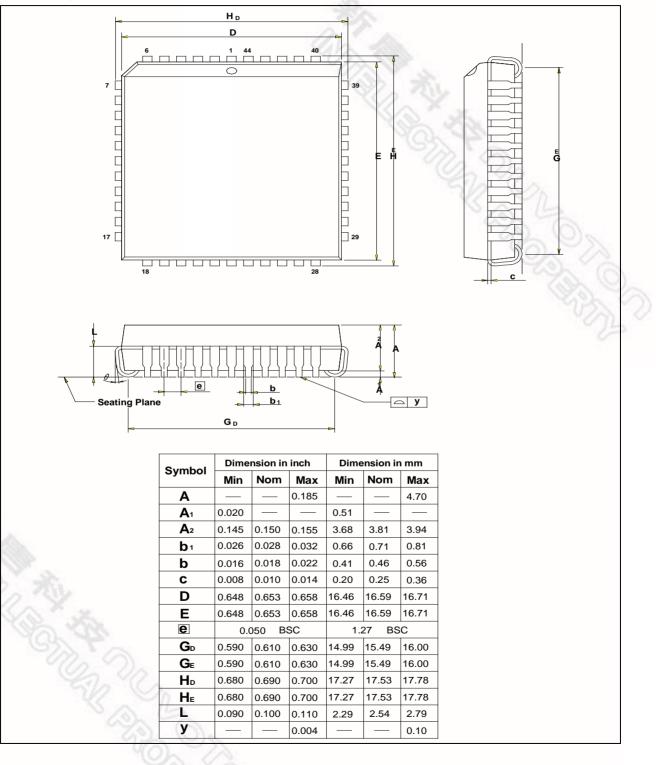

| Package / Case             | 48-LQFP                                                                                 |

| Supplier Device Package    | -                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/n79e352ralg |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 11. | RESE   | T CONDITIONS                               | 69    |

|-----|--------|--------------------------------------------|-------|

|     | 11.1   | Sources of reset                           | 69    |

|     | 11.2   | Reset State                                | 69    |

| 12. | PROC   | GRAMMABLE TIMERS/COUNTERS                  | 71    |

|     | 12.1   | Timer/Counters 0 & 1                       | 71    |

|     | 12.2   | Time-base Selection                        | 71    |

|     | 12.3   | Timer/Counter 2                            | 74    |

| 13. | NVM    | MEMORY                                     | 78    |

|     | 13.1   | Operation                                  | 78    |

| 14. | WAT    | CHDOG TIMER                                | 80    |

| 15. | UART   | SERIAL PORT                                | 82    |

|     | 15.1   | Mode 0                                     |       |

|     | 15.2   | Mode 1                                     | 83    |

|     | 15.3   | Mode 2                                     | 84    |

|     | 15.4   | Mode 3                                     | 87    |

|     | 15.5   | Framing Error Detection                    | 88    |

|     | 15.6   | Multiprocessor Communications              | 88    |

| 16. | I2C S  | ERIAL PORT                                 | 90    |

|     | 16.1   | I2C Bus                                    | 90    |

|     | 16.2   | The I2C Control Registers:                 | 91    |

|     | 16.3   | Modes of Operation                         | 93    |

|     | 16.4   | Data Transfer Flow in Five Operating Modes | 94    |

| 17. | TIME   | D ACCESS PROTECTION                        | . 100 |

| 18. | INTEF  | RRUPTS                                     | . 102 |

|     | 18.1   | Interrupt Sources                          | . 102 |

|     | 18.2   | Priority Level Structure                   | . 103 |

|     | 18.3   | Interrupt Response Time                    | . 105 |

|     | 18.4   | Interrupt Inputs                           | . 105 |

| 19. | KEYB   | OARD FUNCTION                              | . 106 |

| 20. | INPU   | T CAPTURE                                  | . 108 |

| 21. | PULS   | E WIDTH MODULATED OUTPUTS (PWM)            | . 110 |

| 22. | I/O P0 | DRT                                        | . 111 |

|     | 22.1   | Quasi-Bidirectional Output Configuration   |       |

|     | 22.2   | Open Drain Output Configuration            | . 112 |

|     | 22.3   | Push-Pull Output Configuration             | . 113 |

|     | 22.4   | Input Only Mode                            | . 113 |

# nuvoTon

|      | SMOD                        | SMOD0                                                                                                   | BOF                                                                | -           | GF1          | GF0            | PD                                      | IDL                                       |  |  |  |

|------|-----------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------|--------------|----------------|-----------------------------------------|-------------------------------------------|--|--|--|

| Mnem | Inemonic: PCON Address: 87h |                                                                                                         |                                                                    |             |              |                |                                         |                                           |  |  |  |

| BIT  | NAME                        | FUNCTION                                                                                                |                                                                    |             |              |                |                                         |                                           |  |  |  |

| 7    | SMOD                        | 1: This bit                                                                                             | 1: This bit doubles the serial port baud rate in mode 1, 2, and 3. |             |              |                |                                         |                                           |  |  |  |

| 6    | SMODO                       |                                                                                                         | ng Error De<br>ard 8052 fun                                        |             | able. SCO    | N.7 (SM0/F     | E) bit is i                             | used as SM0                               |  |  |  |

| 0    | SMOD0                       | 1: Framing Error Detection Enable. SCON.7 (SM0/FE) bit is used to reflect Frame Error (FE) status flag. |                                                                    |             |              |                |                                         | d to reflect as                           |  |  |  |

|      |                             | 0: Cleared                                                                                              | by software                                                        | Э.          |              | ~(1)           | 0                                       |                                           |  |  |  |

| 5    | BOF                         | 1: Set aut<br>power                                                                                     |                                                                    | hen a brow  | nout reset   | or interrupt h | as occurre                              | ed. Also set at                           |  |  |  |

| 4    | -                           | Reserved                                                                                                |                                                                    |             |              |                | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | - Ca                                      |  |  |  |

| 3    | GF1                         | General p                                                                                               | urpose user                                                        | flags.      |              |                | N                                       | 502                                       |  |  |  |

| 2    | GF0                         | General p                                                                                               | urpose user                                                        | flags.      |              |                |                                         | YON CO                                    |  |  |  |

| 1    | PD                          |                                                                                                         | PU goes into<br>d and progra                                       |             |              |                | mode, all                               | the clocks are                            |  |  |  |

| 0    | IDL                         | stoppe                                                                                                  | d, so progra                                                       | m executior | n is frozen. |                | k to the se                             | ks CPU clock<br>erial, timer and<br>ting. |  |  |  |

#### TIMER CONTROL

| Bit: | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0           |

|------|------------|-----|-----|-----|-----|-----|-----|-------------|

|      | TF1        | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0         |

| Mnem | onic: TCON |     |     |     |     |     | A   | ddress: 88h |

| BIT | NAME | FUNCTION                                                                                                                                                                                                                                                           |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1  | Timer 1 Overflow Flag. This bit is set when Timer 1 overflows. It is cleared automatically when the program does a timer 1 interrupt service routine. Software can also set or clear this bit.                                                                     |

| 6   | TR1  | Timer 1 Run Control. This bit is set or cleared by software to turn timer/counter on or off.                                                                                                                                                                       |

| 5   | TF0  | Timer 0 Overflow Flag. This bit is set when Timer 0 overflows. It is cleared automatically when the program does a timer 0 interrupt service routine. Software can also set or clear this bit.                                                                     |

| 4   | TR0  | Timer 0 Run Control. This bit is set or cleared by software to turn timer/counter on or off.                                                                                                                                                                       |

| 3   | IE1  | Interrupt 1 Edge Detect Flag: Set by hardware when an edge/level is detected on $\overline{INT1}$ . This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the inverse of the pin. |

| 2   | IT1  | Interrupt 1 Type Control. Set/cleared by software to specify falling edge/ low level triggered external inputs.                                                                                                                                                    |

| 1   | IE0  | Interrupt 0 Edge Detect Flag. Set by hardware when an edge/level is detected on                                                                                                                                                                                    |

# nuvoTon

|                                           | NAME                                                             | FUNCTIC                                                      | DN                                                                                |                                                 | 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -                                                      |                                                 |                                                                        |                         |

|-------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------|-------------------------|

| 7-0                                       | TL0.[7:0]                                                        | Timer 0 L                                                    | _SB.                                                                              |                                                 | - AR                                                                                         |                                                 |                                                                        |                         |

| TIME                                      | R 1 LSB                                                          |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        |                         |

| Bit:                                      | 7                                                                | 6                                                            | 5                                                                                 | 4                                               | 3                                                                                            | 2                                               | 1                                                                      | 0                       |

|                                           | TL1.7                                                            | TL1.6                                                        | TL1.5                                                                             | TL1.4                                           | TL1.3                                                                                        | TL1.2                                           | TL1.1                                                                  | TL1.0                   |

| Mnem                                      | onic: TL1                                                        |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | Address: 8B             |

| BIT                                       | NAME                                                             | FUNCTIC                                                      | N                                                                                 |                                                 |                                                                                              | Top.                                            | 20                                                                     |                         |

| 7-0                                       | TL1.[7:0]                                                        | Timer 1 L                                                    | _SB.                                                                              |                                                 |                                                                                              | 277                                             | A                                                                      |                         |

| TIME                                      | R 0 MSB                                                          |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        |                         |

| Bit:                                      | 7                                                                | 6                                                            | 5                                                                                 | 4                                               | 3                                                                                            | 2                                               | 3/1                                                                    | 0                       |

|                                           | TH0.7                                                            | TH0.6                                                        | TH0.5                                                                             | TH0.4                                           | 4 TH0.3                                                                                      | TH0.2                                           | TH0.1                                                                  | TH0.0                   |

| Mnem                                      | onic: TH0                                                        |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | Address: 8              |

| BIT                                       | NAME                                                             | FUNCTIO                                                      | ON                                                                                |                                                 |                                                                                              |                                                 |                                                                        | 2020                    |

| 7-0                                       | TH0.[7:0]                                                        | Timer 0                                                      | MSB.                                                                              |                                                 |                                                                                              |                                                 |                                                                        | CO.                     |

| TIMEF                                     | R 1 MSB                                                          |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | 0                       |

| Bit:                                      | 7                                                                | 6                                                            | 5                                                                                 | 4                                               | 3                                                                                            | 2                                               | 1                                                                      | 0                       |

|                                           | TH1.7                                                            | TH1.6                                                        | TH1.5                                                                             | TH1.4                                           | 4 TH1.3                                                                                      | TH1.2                                           | TH1.1                                                                  | TH1.0                   |

|                                           |                                                                  |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        |                         |

| Mnem                                      | onic: TH1                                                        |                                                              |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | Address: 8D             |

| Mnem<br>BIT                               | onic: TH1                                                        | FUNCTIO                                                      | DN                                                                                |                                                 |                                                                                              |                                                 |                                                                        | Address: 8D             |

|                                           |                                                                  | FUNCTIC                                                      |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | Address: 8D             |

| <b>BIT</b><br>7-0                         | <b>NAME</b><br>TH1.[7:0]                                         | Timer 1 I                                                    |                                                                                   |                                                 |                                                                                              |                                                 |                                                                        | Address: 8D             |

| <b>BIT</b><br>7-0                         | NAME                                                             | Timer 1 I                                                    |                                                                                   | 4                                               | 3                                                                                            | 2                                               | 1                                                                      | Address: 8D             |

| <b>BIT</b><br>7-0<br><b>CLOC</b>          | NAME<br>TH1.[7:0]                                                | Timer 1 I                                                    | MSB.                                                                              | 4<br>T1M                                        | 3<br>  TOM                                                                                   | 2<br>MD2                                        | 1<br>MD1                                                               |                         |

| BIT<br>7-0<br>CLOC<br>Bit:                | NAME<br>TH1.[7:0]<br>K CONTRO<br>7                               | Timer 1 I<br>6<br>WD0                                        | MSB.<br>5                                                                         |                                                 |                                                                                              |                                                 |                                                                        | 0                       |

| BIT<br>7-0<br>CLOC<br>Bit:                | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1                        | Timer 1 I<br>6<br>WD0                                        | MSB.<br>5<br>T2M                                                                  |                                                 |                                                                                              |                                                 |                                                                        | 0<br>MD0                |

| BIT<br>7-0<br>CLOC<br>Bit:<br>Mnem        | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1<br>onic: CKCOI         | Timer 1 I<br>6<br>WD0<br>N<br>FUNCTIO<br>Watchdo<br>the wato | MSB.<br>5<br>T2M<br>DN<br>Dg timer mo                                             | T1M                                             |                                                                                              | MD2<br>bits determ                              | MD1                                                                    | 0<br>MD0<br>Address: 8E |

| BIT<br>7-0<br>CLOC<br>Bit:<br>Mnem        | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1<br>onic: CKCOI         | Timer 1 I<br>6<br>WD0<br>N<br>FUNCTIO<br>Watchdo<br>the wato | MSB.<br>5<br>T2M<br>DN<br>Dg timer mo                                             | T1M                                             | T0M<br>ct bits: These<br>our time-out op                                                     | MD2<br>bits determ<br>bitons the r              | MD1                                                                    | 0<br>MD0<br>Address: 8E |

| BIT<br>7-0<br>CLOC<br>Bit:<br>Mnem        | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1<br>onic: CKCOI         | Timer 1 I<br>6<br>WD0<br>N<br>FUNCTIO<br>Watchdo<br>the wato | MSB.<br>5<br>T2M<br>DN<br>Dg timer mo<br>chdog timer<br>an the interr             | T1M<br>ode sele<br>: In all fo                  | T0M<br>ct bits: These<br>our time-out op<br>-out period.                                     | MD2<br>bits determ<br>otions the re<br>e-out Re | MD1<br>nine the time<br>eset time-out                                  | 0<br>MD0<br>Address: 8E |

| BIT<br>7-0<br>CLOC<br>Bit:<br>Mnem<br>BIT | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1<br>onic: CKCOI<br>NAME | Timer 1 I<br>6<br>WD0<br>N<br>FUNCTIO<br>Watchdo<br>the wato | MSB.<br>5<br>T2M<br>DN<br>Dg timer mo<br>chdog timer<br>an the interr<br>WD1      | Dde sele<br>c. In all fo<br>upt time<br>WD0     | T0M<br>ct bits: These<br>our time-out op<br>-out period.<br>Interrupt time                   | MD2<br>bits determ<br>ptions the m<br>e-out Re  | MD1<br>nine the time<br>eset time-out<br>set time-out                  | 0<br>MD0<br>Address: 8E |

| BIT<br>7-0<br>CLOC<br>Bit:<br>Mnem<br>BIT | NAME<br>TH1.[7:0]<br>K CONTRO<br>7<br>WD1<br>onic: CKCOI<br>NAME | Timer 1 I<br>6<br>WD0<br>N<br>FUNCTIO<br>Watchdo<br>the wato | MSB.<br>5<br>T2M<br>DN<br>Dg timer mo<br>chdog timer<br>an the interr<br>WD1<br>0 | Dde sele<br>. In all fo<br>upt time<br>WD0<br>0 | T0M<br>ct bits: These<br>our time-out op<br>-out period.<br>Interrupt time<br>2 <sup>6</sup> | MD2<br>bits determ<br>ptions the r              | MD1<br>hine the time<br>eset time-out<br>set time-out<br>$2^{6} + 512$ | 0<br>MD0<br>Address: 8E |

|               | -             | NVMADD<br>R.6                                                                                                                                                                                                                                                                                                                                               | NVMADD<br>R.5                                                | NVMADD<br>R.4                                     | NVMADD<br>R.3                              | NVMADD<br>R.2                                  | NVMADD<br>R.1                                                                | NVMADD<br>R.0              |

|---------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------|--------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------|----------------------------|

| Mnem          | onic: NVMA    | DDR                                                                                                                                                                                                                                                                                                                                                         |                                                              |                                                   | No.                                        |                                                | Ad                                                                           | ddress: C6h                |

| BIT           | NAME FUNCTION |                                                                                                                                                                                                                                                                                                                                                             |                                                              |                                                   |                                            |                                                |                                                                              |                            |

| 7             | -             | Re                                                                                                                                                                                                                                                                                                                                                          | served                                                       |                                                   | CO.                                        | Sec. 1                                         |                                                                              |                            |

| 6~0           | NVMADDF       | R.[6:0] Th                                                                                                                                                                                                                                                                                                                                                  | e NVM addre                                                  | ess:                                              | N/                                         | NY.                                            |                                                                              |                            |

|               |               | The register indicates NVM data memory address on On-<br>memory space.                                                                                                                                                                                                                                                                                      |                                                              |                                                   |                                            | Chip code                                      |                                                                              |                            |

| ТІМЕГ         | D ACCESS      |                                                                                                                                                                                                                                                                                                                                                             |                                                              |                                                   |                                            | -m                                             | 5                                                                            |                            |

| Bit:          | 7             | 6                                                                                                                                                                                                                                                                                                                                                           | 5                                                            | 4                                                 | 3                                          | 2                                              | 1. 0                                                                         | 0                          |

|               | TA.7          | TA.6                                                                                                                                                                                                                                                                                                                                                        | TA.5                                                         | TA.4                                              | TA.3                                       | TA.2                                           | TA.1                                                                         | TA.0                       |

| Mnem          | ionic: TA     |                                                                                                                                                                                                                                                                                                                                                             |                                                              |                                                   |                                            |                                                | Ad                                                                           | ddress: C7h                |

| BIT           | NAME          | FUNCTIO                                                                                                                                                                                                                                                                                                                                                     | N                                                            |                                                   |                                            |                                                | 0                                                                            | 20                         |

|               |               | The Timed Access register:<br>The Timed Access register controls the access to protected bits. To access<br>protected bits, the user must first write AAH to the TA. This must be immediately<br>followed by a write of 55H to TA. Now a window is opened in the protected bits<br>for three machine cycles, during which the user can write to these bits. |                                                              |                                                   |                                            |                                                |                                                                              |                            |

| 7-0           | TA.[7:0]      | The Time<br>protected<br>followed                                                                                                                                                                                                                                                                                                                           | ed Access r<br>bits, the use<br>by a write of                | er must first<br>55H to TA.                       | write AAH to<br>Now a wino                 | o the TA. Th<br>dow is opene                   | is must be in<br>ed in the pro                                               | mmediately<br>otected bits |

|               | TA.[7:0]      | The Time<br>protected<br>followed<br>for three                                                                                                                                                                                                                                                                                                              | ed Access r<br>bits, the use<br>by a write of                | er must first<br>55H to TA.                       | write AAH to<br>Now a wino                 | o the TA. Th<br>dow is opene                   | is must be in<br>ed in the pro                                               | mmediately<br>otected bits |

|               |               | The Time<br>protected<br>followed<br>for three                                                                                                                                                                                                                                                                                                              | ed Access r<br>bits, the use<br>by a write of                | er must first<br>55H to TA.                       | write AAH to<br>Now a wino                 | o the TA. Th<br>dow is opene                   | is must be in<br>ed in the pro                                               | mmediately<br>otected bits |

| TIMEF         | R 2 CONTRO    | The Time<br>protected<br>followed<br>for three                                                                                                                                                                                                                                                                                                              | ed Access r<br>bits, the use<br>by a write of<br>machine cyc | er must first<br>55H to TA.<br>les, during w      | write AAH to<br>Now a wind<br>hich the use | o the TA. Th<br>dow is open<br>er can write t  | is must be in<br>ed in the pro<br>o these bits.                              | mmediately<br>otected bits |

| TIMEF<br>Bit: | 7<br>7        | The Timprotected<br>followed<br>for three<br><b>DL</b><br>6<br>EXF2                                                                                                                                                                                                                                                                                         | ed Access r<br>bits, the use<br>by a write of<br>machine cyc | er must first<br>55H to TA.<br>les, during w<br>4 | write AAH to<br>Now a wino<br>hich the use | o the TA. Th<br>dow is opene<br>er can write t | is must be in<br>ed in the pro-<br>o these bits.<br>1<br>$C / \overline{T2}$ | nmediately<br>ptected bits |

|   |       | Топетной                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|---|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|   |       | Timer 2 overflow flag:                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 7 | TF2   | Timer 2 overflow flag: This bit is set when Timer 2 overflows. It is also set when<br>the count is equal to the capture register in down count mode. It can be set only<br>if RCLK and TCLK are both 0. It is cleared only by software. Software can also<br>set or clear this bit.                                                                                          |  |  |  |  |

| 6 | EXF2  | Timer 2 External Flag: A negative transition on the T2EX pin (P1.1) or timer 2 overflow will cause this flag to set based on the CP/ $\overline{RL2}$ , EXEN2 and DCEN bits. If set by a negative transition, this flag must be cleared by software. Setting this bit in software or detection of a negative transition on T2EX pin will force a timer interrupt if enabled. |  |  |  |  |

|   | and 4 | Receive Clock Flag: This bit determines the serial port time-base when receiving                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 5 | RCLK  | data in serial modes 1 or 3. If it is 0, then timer 1 overflow is used for baud rate generation, otherwise timer 2 overflow is used. Setting this bit forces timer 2 in baud rate generator mode.                                                                                                                                                                            |  |  |  |  |

|   |       | - 40 -                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|   | No.   | 7 TF2<br>6 EXF2                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Bit:  | 7           | 6        | 5              | 4             | 3       | 2       | 1      | 0          |

|-------|-------------|----------|----------------|---------------|---------|---------|--------|------------|

|       | CCH0.7      | CCH0.6   | CCH0.5         | CCH0.4        | CCH0.3  | CCH0.2  | CCH0.1 | CCH0.0     |

| Mnem  | nonic: CCH0 | )        |                |               | april 1 |         |        | Address: E |

| BIT   | NAME        | FUNCT    | ION            |               | -       | N.      |        |            |

| 7-0   | CCH0        | Capture  | e 0 high byte  | э.            | 6       | CAX.    | 26     |            |

| IINTE |             |          | GISTER 1       |               |         | Val.    | 225    |            |

| Bit:  | 7           | 6        | 5              | 4             | 3       | 2       | 10     | 0          |

|       | ECPTF       | EBO      | -              | EWDI          | -       | - 0     | EKB    | El2        |

| Mnem  | nonic: EIE  |          |                |               |         | <u></u> | R X    | Address: E |

| BIT   | NAME        | FUNCT    | ION            |               |         |         | - 493  | 0.0        |

| 7     | ECPTF       | 0: Disa  | ble capture    | interrupt.    |         |         | -4     | 0          |

| 1     | ECPIF       | 1: Enal  | ble capture    | interrupt.    |         |         |        |            |

|       |             | Enable   | brownout in    | nterrupt.     |         |         |        | SS)        |

| 6     | EBO         | 0: Disa  | ble brownou    | ut interrupt. |         |         |        |            |

|       |             | 1: Enal  | ble brownou    | it interrupt. |         |         |        | 1.2        |

| 5     | -           | Reserv   | /ed.           |               |         |         |        |            |

| 4     | EWDI        | 0: Disa  | ble Watchd     | log Timer Int | errupt. |         |        |            |

| 4     |             | 1: Enal  | ble Watchdo    | og Timer Inte | errupt. |         |        |            |

| 3~2   | -           | Reserv   | ed.            |               |         |         |        |            |

| 1     | EKB         | 0: Disa  | ble Keypad     | Interrupt.    |         |         |        |            |

|       | END         | 1: Enal  | ble Keypad     | Interrupt.    |         |         |        |            |

| 0     | EI2         | 0: Disal | ble I2C Inter  | rrupt.        |         |         |        |            |

| 0     |             | 1: Enat  | ole I2C Inter  | rupt.         |         |         |        |            |

| KEYE  | BOARD LE    | VEL      |                |               |         |         |        |            |

| Bit:  |             | 6        | 5              | 4             | 3       | 2       | 1      | 0          |

|       | KBL.7       | KBL.6    | KBL.5          | 6 KBL.4       | KBL.3   | KBL.2   | KBL.1  | KBL.0      |

| Mnem  | nonic: KBL  |          |                |               |         |         |        | Address: E |

| BIT   | NAME        | FUNCT    | ION            |               |         |         |        |            |

| 1     | 22.0        | Keyboa   | rd trigger lev | vel.          |         |         |        |            |

| 7~0   | KBL.7~0     | 0: Low   | level trigger. | .x pin.       |         |         |        |            |

| 1~0   | NDL.7~0     | 1: High  | level trigger  | r on KBI.x pi | n.      |         |        |            |

|       |             | [x = 0-7 | Ra             |               |         |         |        |            |

| PORT  | ГS SHMITT   | REGISTE  | RUN            |               |         |         |        |            |

| Bit:  | 7           | 6        | 5              | 4             | 3       | 2       | 1      | 0          |

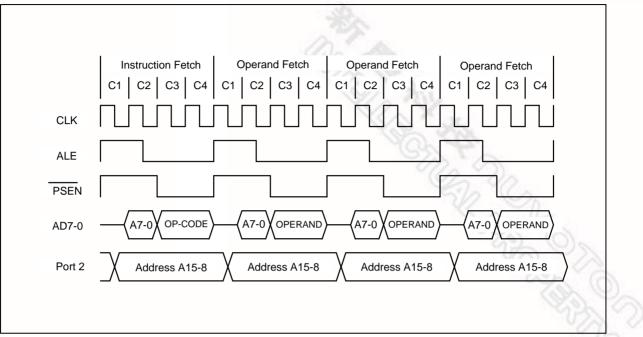

Figure 9-4: Four Cycle Instruction Timing

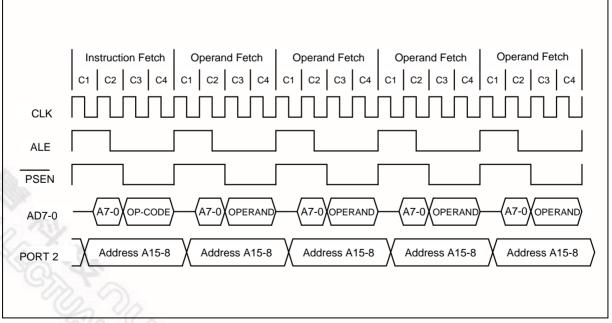

Figure 9-5: Five Cycle Instruction Timing

### nuvoTon

Reset does not affect the on-chip RAM, however, so RAM is preserved as long as VDD remains above approximately 2V, the minimum operating voltage for the RAM. If VDD falls below 2V, the RAM contents are also lost. In either case, the stack pointer is always reset, so the stack contents are lost.

The WDCON SFR bits are set/cleared in reset condition depending on the source of the reset.

|       | External reset | Watchdog reset | Power on reset |

|-------|----------------|----------------|----------------|

| WDCON | 0xxx0x00b      | 0xxx0100b      | 01xx0000b      |

The POR bit WDCON.6 is set only by the power on reset. WTRF bit WDCON.2 is set when the Watchdog timer causes a reset. A power on reset will also clear this bit. The EWRST bit WDCON.1 is cleared by all reset. This disables the Watchdog timer resets.

All the bits in this SFR have unrestricted read access. WDRUN, POR, EWRST, WDIF and WDCLR require Timed Access procedure to write. The remaining bits have unrestricted write accesses.

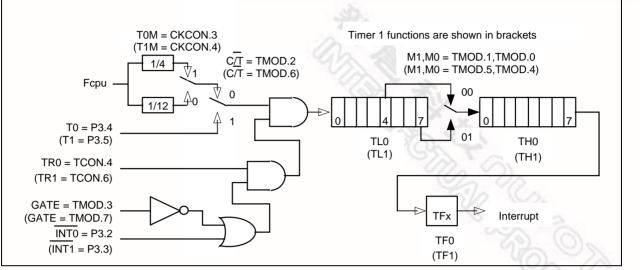

#### **12. PROGRAMMABLE TIMERS/COUNTERS**

The N79E352(R) has three 16-bit programmable timer/counters and one programmable Watchdog timer. The Watchdog timer is operationally quite different from the other two timers.

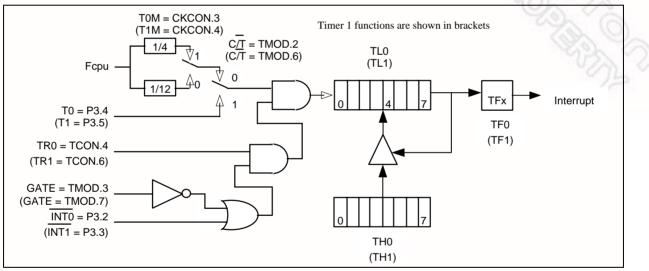

#### 12.1 Timer/Counters 0 & 1

Each of these Timer/Counters has two 8 bit registers which form the 16 bit counting register. For Timer/Counter 0 they are TH0, the upper 8 bits register, and TL0, the lower 8 bit register. Similarly Timer/Counter 1 has two 8 bit registers, TH1 and TL1. The two can be configured to operate either as timers, counting machine cycles or as counters counting external inputs.

When configured as a "Timer", the timer counts clock cycles. The timer clock can be programmed to be thought of as 1/12 of the system clock or 1/4 of the system clock. In the "Counter" mode, the register is incremented on the falling edge of the external input pin, T0 in case of Timer 0, and T1 for Timer 1. The T0 and T1 inputs are sampled in every machine cycle at C4. If the sampled value is high in one machine cycle and low in the next, then a valid high to low transition on the pin is recognized and the count register is incremented. Since it takes two machine cycles to recognize a negative transition on the pin, the maximum rate at which counting will take place is 1/24 of the master clock frequency. In either the "Timer" or "Counter" mode, the count register will be updated at C3. Therefore, in the "Timer" mode, the recognized negative transition on pin T0 and T1 can cause the count register value to be updated only in the machine cycle following the one in which the negative edge was detected.

The "Timer" or "Counter" function is selected by the " $C/\overline{T}$ " bit in the TMOD Special Function Register. Each Timer/Counter has one selection bit for its own; bit 2 of TMOD selects the function for Timer/Counter 0 and bit 6 of TMOD selects the function for Timer/Counter 1. In addition each Timer/Counter can be set to operate in any one of four possible modes. The mode selection is done by bits M0 and M1 in the TMOD SFR.

#### 12.2 Time-base Selection

The N79E352(R) gives the user two modes of operation for the timer. The timers can be programmed to operate like the standard 8051 family, counting at the rate of 1/12 of the clock speed. This will ensure that timing loops on the N79E352(R) and the standard 8051 can be matched. This is the default mode of operation of the N79E352(R) timers. The user also has the option to count in the turbo mode, where the timers will increment at the rate of 1/4 clock speed. This will straight-away increase the counting speed three times. This selection is done by the TOM and T1M bits in CKCON SFR. A reset sets these bits to 0, and the timers then operate in the standard 8051 mode. The user should set these bits to 1 if the timers are to operate in turbo mode.

#### 12.2.1 Mode 0

In Mode 0, the timer/counters act as a 8 bit counter with a 5 bit, divide by 32 pre-scale. In this mode we have a 13 bit timer/counter. The 13 bit counter consists of 8 bits of THx and 5 lower bits of TLx. The upper 3 bits of TLx are ignored.

The negative edge of the clock increments the count in the TLx register. When the fifth bit in TLx moves from 1 to 0, then the count in the THx register is incremented. When the count in THx moves from FFh to 00h, then the overflow flag TFx in TCON SFR is set. The counted input is enabled only if TRx is set and either GATE = 0 or  $\overline{INTx}$  = 1. When C/T is set to 0, then it will count clock cycles, and

if  $C/\overline{T}$  is set to 1, then it will count 1 to 0 transitions on T0 (P3.4) for timer 0 and T1 (P3.5) for timer 1. When the 13 bit count reaches 1FFFh the next count will cause it to roll-over to 0000h. The timer overflow flag TFx of the relevant timer is set and if enabled an interrupts will occur. Note that when used as a timer, the time-base may be either clock cycles/12 or clock cycles/4 as selected by the bits TxM of the CKCON SFR.

Figure 12-1: Timer/Counter Mode 0 & Mode 1

#### 12.2.2 Mode 1

Mode 1 is similar to Mode 0 except that the counting register forms a 16 bit counter, rather than a 13 bit counter. This means that all the bits of THx and TLx are used. Roll-over occurs when the timer moves from a count of FFFFh to 0000h. The timer overflow flag TFx of the relevant timer is set and if enabled an interrupt will occur. The selection of the time-base in the timer mode is similar to that in Mode 0. The gate function operates similarly to that in Mode 0.

#### 12.2.3 Mode 2

In Mode 2, the timer/counter is in the Auto Reload Mode. In this mode, TLx acts as a 8 bit count register, while THx holds the reload value. When the TLx register overflows from FFh to 00h, the TFx bit in TCON is set and TLx is reloaded with the contents of THx, and the counting process continues from here. The reload operation leaves the contents of the THx register unchanged. Counting is enabled by the TRx bit and proper setting of GATE and INTx pins. As in the other two modes 0 and 1 mode 2 allows counting of either clock cycles (clock/12 or clock/4) or pulses on pin Tn.

Figure 12-2: Timer/Counter Mode 2

#### 12.2.4 Mode 3

Mode 3 has different operating methods for the two timer/counters. For timer/counter 1, mode 3 simply freezes the counter. Timer/Counter 0, however, configures TL0 and TH0 as two separate 8 bit count registers in this mode. The logic for this mode is shown in the figure. TL0 uses the Timer/Counter 0 control bits  $C/\overline{T}$ , GATE, TR0, INT0 and TF0. The TL0 can be used to count clock cycles (clock/12 or clock/4) or 1-to-0 transitions on pin T0 as determined by C/T (TMOD.2). TH0 is forced as a clock cycle counter (clock/12 or clock/4) and takes over the use of TR1 and TF1 from Timer/Counter 1. Mode 3 is used in cases where an extra 8 bit timer is needed. With Timer 0 in Mode 3, Timer 1 can still be used in Modes 0, 1 and 2., but its flexibility is somewhat limited. While its basic functionality is maintained, it no longer has control over its overflow flag TF1 and the enable bit TR1. Timer 1 can still be used as a timer/counter and retains the use of GATE and INT1 pin. In this condition it can be turned on and off by switching it out of and into its own Mode 3. It can also be used as a baud rate generator for the serial port.

#### 16.2 The I2C Control Registers:

The I2C has 1 control register (I2CON) to control the transmit/receive flow, 1 data register (I2DAT) to buffer the Tx/Rx data, 1 status register (I2STATUS) to catch the state of Tx/Rx, recognizable slave address register for slave mode use and 1 clock rate control block for master mode to generate the variable baud rate.

#### 16.2.1 The Address Registers, I2ADDR

I2C port is equipped with one slave address register. The contents of the register are irrelevant when I2C is in master mode. In the slave mode, the seven most significant bits must be loaded with the MCU's own slave address. The I2C hardware will react if the contents of I2ADDR are matched with the received slave address.

The I2C ports support the "General Call" function. If the GC bit is set the I2C port1 hardware will respond to General Call address (00H). Clear GC bit to disable general call function.

When GC bit is set, the I2C is in Slave mode, it can be received the general call address by 00H after Master send general call address to I2C bus, then it will follow status of GC mode. If it is in Master mode, the AA bit must be cleared when it will send general call address of 00H to I2C bus.

#### 16.2.2 The Data Register, I2DAT

This register contains a byte of serial data to be transmitted or a byte which has just been received. The CPU can read from or write to this 8-bit directly addressable SFR while it is not in the process of shifting a byte. This occurs when the bus is in a defined state and the serial interrupt flag (SI) is set. Data in I2DAT remains stable as long as SI bit is set. While data is being shifted out, data on the bus is simultaneously being shifted in; I2DAT always contains the last data byte present on the bus. Thus, in the event of arbitration lost, the transition from master transmitter to slave receiver is made with the correct data in I2DAT.

I2DAT and the acknowledge bit form a 9-bit shift register, the acknowledge bit is controlled by the hardware and cannot be accessed by the CPU. Serial data is shifted through the acknowledge bit into I2DAT on the rising edges of serial clock pulses on the SCL line. When a byte has been shifted into I2DAT, the serial data is available in I2DAT, and the acknowledge bit (ACK or NACK) is returned by the control logic during the ninth clock pulse. Serial data is shifted out from I2DAT on the falling edges of SCL clock pulses, and is shifted into I2DAT on the rising edges of SCL clock pulses.

| Str. | I2DAT.7 I2DAT.6 I2DAT. | 5 I2DAT.4 I2DA <sup>-</sup> | T.3 I2DAT.2 | I2DAT.1 I2DAT.0 |  |

|------|------------------------|-----------------------------|-------------|-----------------|--|

| 2.3  | ◀───                   | shifting direction          | on 🚽        | •               |  |

| Ch S | 15                     |                             |             |                 |  |

|      |                        |                             |             |                 |  |

|      |                        |                             |             |                 |  |

|      |                        |                             |             |                 |  |

|      |                        |                             |             |                 |  |

|      |                        |                             |             |                 |  |

|      |                        |                             |             |                 |  |

### ηυνοτοη

#### 16.3.3 Slave Receiver Mode

Serial data and the serial clock are received through SDA and SCL. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit.

#### 16.3.4 Slave Transmitter Mode

The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit will indicate that the transfer direction is reversed. Serial data is transmitted via SDA while the serial clock is input through SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer.

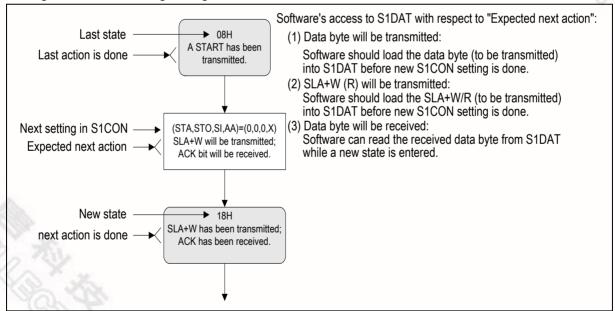

#### 16.4 Data Transfer Flow in Five Operating Modes

The five operating modes are: Master/Transmitter, Master/Receiver, Slave/Transmitter, Slave/Receiver and GC Call. Bits STA, STO and AA in I2CON register will determine the next state of the I2C hardware after SI flag is cleared. Upon complexion of the new action, a new status code will be updated and the SI flag will be set. If the I2C interrupt control bits (EA and EI2) are enable, appropriate action or software branch of the new status code can be performed in the Interrupt service routine.

Data transfers in each mode are shown in the following figures.

\*\*\* Legend for the following five figures:

Figure 16-3: Legen for the following four figures

- 94 -

#### **18. INTERRUPTS**

N79E352(R) has four priority level interrupts structure with 11 interrupt sources. Each of the interrupt sources has an individual priority bit, flag, interrupt vector and enable bit. In addition, the interrupts can be globally enabled or disabled.

#### **18.1 Interrupt Sources**

The External Interrupts INT0 and INT1 can be either edge triggered or level triggered, programmable through bits IT0 and IT1 (SFR TCON). The bits IE0 and IE1 in TCON register are the flags which are checked to generate the interrupt. In the edge triggered mode, the INTx inputs are sampled in every machine cycle. If the sample is high in one cycle and low in the next, then a high to low transition is detected and the interrupts request flag IEx in TCON is set. The flag bit requests the interrupt. Since the external interrupts are sampled every machine cycle, they have to be held high or low for at least one complete machine cycle. The IEx flag is automatically cleared when the service routine is called. If the level triggered mode is selected, then the requesting source has to hold the pin low till the interrupt is serviced. The IEx flag will not be cleared by the hardware on entering the service routine. If the interrupt continues to be held low even after the service routine is completed, then the processor may acknowledge another interrupt request from the same source.

The Timer 0 and 1 Interrupts are generated by the TF0 and TF1 flags. These flags are set by the overflow in the Timer 0 and Timer 1. The TF0 and TF1 flags are automatically cleared by the hardware when the timer interrupt is serviced. The Watchdog timer can be used as a system monitor or a simple timer. In either case, when the time-out count is reached, the Watchdog Timer interrupt flag WDIF (WDCON.3) is set. If the interrupt is enabled by the enable bit EIE.4, then an interrupt will occur.

The timer 2 interrupt is generated through TF2 (timer 2 overflow/compare match). The hardware does not clear these flags when a timer 2 interrupt is executed.

The uart serial block can generate interrupt on reception or transmission. There are two interrupt sources from the uart block, which are obtained by the RI and TI bits in the SCON SFR. These bits are not automatically cleared by the hardware, and the user will have to clear these bits using software.

This device also provide an independent I2C serial port. When new I2C state is present in I2STATUS, the SI flag is set by hardware, and if EA and EI2 bits are both set, the I2C interrupt is requested. SI must be cleared by software.

Keyboard interrupt is generated when any of the keypad connected to P0 pins is pressed. Each keypad interrupt can be individually enabled or disabled. User will have to software clear the flag bit.

The input capture 0 interrupt is generated through CPTF0 flag. CPTF0 flag is set by input capture events. The hardware does not clear this flag when the capture interrupt is executed. Software has to clear the flag.

Brownout detect can cause brownout flag, BOF, to be asserted if power voltage drop below brownout voltage level. Interrupt will occur if BOI (AUXR1.5), EBO (EIE.6) and global interrupt enable are set.

| Source               | Vector Address | Source             | Vector Address |

|----------------------|----------------|--------------------|----------------|

| External Interrupt 0 | 0003H          | Timer 0 Overflow   | 000BH          |

| External Interrupt 1 | 0013H          | Timer 1 Overflow   | 001BH          |

| Serial Port          | 0023H          | Brownout Interrupt | 002BH          |

| I2C Interrupt        | 0033H          | KBI Interrupt      | 003BH          |

| Timer 2 Overflow     | 0043H          | -                  | 004BH          |

| Watchdog Timer       | 0053H          | -                  | 005BH          |

|  | 0063H | Input Capture 0 Interrupt | 006BH |  |  |

|--|-------|---------------------------|-------|--|--|

|  |       |                           |       |  |  |

Table 18- 1: N79E352(R) interrupt vector table

#### **18.2 Priority Level Structure**

There are four priority levels for the interrupts, highest, high, low and lowest. The interrupt sources can be individually set to either high or low levels. Naturally, a higher priority interrupt cannot be interrupted by a lower priority interrupt. However there exists a pre-defined hierarchy amongst the interrupts themselves. This hierarchy comes into play when the interrupt controller has to resolve simultaneous requests having the same priority level. This hierarchy is defined as shown on Table 18- 2: Four-level interrupts priority.

The interrupt flags are sampled every machine cycle. In the same machine cycle, the sampled interrupts are polled and their priority is resolved. If certain conditions are met then the hardware will execute an internally generated LCALL instruction which will vector the process to the appropriate interrupt vector address. The conditions for generating the LCALL are;

1. An interrupt of equal or higher priority is not currently being serviced.

2. The current polling cycle is the last machine cycle of the instruction currently being execute.

3. The current instruction does not involve a write to IE, EIE, IPO, IPOH, IP1 or IPH1 registers and is not a RETI.

If any of these conditions are not met, then the LCALL will not be generated. The polling cycle is repeated every machine cycle, with the interrupts sampled in the same machine cycle. If an interrupt flag is active in one cycle but not responded to, and is not active when the above conditions are met, the denied interrupt will not be serviced. This means that active interrupts are not remembered; every polling cycle is new.

The processor responds to a valid interrupt by executing an LCALL instruction to the appropriate service routine. This may or may not clear the flag which caused the interrupt. In case of Timer interrupts, the TF0 or TF1 flags are cleared by hardware whenever the processor vectors to the appropriate timer service routine. In case of external interrupt, /INT0 and /INT1, the flags are cleared only if they are edge triggered. In case of Serial interrupts, the flags are not cleared by hardware. In the case of Timer 2 interrupt, the flags are not cleared by hardware. The Watchdog timer interrupt flag WDIF has to be cleared by software. The hardware LCALL behaves exactly like the software LCALL instruction. This instruction saves the Program Counter contents onto the Stack, but does not save the Program Status Word PSW. The PC is reloaded with the vector address of that interrupt which caused the LCALL. These address of vector for the different sources are as shown on Table 18- 3: Summary of interrupt sources. The vector table is not evenly spaced; this is to accommodate future expansions to the device family.

Execution continues from the vectored address till an RETI instruction is executed. On execution of the RETI instruction the processor pops the Stack and loads the PC with the contents at the top of the stack. The user must take care that the status of the stack is restored to what it was after the hardware LCALL, if the execution is to return to the interrupted program. The processor does not notice anything if the stack contents are modified and will proceed with execution from the address put back into PC. Note that a RET instruction would perform exactly the same process as a RETI instruction, but it would not inform the Interrupt Controller that the interrupt service routine is completed, and would leave the controller still thinking that the service routine is underway.

N79E352(R) uses a four priority level interrupt structure. This allows great flexibility in controlling the handling of the interrupt sources.

| PRIOR | ITY BITS | INTERRUPT PRIORITY LEVEL   |

|-------|----------|----------------------------|

| IPXH  | IPX      | INTERROFT PRIORITT LEVEL   |

| 0     | 0        | Level 0 (lowest priority)  |

| 0     | 1        | Level 1                    |

| 1     | 0        | Level 2                    |

| 1     | 1        | Level 3 (highest priority) |

Table 18- 2: Four-level interrupts priority

Each interrupt source can be individually enabled or disabled by setting or clearing a bit in registers IE or EIE. The IE register also contains a global disable bit, EA, which disables all interrupts at once.

Each interrupt source can be individually programmed to one of four priority levels by setting or clearing bits in the IPO, IPOH, IP1, and IP1H registers. An interrupt service routine in progress can be interrupted by a higher priority interrupt, but not by another interrupt of the same or lower priority. The highest priority interrupt service cannot be interrupted by any other interrupt source. So, if two requests of different priority levels are received simultaneously, the request of higher priority level is serviced.

If requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. This is called the arbitration ranking. Note that the arbitration ranking is only used to resolve simultaneous requests of the same priority level.

| Table below summarizes the interrupt sources,      | , flag bits, vector address, enable bits, priority bits, |

|----------------------------------------------------|----------------------------------------------------------|

| arbitration ranking, and whether each interrupt ma | ay wake up the CPU from Power Down mode.                 |

| Source                  | Flag     | Vector<br>address | Enable<br>bit   | Flag<br>cleared by    | Priority<br>bit  | Arbitration<br>ranking | Power-<br>down<br>wakeup |

|-------------------------|----------|-------------------|-----------------|-----------------------|------------------|------------------------|--------------------------|

| External<br>Interrupt 0 | IE0      | 0003H             | EX0<br>(IE.0)   | Hardware,<br>Software | IP0H.0,<br>IP0.0 | 1(highest)             | Yes                      |

| Brownout<br>Detect      | BOF      | 002BH             | EBO<br>(EIE.6)  | Hardware              | IP1H.6,<br>IP1.6 | 2                      | Yes                      |

| Watchdog<br>Timer       | WDIF     | 0053H             | EWDI<br>(EIE.4) | Software              | IP1H.4,<br>IP1.4 | 3                      | Yes                      |

| Timer 0<br>Overflow     | TF0      | 000BH             | ET0<br>(IE.1)   | Hardware,<br>Software | IP0H.1,<br>IP0.1 | 4                      | No                       |

| I2C<br>Interrupt        | SI + TIF | 0033h             | El2<br>(EIE.0)  | Software              | IP1H.0,<br>IP1.0 | 5                      | No                       |

| External<br>Interrupt 1 | IE1      | 0013H             | EX1<br>(IE.2)   | Hardware,<br>Software | IP0H.2,<br>IP0.2 | 6                      | Yes                      |

| КВІ                     | KBF      | 003BH             | EKB<br>(EIE.1)  | Software              | IP1H.1,<br>IP1.1 | 7                      | Yes                      |

| Timer 1<br>Overflow     | TF1      | 001BH             | ET1<br>(IE.3)   | Hardware,<br>Software | IP0H.3,<br>IP0.3 | 8                      | No                       |

| UART                    | RI + TI  | 0023H             | ES<br>(IE.4)    | Software              | IP0H.4,<br>IP0.4 | 9                      | No                       |

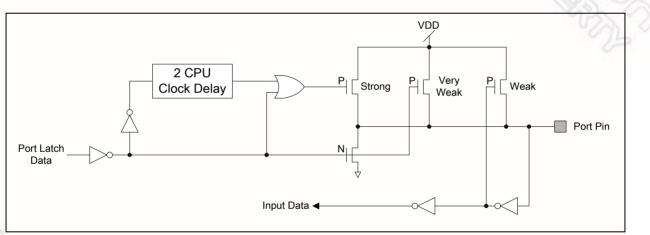

The default port output configuration for standard N79E352(R) I/O ports is the guasi-bidirectional output that is common on the 80C51 and most of its derivatives. This output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is pulled low, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open drain output except that there are three pull-up transistors in the quasi-bidirectional output that serve different purposes. One of these pull-ups, called the "very weak" pull-up, is turned on whenever the port latch for the pin contains a logic 1. The very weak pull-up sources a very small current that will pull the pin high if it is left floating.

A second pull-up, called the "weak" pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the weak pull-up turns off, and only the very weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the weak pullup and take the voltage on the port pin below its input threshold.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-to-high transitions on a quasi-bidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for a brief time, two CPU clocks, in order to pull the port pin high quickly. Then it turns off again. The quasi-bidirectional port configuration is shown as below.

Figure 22-1: Quasi-Bidirectional Output

#### 22.2 Open Drain Output Configuration

The open drain output configuration turns off all pull-ups and only drives the pull-down transistor of the port driver when the port latch contains a logic 0. To be used as a logic output, a port configured in this manner must have an external pull-up, typically a resistor tied to VDD. The pull-down for this mode is The second second the same as for the quasi-bidirectional mode. The open drain port configuration is shown as below.

#### 27.2 D.C. Characteristics

| (TA = -40~85°C, unless otherwise specified.) |

|----------------------------------------------|

|----------------------------------------------|

| DADAMETER                                                | OVM                             |                    | SPECIFI       | CATION               | 5    | TEST CONDITIONS                                                         |