# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                 |

| Core Size                  | 32-Bit Single-Core                                              |

| Speed                      | 80MHz                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT    |

| Number of I/O              | 65                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 32K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 32x12b; D/A 2x10b                                           |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 80-TQFP                                                         |

| Supplier Device Package    | 80-TQFP (12x12)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/sim3c157-b-gq |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

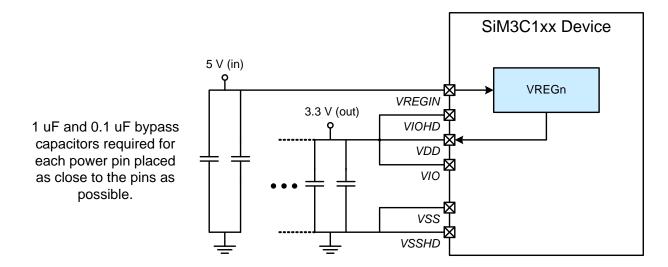

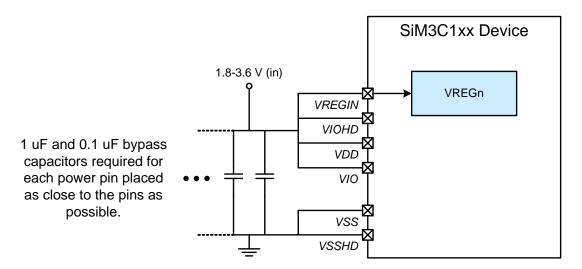

# 2. Typical Connection Diagrams

This section provides typical connection diagrams for SiM3C1xx devices.

### 2.1. Power

Figure 2.1 shows a typical connection diagram for the power pins of the SiM3C1xx devices when the internal regulator is in use.

Figure 2.1. Connection Diagram with Voltage Regulator Used

Figure 2.2 shows a typical connection diagram for the power pins of the SiM3C1xx devices when the internal regulator is not used.

Figure 2.2. Connection Diagram with Voltage Regulator Not Used

| Table 3.2. Power Co | nsumption | (Continued) |

|---------------------|-----------|-------------|

|---------------------|-----------|-------------|

| Parameter                            | Symbol               | Test Condition                                               | Min | Тур  | Max  | Unit |

|--------------------------------------|----------------------|--------------------------------------------------------------|-----|------|------|------|

| Analog Peripheral Supply Current     | ts                   |                                                              | 1   |      |      |      |

| Voltage Regulator (VREG0)            | I <sub>VREGIN</sub>  | Normal Mode, T <sub>A</sub> = 25 °C<br>BGDIS = 0, SUSEN = 0  |     | 300  |      | μA   |

|                                      |                      | Normal Mode, $T_A = 85 \degree C$<br>BGDIS = 0, SUSEN = 0    | _   |      | 650  | μA   |

|                                      |                      | Suspend Mode, T <sub>A</sub> = 25 °C<br>BGDIS = 0, SUSEN = 1 | _   | 75   |      | μA   |

|                                      |                      | Suspend Mode, T <sub>A</sub> = 85 °C<br>BGDIS = 0, SUSEN = 1 | _   |      | 115  | μA   |

|                                      |                      | Sleep Mode, T <sub>A</sub> = 25 °C<br>BGDIS = 1, SUSEN = X   | _   | 90   | _    | nA   |

|                                      |                      | Sleep Mode, T <sub>A</sub> = 85 °C<br>BGDIS = 1, SUSEN = X   | _   | _    | 500  | nA   |

| Voltage Regulator (VREG0) Sense      | I <sub>VRSENSE</sub> | SENSEEN = 1                                                  |     | 3    |      | μA   |

| External Regulator (EXTVREG0)        | I <sub>EXTVREG</sub> | Regulator                                                    | _   | 215  | 250  | μA   |

|                                      |                      | Current Sensor                                               |     | 7    | —    | μA   |

| PLL0 Oscillator (PLL0OSC)            | I <sub>PLLOSC</sub>  | Operating at 80 MHz                                          | _   | 1.75 | 1.86 | mA   |

| Low-Power Oscillator (LPOSC0)        | I <sub>LPOSC</sub>   | Operating at 20 MHz                                          |     | 190  | —    | μA   |

|                                      |                      | Operating at 2.5 MHz                                         |     | 40   | _    | μA   |

| Low-Frequency Oscillator<br>(LFOSC0) | I <sub>LFOSC</sub>   | Operating at 16.4 kHz,<br>T <sub>A</sub> = 25 °C             | _   | 215  |      | nA   |

|                                      |                      | Operating at 16.4 kHz,<br>T <sub>A</sub> = 85 °C             | _   |      | 500  | nA   |

Notes:

1. Perhipheral currents drop to zero when peripheral clock and peripheral are disabled, unless otherwise noted.

Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

3. Includes all peripherals that cannot have clocks gated in the Clock Control module.

4. Includes supply current from internal regulator and PLL0OSC (>20 MHz) or LPOSC0 (<=20 MHz).

5. Flash execution numbers use 2 wait states for 80 MHz and 0 wait states at 20 MHz or less.

6. RAM execution numbers use 0 wait states for all frequencies.

7. IDAC output current and IVC input current not included.

8. Bias current only. Does not include dynamic current from oscillator running at speed.

#### Table 3.2. Power Consumption (Continued)

| Parameter            | Symbol               | Test Condition | Min | Тур | Max | Unit |

|----------------------|----------------------|----------------|-----|-----|-----|------|

| Flash Current on VDD |                      |                |     |     |     |      |

| Write Operation      | I <sub>FLASH-W</sub> |                | _   | _   | 8   | mA   |

| Erase Operation      | I <sub>FLASH-E</sub> |                | _   |     | 15  | mA   |

| Notes:               | · · ·                |                |     | •   | •   | •    |

Notes:

- 1. Perhipheral currents drop to zero when peripheral clock and peripheral are disabled, unless otherwise noted.

- Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 3. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 4. Includes supply current from internal regulator and PLL0OSC (>20 MHz) or LPOSC0 (<=20 MHz).

- 5. Flash execution numbers use 2 wait states for 80 MHz and 0 wait states at 20 MHz or less.

- 6. RAM execution numbers use 0 wait states for all frequencies.

- 7. IDAC output current and IVC input current not included.

- 8. Bias current only. Does not include dynamic current from oscillator running at speed.

#### Table 3.3. Power Mode Wake Up Times

| Parameter                   | Symbol             | Test Condition | Min | Тур | Max | Unit   |

|-----------------------------|--------------------|----------------|-----|-----|-----|--------|

| Power Mode 2 Wake Time      | t <sub>PM2</sub>   |                | 4   |     | 5   | clocks |

| Power Mode 3 Fast Wake Time | t <sub>PM3FW</sub> |                | _   | 425 | —   | μs     |

| Power Mode 9 Wake Time      | t <sub>PM9</sub>   |                |     | 12  |     | μs     |

## Table 3.16. Comparator (Continued)

| Parameter                    | Symbol             | Test Condition | Min   | Тур  | Max                   | Unit  |

|------------------------------|--------------------|----------------|-------|------|-----------------------|-------|

| Positive Hysteresis          | HYS <sub>CP+</sub> | CMPHYP = 00    |       | 1.4  | _                     | mV    |

| Mode 3 (CPMD = 11)           |                    | CMPHYP = 01    |       | 4    |                       | mV    |

|                              |                    | CMPHYP = 10    |       | 8    | —                     | mV    |

|                              |                    | CMPHYP = 11    |       | 16   | —                     | mV    |

| Negative Hysteresis          | HYS <sub>CP-</sub> | CMPHYN = 00    |       | 1.4  |                       | mV    |

| Mode 3 (CPMD = 11)           |                    | CMPHYN = 01    |       | -4   | —                     | mV    |

|                              |                    | CMPHYN = 10    |       | -8   | —                     | mV    |

|                              |                    | CMPHYN = 11    |       | -16  | —                     | mV    |

| Input Range (CP+ or CP-)     | V <sub>IN</sub>    |                | -0.25 | _    | V <sub>DD</sub> +0.25 | V     |

| Input Pin Capacitance        | C <sub>CP</sub>    | PB2 Pins       |       | 7.5  | —                     | pF    |

|                              |                    | PB3 Pins       |       | 10.5 |                       | pF    |

| Common-Mode Rejection Ratio  | CMRR <sub>CP</sub> |                |       | 75   |                       | dB    |

| Power Supply Rejection Ratio | PSRR <sub>CP</sub> |                | _     | 72   | —                     | dB    |

| Input Offset Voltage         | V <sub>OFF</sub>   |                | -10   | 0    | 10                    | mV    |

| Input Offset Tempco          | TC <sub>OFF</sub>  |                | —     | 3.5  | —                     | µV/°C |

| Reference DAC Resolution     | N <sub>Bits</sub>  |                |       | 6    |                       | bits  |

## Table 3.17. Port I/O (Continued)

| Parameter                                                             | Symbol              | Test Condition                                  | Min                     | Тур         | Max | Unit |

|-----------------------------------------------------------------------|---------------------|-------------------------------------------------|-------------------------|-------------|-----|------|

| Output Fall Time                                                      | t <sub>F</sub>      | Slew Rate Mode 0,<br>V <sub>IOHD</sub> = 5 V    | _                       | 50          |     | ns   |

|                                                                       |                     | Slew Rate Mode 1,<br>V <sub>IOHD</sub> = 5 V    |                         | 300         | —   | ns   |

|                                                                       |                     | Slew Rate Mode 2,<br>V <sub>IOHD</sub> = 5 V    |                         | 1           |     | μs   |

|                                                                       |                     | Slew Rate Mode 3,<br>V <sub>IOHD</sub> = 5 V    |                         | 3           |     | μs   |

| Input High Voltage                                                    | V <sub>IH</sub>     | 1.8 V <u>≤</u> V <sub>IOHD</sub> <u>≤</u> 2.0 V | 0.7 x V <sub>IOHD</sub> | _           |     | V    |

|                                                                       |                     | 2.0 V <u>&lt;</u> V <sub>IOHD</sub> ≤ 6 V       | V <sub>IOHD</sub> – 0.6 | _           | _   | V    |

| Input Low Voltage                                                     | V <sub>IL</sub>     |                                                 | _                       | _           | 0.6 | V    |

| N-Channel Sink Current Limit                                          | I <sub>SINKL</sub>  | Mode 0                                          | _                       | 1.75        |     | mA   |

| $(2.7 V \le V_{IOHD} \le 6 V,$<br>$V_{OL} = 0.8 V)$<br>See Figure 3.1 |                     | Mode 1                                          | _                       | 2.5         |     |      |

|                                                                       |                     | Mode 2                                          | _                       | 3.5         |     |      |

|                                                                       |                     | Mode 3                                          |                         | 4.75        |     |      |

|                                                                       |                     | Mode 4                                          | _                       | 7           | _   |      |

|                                                                       | -                   | Mode 5                                          | —                       | 9.5         |     |      |

|                                                                       | -                   | Mode 6                                          |                         | 14          | _   |      |

|                                                                       | -                   | Mode 7                                          |                         | 18.75       | _   |      |

|                                                                       | -                   | Mode 8                                          | _                       | 28.25       |     |      |

|                                                                       | -                   | Mode 9                                          | _                       | 37.5        |     |      |

|                                                                       |                     | Mode 10                                         | _                       | 56.25       | _   |      |

|                                                                       | -                   | Mode 11                                         | _                       | 75          |     |      |

|                                                                       | -                   | Mode 12                                         |                         | 112.5       |     |      |

|                                                                       |                     | Mode 13                                         | —                       | 150         |     | 1    |

|                                                                       |                     | Mode 14                                         | —                       | 225         | —   | 1    |

|                                                                       |                     | Mode 15                                         | —                       | 300         | —   | 1    |

| Total N-Channel Sink Current on P4.0-P4.5 (DC)                        | I <sub>SINKLT</sub> |                                                 | _                       |             | 400 | mA   |

| *Note: RESET does not drive to logic                                  | high. Specific      | cations for RESET V <sub>OL</sub> adhe          | ere to the low dri      | ve setting. |     |      |

# Table 3.17. Port I/O (Continued)

| Parameter                                          | Symbol             | Test Condition                        | Min              | Тур           | Мах | Unit |

|----------------------------------------------------|--------------------|---------------------------------------|------------------|---------------|-----|------|

| P-Channel Source Current Limit                     | I <sub>SRCL</sub>  | Mode 0                                | _                | 0.8           |     | mA   |

| $(2.7 V \leq VIOHD \leq 6 V,$                      |                    | Mode 1                                | _                | 1.25          |     |      |

| V <sub>OH</sub> = VIOHD – 0.8 V)<br>See Figure 3.2 |                    | Mode 2                                | _                | 1.75          |     |      |

| See Figure 5.2                                     |                    | Mode 3                                | _                | 2.5           |     |      |

|                                                    |                    | Mode 4                                | _                | 3.5           |     |      |

|                                                    |                    | Mode 5                                | _                | 4.75          |     |      |

|                                                    |                    | Mode 6                                | _                | 7             |     |      |

|                                                    |                    | Mode 7                                | _                | 9.5           |     |      |

|                                                    |                    | Mode 8                                | _                | 14            |     |      |

|                                                    |                    | Mode 9                                | _                | 18.75         |     |      |

|                                                    |                    | Mode 10                               | _                | 28.25         | _   |      |

|                                                    |                    | Mode 11                               | _                | 37.5          | _   |      |

|                                                    |                    | Mode 12                               | _                | 56.25         |     |      |

|                                                    |                    | Mode 13                               | _                | 75            | _   |      |

|                                                    |                    | Mode 14                               | _                | 112.5         |     |      |

|                                                    |                    | Mode 15                               | _                | 150           |     |      |

| Total P-Channel Source Current on P4.0-P4.5 (DC)   | I <sub>SRCLT</sub> |                                       | -                | —             | 400 | mA   |

| Pin Capacitance                                    | C <sub>IO</sub>    |                                       | _                | 30            |     | pF   |

| Weak Pull-Up Current in Low Volt-<br>age Mode      | I <sub>PU</sub>    | V <sub>IOHD</sub> = 1.8 V             | -6               | -3.5          | -2  | μA   |

|                                                    |                    | V <sub>IOHD</sub> = 3.6 V             | -30              | -20           | -10 | μA   |

| Weak Pull-Up Current in High Volt-<br>age Mode     | I <sub>PU</sub>    | V <sub>IOHD</sub> = 2.7 V             | -15              | -10           | -5  | μA   |

|                                                    |                    | V <sub>IOHD</sub> = 6 V               | -30              | -20           | -10 | μA   |

| Input Leakage (Pullups off)                        | I <sub>LK</sub>    |                                       | -1               |               | 1   | μA   |

| *Note: RESET does not drive to logic h             | igh. Specifica     | itions for RESET V <sub>OL</sub> adhe | ere to the low d | rive setting. |     |      |

# 4. Precision32<sup>™</sup> SiM3C1xx System Overview

The SiM3C1xx Precision32<sup>™</sup> devices are fully integrated, mixed-signal system-on-a-chip MCUs. Highlighted features are listed below. Refer to Table 5.1 for specific product feature selection and part ordering numbers.

- Core:

- 32-bit ARM Cortex-M3 CPU.

- 80 MHz maximum operating frequency.

- Branch target cache and prefetch buffers to minimize wait states.

- Memory: 32–256 kB Flash; in-system programmable, 8–32 kB SRAM (including 4 kB retention SRAM, which preserves state in PM9 mode).

- Power:

- Low drop-out (LDO) regulator for CPU core voltage.

- Power-on reset circuit and brownout detectors.

- 3.3 V output LDO for direct power from 5 V supplies.

- External transistor regulator.

- Power Management Unit (PMU).

- I/O: Up to 65 total multifunction I/O pins:

- Up to six programmable high-power capable (5–300 mA with programmable current limiting, 1.8–5 V).

- Up to twelve 5 V tolerant general purpose pins.

- Two flexible peripheral crossbars for peripheral routing.

- Clock Sources:

- Internal oscillator with PLL: 23–80 MHz with ± 1.5% accuracy in free-running mode.

- Low-power internal oscillator: 20 MHz and 2.5 MHz modes.

- Low-frequency internal oscillator: 16.4 kHz.

- External RTC crystal oscillator: 32.768 kHz.

- External oscillator: Crystal, RC, C, CMOS clock modes.

- Programmable clock divider allows any oscillator source to be divided by binary factor from 1-128.

- Data Peripherals:

- 16-Channel DMA Controller.

- 128/192/256-bit Hardware AES Encryption.

- 16/32-bit CRC.

#### Timers/Counters and PWM:

- 6-channel Enhanced Programmable Counter Array (EPCAn) supporting advanced PWM and capture/compare.

- 2 x 2-channel Standard Programmable Counter Array (PCAn) supporting PWM and capture/compare.

- 2 x 32-bit Timers can be split into 4 x 16-bit Timers, support PWM and capture/compare.

- Real Time Clock (RTCn).

- Low Power Timer.

- Watchdog Timer.

- Communications Peripherals:

- External Memory Interface.

- 2 x USARTs and 2 x UARTs with IrDA and ISO7816 SmartCard support.

- 3 x SPIs.

- 2 x I2C.

- I<sup>2</sup>S (receive and transmit).

- Analog:

- 2 x 12-Bit Analog-to-Digital Converters (SARADC).

- 2 x 10-Bit Digital-to-Analog Converter (IDAC).

- 16-Channel Capacitance-to-Digital Converter (CAPSENSE).

- 2 x Low-Current Comparators (CMP).

- 1 x Current-to-Voltage Converter (IVC) module with two channels.

#### On-Chip Debugging

With on-chip power-on reset, voltage supply monitor, watchdog timer, and clock oscillator, the SiM3C1xx devices are truly standalone system-on-a-chip solutions. The Flash memory is reprogrammable in-circuit, providing non-

#### 4.1.5. Device Power Modes

The SiM3C1xx devices feature four low power modes in addition to normal operating mode. Several peripherals provide wake up sources for these low power modes, including the Low-Power Timer (LPT0), RTC0 (alarms and oscillator failure notification), Comparator 0, and PMU Pin Wake.

In addition, all peripherals can have their clocks disabled to reduce power consumption whenever a peripheral is not being used using the clock control (CLKCTRL) registers.

#### 4.1.5.1. Normal Mode (Power Mode 0)

Normal Mode is the default mode of the device. The core and peripherals are fully operational, and instructions are executed from flash memory.

#### 4.1.5.2. Power Mode 1

In Power Mode 1 the core and peripherals are fully operational, with instructions executing from RAM. Compared with Normal Mode, the active power consumption of the device in PM1 is reduced. Additionally, at higher speeds in PM1, the core throughput can also be increased because RAM does not require additional wait states that reduce the instruction fetch speed.

#### 4.1.5.3. Power Mode 2

In Power Mode 2 the core halts and any enabled peripherals continue to run at the selected clock speed. The power consumption in PM2 corresponds to the AHB and APB clocks left enabled, thus the power can be tuned to the optimal level for the needs of the application. To place the device in PM2, the core should execute a wait-for-interrupt (WFI) or wait-for-event (WFE) instruction. If the WFI instruction is called from an interrupt service routine, the interrupt that wakes the device from PM2 must be of a sufficient priority to be recognized by the core. It is recommended to perform both a DSB (Data Synchronization Barrier) and an ISB (Instruction Syncronization Barrier) operation prior to the WFI to ensure all bus accesses complete. When operating from the LFOSC0 with the DMACTRL0 AHB clock disabled, PM2 can achieve similar power consumption to PM3, but with the ability to wake on APB-clocked interrupts. For example, enabling only the APB clock to the Ports will allow the firmware to wake on a PMATCH0, PBEXT0 or PBEXT1 interrupt with minimal impact on the supply current.

#### 4.1.5.4. Power Mode 3

In Power Mode 3, the AHB and APB clocks are halted. The device may only wake from enabled interrupt sources which do not require the APB clock (RTC0ALRM, RTC0FAIL, LPTIMER0, VDDLOW and VREGLOW). A special fast wake option allows the device to operate at a very low level from the RTC0TCLK or LFOSC0 oscillator while in PM3, but quickly switch to the faster LPOSC0 when the wake event occurs. Because the current consumption of these blocks is minimal, it is recommended to use the fast wake option.

The device will enter PM3 on a WFI or WFE instruction. Because all AHB master clocks are disabled, the LPOSC will automatically halt and go into a low-power suspended state. If the WFI instruction is called from an interrupt service routine, the interrupt that wakes the device from PM3 must be of a sufficient priority to be recognized by the core. It is recommended to perform both a DSB (Data Synchronization Barrier) and an ISB (Instruction Synchronization Barrier) operation prior to the WFI to ensure all bus access is complete.

#### 4.1.5.5. Power Mode 9

In Power Mode 9, the core and all peripherals are halted, all clocks are stopped, and the pins and peripherals are set to a lower power mode. In addition, standard RAM contents are not preserved, though retention RAM contents are still available after exiting the power mode. This mode provides the lowest power consumption for the device, but requires an appropriate reset to exit. The available reset sources to wake from PM9 are controlled by the Power Management Unit (PMU).

Before entering PM9, the desired reset source(s) should be configured in the PMU. The SLEEPDEEP bit in the ARM System Control Register should be set, and the PMSEL bit in the RSTSRC0\_CONFIG register must be set to indicate that PM9 is the desired power mode.

The device will enter PM9 on a WFI or WFE instruction, and remain in PM9 until a reset configured by the PMU occurs. It is recommended to perform both a DSB (Data Synchronization Barrier) and an ISB (Instruction Synchronization Barrier) operation prior to the WFI to ensure all bus access is complete.

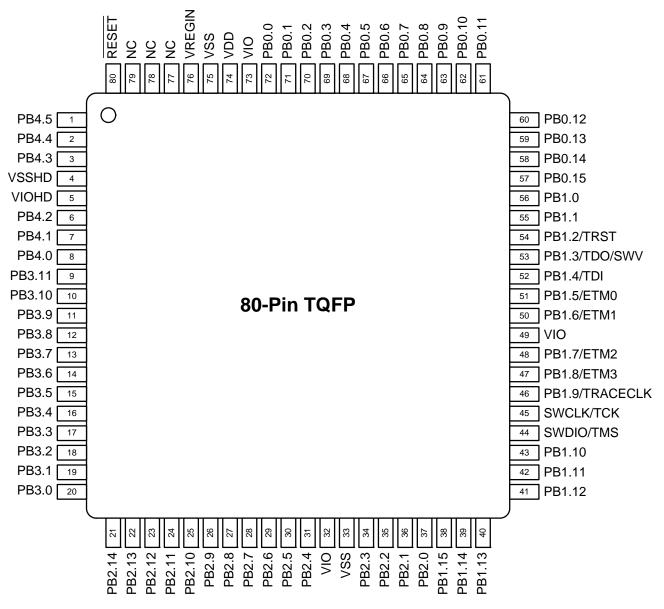

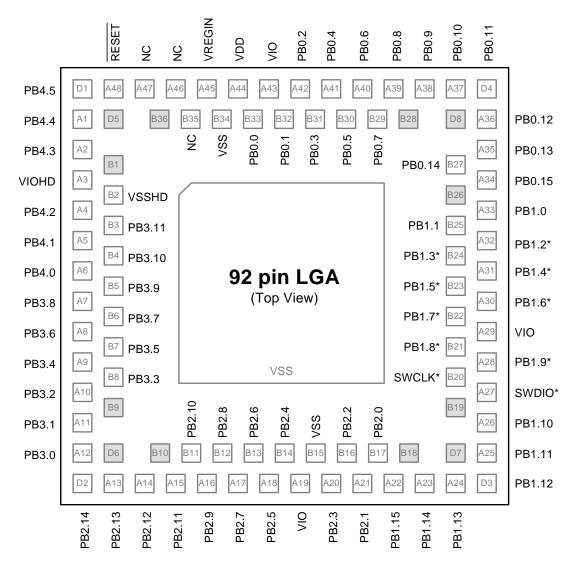

# 6. Pin Definitions and Packaging Information

# 6.1. SiM3C1x7 Pin Definitions

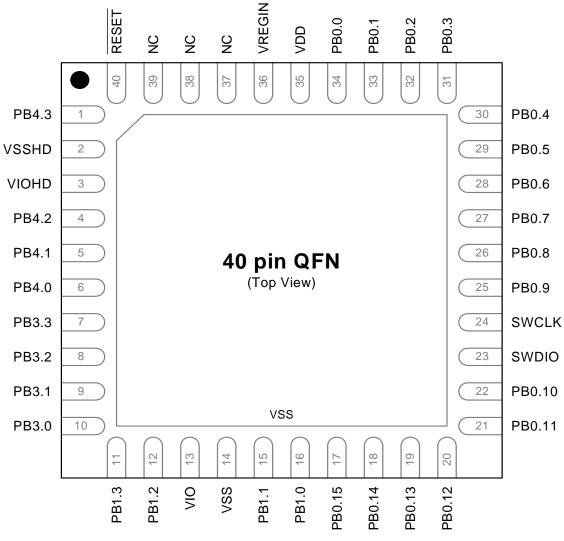

Figure 6.1. SiM3C1x7-GQ Pinout

\*Noted pins are listed in the pinout table and 80-pin TQFP package figure with additional names. These alternate functions are also present on the 92-pin LGA package and are identical to those on the 80-pin TQFP package.

Figure 6.2. SiM3C1x7-GM Pinout

|                   | 1                                         |                     | 1                  |                                                  |              |                                               |                           | 1                   | 1                       |                                   |

|-------------------|-------------------------------------------|---------------------|--------------------|--------------------------------------------------|--------------|-----------------------------------------------|---------------------------|---------------------|-------------------------|-----------------------------------|

| Pin Name          | Туре                                      | Pin Numbers TQFP-80 | Pin Numbers LGA-92 | Crossbar Capability<br>(see Port Config Section) | Port Match   | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs | Analog or Additional<br>Functions |

| PB0.8             | Standard I/O                              | 64                  | A39                | XBR0                                             | ~            |                                               |                           |                     |                         | ADC0.7<br>CS0.7<br>IVC0.1         |

| PB0.9             | Standard I/O                              | 63                  | A38                | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC0.8<br>RTC1                    |

| PB0.10            | Standard I/O                              | 62                  | A37                | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | RTC2                              |

| PB0.11            | Standard I/O                              | 61                  | D4                 | XBR0                                             | ~            |                                               |                           |                     |                         | ADC0.9<br>VREFGND                 |

| PB0.12            | Standard I/O                              | 60                  | A36                | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC0.10<br>VREF                   |

| PB0.13            | Standard I/O                              | 59                  | A35                | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | IDAC0                             |

| PB0.14            | Standard I/O                              | 58                  | B27                | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | IDAC1                             |

| PB0.15            | Standard I/O                              | 57                  | A34                | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | XTAL1                             |

| PB1.0             | Standard I/O                              | 56                  | A33                | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | XTAL2                             |

| PB1.1             | Standard I/O                              | 55                  | B25                | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC0.11                           |

| PB1.2/TRST        | Standard I/O /JTAG                        | 54                  | A32                | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         |                                   |

| PB1.3/TDO/<br>SWV | Standard I/O /JTAG/<br>Serial Wire Viewer | 53                  | B24                | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC0.12<br>ADC1.12                |

| PB1.4/TDI         | Standard I/O /JTAG                        | 52                  | A31                | XBR0                                             | ~            |                                               |                           |                     |                         | ADC0.13<br>ADC1.13                |

| PB1.5/ETM0        | Standard I/O /ETM                         | 51                  | B23                | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC0.14<br>ADC1.14                |

| PB1.6/ETM1        | Standard I/O /ETM                         | 50                  | A30                | XBR0                                             | ~            |                                               |                           |                     |                         | ADC0.15<br>ADC1.15                |

| PB1.7/ETM2        | Standard I/O /ETM                         | 48                  | B22                | XBR0                                             | ~            |                                               |                           |                     |                         | ADC1.11<br>CS0.8                  |

| PB1.8/ETM3        | Standard I/O /ETM                         | 47                  | B21                | XBR0                                             | ~            |                                               |                           |                     |                         | ADC1.10<br>CS0.9                  |

| Table 6.1. Pin Definitions and alternate | e functions for SiM3C1x7 | (Continued) |

|------------------------------------------|--------------------------|-------------|

|------------------------------------------|--------------------------|-------------|

| Dia Nama                       | Toma                      | Pin Numbers TQFP-80 | Pin Numbers LGA-92 | Crossbar Capability<br>(see Port Config Section) | Port Match   | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs    | Analog or Additional<br>Functions |

|--------------------------------|---------------------------|---------------------|--------------------|--------------------------------------------------|--------------|-----------------------------------------------|---------------------------|---------------------|----------------------------|-----------------------------------|

| Pin Name<br>PB1.9/<br>TRACECLK | Type<br>Standard I/O /ETM | <b>ä</b><br>46      | <b>ā</b><br>A28    | <b>ن</b> ق<br>XBR0                               | <u>√</u>     | ά£                                            | Рс                        | õ                   | <u>ش</u>                   | <b>ਪ</b> ਛੋ<br>ADC1.9             |

| PB1.10                         | Standard I/O              | 43                  | A26                | XBR0                                             | ~            | A23m/<br>A15                                  |                           |                     | DMA0T1                     | ADC1.8                            |

| PB1.11                         | Standard I/O              | 42                  | A25                | XBR0                                             | ~            | A22m/<br>A14                                  |                           |                     | DMA0T0                     | ADC1.7                            |

| PB1.12                         | Standard I/O              | 41                  | D3                 | XBR0                                             | ~            | A21m/<br>A13                                  |                           |                     |                            | ADC1.6                            |

| PB1.13                         | Standard I/O              | 40                  | A24                | XBR0                                             | ~            | A20m/<br>A12                                  |                           |                     | ADC0T15<br>WAKE.0          | ADC1.5<br>CS0.10                  |

| PB1.14                         | Standard I/O              | 39                  | A23                | XBR0                                             | ~            | A19m/<br>A11                                  |                           |                     | ADC1T15<br>WAKE.1          | ADC1.4<br>CS0.11                  |

| PB1.15                         | Standard I/O              | 38                  | A22                | XBR0                                             | ~            | A18m/<br>A10                                  |                           |                     | WAKE.2                     | ADC1.3<br>CS0.12                  |

| PB2.0                          | Standard I/O              | 37                  | B17                | XBR1                                             | V            | A17m/<br>A9                                   | LSI0                      | Yes                 | INT0.0<br>INT1.0<br>WAKE.3 | ADC1.2<br>CS0.13                  |

| PB2.1                          | Standard I/O              | 36                  | A21                | XBR1                                             | ~            | A16m/<br>A8                                   | LSI1                      | Yes                 | INT0.1<br>INT1.1<br>WAKE.4 | ADC1.1<br>CS0.14                  |

| PB2.2                          | Standard I/O              | 35                  | B16                | XBR1                                             | ~            | AD15m/<br>A7                                  | LSI2                      | Yes                 | INT0.2<br>INT1.2<br>WAKE.5 | ADC1.0<br>CS0.15<br>PMU_Asleep    |

| PB2.3                          | Standard I/O              | 34                  | A20                | XBR1                                             | ~            | AD14m/<br>A6                                  | LSI3                      | Yes                 | INT0.3<br>INT1.3<br>WAKE.6 |                                   |

| PB2.4                          | Standard I/O              | 31                  | B14                | XBR1                                             | ~            | AD13m/<br>A5                                  | LSI4                      | Yes                 | INT0.4<br>INT1.4<br>WAKE.7 |                                   |

| PB2.5                          | Standard I/O              | 30                  | A18                | XBR1                                             | $\checkmark$ | AD12m /<br>A4                                 | LSI5                      | Yes                 | INT0.5<br>INT1.5           |                                   |

| Pin Name | Туре             | Pin Numbers | Crossbar Capability<br>(see Port Config Section) | Port Match | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs                                     | Analog or Additional<br>Functions |

|----------|------------------|-------------|--------------------------------------------------|------------|-----------------------------------------------|---------------------------|---------------------|-------------------------------------------------------------|-----------------------------------|

| PB3.9    | 5 V Tolerant I/O | 7           | XBR1                                             | ~          | BE0                                           |                           |                     | DAC0T6<br>DAC1T6<br>LPT0T2<br>INT0.10<br>INT1.10<br>WAKE.15 | CMP0N.5<br>CMP1N.5<br>EXREGBD     |

| PB4.0    | High Drive I/O   | 6           |                                                  |            |                                               | LSO0                      |                     |                                                             |                                   |

| PB4.1    | High Drive I/O   | 5           |                                                  |            |                                               | LSO1                      |                     |                                                             |                                   |

| PB4.2    | High Drive I/O   | 4           |                                                  |            |                                               | LSO2                      |                     |                                                             |                                   |

| PB4.3    | High Drive I/O   | 1           |                                                  |            |                                               | LSO3                      |                     |                                                             |                                   |

Table 6.2. Pin Definitions and alternate functions for SiM3C1x6 (Continued)

# SiM3C1xx

# 6.3. SiM3C1x4 Pin Definitions

Figure 6.5. SiM3C1x4-GM Pinout

#### 6.4.1. LGA-92 Solder Mask Design

All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60  $\mu$ m minimum, all the way around the pad.

#### 6.4.2. LGA-92 Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

- 4. A 2 x 2 array of 1.25 mm square openings on 1.60 mm pitch should be used for the center ground pad.

#### 6.4.3. LGA-92 Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### 6.5.1. TQFP-80 Solder Mask Design

All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

#### 6.5.2. TQFP-80 Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all pads.

#### 6.5.3. TQFP-80 Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

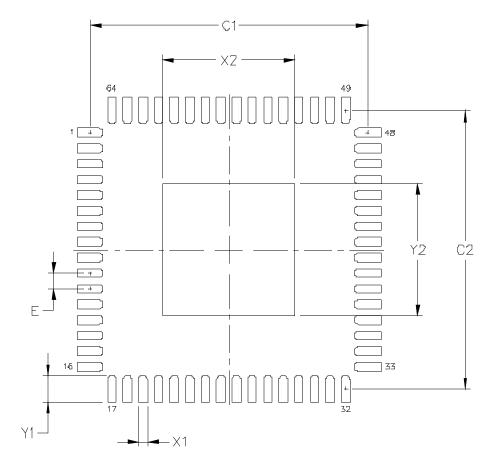

#### Figure 6.11. QFN-64 Landing Diagram

| Dimension | mm   |  |  |

|-----------|------|--|--|

| C1        | 8.90 |  |  |

| C2        | 8.90 |  |  |

| E         | 0.50 |  |  |

| X1        | 0.30 |  |  |

| Y1        | 0.85 |  |  |

| X2        | 4.25 |  |  |

| Y2        | 4.25 |  |  |

| Notes:    |      |  |  |

### Table 6.9. QFN-64 Landing Diagram Dimensions

- 1. All dimensions shown are in millimeters (mm).

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

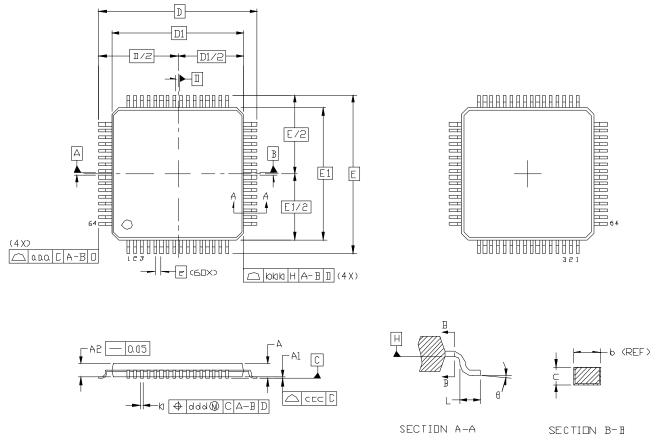

# 6.7. TQFP-64 Package Specifications

Figure 6.12. TQFP-64 Package Drawing

| Dimension | Min       | Nominal | Max  |  |  |

|-----------|-----------|---------|------|--|--|

| A         | —         | _       | 1.20 |  |  |

| A1        | 0.05      | _       | 0.15 |  |  |

| A2        | 0.95      | 1.00    | 1.05 |  |  |

| b         | 0.17      | 0.22    | 0.27 |  |  |

| с         | 0.09      | —       | 0.20 |  |  |

| D         | 12.00 BSC |         |      |  |  |

| D1        | 10.00 BSC |         |      |  |  |

| е         | 0.50 BSC  |         |      |  |  |

| E         | 12.00 BSC |         |      |  |  |

| E1        | 10.00 BSC |         |      |  |  |

| L         | 0.45      | 0.60    | 0.75 |  |  |

| Θ         | 0°        | 3.5°    | 7°   |  |  |

### Table 6.10. TQFP-64 Package Dimensions

| Dimension                                                                                                                                                                                                                                                                                                                                                                      | Min | Nominal | Мах  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|--|--|

| aaa                                                                                                                                                                                                                                                                                                                                                                            |     | _       | 0.20 |  |  |

| bbb                                                                                                                                                                                                                                                                                                                                                                            |     | _       | 0.20 |  |  |

| ccc                                                                                                                                                                                                                                                                                                                                                                            |     | _       | 0.08 |  |  |

| ddd                                                                                                                                                                                                                                                                                                                                                                            |     |         | 0.08 |  |  |

| <ol> <li>Notes:         <ol> <li>All dimensions shown are in millimeters (mm) unless otherwise noted.</li> <li>Dimensioning and Tolerancing per ANSI Y14.5M-1994.</li> <li>This package outline conforms to JEDEC MS-026, variant ACD.</li> <li>Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.</li> </ol> </li> </ol> |     |         |      |  |  |

Table 6.10. TQFP-64 Package Dimensions (Continued)

SILICON LABS

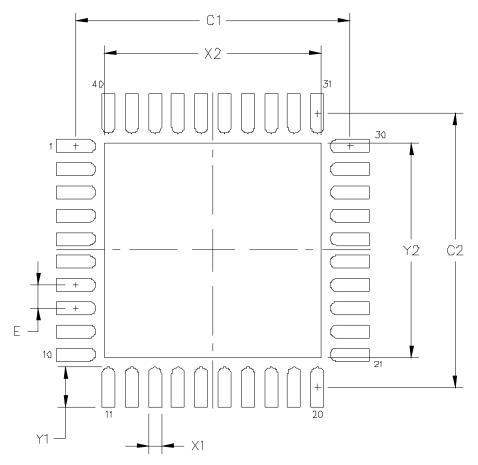

Figure 6.15. QFN-40 Landing Diagram

| Dimension | mm   |  |  |

|-----------|------|--|--|

| C1        | 5.90 |  |  |

| C2        | 5.90 |  |  |

| E         | 0.50 |  |  |

| X1        | 0.30 |  |  |

| Y1        | 0.85 |  |  |

| X2        | 4.65 |  |  |

| Y2        | 4.65 |  |  |

| Notos     |      |  |  |

### Table 6.13. QFN-40 Landing Diagram Dimensions

Notes:

- 1. All dimensions shown are in millimeters (mm).

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- **3.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a

- Fabrication Allowance of 0.05 mm.