# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                 |

| Core Size                  | 32-Bit Single-Core                                              |

| Speed                      | 80MHz                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT    |

| Number of I/O              | 50                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 32K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 28x12b; D/A 2x10b                                           |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/sim3c166-b-gm |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

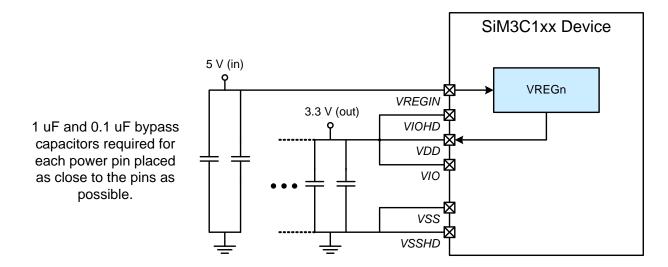

# 2. Typical Connection Diagrams

This section provides typical connection diagrams for SiM3C1xx devices.

# 2.1. Power

Figure 2.1 shows a typical connection diagram for the power pins of the SiM3C1xx devices when the internal regulator is in use.

Figure 2.1. Connection Diagram with Voltage Regulator Used

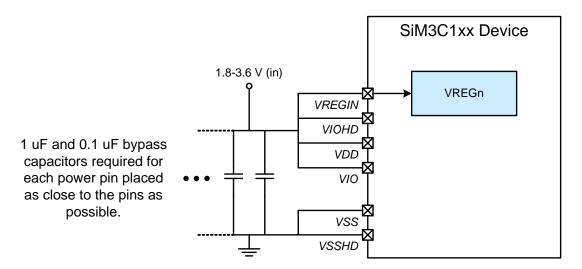

Figure 2.2 shows a typical connection diagram for the power pins of the SiM3C1xx devices when the internal regulator is not used.

Figure 2.2. Connection Diagram with Voltage Regulator Not Used

# 3. Electrical Specifications

# 3.1. Electrical Characteristics

All electrical parameters in all tables are specified under the conditions listed in Table 3.1, unless stated otherwise.

Table 3.1. Recommended Operating Conditions

| Parameter                                         | Symbol             | Test Condition                       | Min               | Тур | Max                                                              | Unit |

|---------------------------------------------------|--------------------|--------------------------------------|-------------------|-----|------------------------------------------------------------------|------|

| Operating Supply Voltage on VDD                   | V <sub>DD</sub>    |                                      | 1.8               |     | 3.6                                                              | V    |

| Operating Supply Voltage on VREGIN                | V <sub>REGIN</sub> | EXTVREG0 Not Used                    | 4                 | _   | 5.5                                                              | V    |

|                                                   |                    | EXTVREG0 Used                        | 3.0               |     | 3.6                                                              | V    |

| Operating Supply Voltage on VIO                   | V <sub>IO</sub>    |                                      | 1.8               | —   | V <sub>DD</sub>                                                  | V    |

| Operating Supply Voltage on VIOHD                 | V <sub>IOHD</sub>  | HV Mode (default)                    | 2.7               | —   | 6.0                                                              | V    |

|                                                   |                    | LV Mode                              | 1.8               |     | 3.6                                                              | V    |

| Voltage on I/O pins, Port Bank 0, 1<br>and 2 I/O  | V <sub>IN</sub>    |                                      | V <sub>SS</sub>   | —   | V <sub>IO</sub>                                                  | V    |

| Voltage on I/O pins, Port Bank 3 I/O<br>and RESET | V <sub>IN</sub>    | SiM3C1x7<br>PB3.0–PB3.7 and<br>RESET | V <sub>SS</sub>   | —   | V <sub>IO</sub> +2.0                                             | V    |

|                                                   |                    | SiM3C1x7<br>PB3.8 - PB3.11           | V <sub>SS</sub>   | _   | Lowest<br>of<br>V <sub>IO</sub> +2.0<br>or<br>V <sub>REGIN</sub> | V    |

|                                                   |                    | SiM3C1x6<br>PB3.0–PB3.5 and<br>RESET | V <sub>SS</sub>   | _   | V <sub>IO</sub> +2.0                                             | V    |

|                                                   |                    | SiM3C1x6<br>PB3.6–PB3.9              | V <sub>SS</sub>   | _   | Lowest<br>of<br>V <sub>IO</sub> +2.0<br>or<br>V <sub>REGIN</sub> | V    |

|                                                   |                    | SiM3C1x4<br>RESET                    | V <sub>SS</sub>   | _   | V <sub>IO</sub> +2.0                                             | V    |

|                                                   |                    | SiM3C1x4<br>PB3.0–PB3.3              | V <sub>SS</sub>   | _   | Lowest<br>of<br>V <sub>IO</sub> +2.0<br>or<br>V <sub>REGIN</sub> | V    |

| Voltage on I/O pins, Port Bank 4 I/O              | V <sub>IN</sub>    |                                      | V <sub>SSHD</sub> |     | V <sub>IOHD</sub>                                                | V    |

| System Clock Frequency (AHB)                      | f <sub>AHB</sub>   |                                      | 0                 |     | 80                                                               | MHz  |

| Peripheral Clock Frequency (APB)                  | f <sub>APB</sub>   |                                      | 0                 |     | 50                                                               | MHz  |

| Operating Ambient Temperature                     | T <sub>A</sub>     |                                      | -40               |     | 85                                                               | °C   |

| Operating Junction Temperature                    | TJ                 |                                      | -40               |     | 105                                                              | °C   |

| Note: All voltages with respect to $V_{SS}$ .     | <u> </u>           | ,                                    | ıl                |     | ļ.                                                               |      |

# Table 3.2. Power Consumption

| Parameter                                                                                            | Symbol          | Test Condition                                          | Min | Тур  | Max  | Unit |

|------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------|-----|------|------|------|

| Digital Core Supply Current                                                                          |                 |                                                         | -   | 1    | L    | 1    |

| Normal Mode <sup>2,3,4,5</sup> —Full speed<br>with code executing from Flash,                        | I <sub>DD</sub> | F <sub>AHB</sub> = 80 MHz,<br>F <sub>APB</sub> = 40 MHz | —   | 33   | 36.5 | mA   |

| peripheral clocks ON                                                                                 |                 | $F_{AHB} = F_{APB} = 20 \text{ MHz}$                    | _   | 10.5 | 13.3 | mA   |

|                                                                                                      |                 | F <sub>AHB</sub> = F <sub>APB</sub> = 2.5 MHz           | _   | 2.0  | 3.8  | mA   |

| Normal Mode <sup>2,3,4,5</sup> —Full speed<br>with code executing from Flash,                        | I <sub>DD</sub> | F <sub>AHB</sub> = 80 MHz,<br>F <sub>APB</sub> = 40 MHz | —   | 22   | 24.9 | mA   |

| peripheral clocks OFF                                                                                |                 | F <sub>AHB</sub> = F <sub>APB</sub> = 20 MHz            | _   | 7.8  | 10   | mA   |

|                                                                                                      |                 | F <sub>AHB</sub> = F <sub>APB</sub> = 2.5 MHz           | _   | 1.2  | 3    | mA   |

| Power Mode 1 <sup>2,3,4,6</sup> —Full speed<br>with code executing from RAM,<br>peripheral clocks ON | I <sub>DD</sub> | F <sub>AHB</sub> = 80 MHz,<br>F <sub>APB</sub> = 40 MHz | —   | 30.5 | 35.5 | mA   |

|                                                                                                      |                 | $F_{AHB} = F_{APB} = 20 \text{ MHz}$                    | _   | 8.5  | _    | mA   |

|                                                                                                      |                 | F <sub>AHB</sub> = F <sub>APB</sub> = 2.5 MHz           | —   | 1.7  | —    | mA   |

| Power Mode 1 <sup>2,3,4,6</sup> —Full speed<br>with code executing from RAM,                         | I <sub>DD</sub> | F <sub>AHB</sub> = 80 MHz,<br>F <sub>APB</sub> = 40 MHz | _   | 20   | 23   | mA   |

| peripheral clocks OFF                                                                                |                 | F <sub>AHB</sub> = F <sub>APB</sub> = 20 MHz            |     | 5.3  | —    | mA   |

|                                                                                                      |                 | F <sub>AHB</sub> = F <sub>APB</sub> = 2.5 MHz           | _   | 1.0  | —    | mA   |

| Power Mode 2 <sup>2,3,4</sup> —Core halted with peripheral clocks ON                                 | I <sub>DD</sub> | F <sub>AHB</sub> = 80 MHz,<br>F <sub>APB</sub> = 40 MHz | —   | 19   | 22   | mA   |

|                                                                                                      |                 | $F_{AHB} = F_{APB} = 20 \text{ MHz}$                    | _   | 7.8  | —    | mA   |

|                                                                                                      |                 | F <sub>AHB</sub> = F <sub>APB</sub> = 2.5 MHz           | _   | 1.3  | _    | mA   |

| Power Mode 3 <sup>2,3</sup>                                                                          | I <sub>DD</sub> | $V_{DD}$ = 1.8 V, $T_A$ = 25 °C                         | _   | 175  | _    | μA   |

|                                                                                                      |                 | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C         | _   | 250  | _    | μA   |

Notes:

1. Perhipheral currents drop to zero when peripheral clock and peripheral are disabled, unless otherwise noted.

2. Currents are additive. For example, where  $I_{DD}$  is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

3. Includes all peripherals that cannot have clocks gated in the Clock Control module.

4. Includes supply current from internal regulator and PLL0OSC (>20 MHz) or LPOSC0 (<=20 MHz).

5. Flash execution numbers use 2 wait states for 80 MHz and 0 wait states at 20 MHz or less.

6. RAM execution numbers use 0 wait states for all frequencies.

7. IDAC output current and IVC input current not included.

8. Bias current only. Does not include dynamic current from oscillator running at speed.

# Table 3.2. Power Consumption (Continued)

| Parameter                                                                      | Symbol              | Test Condition                                                                 | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------|-----|-----|-----|------|

| Power Mode 9 <sup>2,3</sup> —Low Power<br>Shutdown with VREG0 disabled,        | I <sub>DD</sub>     | RTC Disabled,<br>V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 25 °C               | _   | 85  | _   | nA   |

| powered through VDD and VIO                                                    |                     | RTC w/ 16.4 kHz LFO,<br>V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 25 °C        |     | 350 |     | nA   |

|                                                                                |                     | RTC w/ 32.768 kHz Crystal,<br>V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 25 °C  | _   | 620 |     | nA   |

|                                                                                |                     | RTC Disabled,<br>$V_{DD} = 3.0 \text{ V}, \text{ T}_{A} = 25 ^{\circ}\text{C}$ | _   | 145 |     | nA   |

|                                                                                |                     | RTC w/ 16.4 kHz LFO,<br>V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C        |     | 500 | _   | nA   |

|                                                                                |                     | RTC w/ 32.768 kHz Crystal,<br>V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C  |     | 800 | _   | nA   |

| Power Mode 9 <sup>2,3</sup> —Low Power<br>Shutdown with VREG0 in low-          | I <sub>VREGIN</sub> | RTC Disabled,<br>VREGIN = 5 V, T <sub>A</sub> = 25 °C                          |     | 300 | _   | nA   |

| power mode, VDD and VIO pow-<br>ered through VREG0 (Includes<br>VREG0 current) |                     | RTC w/ 16.4 kHz LFO,<br>VREGIN = 5 V, T <sub>A</sub> = 25 °C                   | _   | 650 |     | nA   |

|                                                                                |                     | RTC w/ 32.768 kHz Crystal,<br>VREGIN = 5 V, T <sub>A</sub> = 25 °C             | _   | 950 |     | nA   |

| VIOHD Current (High-drive I/O dis-                                             | I <sub>VIOHD</sub>  | HV Mode (default)                                                              | _   | 2.5 | 5   | μA   |

| abled)                                                                         |                     | LV Mode                                                                        |     | 2   | —   | nA   |

Notes:

1. Perhipheral currents drop to zero when peripheral clock and peripheral are disabled, unless otherwise noted.

Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

3. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 4. Includes supply current from internal regulator and PLL0OSC (>20 MHz) or LPOSC0 (<=20 MHz).

- 5. Flash execution numbers use 2 wait states for 80 MHz and 0 wait states at 20 MHz or less.

- 6. RAM execution numbers use 0 wait states for all frequencies.

- 7. IDAC output current and IVC input current not included.

8. Bias current only. Does not include dynamic current from oscillator running at speed.

# Table 3.2. Power Consumption (Continued)

| Parameter                                  | Symbol              | Test Condition                                    | Min | Тур | Max | Unit |

|--------------------------------------------|---------------------|---------------------------------------------------|-----|-----|-----|------|

| External Oscillator (EXTOSC0) <sup>8</sup> | I <sub>EXTOSC</sub> | FREQCN = 111                                      |     | 3.8 | 4.7 | mA   |

|                                            |                     | FREQCN = 110                                      |     | 840 | 950 | μA   |

|                                            |                     | FREQCN = 101                                      |     | 185 | 220 | μA   |

|                                            |                     | FREQCN = 100                                      |     | 65  | 80  | μA   |

|                                            |                     | FREQCN = 011                                      |     | 25  | 30  | μA   |

|                                            |                     | FREQCN = 010                                      | _   | 10  | 15  | μA   |

|                                            |                     | FREQCN = 001                                      |     | 5   | 10  | μA   |

|                                            |                     | FREQCN = 000                                      |     | 3   | 8   | μA   |

| SARADC0,<br>SARADC1                        | ISARADC             | Sampling at 1 Msps, highest power mode settings.  |     | 1.2 | 1.5 | mA   |

|                                            |                     | Sampling at 250 ksps, lowest power mode settings. |     | 390 | 510 | μA   |

| Temperature Sensor                         | I <sub>TSENSE</sub> |                                                   |     | 75  | 105 | μA   |

| Internal SAR Reference                     | I <sub>REFFS</sub>  | Normal Power Mode                                 |     | 680 | 750 | μA   |

|                                            |                     | Low Power Mode                                    |     | 160 | 190 | μA   |

| VREF0                                      | I <sub>REFP</sub>   |                                                   |     | 75  | 100 | μA   |

| Comparator 0 (CMP0),                       | I <sub>CMP</sub>    | CMPMD = 11                                        |     | 0.5 | —   | μA   |

| Comparator 1 (CMP1)                        |                     | CMPMD = 10                                        |     | 3   | _   | μA   |

|                                            |                     | CMPMD = 01                                        | —   | 10  | —   | μA   |

|                                            |                     | CMPMD = 00                                        | —   | 25  | —   | μA   |

| Capacitive Sensing (CAPSENSE0)             | I <sub>CS</sub>     | Continuous Conversions                            |     | 55  | 80  | μA   |

| IDAC0 <sup>7</sup> ,<br>IDAC1 <sup>7</sup> | I <sub>IDAC</sub>   |                                                   | —   | 75  | 90  | μA   |

| IVC0 <sup>7</sup>                          | I <sub>IVC</sub>    | I <sub>IN</sub> = 0                               | _   | 1.5 | 2.5 | μA   |

| Voltage Supply Monitor (VMON0)             | I <sub>VMON</sub>   |                                                   | _   | 15  | 25  | μA   |

Notes:

1. Perhipheral currents drop to zero when peripheral clock and peripheral are disabled, unless otherwise noted.

Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

- 3. Includes all peripherals that cannot have clocks gated in the Clock Control module.

- 4. Includes supply current from internal regulator and PLL0OSC (>20 MHz) or LPOSC0 (<=20 MHz).

- 5. Flash execution numbers use 2 wait states for 80 MHz and 0 wait states at 20 MHz or less.

- 6. RAM execution numbers use 0 wait states for all frequencies.

- 7. IDAC output current and IVC input current not included.

- 8. Bias current only. Does not include dynamic current from oscillator running at speed.

# Table 3.7. Flash Memory

| Parameter                                  | Symbol             | Test Condition                    | Min | Тур  | Max | Unit   |

|--------------------------------------------|--------------------|-----------------------------------|-----|------|-----|--------|

| Write Time <sup>1</sup>                    | t <sub>WRITE</sub> | One 16-bit Half Word              | 20  | 21   | 22  | μs     |

| Erase Time <sup>1</sup>                    | t <sub>ERASE</sub> | One Page                          | 20  | 21   | 22  | ms     |

|                                            | t <sub>ERALL</sub> | Full Device                       | 20  | 21   | 22  | ms     |

| V <sub>DD</sub> Voltage During Programming | V <sub>PROG</sub>  |                                   | 1.8 | _    | 3.6 | V      |

| Endurance (Write/Erase Cycles)             | N <sub>WE</sub>    |                                   | 20k | 100k | —   | Cycles |

| Retention <sup>2</sup>                     | t <sub>RET</sub>   | T <sub>A</sub> = 25 °C, 1k Cycles | 10  | 100  |     | Years  |

Notes:

1. Does not include sequencing time before and after the write/erase operation, which may take up to 35 µs. During a sequential write operation, this extra time is only taken prior to the first write and after the last write.

2. Additional Data Retention Information is published in the Quarterly Quality and Reliability Report.

# Table 3.8. Internal Oscillators

| Parameter                            | Symbol                 | Test Condition                                                                             | Min | Тур | Max | Unit   |

|--------------------------------------|------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| Phase-Locked Loop (PLL0OSC)          |                        |                                                                                            |     |     | 1   |        |

| Calibrated Output Frequency*         | f <sub>PLL0OSC</sub>   | Full Temperature and<br>Supply Range                                                       | 77  | 79  | 80  | MHz    |

| Power Supply Sensitivity*            | PSS <sub>PLL0OSC</sub> | T <sub>A</sub> = 25 °C,<br>Fout = 79 MHz                                                   | —   | 430 | _   | ppm/V  |

| Temperature Sensitivity*             | TS <sub>PLL0OSC</sub>  | V <sub>DD</sub> = 3.3 V,<br>Fout = 79 MHz                                                  | —   | 95  | _   | ppm/°C |

| Adjustable Output Frequency<br>Range | f <sub>PLL0OSC</sub>   |                                                                                            | 23  | _   | 80  | MHz    |

| Lock Time                            | t <sub>PLLOLOCK</sub>  | f <sub>REF</sub> = 20 MHz,<br>f <sub>PLL0OSC</sub> = 80 MHz,<br>M=24, N=99,<br>LOCKTH = 0  | _   | 1.7 |     | μs     |

|                                      |                        | f <sub>REF</sub> = 32 kHz,<br>f <sub>PLL0OSC</sub> = 80 MHz,<br>M=0, N=2440,<br>LOCKTH = 0 | _   | 91  |     | μs     |

| *Note: PLL0OSC in free-running osc   | illator mode.          |                                                                                            |     |     |     |        |

# Table 3.17. Port I/O

| Parameter                                                                          | Symbol          | Test Condition                                                                                  | Min                     | Тур  | Max | Unit |

|------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------|-------------------------|------|-----|------|

| Standard I/O (PB0, PB1, and PB                                                     | 32), 5 V Tole   | rant I/O (PB3), and RESE                                                                        | Т                       |      |     | 4    |

| Output High Voltage*                                                               | V <sub>OH</sub> | Low Drive, I <sub>OH</sub> = -2 mA                                                              | V <sub>IO</sub> – 0.7   | _    | _   | V    |

|                                                                                    |                 | High Drive, $I_{OH} = -5 \text{ mA}$                                                            | V <sub>IO</sub> – 0.7   | _    |     | V    |

| Output Low Voltage*                                                                | V <sub>OL</sub> | Low Drive, I <sub>OL</sub> = 3 mA                                                               | —                       | _    | 0.6 | V    |

|                                                                                    |                 | High Drive,<br>I <sub>OL</sub> = 12.5 mA                                                        | —                       |      | 0.6 | V    |

| nput High Voltage                                                                  | V <sub>IH</sub> | 1.8 <u>&lt;</u> V <sub>IO</sub> <u>&lt;</u> 2.0                                                 | 0.7 x V <sub>IO</sub>   | _    | _   | V    |

|                                                                                    |                 | 2.0 <u>&lt;</u> V <sub>IO</sub> <u>&lt;</u> 3.6                                                 | V <sub>IO</sub> – 0.6   |      |     | V    |

| nput Low Voltage                                                                   | VIL             |                                                                                                 | —                       | _    | 0.6 | V    |

| Pin Capacitance                                                                    | C <sub>IO</sub> | PB0, PB1 and PB2 Pins                                                                           | _                       | 4    | _   | pF   |

|                                                                                    |                 | PB3 Pins                                                                                        | —                       | 7    |     | pF   |

| Weak Pull-Up Current                                                               | I <sub>PU</sub> | V <sub>IO</sub> = 1.8                                                                           | -6                      | -3.5 | -2  | μA   |

| (Input Voltage = 0 V)                                                              |                 | V <sub>IO</sub> = 3.6                                                                           | -30                     | -20  | -10 | μA   |

| nput Leakage<br>(Pullups off or Analog)                                            | I <sub>LK</sub> | $0 \le V_{IN} \le V_{IO}$                                                                       | -1                      | —    | 1   | μA   |

| Input Leakage Current of Port<br>Bank 3 I/O, V <sub>IN</sub> above V <sub>IO</sub> | ١L              | V <sub>IO</sub> < V <sub>IN</sub> < V <sub>IO</sub> +2.0 V<br>(pins without EXREG<br>functions) | 0                       | 5    | 150 | μA   |

|                                                                                    |                 | V <sub>IO</sub> < V <sub>IN</sub> < V <sub>REGIN</sub><br>(pins with EXREG<br>functions)        | 0                       | 5    | 150 | μA   |

| High Drive I/O (PB4)                                                               |                 |                                                                                                 | I I                     |      |     | I    |

| Output High Voltage                                                                | V <sub>OH</sub> | Standard Mode, Low<br>Drive, I <sub>OH</sub> = −3 mA                                            | V <sub>IOHD</sub> – 0.7 | —    |     | V    |

|                                                                                    |                 | Standard Mode, High<br>Drive, I <sub>OH</sub> = -10 mA                                          | V <sub>IOHD</sub> – 0.7 | _    |     | V    |

| Output Low Voltage                                                                 | V <sub>OL</sub> | Standard Mode, Low<br>Drive, I <sub>OH</sub> = 3 mA                                             | —                       | —    | 0.6 | V    |

|                                                                                    |                 | Standard Mode, High<br>Drive, I <sub>OH</sub> = 12.5 mA                                         | —                       | —    | 0.6 | V    |

| Output Rise Time                                                                   | t <sub>R</sub>  | Slew Rate Mode 0,<br>V <sub>IOHD</sub> = 5 V                                                    | _                       | 50   | _   | ns   |

|                                                                                    |                 | Slew Rate Mode 1,<br>V <sub>IOHD</sub> = 5 V                                                    | —                       | 300  |     | ns   |

|                                                                                    |                 | Slew Rate Mode 2,<br>V <sub>IOHD</sub> = 5 V                                                    | —                       | 1    |     | μs   |

|                                                                                    |                 | Slew Rate Mode 3,<br>V <sub>IOHD</sub> = 5 V                                                    | —                       | 3    | _   | μs   |

volatile data storage and allowing field upgrades of the firmware. User firmware has complete control of all peripherals and may individually shut down and gate the clocks of any or all peripherals for power savings.

The on-chip debugging interface (SWJ-DP) allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging.

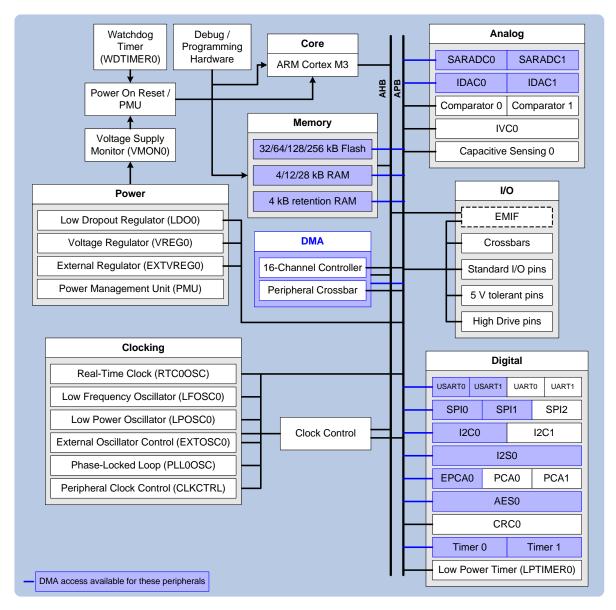

Each device is specified for 1.8 to 3.6 V operation over the industrial temperature range (-40 to +85 °C). The Port I/O and RESET pins are powered from the IO supply voltage. The SiM3C1xx devices are available in 40-pin or 64-pin QFN, 64-pin or 80-pin TQFP, or 92-pin LGA packages. All package options are lead-free and RoHS compliant. See Table 5.1 for ordering information. A block diagram is included in Figure 4.1.

Figure 4.1. Precision32<sup>™</sup> SiM3C1xx Family Block Diagram

## 4.1.5. Device Power Modes

The SiM3C1xx devices feature four low power modes in addition to normal operating mode. Several peripherals provide wake up sources for these low power modes, including the Low-Power Timer (LPT0), RTC0 (alarms and oscillator failure notification), Comparator 0, and PMU Pin Wake.

In addition, all peripherals can have their clocks disabled to reduce power consumption whenever a peripheral is not being used using the clock control (CLKCTRL) registers.

#### 4.1.5.1. Normal Mode (Power Mode 0)

Normal Mode is the default mode of the device. The core and peripherals are fully operational, and instructions are executed from flash memory.

#### 4.1.5.2. Power Mode 1

In Power Mode 1 the core and peripherals are fully operational, with instructions executing from RAM. Compared with Normal Mode, the active power consumption of the device in PM1 is reduced. Additionally, at higher speeds in PM1, the core throughput can also be increased because RAM does not require additional wait states that reduce the instruction fetch speed.

#### 4.1.5.3. Power Mode 2

In Power Mode 2 the core halts and any enabled peripherals continue to run at the selected clock speed. The power consumption in PM2 corresponds to the AHB and APB clocks left enabled, thus the power can be tuned to the optimal level for the needs of the application. To place the device in PM2, the core should execute a wait-for-interrupt (WFI) or wait-for-event (WFE) instruction. If the WFI instruction is called from an interrupt service routine, the interrupt that wakes the device from PM2 must be of a sufficient priority to be recognized by the core. It is recommended to perform both a DSB (Data Synchronization Barrier) and an ISB (Instruction Syncronization Barrier) operation prior to the WFI to ensure all bus accesses complete. When operating from the LFOSC0 with the DMACTRL0 AHB clock disabled, PM2 can achieve similar power consumption to PM3, but with the ability to wake on APB-clocked interrupts. For example, enabling only the APB clock to the Ports will allow the firmware to wake on a PMATCH0, PBEXT0 or PBEXT1 interrupt with minimal impact on the supply current.

#### 4.1.5.4. Power Mode 3

In Power Mode 3, the AHB and APB clocks are halted. The device may only wake from enabled interrupt sources which do not require the APB clock (RTC0ALRM, RTC0FAIL, LPTIMER0, VDDLOW and VREGLOW). A special fast wake option allows the device to operate at a very low level from the RTC0TCLK or LFOSC0 oscillator while in PM3, but quickly switch to the faster LPOSC0 when the wake event occurs. Because the current consumption of these blocks is minimal, it is recommended to use the fast wake option.

The device will enter PM3 on a WFI or WFE instruction. Because all AHB master clocks are disabled, the LPOSC will automatically halt and go into a low-power suspended state. If the WFI instruction is called from an interrupt service routine, the interrupt that wakes the device from PM3 must be of a sufficient priority to be recognized by the core. It is recommended to perform both a DSB (Data Synchronization Barrier) and an ISB (Instruction Synchronization Barrier) operation prior to the WFI to ensure all bus access is complete.

#### 4.1.5.5. Power Mode 9

In Power Mode 9, the core and all peripherals are halted, all clocks are stopped, and the pins and peripherals are set to a lower power mode. In addition, standard RAM contents are not preserved, though retention RAM contents are still available after exiting the power mode. This mode provides the lowest power consumption for the device, but requires an appropriate reset to exit. The available reset sources to wake from PM9 are controlled by the Power Management Unit (PMU).

Before entering PM9, the desired reset source(s) should be configured in the PMU. The SLEEPDEEP bit in the ARM System Control Register should be set, and the PMSEL bit in the RSTSRC0\_CONFIG register must be set to indicate that PM9 is the desired power mode.

The device will enter PM9 on a WFI or WFE instruction, and remain in PM9 until a reset configured by the PMU occurs. It is recommended to perform both a DSB (Data Synchronization Barrier) and an ISB (Instruction Synchronization Barrier) operation prior to the WFI to ensure all bus access is complete.

# 4.2. I/O

# 4.2.1. General Features

The SiM3C1xx ports have the following features:

- Push-pull or open-drain output modes and analog or digital modes.

- Option for high or low output drive strength.

- Port Match allows the device to recognize a change on a port pin value.

- Internal pull-up resistors are enabled or disabled on a port-by-port basis.

- Two external interrupts with up to 16 inputs provide monitoring capability for external signals.

- Internal Pulse Generator Timer (PB2 only) to generate simple square waves.

- A subset of pins can also serve as inputs to the Port Mapped Level Shifters available on the High Drive Pins.

# 4.2.2. High Drive Pins (PB4)

The High Drive pins have the following additional features:

- Programmable safe state: high, low, or high impedance.

- Programmable drive strength and slew rates.

- Programmable hardware current limiting.

- Powered from a separate source (VIOHD, which can be up to 6 V) from the rest of the device.

- Supports various functions, including GPIO, UART1 pins, EPCA0 pins, or Port Mapped Level Shifting.

# 4.2.3. 5 V Tolerant Pins (PB3)

The 5 V tolerant pins can be connected to external circuitry operating at voltages above the device supply without needing extra components to shift the voltage level.

## 4.2.4. Crossbars

The SiM3C1xx devices have two Crossbars with the following features:

- Flexible peripheral assignment to port pins.

- Pins can be individually skipped to move peripherals as needed for design or layout considerations.

The Crossbars have a fixed priority for each I/O function and assign these functions to the port pins. When a digital resource is selected, the least-significant unassigned port pin is assigned to that resource. If a port pin is assigned, the Crossbars skip that pin when assigning the next selected resource. Additionally, the Crossbars will skip port pins whose associated bits in the PBSKIPEN registers are set. This provides some flexibility when designing a system: pins involved with sensitive analog measurements can be moved away from digital I/O and peripherals can be moved around the chip as needed to ease layout constraints.

• Spike suppression up to 2 times the APB period.

# 4.6.6. I<sup>2</sup>S (I2S0)

The I<sup>2</sup>S module receives digital data from an external source over a data line in the standard I<sup>2</sup>S, left-justified, rightjustified, or time domain multiplexing format, de-serializes the data, and generates requests to transfer the data using the DMA. The module also reads stereo audio samples from the DMA, serializes the data, and sends it out of the chip on a data line in the same standard serial format for digital audio. The I<sup>2</sup>S receive interface consists of 3 signals: SCK (bit clock), WS (word select or frame sync), and SD (data input). The block's transmit interface consists of 3 signals: SCK (bit clock), WS (word select or frame sync) and SD (data output).

The I<sup>2</sup>S module includes the following features:

- Master or slave capability.

- Flexible 10-bit clock divider with 8-bit fractional clock divider provides support for various common sampling frequencies (16 kHz, 22.05 kHz, 24 kHz, 32 kHz, 44.1 kHz, and 48 kHz) for up to two 32-bit channels.

- Support for DMA data transfers.

- Support for various data formats.

- Time Division Multiplexing

| Pin Name | Туре             | Pin Numbers | Crossbar Capability<br>(see Port Config Section) | Port Match            | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs | Analog or Additional<br>Functions  |

|----------|------------------|-------------|--------------------------------------------------|-----------------------|-----------------------------------------------|---------------------------|---------------------|-------------------------|------------------------------------|

| PB1.8    | Standard I/O     | 30          | XBR0                                             | ~                     | AD14m/<br>A6                                  |                           |                     | WAKE.2                  | ADC1.3<br>CS0.12                   |

| PB1.9    | Standard I/O     | 29          | XBR0                                             | $\checkmark$          | AD13m/<br>A5                                  |                           |                     | WAKE.3                  | ADC1.2<br>CS0.13                   |

| PB1.10   | Standard I/O     | 28          | XBR0                                             | $\checkmark$          | AD12m/<br>A4                                  |                           |                     | DMA0T1<br>WAKE.4        | ADC1.1<br>CS0.14                   |

| PB1.11   | Standard I/O     | 27          | XBR0                                             | ~                     | AD11m/<br>A3                                  |                           |                     | DMA0T0<br>WAKE.5        | ADC1.0<br>CS0.15<br>PMU_Asleep     |

| PB1.12   | Standard I/O     | 26          | XBR0                                             | ~                     | AD10m/<br>A2                                  |                           |                     | WAKE.6                  |                                    |

| PB1.13   | Standard I/O     | 23          | XBR0                                             | ~                     | AD9m/<br>A1                                   |                           |                     |                         |                                    |

| PB1.14   | Standard I/O     | 22          | XBR0                                             | ~                     | AD8m/<br>A0                                   |                           |                     |                         |                                    |

| PB1.15   | Standard I/O     | 21          | XBR0                                             | $\checkmark$          | AD7m/<br>D7                                   |                           |                     |                         |                                    |

| PB2.0    | Standard I/O     | 20          | XBR1                                             | $\mathbf{\mathbf{Y}}$ | AD6m/<br>D6                                   | LSI0                      | Yes                 | INT0.0<br>INT1.0        |                                    |

| PB2.1    | Standard I/O     | 19          | XBR1                                             | $\checkmark$          | AD5m/<br>D5                                   | LSI1                      | Yes                 | INT0.1<br>INT1.1        |                                    |

| PB2.2    | Standard I/O     | 18          | XBR1                                             | >                     | AD4m/<br>D4                                   | LSI2                      | Yes                 | INT0.2<br>INT1.2        | CMP0N.0<br>CMP1N.0<br>RTC0TCLK_OUT |

| PB2.3    | Standard I/O     | 17          | XBR1                                             | $\checkmark$          | AD3m/<br>D3                                   | LSI3                      | Yes                 | INT0.3<br>INT1.3        | CMP0P.0<br>CMP1P.0                 |

| PB3.0    | 5 V Tolerant I/O | 16          | XBR1                                             | $\checkmark$          | AD2m/<br>D2                                   |                           |                     |                         | CMP0P.1<br>CMP1P.1                 |

| PB3.1    | 5 V Tolerant I/O | 15          | XBR1                                             | ~                     | AD1m/<br>D1                                   |                           |                     |                         | CMP0N.1<br>CMP1N.1                 |

| Pin Name | Туре                | Pin Numbers | Crossbar Capability<br>(see Port Config Section) | Port Match   | Output Toggle Logic | External Trigger Inputs | Analog or Additional<br>Functions |

|----------|---------------------|-------------|--------------------------------------------------|--------------|---------------------|-------------------------|-----------------------------------|

| VSS      | Ground              | 14          |                                                  |              |                     |                         |                                   |

| VDD      | Power (Core)        | 35          |                                                  |              |                     |                         |                                   |

| VIO      | Power (I/O)         | 13          |                                                  |              |                     |                         |                                   |

| VREGIN   | Power (Regulator)   | 36          |                                                  |              |                     |                         |                                   |

| VSSHD    | Ground (High Drive) | 2           |                                                  |              |                     |                         |                                   |

| VIOHD    | Power (High Drive)  | 3           |                                                  |              |                     |                         |                                   |

| RESET    | Active-low Reset    | 40          |                                                  |              |                     |                         |                                   |

| SWCLK    | Serial Wire         | 24          |                                                  |              |                     |                         |                                   |

| SWDIO    | Serial Wire         | 23          |                                                  |              |                     |                         |                                   |

| PB0.0    | Standard I/O        | 34          | XBR0                                             | ~            |                     |                         | ADC0.8<br>CS0.7<br>RTC1           |

| PB0.1    | Standard I/O        | 33          | XBR0                                             | $\checkmark$ |                     |                         | RTC2                              |

| PB0.2    | Standard I/O        | 32          | XBR0                                             | ~            |                     |                         | ADC0.9<br>CS0.0<br>VREFGND        |

| PB0.3    | Standard I/O        | 31          | XBR0                                             | ~            |                     |                         | ADC0.10<br>CS0.1<br>VREF          |

| PB0.4    | Standard I/O        | 30          | XBR0                                             | $\checkmark$ |                     |                         | ADC1.6<br>CS0.2<br>IDAC0          |

| PB0.5    | Standard I/O        | 29          |                                                  |              |                     |                         | IDAC1                             |

| PB0.6    | Standard I/O        | 28          | XBR0                                             | $\checkmark$ |                     |                         | ADC0.0<br>CS0.3<br>XTAL1          |

| PB0.7    | Standard I/O        | 27          | XBR0                                             | $\checkmark$ |                     |                         | ADC0.1<br>CS0.4<br>XTAL2          |

Table 6.3. Pin Definitions and Alternate Functions for SiM3C1x4

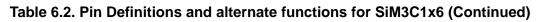

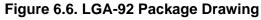

# 6.4. LGA-92 Package Specifications

| Dimension | Min           | Nominal  | Max  |  |  |  |  |

|-----------|---------------|----------|------|--|--|--|--|

| Α         | 0.74          | 0.84     | 0.94 |  |  |  |  |

| b         | 0.25 0.30 0.3 |          |      |  |  |  |  |

| C         | 3.15          | 3.20     | 3.25 |  |  |  |  |

| D         |               | 7.00 BSC |      |  |  |  |  |

| D1        |               | 6.50 BSC |      |  |  |  |  |

| D2        |               | 4.00 BSC |      |  |  |  |  |

| е         |               | 0.50 BSC |      |  |  |  |  |

| E         |               | 7.00 BSC |      |  |  |  |  |

| E1        |               | 6.50 BSC |      |  |  |  |  |

| E2        |               | 4.00 BSC |      |  |  |  |  |

| aaa       | _             | —        | 0.10 |  |  |  |  |

| bbb       | _             | —        | 0.10 |  |  |  |  |

| CCC       | _             | —        | 0.08 |  |  |  |  |

| ddd       |               | —        | 0.10 |  |  |  |  |

| eee       | — — 0.10      |          |      |  |  |  |  |

| Notes:    |               | •        |      |  |  |  |  |

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

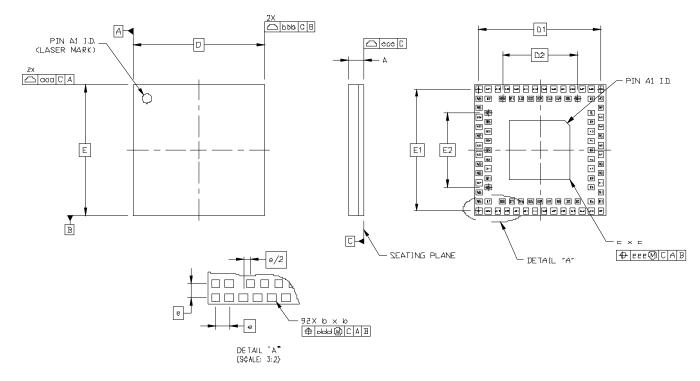

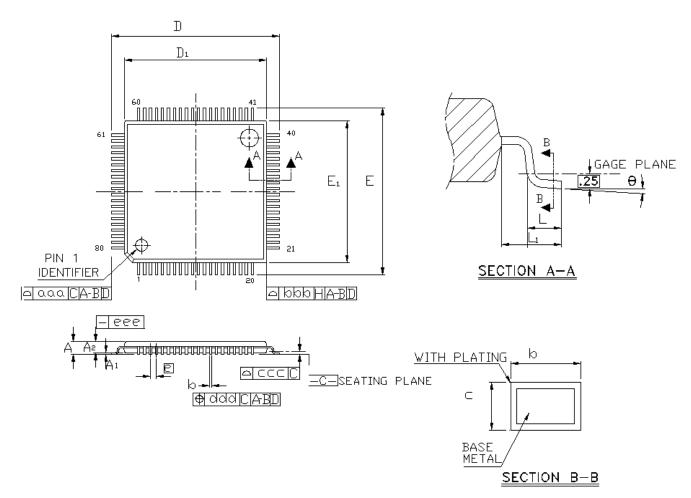

Figure 6.8. TQFP-80 Package Drawing

| Dimension | Min  | Nominal   | Max  |

|-----------|------|-----------|------|

| A         | —    | —         | 1.20 |

| A1        | 0.05 | —         | 0.15 |

| A2        | 0.95 | 1.00      | 1.05 |

| b         | 0.17 | 0.20      | 0.27 |

| с         | 0.09 | —         | 0.20 |

| D         |      | 14.00 BSC |      |

| D1        |      | 12.00 BSC |      |

| е         |      | 0.50 BSC  |      |

| E         |      | 14.00 BSC |      |

| E1        |      | 12.00 BSC |      |

| Dimension | Min      | Nominal | Мах  |

|-----------|----------|---------|------|

| L         | 0.45     | 0.60    | 0.75 |

| L1        | 1.00 Ref |         |      |

| Θ         | 0°       | 3.5°    | 7°   |

| aaa       | 0.20     |         |      |

| bbb       | 0.20     |         |      |

| CCC       | 0.08     |         |      |

| ddd       | 0.08     |         |      |

| eee       | 0.05     |         |      |

# Table 6.6. TQFP-80 Package Dimensions (Continued)

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This package outline conforms to JEDEC MS-026, variant ADD.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

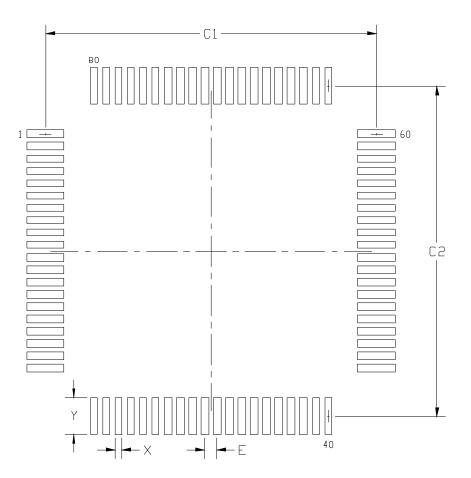

| Table 6.7. TQFP-80 Landing | <b>Diagram Dimensions</b> |

|----------------------------|---------------------------|

|----------------------------|---------------------------|

| Dimension | Min                      | Max                   |

|-----------|--------------------------|-----------------------|

| C1        | 13.30                    | 13.40                 |

| C2        | 13.30                    | 13.40                 |

| E         | 0.5                      | 0 BSC                 |

| X         | 0.20                     | 0.30                  |

| Y         | 1.40                     | 1.50                  |

| noted.    | own are in millimeters ( | (mm) unless otherwise |

2. This land pattern design is based on the IPC-7351 guidelines.

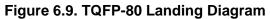

# 6.6. QFN-64 Package Specifications

| Dimension | Min      | Nominal | Max  |

|-----------|----------|---------|------|

| Α         | 0.80     | 0.85    | 0.90 |

| A1        | 0.00     | 0.02    | 0.05 |

| b         | 0.18     | 0.25    | 0.30 |

| D         | 9.00 BSC |         |      |

| D2        | 3.95     | 4.10    | 4.25 |

| e         | 0.50 BSC |         |      |

| E         | 9.00 BSC |         |      |

| E2        | 3.95     | 4.10    | 4.25 |

| L         | 0.30     | 0.40    | 0.50 |

| aaa       | 0.10     |         |      |

| bbb       | 0.10     |         |      |

| ccc       | 0.08     |         |      |

| ddd       | 0.10     |         |      |

| eee       | 0.05     |         |      |

# Table 6.8. QFN-64 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This package outline conforms to JEDEC MO-220.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 6.6.1. QFN-64 Solder Mask Design

All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

## 6.6.2. QFN-64 Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all pads.

- 4. A 3x3 array of 1.0 mm square openings on a 1.5 mm pitch should be used for the center ground pad.

## 6.6.3. QFN-64 Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

Silicon Labs

Simplicity Studio<sup>4</sup>

#### **Simplicity Studio**

One-click access to MCU and wireless tools, documentation, software, source code libraries & more. Available for Windows, Mac and Linux!

Support and Community community.silabs.com

#### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadio®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# http://www.silabs.com