Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                         |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                  |

| Core Size                  | 32-Bit Single-Core                                               |

| Speed                      | 80MHz                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT     |

| Number of I/O              | 65                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                 |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 32K x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                      |

| Data Converters            | A/D 32x12b; D/A 2x10b                                            |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 80-TQFP                                                          |

| Supplier Device Package    | 80-TQFP (12x12)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/sim3c167-b-gqr |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 3.8. Internal Oscillators (Continued)

| Parameter                                   | Symbol               | Test Condition                                     | Min   | Тур  | Max   | Unit   |

|---------------------------------------------|----------------------|----------------------------------------------------|-------|------|-------|--------|

| Low Power Oscillator (LPOSC0)               |                      |                                                    | 1     | I    |       |        |

| Oscillator Frequency                        | f <sub>LPOSC</sub>   | Full Temperature and<br>Supply Range               | 19    | 20   | 21    | MHz    |

|                                             |                      | T <sub>A</sub> = 25 °C,<br>V <sub>DD</sub> = 3.3 V | 19.5  | 20   | 20.5  | MHz    |

| Divided Oscillator Frequency                | f <sub>LPOSCD</sub>  | Full Temperature and<br>Supply Range               | 2.375 | 2.5  | 2.625 | MHz    |

| Power Supply Sensitivity                    | PSS <sub>LPOSC</sub> | T <sub>A</sub> = 25 °C                             |       | 0.5  | —     | %/V    |

| Temperature Sensitivity                     | TS <sub>LPOSC</sub>  | V <sub>DD</sub> = 3.3 V                            |       | 55   |       | ppm/°C |

| Low Frequency Oscillator (LFO               | SCO)                 |                                                    |       |      | 1     |        |

| Oscillator Frequency                        | f <sub>LFOSC</sub>   | Full Temperature and<br>Supply Range               | 13.4  | 16.4 | 19.7  | kHz    |

|                                             |                      | T <sub>A</sub> = 25 °C,<br>V <sub>DD</sub> = 3.3 V | 15.8  | 16.4 | 17.3  | kHz    |

| Power Supply Sensitivity                    | PSS <sub>LFOSC</sub> | T <sub>A</sub> = 25 °C                             | _     | 2.4  |       | %/V    |

| Temperature Sensitivity                     | TS <sub>LFOSC</sub>  | V <sub>DD</sub> = 3.3 V                            | _     | 0.2  |       | %/°C   |

| RTC0 Oscillator (RTC0OSC)                   |                      |                                                    | I     |      | 1     | 4      |

| Missing Clock Detector Trigger<br>Frequency | f <sub>RTCMCD</sub>  |                                                    |       | 8    | 15    | kHz    |

| RTC Robust Duty Cycle Range                 | DC <sub>RTC</sub>    |                                                    | 25    | _    | 55    | %      |

| *Note: PLL0OSC in free-running osci         | llator mode.         | 1                                                  | 1     | 1    | 1     | 1      |

## Table 3.9. External Oscillator

| Parameter                                         | Symbol             | Test Condition | Min  | Тур | Max | Unit |  |  |  |  |

|---------------------------------------------------|--------------------|----------------|------|-----|-----|------|--|--|--|--|

| External Input CMOS Clock<br>Frequency*           | f <sub>CMOS</sub>  |                | 0    | _   | 50  | MHz  |  |  |  |  |

| External Input CMOS Clock High Time               | t <sub>CMOSH</sub> |                | 9    | _   |     | ns   |  |  |  |  |

| External Input CMOS Clock Low Time                | t <sub>CMOSL</sub> |                | 9    |     |     | ns   |  |  |  |  |

| External Crystal Clock Frequency                  | f <sub>XTAL</sub>  |                | 0.01 | —   | 30  | MHz  |  |  |  |  |

| *Note: Minimum of 10 kHz during debug operations. |                    |                |      |     |     |      |  |  |  |  |

## Table 3.17. Port I/O (Continued)

| Parameter                                          | Symbol             | Test Condition                        | Min              | Тур           | Мах | Unit |

|----------------------------------------------------|--------------------|---------------------------------------|------------------|---------------|-----|------|

| P-Channel Source Current Limit                     | I <sub>SRCL</sub>  | Mode 0                                | _                | 0.8           |     | mA   |

| $(2.7 V \leq VIOHD \leq 6 V,$                      |                    | Mode 1                                | _                | 1.25          |     |      |

| V <sub>OH</sub> = VIOHD – 0.8 V)<br>See Figure 3.2 |                    | Mode 2                                | _                | 1.75          |     |      |

| See Figure 5.2                                     |                    | Mode 3                                | _                | 2.5           |     |      |

|                                                    |                    | Mode 4                                | _                | 3.5           |     |      |

|                                                    |                    | Mode 5                                | _                | 4.75          |     |      |

|                                                    |                    | Mode 6                                | _                | 7             |     |      |

|                                                    |                    | Mode 7                                | _                | 9.5           |     |      |

|                                                    |                    | Mode 8                                | _                | 14            |     |      |

|                                                    |                    | Mode 9                                | _                | 18.75         |     |      |

|                                                    |                    | Mode 10                               | _                | 28.25         | _   |      |

|                                                    |                    | Mode 11                               | _                | 37.5          | _   |      |

|                                                    |                    | Mode 12                               | _                | 56.25         |     |      |

|                                                    |                    | Mode 13                               | _                | 75            | _   |      |

|                                                    |                    | Mode 14                               | _                | 112.5         |     |      |

|                                                    |                    | Mode 15                               | _                | 150           |     |      |

| Total P-Channel Source Current on P4.0-P4.5 (DC)   | I <sub>SRCLT</sub> |                                       | -                | —             | 400 | mA   |

| Pin Capacitance                                    | C <sub>IO</sub>    |                                       | _                | 30            |     | pF   |

| Weak Pull-Up Current in Low Volt-<br>age Mode      | I <sub>PU</sub>    | V <sub>IOHD</sub> = 1.8 V             | -6               | -3.5          | -2  | μA   |

|                                                    |                    | V <sub>IOHD</sub> = 3.6 V             | -30              | -20           | -10 | μA   |

| Weak Pull-Up Current in High Volt-<br>age Mode     | I <sub>PU</sub>    | V <sub>IOHD</sub> = 2.7 V             | -15              | -10           | -5  | μA   |

|                                                    |                    | V <sub>IOHD</sub> = 6 V               | -30              | -20           | -10 | μA   |

| Input Leakage (Pullups off)                        | I <sub>LK</sub>    |                                       | -1               |               | 1   | μA   |

| *Note: RESET does not drive to logic h             | igh. Specifica     | itions for RESET V <sub>OL</sub> adhe | ere to the low d | rive setting. |     |      |

| Table 3.19. Absolute Maximum | Ratings (Continued) |

|------------------------------|---------------------|

|------------------------------|---------------------|

| Parameter                                   | Symbol            | Test Condition                                     | Min                  | Мах                                                                      | Unit |  |

|---------------------------------------------|-------------------|----------------------------------------------------|----------------------|--------------------------------------------------------------------------|------|--|

| Voltage on I/O pins, Port Bank 3 I/O        | V <sub>IN</sub>   | SiM3C1x7, PB3.0–<br>PB3.7, V <sub>IO</sub> ≥ 3.3 V | V <sub>SS</sub> -0.3 | 5.8                                                                      | V    |  |

|                                             |                   | SiM3C1x7, PB3.0–<br>PB3.7, V <sub>IO</sub> < 3.3 V | V <sub>SS</sub> -0.3 | V <sub>IO</sub> +2.5                                                     | V    |  |

|                                             |                   | SiM3C1x7, PB3.8 -<br>PB3.11                        | V <sub>SS</sub> -0.3 | Lowest of<br>V <sub>IO</sub> +2.5,<br>V <sub>REGIN</sub> +0.3,<br>or 5.8 | V    |  |

|                                             |                   | SiM3C1x6, PB3.0–<br>PB3.5, V <sub>IO</sub> ≥ 3.3 V | V <sub>SS</sub> -0.3 | 5.8                                                                      | V    |  |

|                                             |                   | SiM3C1x6, PB3.0–<br>PB3.5, V <sub>IO</sub> < 3.3 V | V <sub>SS</sub> -0.3 | V <sub>IO</sub> +2.5                                                     | V    |  |

|                                             |                   | SiM3C1x6, PB3.6–<br>PB3.9                          | V <sub>SS</sub> -0.3 | Lowest of<br>V <sub>IO</sub> +2.5,<br>V <sub>REGIN</sub> +0.3,<br>or 5.8 | V    |  |

|                                             |                   | SiM3C1x4, PB3.0–<br>PB3.3                          | V <sub>SS</sub> -0.3 | Lowest of<br>V <sub>IO</sub> +2.5,<br>V <sub>REGIN</sub> +0.3,<br>or 5.8 | V    |  |

| Total Current Sunk into Supply Pins         | I <sub>SUPP</sub> | $V_{DD},V_{REGIN},V_{IO},V_{IOHD}$                 | —                    | 400                                                                      | mA   |  |

| Total Current Sourced out of Ground<br>Pins | I <sub>VSS</sub>  | V <sub>SS</sub> , V <sub>SSHD</sub>                | 400                  | _                                                                        | mA   |  |

| Current Sourced or Sunk by Any I/O<br>Pin   | I <sub>PIO</sub>  | PB0, PB1 <u>, PB2,</u> PB3,<br>and RESET           | -100                 | 100                                                                      | mA   |  |

|                                             |                   | PB4                                                | -300                 | 300                                                                      | mA   |  |

| Current Injected on Any I/O Pin             | I <sub>INJ</sub>  | PB0, PB1 <u>, PB2,</u> PB3,<br>and RESET           | -100                 | 100                                                                      | mA   |  |

|                                             |                   | PB4                                                | -300                 | 300                                                                      | mA   |  |

| Total Injected Current on I/O Pins          | ΣΙ <sub>INJ</sub> | Sum <u>of all I/O</u> and<br>RESET                 | -400                 | 400                                                                      | mA   |  |

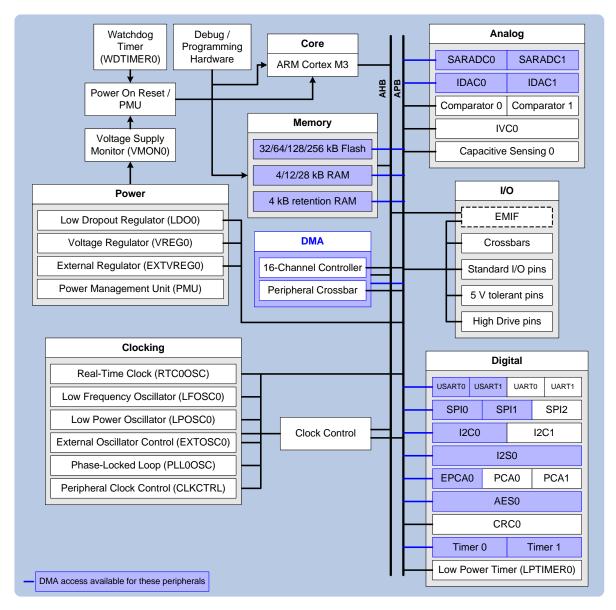

## 4. Precision32<sup>™</sup> SiM3C1xx System Overview

The SiM3C1xx Precision32<sup>™</sup> devices are fully integrated, mixed-signal system-on-a-chip MCUs. Highlighted features are listed below. Refer to Table 5.1 for specific product feature selection and part ordering numbers.

- Core:

- 32-bit ARM Cortex-M3 CPU.

- 80 MHz maximum operating frequency.

- Branch target cache and prefetch buffers to minimize wait states.

- Memory: 32–256 kB Flash; in-system programmable, 8–32 kB SRAM (including 4 kB retention SRAM, which preserves state in PM9 mode).

- Power:

- Low drop-out (LDO) regulator for CPU core voltage.

- Power-on reset circuit and brownout detectors.

- 3.3 V output LDO for direct power from 5 V supplies.

- External transistor regulator.

- Power Management Unit (PMU).

- I/O: Up to 65 total multifunction I/O pins:

- Up to six programmable high-power capable (5–300 mA with programmable current limiting, 1.8–5 V).

- Up to twelve 5 V tolerant general purpose pins.

- Two flexible peripheral crossbars for peripheral routing.

- Clock Sources:

- Internal oscillator with PLL: 23–80 MHz with ± 1.5% accuracy in free-running mode.

- Low-power internal oscillator: 20 MHz and 2.5 MHz modes.

- Low-frequency internal oscillator: 16.4 kHz.

- External RTC crystal oscillator: 32.768 kHz.

- External oscillator: Crystal, RC, C, CMOS clock modes.

- Programmable clock divider allows any oscillator source to be divided by binary factor from 1-128.

- Data Peripherals:

- 16-Channel DMA Controller.

- 128/192/256-bit Hardware AES Encryption.

- 16/32-bit CRC.

#### Timers/Counters and PWM:

- 6-channel Enhanced Programmable Counter Array (EPCAn) supporting advanced PWM and capture/compare.

- 2 x 2-channel Standard Programmable Counter Array (PCAn) supporting PWM and capture/compare.

- 2 x 32-bit Timers can be split into 4 x 16-bit Timers, support PWM and capture/compare.

- Real Time Clock (RTCn).

- Low Power Timer.

- Watchdog Timer.

- Communications Peripherals:

- External Memory Interface.

- 2 x USARTs and 2 x UARTs with IrDA and ISO7816 SmartCard support.

- 3 x SPIs.

- 2 x I2C.

- I<sup>2</sup>S (receive and transmit).

- Analog:

- 2 x 12-Bit Analog-to-Digital Converters (SARADC).

- 2 x 10-Bit Digital-to-Analog Converter (IDAC).

- 16-Channel Capacitance-to-Digital Converter (CAPSENSE).

- 2 x Low-Current Comparators (CMP).

- 1 x Current-to-Voltage Converter (IVC) module with two channels.

#### On-Chip Debugging

With on-chip power-on reset, voltage supply monitor, watchdog timer, and clock oscillator, the SiM3C1xx devices are truly standalone system-on-a-chip solutions. The Flash memory is reprogrammable in-circuit, providing non-

volatile data storage and allowing field upgrades of the firmware. User firmware has complete control of all peripherals and may individually shut down and gate the clocks of any or all peripherals for power savings.

The on-chip debugging interface (SWJ-DP) allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging.

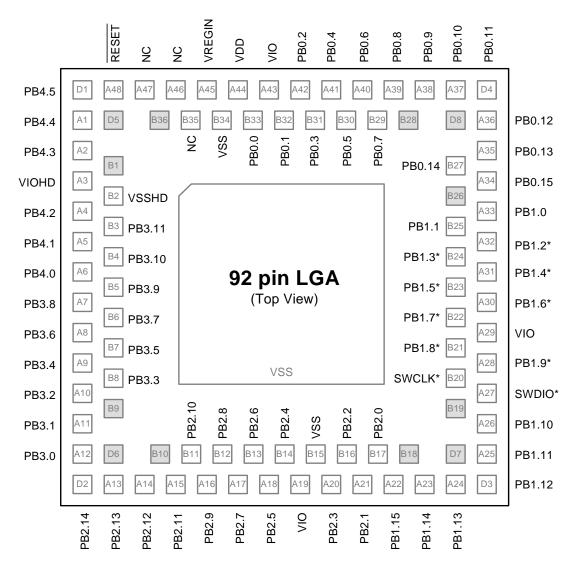

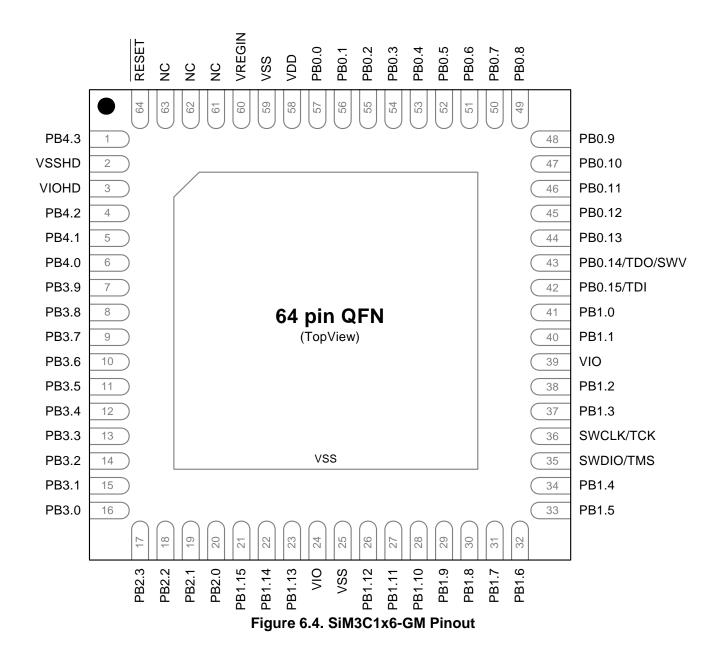

Each device is specified for 1.8 to 3.6 V operation over the industrial temperature range (-40 to +85 °C). The Port I/O and RESET pins are powered from the IO supply voltage. The SiM3C1xx devices are available in 40-pin or 64-pin QFN, 64-pin or 80-pin TQFP, or 92-pin LGA packages. All package options are lead-free and RoHS compliant. See Table 5.1 for ordering information. A block diagram is included in Figure 4.1.

Figure 4.1. Precision32<sup>™</sup> SiM3C1xx Family Block Diagram

## 4.1. Power

## 4.1.1. LDO and Voltage Regulator (VREG0)

The SiM3C1xx devices include two internal regulators: the core LDO Regulator and the Voltage Regulator (VREG0).

The LDO Regulator converts a 1.8–3.6 V supply to the core operating voltage of 1.8 V. This LDO consumes little power and provides flexibility in choosing a power supply for the system.

The Voltage Regulator regulates from 5.5 to 2.7 V and can serve as an input to the LDO. This allows the device to be powered from up to a 5.5 V supply without any external components other than bypass capacitors.

#### 4.1.2. Voltage Supply Monitor (VMON0)

The SiM3C1xx devices include a voltage supply monitor which allows devices to function in known, safe operating condition without the need for external hardware. The supply monitor includes additional circuitry that can monitor the main supply voltage and the VREGIN input voltage divided by 4 (VREGIN / 4).

The supply monitor module includes the following features:

- Main supply "VDD Low" (VDD below the early warning threshold) notification.

- Holds the device in reset if the main VDD supply drops below the VDD Reset threshold.

- VREGIN divided by 4 (VREGIN / 4) supply "VREGIN Low" notification.

#### 4.1.3. External Regulator (EXTVREG0)

The External Regulator provides all the circuitry needed for a high-power regulator except the power transistor (NPN or PNP) and current sensing resistor (if current limiting is enabled).

The External Regulator module has the following features:

- Interfaces with either an NPN or PNP external transistor that serves as the pass device for the high current regulator.

- Automatic current limiting.

- Automatic foldback limiting.

- Sources up to 1 A for use by external circuitry.

- Variable output voltage from 1.8–3.6 V in 100 mV steps.

#### 4.1.4. Power Management Unit (PMU)

The Power Management Unit on the SiM3C1xx manages the power systems of the device. On power-up, the PMU ensures the core voltages are a proper value before core instruction execution begins. It also recognizes and manages the various wake sources for low-power modes of the device.

The PMU module includes the following features:

- Up to 16 pin wake inputs can wake the device from Power Mode 9.

- The Low Power Timer, RTC0 (alarms and oscillator fail), Comparator 0, and the RESET pin can also serve as wake sources for Power Mode 9.

- All PM9 wake sources (except for the RESET pin) can also reset the Low Power Timer or RTC0 modules.

- Disables the level shifters to pins and peripherals to further reduce power usage in PM9. These level shifters must be re-enabed by firmware after exiting PM9.

- Provides a PMU\_Asleep signal to a pin as an indicator that the device is in PM9.

## 4.2. I/O

## 4.2.1. General Features

The SiM3C1xx ports have the following features:

- Push-pull or open-drain output modes and analog or digital modes.

- Option for high or low output drive strength.

- Port Match allows the device to recognize a change on a port pin value.

- Internal pull-up resistors are enabled or disabled on a port-by-port basis.

- Two external interrupts with up to 16 inputs provide monitoring capability for external signals.

- Internal Pulse Generator Timer (PB2 only) to generate simple square waves.

- A subset of pins can also serve as inputs to the Port Mapped Level Shifters available on the High Drive Pins.

## 4.2.2. High Drive Pins (PB4)

The High Drive pins have the following additional features:

- Programmable safe state: high, low, or high impedance.

- Programmable drive strength and slew rates.

- Programmable hardware current limiting.

- Powered from a separate source (VIOHD, which can be up to 6 V) from the rest of the device.

- Supports various functions, including GPIO, UART1 pins, EPCA0 pins, or Port Mapped Level Shifting.

### 4.2.3. 5 V Tolerant Pins (PB3)

The 5 V tolerant pins can be connected to external circuitry operating at voltages above the device supply without needing extra components to shift the voltage level.

#### 4.2.4. Crossbars

The SiM3C1xx devices have two Crossbars with the following features:

- Flexible peripheral assignment to port pins.

- Pins can be individually skipped to move peripherals as needed for design or layout considerations.

The Crossbars have a fixed priority for each I/O function and assign these functions to the port pins. When a digital resource is selected, the least-significant unassigned port pin is assigned to that resource. If a port pin is assigned, the Crossbars skip that pin when assigning the next selected resource. Additionally, the Crossbars will skip port pins whose associated bits in the PBSKIPEN registers are set. This provides some flexibility when designing a system: pins involved with sensitive analog measurements can be moved away from digital I/O and peripherals can be moved around the chip as needed to ease layout constraints.

## 4.6. Communications Peripherals

## 4.6.1. External Memory Interface (EMIF0)

The External Memory Interface (EMIF0) allows external parallel asynchronous devices, like SRAMs and LCD controllers, to appear as part of the system memory map. The EMIF0 module includes the following features:

- Provides a memory mapped view of multiple external devices.

- Support for byte, half-word and word accesses regardless of external device data-width.

- Error indicator for certain invalid transfers.

- Minimum external timing allows for 3 clocks per write or 4 clocks per read.

- Output bus can be shared between non-muxed and muxed devices.

- Available extended address output allows for up to 24-bit address with 8-bit parallel devices.

- Support for 8-bit and 16-bit (muxed-mode only) devices with up to two chip-select signals.

- Support for internally muxed devices with dynamic address shifting.

- Fully programmable control signal waveforms.

### 4.6.2. USART (USART0, USART1)

The USART uses two signals (TX and RX) and a predetermined fixed baud rate to communicate with a single device. In addition to these signals, the USART0 module can optionally use a clock (UCLK) or hardware handshaking (RTS and CTS).

The USART module provides the following features:

- Independent transmitter and receiver configurations with separate 16-bit baud rate generators.

- Synchronous or asynchronous transmissions and receptions.

- Clock master or slave operation with programmable polarity and edge controls.

- Up to 5 Mbaud (synchronous or asynchronous, TX or RX, and master or slave) or 1 Mbaud Smartcard (TX or RX).

- Individual enables for generated clocks during start, stop, and idle states.

- Internal transmit and receive FIFOs with flush capability and support for byte, half-word, and word reads and writes.

- Data bit lengths from 5 to 9 bits.

- Programmable inter-packet transmit delays.

- Auto-baud detection with support for the LIN SYNC byte.

- Automatic parity generation (with enable).

- Automatic start and stop generation (with separate enables).

- Transmit and receive hardware flow-control.

- Independent inversion correction for TX, RX, RTS, and CTS signals.

- IrDA modulation and demodulation with programmable pulse widths.

- Smartcard ACK/NACK support.

- Parity error, frame error, overrun, and underrun detection.

- Multi-master and half-duplex support.

- Multiple loop-back modes supported.

- Multi-processor communications support.

#### 4.6.3. UART (UART0, UART1)

The USART uses two signals (TX and RX) and a predetermined fixed baud rate to communicate with a single device.

The UART module provides the following features:

- Independent transmitter and receiver configurations with separate 16-bit baud-rate generators.

- Asynchronous transmissions and receptions.

- Up to 5 Mbaud (TX or RX) or 1 Mbaud Smartcard (TX or RX).

## 4.7. Analog

## 4.7.1. 12-Bit Analog-to-Digital Converters (SARADC0, SARADC1)

The SARADC0 and SARADC1 modules on SiM3C1xx devices are Successive Approximation Register (SAR) Analog to Digital Converters (ADCs). The key features of the SARADC module are:

- Single-ended 12-bit and 10-bit modes.

- Supports an output update rate of 250 k samples per second in 12-bit mode or 1 M samples per second in 10-bit mode.

- Operation in low power modes at lower conversion speeds.

- Selectable asynchronous hardware conversion trigger with hardware channel select.

- Output data window comparator allows automatic range checking.

- Support for Burst Mode, which produces one set of accumulated data per conversion-start trigger with programmable power-on settling and tracking time.

- Conversion complete, multiple conversion complete, and FIFO overflow and underflow flags and interrupts supported.

- Flexible output data formatting.

- Sequencer allows up to 8 sources to be automatically scanned using one of four channel characteristic profiles without software intervention.

- Eight-word conversion data FIFO for DMA operations.

- Multiple SARADC modules can work together synchronously or by interleaving samples.

- Includes two internal references (1.65 V fast-settling, 1.2/2.4 V precision), support for an external reference, and support for an external signal ground.

#### 4.7.2. Sample Sync Generator (SSG0)

The SSG module includes a phase counter and a pulse generator. The phase counter is a 4-bit free-running counter clocked from the SARADC module clock. Counting-up from zero, the phase counter marks sixteen equally-spaced events for any number of SARADC modules. The ADCs can use this phase counter to start a conversion. The programmable pulse generator creates a 50% duty cycle pulse with a period of 16 phase counter ticks. Up to four programmable outputs available to external devices can be driven by the pulse generator with programmable polarity and a defined output setting when the pulse generator is stopped.

The Sample Sync Generator module has the following features:

- Connects multiple modules together to perform synchronized actions.

- Outputs a clock synchronized to the internal sampling clock used by any number of SARADC modules to pins for use by external devices.

- Includes a phase counter, pulse generator, and up to four programmable outputs.

#### 4.7.3. 10-Bit Digital-to-Analog Converter (IDAC0, IDAC1)

The IDAC takes a digital value as an input and outputs a proportional constant current on a pin. The IDAC module includes the following features:

- 10-bit current DAC with support for four timer, up to seven external I/O, on demand, and SSG0 output update triggers.

- Ability to update on rising, falling, or both edges for any of the external I/O trigger sources (DACnTx).

- Supports an output update rate greater than 600 k samples per second.

- Support for three full-scale output modes: 0.5 mA, 1.0 mA and 2.0 mA.

- Four-word FIFO to aid with high-speed waveform generation or DMA interactions.

- Individual FIFO overrun, underrun, and went-empty interrupt status sources.

- Support for multiple data packing formats, including: single 10-bit sample per word, dual 10-bit samples per word, or four 8-bit samples per word.

- Support for left- and right-justified data.

## 5. Ordering Information

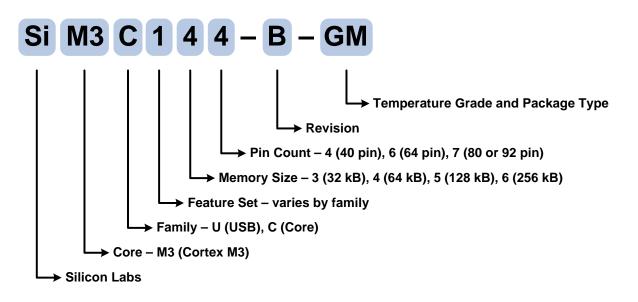

## Figure 5.1. SiM3C1xx Part Numbering

All devices in the SiM3C1xx family have the following features:

- Core: ARM Cortex-M3 with maximum operating frequency of 80 MHz.

- Flash Program Memory: 32-256 kB, in-system programmable.

- RAM: 8–32 kB SRAM, with 4 kB retention SRAM

- I/O: Up to 65 multifunction I/O pins, including high-drive and 5 V-tolerant pins.

- Clock Sources: Internal and external oscillator options.

- 16-Channel DMA Controller.

- 128/192/256-bit AES.

- 16/32-bit CRC.

- **Timers:** 2 x 32-bit (4 x 16-bit).

- Real-Time Clock.

- Low-Power Timer.

- PCA: 1 x 6 channels (Enhanced), 2 x 2 channels (Standard). PWM, capture, and clock generation capabilites.

- ADC: 2 x 12-bit 250 ksps (10-bit 1 Msps) SAR.

- **DAC:** 2 x 10-bit IDAC.

- Temperature Sensor.

- Internal VREF.

- 16-channel Capacitive Sensing (CAPSENSE).

- **Comparator:** 2 x low current.

- Current to Voltage Converter (IVC).

- Serial Buses: 2 x USART, 2 x UART, 3 x SPI, 2 x I2C, 1 x I<sup>2</sup>S.

The inclusion of some features varies across different members of the device family. The differences are detailed in Table 5.1.

# SiM3C1xx

| Ordering Part Number | Flash Memory (kB) | RAM (kB) | External Memory Interface (EMIF) | Maximum Number of EMIF Address/Data Pins | Digital Port I/Os (Total) | Digital Port I/Os with High Drive Capability | Number of SARADC0 Channels | Number of SARADC1 Channels | Number of CAPSENSE0 Channels | Number of Comparator 0/1 Inputs (+/-) | Number of PMU Pin Wake Sources | JTAG Debugging Interface | ETM Debugging Interface | Serial Wire Debugging Interface | Lead-free (RoHS Compliant) | Package |

|----------------------|-------------------|----------|----------------------------------|------------------------------------------|---------------------------|----------------------------------------------|----------------------------|----------------------------|------------------------------|---------------------------------------|--------------------------------|--------------------------|-------------------------|---------------------------------|----------------------------|---------|

| SiM3C167-B-GM        | 256               | 32       | $\checkmark$                     | 24                                       | 65                        | 6                                            | 16                         | 16                         | 16                           | 8/8                                   | 16                             | $\checkmark$             | $\checkmark$            | $\checkmark$                    | $\checkmark$               | LGA-92  |

| SiM3C167-B-GQ        | 256               | 32       | $\checkmark$                     | 24                                       | 65                        | 6                                            | 16                         | 16                         | 16                           | 8/8                                   | 16                             | $\checkmark$             | $\checkmark$            | $\checkmark$                    | $\checkmark$               | TQFP-80 |

| SiM3C166-B-GM        | 256               | 32       | $\checkmark$                     | 16                                       | 50                        | 4                                            | 13                         | 15                         | 15                           | 6/6                                   | 15                             | $\checkmark$             |                         | $\checkmark$                    | $\checkmark$               | QFN-64  |

| SiM3C166-B-GQ        | 256               | 32       | $\checkmark$                     | 16                                       | 50                        | 4                                            | 13                         | 15                         | 15                           | 6/6                                   | 15                             | $\checkmark$             |                         | $\checkmark$                    | $\checkmark$               | TQFP-64 |

| SiM3C164-B-GM        | 256               | 32       |                                  |                                          | 28                        | 4                                            | 7                          | 11                         | 12                           | 3/3                                   | 10                             |                          |                         | $\checkmark$                    | $\checkmark$               | QFN-40  |

| SiM3C157-B-GM        | 128               | 32       | $\checkmark$                     | 24                                       | 65                        | 6                                            | 16                         | 16                         | 16                           | 8/8                                   | 16                             | $\checkmark$             | $\checkmark$            | ~                               | $\checkmark$               | LGA-92  |

| SiM3C157-B-GQ        | 128               | 32       | $\checkmark$                     | 24                                       | 65                        | 6                                            | 16                         | 16                         | 16                           | 8/8                                   | 16                             | $\checkmark$             | ~                       | $\checkmark$                    | $\checkmark$               | TQFP-80 |

| SiM3C156-B-GM        | 128               | 32       | $\checkmark$                     | 16                                       | 50                        | 4                                            | 13                         | 15                         | 15                           | 6/6                                   | 15                             | $\checkmark$             |                         | $\checkmark$                    | $\checkmark$               | QFN-64  |

| SiM3C156-B-GQ        | 128               | 32       | $\checkmark$                     | 16                                       | 50                        | 4                                            | 13                         | 15                         | 15                           | 6/6                                   | 15                             | $\checkmark$             |                         | V                               | $\checkmark$               | TQFP-64 |

| SiM3C154-B-GM        | 128               | 32       |                                  |                                          | 28                        | 4                                            | 7                          | 11                         | 12                           | 3/3                                   | 10                             |                          |                         | $\checkmark$                    | $\checkmark$               | QFN-40  |

| SiM3C146-B-GM        | 64                | 16       | $\checkmark$                     | 16                                       | 50                        | 4                                            | 13                         | 15                         | 15                           | 6/6                                   | 15                             | $\checkmark$             |                         | ~                               | $\checkmark$               | QFN-64  |

| SiM3C146-B-GQ        | 64                | 16       | $\checkmark$                     | 16                                       | 50                        | 4                                            | 13                         | 15                         | 15                           | 6/6                                   | 15                             | $\checkmark$             |                         | ~                               | $\checkmark$               | TQFP-64 |

| SiM3C144-B-GM        | 64                | 16       |                                  |                                          | 28                        | 4                                            | 7                          | 11                         | 12                           | 3/3                                   | 10                             |                          |                         | ~                               | $\checkmark$               | QFN-40  |

| SiM3C136-B-GM        | 32                | 8        | $\checkmark$                     | 16                                       | 50                        | 4                                            | 13                         | 15                         | 15                           | 6/6                                   | 15                             | $\checkmark$             |                         | ~                               | $\checkmark$               | QFN-64  |

| SiM3C136-B-GQ        | 32                | 8        | $\checkmark$                     | 16                                       | 50                        | 4                                            | 13                         | 15                         | 15                           | 6/6                                   | 15                             | $\checkmark$             |                         | V                               | $\checkmark$               | TQFP-64 |

| SiM3C134-B-GM        | 32                | 8        |                                  |                                          | 28                        | 4                                            | 7                          | 11                         | 12                           | 3/3                                   | 10                             |                          |                         | $\checkmark$                    | $\checkmark$               | QFN-40  |

Table 5.1. Product Selection Guide

\*Noted pins are listed in the pinout table and 80-pin TQFP package figure with additional names. These alternate functions are also present on the 92-pin LGA package and are identical to those on the 80-pin TQFP package.

Figure 6.2. SiM3C1x7-GM Pinout

| Pin Name | Туре                                                 | Pin Numbers TQFP-80 | Pin Numbers LGA-92 | Crossbar Capability<br>(see Port Config Section) | Port Match | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs | Analog or Additional<br>Functions |

|----------|------------------------------------------------------|---------------------|--------------------|--------------------------------------------------|------------|-----------------------------------------------|---------------------------|---------------------|-------------------------|-----------------------------------|

| PB4.0    | High Drive I/O                                       | 8                   | A6                 |                                                  |            |                                               | LSO0                      |                     |                         |                                   |

| PB4.1    | High Drive I/O                                       | 7                   | A5                 |                                                  |            |                                               | LSO1                      |                     |                         |                                   |

| PB4.2    | High Drive I/O                                       | 6                   | A4                 |                                                  |            |                                               | LSO2                      |                     |                         |                                   |

| PB4.3    | High Drive I/O                                       | 3                   | A2                 |                                                  |            |                                               | LSO3                      |                     |                         |                                   |

| PB4.4    | High Drive I/O                                       | 2                   | A1                 |                                                  |            |                                               | LSO4                      |                     |                         |                                   |

| PB4.5    | High Drive I/O                                       | 1                   | D1                 |                                                  |            |                                               | LSO5                      |                     |                         |                                   |

|          | ed pins on the LGA-92 p<br>ve no internal connectior | -                   |                    |                                                  | ect pin    | s. They sho                                   | ould be s                 | oldere              | d to the PCB            | for mechanical stabil-            |

## Table 6.1. Pin Definitions and alternate functions for SiM3C1x7 (Continued)

## SiM3C1xx

| Pin Name  | Туре                | Pin Numbers | Crossbar Capability<br>(see Port Config Section) | Port Match            | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs | Analog or Additional<br>Functions |

|-----------|---------------------|-------------|--------------------------------------------------|-----------------------|-----------------------------------------------|---------------------------|---------------------|-------------------------|-----------------------------------|

| VSS       | Ground              | 25<br>59    |                                                  |                       |                                               |                           |                     |                         |                                   |

| VDD       | Power (Core)        | 58          |                                                  |                       |                                               |                           |                     |                         |                                   |

| VIO       | Power (I/O)         | 24<br>39    |                                                  |                       |                                               |                           |                     |                         |                                   |

| VREGIN    | Power (Regulator)   | 60          |                                                  |                       |                                               |                           |                     |                         |                                   |

| VSSHD     | Ground (High Drive) | 2           |                                                  |                       |                                               |                           |                     |                         |                                   |

| VIOHD     | Power (High Drive)  | 3           |                                                  |                       |                                               |                           |                     |                         |                                   |

| RESET     | Active-low Reset    | 64          |                                                  |                       |                                               |                           |                     |                         |                                   |

| SWCLK/TCK | Serial Wire / JTAG  | 36          |                                                  |                       |                                               |                           |                     |                         |                                   |

| SWDIO/TMS | Serial Wire / JTAG  | 35          |                                                  |                       |                                               |                           |                     |                         |                                   |

| PB0.0     | Standard I/O        | 57          | XBR0                                             | ~                     |                                               |                           |                     |                         | ADC0.2<br>CS0.1                   |

| PB0.1     | Standard I/O        | 56          | XBR0                                             | $\checkmark$          |                                               |                           |                     |                         | ADC0.3<br>CS0.2                   |

| PB0.2     | Standard I/O        | 55          | XBR0                                             | $\mathbf{\mathbf{Y}}$ |                                               |                           |                     |                         | ADC0.4<br>CS0.3                   |

| PB0.3     | Standard I/O        | 54          | XBR0                                             | $\checkmark$          |                                               |                           |                     |                         | ADC0.5<br>CS0.4                   |

| PB0.4     | Standard I/O        | 53          | XBR0                                             | $\checkmark$          |                                               |                           |                     |                         | ADC0.6<br>CS0.5<br>IVC0.0         |

| PB0.5     | Standard I/O        | 52          | XBR0                                             | ~                     |                                               |                           |                     |                         | ADC0.7<br>CS0.6<br>IVC0.1         |

| PB0.6     | Standard I/O        | 51          | XBR0                                             | $\checkmark$          |                                               |                           |                     |                         | ADC0.8<br>CS0.7<br>RTC1           |

Table 6.2. Pin Definitions and alternate functions for SiM3C1x6

| <b></b>            | 1                                           |             | 1                                                |              | 1                                             | 1                         | 1                   |                         | ,                                 |

|--------------------|---------------------------------------------|-------------|--------------------------------------------------|--------------|-----------------------------------------------|---------------------------|---------------------|-------------------------|-----------------------------------|

| Pin Name           | Туре                                        | Pin Numbers | Crossbar Capability<br>(see Port Config Section) | Port Match   | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs | Analog or Additional<br>Functions |

| PB0.7              | Standard I/O                                | 50          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | RTC2                              |

| PB0.8              | Standard I/O                                | 49          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC0.9<br>VREFGND                 |

| PB0.9              | Standard I/O                                | 48          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC0.10<br>VREF                   |

| PB0.10             | Standard I/O                                | 47          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC1.6<br>IDAC0                   |

| PB0.11             | Standard I/O                                | 46          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | IDAC1                             |

| PB0.12             | Standard I/O                                | 45          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | XTAL1                             |

| PB0.13             | Standard I/O                                | 44          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | XTAL2                             |

| PB0.14/TDO/<br>SWV | Standard I/O / JTAG<br>/ Serial Wire Viewer | 43          | XBR0                                             | ~            |                                               |                           |                     |                         | ADC0.12<br>ADC1.12                |

| PB0.15/TDI         | Standard I/O / JTAG                         | 42          | XBR0                                             | ~            |                                               |                           |                     |                         | ADC0.13<br>ADC1.13                |

| PB1.0              | Standard I/O                                | 41          | XBR0                                             | ~            |                                               |                           |                     |                         | ADC0.14<br>ADC1.14                |

| PB1.1              | Standard I/O                                | 40          | XBR0                                             | ~            |                                               |                           |                     |                         | ADC0.15<br>ADC1.15                |

| PB1.2              | Standard I/O                                | 38          | XBR0                                             | ~            |                                               |                           |                     |                         | ADC1.11<br>CS0.8                  |

| PB1.3              | Standard I/O                                | 37          | XBR0                                             | ~            |                                               |                           |                     |                         | ADC1.10<br>CS0.9                  |

| PB1.4              | Standard I/O                                | 34          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC1.8                            |

| PB1.5              | Standard I/O                                | 33          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC1.7                            |

| PB1.6              | Standard I/O                                | 32          | XBR0                                             | ~            |                                               |                           |                     | ADC0T15<br>WAKE.0       | ADC1.5<br>CS0.10                  |

| PB1.7              | Standard I/O                                | 31          | XBR0                                             | $\checkmark$ | AD15m/<br>A7                                  |                           |                     | ADC1T15<br>WAKE.1       | ADC1.4<br>CS0.11                  |

## Table 6.2. Pin Definitions and alternate functions for SiM3C1x6 (Continued)

| Pin Name | Туре             | Pin Numbers | Crossbar Capability<br>(see Port Config Section) | Port Match  | Output Toggle Logic | External Trigger Inputs                                   | Analog or Additional<br>Functions |

|----------|------------------|-------------|--------------------------------------------------|-------------|---------------------|-----------------------------------------------------------|-----------------------------------|

| PB3.1    | 5 V Tolerant I/O | 9           | XBR1                                             | <b>&gt;</b> |                     | DAC0T1<br>DAC1T1<br>LPT0T1<br>INT0.1<br>INT1.1<br>WAKE.13 | CMP0N.1<br>CMP1N.1<br>EXREGSN     |

| PB3.2    | 5 V Tolerant I/O | 8           | XBR1                                             | ~           |                     | DAC0T2<br>DAC1T2<br>LPT0T2<br>INT0.2<br>INT1.3<br>WAKE.14 | CMP0P.2<br>CMP1P.2<br>EXREGOUT    |

| PB3.3    | 5 V Tolerant I/O | 7           | XBR1                                             | ~           |                     | DAC0T3<br>DAC1T3<br>INT0.3<br>INT1.3<br>WAKE.15           | CMP0N.2<br>CMP1N.2<br>EXREGBD     |

| PB4.0    | High Drive I/O   | 6           |                                                  |             |                     |                                                           |                                   |

| PB4.1    | High Drive I/O   | 5           |                                                  |             |                     |                                                           |                                   |

| PB4.2    | High Drive I/O   | 4           |                                                  |             |                     |                                                           |                                   |

| PB4.3    | High Drive I/O   | 1           |                                                  |             |                     |                                                           |                                   |

## Table 6.3. Pin Definitions and Alternate Functions for SiM3C1x4 (Continued)

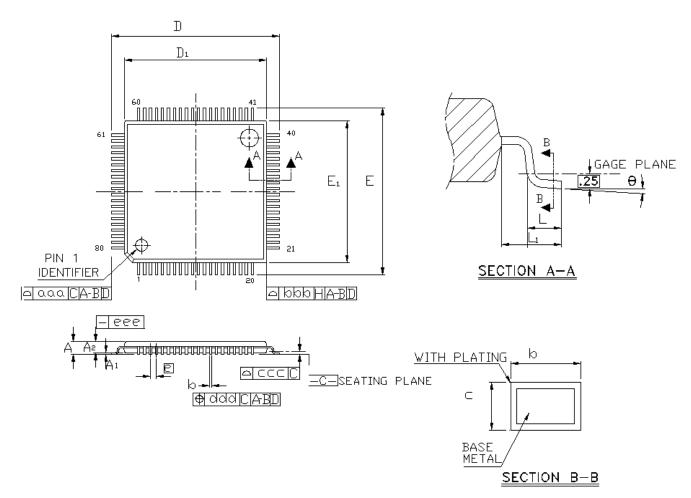

Figure 6.8. TQFP-80 Package Drawing

| Dimension | Min       | Nominal | Max  |

|-----------|-----------|---------|------|

| A         |           | —       | 1.20 |

| A1        | 0.05      | —       | 0.15 |

| A2        | 0.95      | 1.00    | 1.05 |

| b         | 0.17      | 0.20    | 0.27 |

| С         | 0.09      | —       | 0.20 |

| D         | 14.00 BSC |         |      |

| D1        | 12.00 BSC |         |      |

| е         | 0.50 BSC  |         |      |

| E         | 14.00 BSC |         |      |

| E1        | 12.00 BSC |         |      |

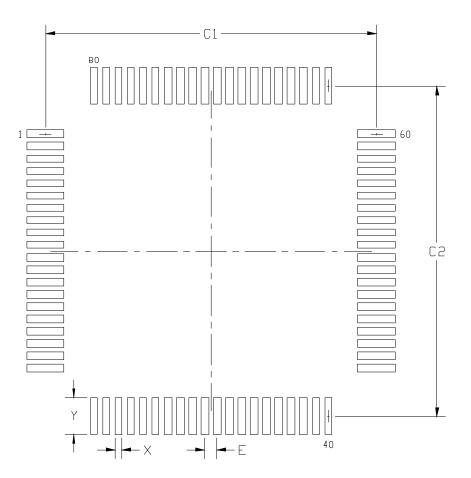

| Table 6.7. TQFP-80 Landing | <b>Diagram Dimensions</b> |

|----------------------------|---------------------------|

|----------------------------|---------------------------|

| Dimension | Min                     | Max                   |  |

|-----------|-------------------------|-----------------------|--|

| C1        | 13.30                   | 13.40                 |  |

| C2        | 13.30                   | 13.40                 |  |

| E         | 0.50 BSC                |                       |  |

| X         | 0.20                    | 0.30                  |  |

| Y         | 1.40                    | 1.50                  |  |

| noted.    | wn are in millimeters ( | (mm) unless otherwise |  |

2. This land pattern design is based on the IPC-7351 guidelines.

## DOCUMENT CHANGE LIST

## **Revision 0.8 to Revision 1.0**

- Added block diagram to front page; updated feature bullet lists.

- Electrical Specifications Tables Additions:

- Voltage Regulator Current Sense Supply Current, Typ =  $3 \mu A$  (Table 3.2)

- Power Mode 2 Wake Time, Min = 4 clocks, Max = 5 clocks (Table 3.3)

- External Crystal Clock Frequency, Min = 0.01 MHz, Max = 30 MHz (Table 3.9)

- Added /RESET pin characteristics (Table 3.17)

- Electrical Specifications Tables Removals:

- Power Mode 3 Wake Time (Table 3.3)

- Electrical Specifications Tables Corretions/Adjustments:

- IVC Supply Current, Max = 2.5 μA (Table 3.2)

- VREG0 Output Voltage Normal Mode, Min = 3.15 V (Table 3.5)

- VREG0 Output Voltage Suspend Mode, Min = 3.15 V (Table 3.5)

- External Regulator Internal Pull-Down, Typ = 5 k $\Omega$  (Table 3.6)

- External Regulator Internal Pull-Up, Typ = 10 k $\Omega$  (Table 3.6)

- Flash Memory Endurance, Typ = 100k write/erase cycles (Table 3.7)

- Flash Memory Retention, Min = 10 Years, Typ = 100 Years (Table 3.7)

- Low Power Oscillator Frequency, Min = 19.5 MHz, Max = 20.5 MHz (Table 3.8)

- SAR Dynamic Performance : consolidated all specs. (Table 3.10)

- IDAC Full Scale Output Current 1 mA Range, Min = 0.99 mA (Table 3.11)

- IDAC Full Scale Output Current 0.5 mA Range, Min = 493 μA (Table 3.11)

- IVC Slope @ 1 mA, Min = 1.55 V/mA, Max = 1.75 V/mA (Table 3.13)

- IVC Slope @ 2 mA, Min = 795 mV/mA, Max = 860 mV/mA (Table 3.13)

- IVC Slope @ 3 mA, Min = 525 mV/mA, Max = 570 mV/mA (Table 3.13)

- IVC Slope @ 4 mA, Min = 390 mV/mA, Max = 430 mV/mA (Table 3.13)

- IVC Slope @ 5 mA, Min = 315 mV/mA (Table 3.13)

- IVC Slope @ 6 mA, Min = 260 mV/mA (Table 3.13)

- Temperature Sensor Slope Error, Type =  $\pm 120 \,\mu$ V/C (Table 3.15)

- Comparator Input Offset Voltage, Min = -10 mV, Max = 10 mV (Table 3.16)

- "4. Precision32<sup>TM</sup> SiM3C1xx System Overview":

- Updated Power Modes discussion.

- Refined and updated feature bullet lists.

- Updated and clarified RTC timer clock output. The RTC output is now referred to as "RTC0TCLK".

- "6. Pin Definitions and Packaging Information": Renamed RTC0OSC\_OUT function to RTC0TCLK\_OUT for consistency.

- "7. Revision Specific Behavior": Updated revision identification drawings to better match physical appearance of packages.