# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                 |

| Core Size                  | 32-Bit Single-Core                                              |

| Speed                      | 80MHz                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT    |

| Number of I/O              | 28                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 16K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 18x12b; D/A 2x10b                                           |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 40-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 40-QFN (6x6)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/sim3u144-b-gm |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

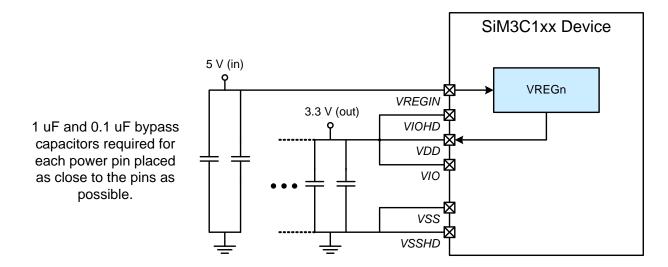

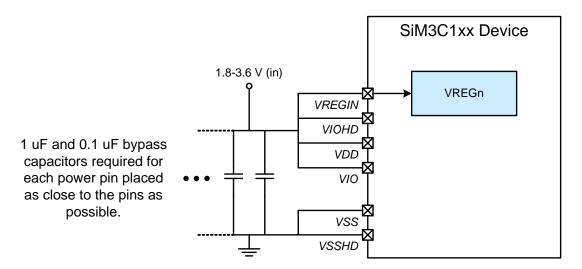

## 2. Typical Connection Diagrams

This section provides typical connection diagrams for SiM3C1xx devices.

#### 2.1. Power

Figure 2.1 shows a typical connection diagram for the power pins of the SiM3C1xx devices when the internal regulator is in use.

Figure 2.1. Connection Diagram with Voltage Regulator Used

Figure 2.2 shows a typical connection diagram for the power pins of the SiM3C1xx devices when the internal regulator is not used.

Figure 2.2. Connection Diagram with Voltage Regulator Not Used

# 3. Electrical Specifications

## **3.1. Electrical Characteristics**

All electrical parameters in all tables are specified under the conditions listed in Table 3.1, unless stated otherwise.

Table 3.1. Recommended Operating Conditions

| Parameter                                         | Symbol             | Test Condition                       | Min               | Тур | Max                                                              | Unit |

|---------------------------------------------------|--------------------|--------------------------------------|-------------------|-----|------------------------------------------------------------------|------|

| Operating Supply Voltage on VDD                   | V <sub>DD</sub>    |                                      | 1.8               |     | 3.6                                                              | V    |

| Operating Supply Voltage on VREGIN                | V <sub>REGIN</sub> | EXTVREG0 Not Used                    | 4                 | _   | 5.5                                                              | V    |

|                                                   |                    | EXTVREG0 Used                        | 3.0               |     | 3.6                                                              | V    |

| Operating Supply Voltage on VIO                   | V <sub>IO</sub>    |                                      | 1.8               | —   | V <sub>DD</sub>                                                  | V    |

| Operating Supply Voltage on VIOHD                 | V <sub>IOHD</sub>  | HV Mode (default)                    | 2.7               | —   | 6.0                                                              | V    |

|                                                   |                    | LV Mode                              | 1.8               |     | 3.6                                                              | V    |

| Voltage on I/O pins, Port Bank 0, 1<br>and 2 I/O  | V <sub>IN</sub>    |                                      | V <sub>SS</sub>   | —   | V <sub>IO</sub>                                                  | V    |

| Voltage on I/O pins, Port Bank 3 I/O<br>and RESET | V <sub>IN</sub>    | SiM3C1x7<br>PB3.0–PB3.7 and<br>RESET | V <sub>SS</sub>   | —   | V <sub>IO</sub> +2.0                                             | V    |

|                                                   |                    | SiM3C1x7<br>PB3.8 - PB3.11           | V <sub>SS</sub>   | _   | Lowest<br>of<br>V <sub>IO</sub> +2.0<br>or<br>V <sub>REGIN</sub> | V    |

|                                                   |                    | SiM3C1x6<br>PB3.0–PB3.5 and<br>RESET | V <sub>SS</sub>   | _   | V <sub>IO</sub> +2.0                                             | V    |

|                                                   |                    | SiM3C1x6<br>PB3.6–PB3.9              | V <sub>SS</sub>   | _   | Lowest<br>of<br>V <sub>IO</sub> +2.0<br>or<br>V <sub>REGIN</sub> | V    |

|                                                   |                    | SiM3C1x4<br>RESET                    | V <sub>SS</sub>   | _   | V <sub>IO</sub> +2.0                                             | V    |

|                                                   |                    | SiM3C1x4<br>PB3.0–PB3.3              | V <sub>SS</sub>   | _   | Lowest<br>of<br>V <sub>IO</sub> +2.0<br>or<br>V <sub>REGIN</sub> | V    |

| Voltage on I/O pins, Port Bank 4 I/O              | V <sub>IN</sub>    |                                      | V <sub>SSHD</sub> |     | V <sub>IOHD</sub>                                                | V    |

| System Clock Frequency (AHB)                      | f <sub>AHB</sub>   |                                      | 0                 |     | 80                                                               | MHz  |

| Peripheral Clock Frequency (APB)                  | f <sub>APB</sub>   |                                      | 0                 |     | 50                                                               | MHz  |

| Operating Ambient Temperature                     | T <sub>A</sub>     |                                      | -40               |     | 85                                                               | °C   |

| Operating Junction Temperature                    | TJ                 |                                      | -40               |     | 105                                                              | °C   |

| Note: All voltages with respect to $V_{SS}$ .     | <u> </u>           | ,                                    | ı                 |     | ļ.                                                               |      |

| Table 3.2. Power Co | nsumption | (Continued) |

|---------------------|-----------|-------------|

|---------------------|-----------|-------------|

| Parameter                            | Symbol               | Test Condition                                               | Min | Тур  | Max  | Unit |

|--------------------------------------|----------------------|--------------------------------------------------------------|-----|------|------|------|

| Analog Peripheral Supply Current     | ts                   |                                                              | 1   |      |      |      |

| Voltage Regulator (VREG0)            | I <sub>VREGIN</sub>  | Normal Mode, T <sub>A</sub> = 25 °C<br>BGDIS = 0, SUSEN = 0  |     | 300  |      | μA   |

|                                      |                      | Normal Mode, $T_A = 85 \degree C$<br>BGDIS = 0, SUSEN = 0    | _   |      | 650  | μA   |

|                                      |                      | Suspend Mode, T <sub>A</sub> = 25 °C<br>BGDIS = 0, SUSEN = 1 | _   | 75   |      | μA   |

|                                      |                      | Suspend Mode, T <sub>A</sub> = 85 °C<br>BGDIS = 0, SUSEN = 1 | _   |      | 115  | μA   |

|                                      |                      | Sleep Mode, T <sub>A</sub> = 25 °C<br>BGDIS = 1, SUSEN = X   | _   | 90   | _    | nA   |

|                                      |                      | Sleep Mode, T <sub>A</sub> = 85 °C<br>BGDIS = 1, SUSEN = X   | _   | _    | 500  | nA   |

| Voltage Regulator (VREG0) Sense      | I <sub>VRSENSE</sub> | SENSEEN = 1                                                  |     | 3    |      | μA   |

| External Regulator (EXTVREG0)        | I <sub>EXTVREG</sub> | Regulator                                                    | _   | 215  | 250  | μA   |

|                                      |                      | Current Sensor                                               |     | 7    | —    | μA   |

| PLL0 Oscillator (PLL0OSC)            | I <sub>PLLOSC</sub>  | Operating at 80 MHz                                          | _   | 1.75 | 1.86 | mA   |

| Low-Power Oscillator (LPOSC0)        | I <sub>LPOSC</sub>   | Operating at 20 MHz                                          |     | 190  | —    | μA   |

|                                      |                      | Operating at 2.5 MHz                                         |     | 40   | _    | μA   |

| Low-Frequency Oscillator<br>(LFOSC0) | I <sub>LFOSC</sub>   | Operating at 16.4 kHz,<br>T <sub>A</sub> = 25 °C             | _   | 215  |      | nA   |

|                                      |                      | Operating at 16.4 kHz,<br>T <sub>A</sub> = 85 °C             | _   |      | 500  | nA   |

Notes:

1. Perhipheral currents drop to zero when peripheral clock and peripheral are disabled, unless otherwise noted.

Currents are additive. For example, where I<sub>DD</sub> is specified and the mode is not mutually exclusive, enabling the functions increases supply current by the specified amount.

3. Includes all peripherals that cannot have clocks gated in the Clock Control module.

4. Includes supply current from internal regulator and PLL0OSC (>20 MHz) or LPOSC0 (<=20 MHz).

5. Flash execution numbers use 2 wait states for 80 MHz and 0 wait states at 20 MHz or less.

6. RAM execution numbers use 0 wait states for all frequencies.

7. IDAC output current and IVC input current not included.

8. Bias current only. Does not include dynamic current from oscillator running at speed.

Table 3.11. IDAC

| Parameter                                        | Symbol            | Test Condition              | Min      | Тур   | Max                   | Unit   |

|--------------------------------------------------|-------------------|-----------------------------|----------|-------|-----------------------|--------|

| Static Performance                               | L                 |                             | 1        | 1     |                       |        |

| Resolution                                       | N <sub>bits</sub> |                             |          | 10    |                       | Bits   |

| Integral Nonlinearity                            | INL               |                             |          | ±0.5  | ±2                    | LSB    |

| Differential Nonlinearity (Guaranteed Monotonic) | DNL               |                             |          | ±0.5  | ±1                    | LSB    |

| Output Compliance Range                          | V <sub>OCR</sub>  |                             |          |       | V <sub>DD</sub> – 1.0 | V      |

| Full Scale Output Current                        | I <sub>OUT</sub>  | 2 mA Range                  | 2.0      | 2.046 | 2.10                  | mA     |

|                                                  |                   | 1 mA Range                  | 0.99     | 1.023 | 1.05                  | mA     |

|                                                  |                   | 0.5 mA Range                | 493      | 511.5 | 525                   | μA     |

| Offset Error                                     | E <sub>OFF</sub>  |                             |          | 250   | _                     | nA     |

| Full Scale Error Tempco                          | TC <sub>FS</sub>  | 2 mA Range                  |          | 100   | —                     | ppm/°C |

| VDD Power Supply Rejection Ratio                 |                   | 2 mA Range                  |          | -220  | —                     | ppm/V  |

| Test Load Impedance (to V <sub>SS</sub> )        | R <sub>TEST</sub> |                             |          | 1     | —                     | kΩ     |

| Dynamic Performance                              |                   |                             |          |       |                       |        |

| Output Settling Time to 1/2 LSB                  |                   | min output to max<br>output |          | 1.2   | _                     | μs     |

| Startup Time                                     |                   |                             | <u> </u> | 3     | —                     | μs     |

#### Table 3.14. Voltage Reference Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                    | Symbol                                                                | Test Condition                          | Min   | Тур  | Max   | Unit   |

|------------------------------|-----------------------------------------------------------------------|-----------------------------------------|-------|------|-------|--------|

| Internal Fast Settling Refer | ence                                                                  |                                         |       |      |       |        |

| Output Voltage               | Voltage $V_{\text{REFFS}}$ -40 to +85 °C, $V_{\text{DD}}$ = 1.8-3.6 V |                                         |       |      | 1.68  | V      |

| Temperature Coefficient      | TC <sub>REFFS</sub>                                                   |                                         | —     | 50   | _     | ppm/°C |

| Turn-on Time                 | t <sub>REFFS</sub>                                                    |                                         | —     |      | 1.5   | μs     |

| Power Supply Rejection       | PSRR <sub>REFFS</sub>                                                 |                                         | —     | 400  | _     | ppm/V  |

| On-Chip Precision Referen    | ce (VREF0)                                                            |                                         |       |      |       |        |

| Valid Supply Range           | V <sub>DD</sub>                                                       | VREF2X = 0                              | 1.8   |      | 3.6   | V      |

|                              |                                                                       | VREF2X = 1                              | 2.7   | _    | 3.6   | V      |

| Output Voltage               | V <sub>REFP</sub>                                                     | 25 °C ambient,<br>VREF2X = 0            | 1.195 | 1.2  | 1.205 | V      |

|                              |                                                                       | 25 °C ambient,<br>VREF2X = 1            | 2.39  | 2.4  | 2.41  | V      |

| Short-Circuit Current        | I <sub>SC</sub>                                                       |                                         | —     |      | 10    | mA     |

| Temperature Coefficient      | TC <sub>VREFP</sub>                                                   |                                         | —     | 25   | _     | ppm/°C |

| Load Regulation              | LR <sub>VREFP</sub>                                                   | Load = 0 to 200 µA to<br>VREFGND        | —     | 4.5  | _     | ppm/µA |

| Load Capacitor               | C <sub>VREFP</sub>                                                    | Load = 0 to 200 µA to<br>VREFGND        | 0.1   | _    | _     | μF     |

| Turn-on Time                 | t <sub>VREFPON</sub>                                                  | 4.7 μF tantalum, 0.1 μF ceramic bypass  | _     | 3.8  | _     | ms     |

|                              |                                                                       | 0.1 µF ceramic bypass                   | —     | 200  | —     | μs     |

| Power Supply Rejection       | PSRR <sub>VREFP</sub>                                                 | VREF2X = 0                              | —     | 320  | —     | ppm/V  |

|                              |                                                                       | VREF2X = 1                              | —     | 560  | —     | ppm/V  |

| External Reference           |                                                                       | •                                       |       |      |       | •      |

| Input Current                | IEXTREF                                                               | Sample Rate = 250 ksps;<br>VREF = 3.0 V | —     | 5.25 | _     | μA     |

## Table 3.16. Comparator

| Parameter                 | Symbol             | Test Condition       | Min | Тур  | Max | Unit |

|---------------------------|--------------------|----------------------|-----|------|-----|------|

| Response Time, CMPMD = 00 | t <sub>RESP0</sub> | +100 mV Differential |     | 100  | _   | ns   |

| (Highest Speed)           |                    | -100 mV Differential | _   | 150  | _   | ns   |

| Response Time, CMPMD = 11 | t <sub>RESP3</sub> | +100 mV Differential | _   | 1.4  | _   | μs   |

| (Lowest Power)            |                    | -100 mV Differential |     | 3.5  | _   | μs   |

| Positive Hysteresis       | HYS <sub>CP+</sub> | CMPHYP = 00          | _   | 0.4  | _   | mV   |

| Mode 0 (CPMD = 00)        |                    | CMPHYP = 01          | _   | 8    | _   | mV   |

|                           |                    | CMPHYP = 10          |     | 16   | _   | mV   |

|                           |                    | CMPHYP = 11          | _   | 33   |     | mV   |

| Negative Hysteresis       | HYS <sub>CP-</sub> | CMPHYN = 00          | _   | 0.4  | _   | mV   |

| Mode 0 (CPMD = 00)        |                    | CMPHYN = 01          |     | -8   | _   | mV   |

|                           |                    | CMPHYN = 10          | _   | -16  | _   | mV   |

|                           |                    | CMPHYN = 11          | _   | -33  |     | mV   |

| Positive Hysteresis       | HYS <sub>CP+</sub> | CMPHYP = 00          |     | 0.5  | _   | mV   |

| Mode 1 (CPMD = 01)        |                    | CMPHYP = 01 —        |     | 6    | _   | mV   |

|                           |                    | CMPHYP = 10          |     | 12   | _   | mV   |

|                           |                    | CMPHYP = 11          | _   | 24   | _   | mV   |

| Negative Hysteresis       | HYS <sub>CP-</sub> | CMPHYN = 00          |     | 0.5  | _   | mV   |

| Mode 1 (CPMD = 01)        |                    | CMPHYN = 01          |     | -6.0 | _   | mV   |

|                           |                    | CMPHYN = 10          | _   | -12  | _   | mV   |

|                           |                    | CMPHYN = 11          |     | -24  | _   | mV   |

| Positive Hysteresis       | HYS <sub>CP+</sub> | CMPHYP = 00          |     | 0.6  | _   | mV   |

| Mode 2 (CPMD = 10)        |                    | CMPHYP = 01          | _   | 4.5  | _   | mV   |

|                           |                    | CMPHYP = 10          | _   | 9.5  | _   | mV   |

|                           |                    | CMPHYP = 11          |     | 19   | _   | mV   |

| Negative Hysteresis       | HYS <sub>CP-</sub> | CMPHYN = 00          | _   | 0.6  | —   | mV   |

| Mode 2 (CPMD = 10)        |                    | CMPHYN = 01          | _   | -4.5 | —   | mV   |

|                           |                    | CMPHYN = 10          | _   | -9.5 | —   | mV   |

|                           |                    | CMPHYN = 11          |     | -19  | _   | mV   |

| Table 3.19. Absolute Maximum | <b>Ratings (Continued)</b> |

|------------------------------|----------------------------|

|------------------------------|----------------------------|

| Parameter                                                                 | Symbol | Test Condition                 | Min              | Max                | Unit    |

|---------------------------------------------------------------------------|--------|--------------------------------|------------------|--------------------|---------|

| Power Dissipation at T <sub>A</sub> = 85 °C                               | PD     | LGA-92 Package                 |                  | 570                | mW      |

|                                                                           |        | TQFP-80 Package                | —                | 500                | mW      |

|                                                                           |        | QFN-64 Package                 | —                | 800                | mW      |

|                                                                           |        | TQFP-64 Package                |                  | 650                | mW      |

|                                                                           | -      | QFN-40 Package                 | —                | 650                | mW      |

| *Note: VSS and VSSHD provide separat<br>connected to the same potential o |        | ent paths for device supplies, | but are not isol | ated. They must al | ways be |

## 4.2. I/O

#### 4.2.1. General Features

The SiM3C1xx ports have the following features:

- Push-pull or open-drain output modes and analog or digital modes.

- Option for high or low output drive strength.

- Port Match allows the device to recognize a change on a port pin value.

- Internal pull-up resistors are enabled or disabled on a port-by-port basis.

- Two external interrupts with up to 16 inputs provide monitoring capability for external signals.

- Internal Pulse Generator Timer (PB2 only) to generate simple square waves.

- A subset of pins can also serve as inputs to the Port Mapped Level Shifters available on the High Drive Pins.

#### 4.2.2. High Drive Pins (PB4)

The High Drive pins have the following additional features:

- Programmable safe state: high, low, or high impedance.

- Programmable drive strength and slew rates.

- Programmable hardware current limiting.

- Powered from a separate source (VIOHD, which can be up to 6 V) from the rest of the device.

- Supports various functions, including GPIO, UART1 pins, EPCA0 pins, or Port Mapped Level Shifting.

#### 4.2.3. 5 V Tolerant Pins (PB3)

The 5 V tolerant pins can be connected to external circuitry operating at voltages above the device supply without needing extra components to shift the voltage level.

#### 4.2.4. Crossbars

The SiM3C1xx devices have two Crossbars with the following features:

- Flexible peripheral assignment to port pins.

- Pins can be individually skipped to move peripherals as needed for design or layout considerations.

The Crossbars have a fixed priority for each I/O function and assign these functions to the port pins. When a digital resource is selected, the least-significant unassigned port pin is assigned to that resource. If a port pin is assigned, the Crossbars skip that pin when assigning the next selected resource. Additionally, the Crossbars will skip port pins whose associated bits in the PBSKIPEN registers are set. This provides some flexibility when designing a system: pins involved with sensitive analog measurements can be moved away from digital I/O and peripherals can be moved around the chip as needed to ease layout constraints.

## 4.5. Counters/Timers and PWM

#### 4.5.1. Programmable Counter Array (EPCA0, PCA0, PCA1)

The SiM3C1xx devices include two types of PCA module: Enhanced and Standard.

The Enhanced Programmable Counter Array (EPCA0) and Standard Programmable Counter Array (PCA0, PCA1) modules are timer/counter systems allowing for complex timing or waveform generation. Multiple modules run from the same main counter, allowing for synchronous output waveforms.

The Enhanced PCA module is multi-purpose, but is optimized for motor control applications. The EPCA module includes the following features:

- Three sets of channel pairs (six channels total) capable of generating complementary waveforms.

- Center- and edge-aligned waveform generation.

- Programmable dead times that ensure channel pairs are never both active at the same time.

- Programmable clock divisor and multiple options for clock source selection.

- Waveform update scheduling.

- Option to function while the core is inactive.

- Multiple synchronization triggers and outputs.

- Pulse-Width Modulation (PWM) waveform generation.

- High-speed square wave generation.

- Input capture mode.

- DMA capability for both input capture and waveform generation.

- PWM generation halt input.

The Standard PCA module (PCA) includes the following features:

- Two independent channels.

- Center- and edge-aligned waveform generation.

- Programmable clock divisor and multiple options for clock source selection.

- Pulse-Width Modulation waveform generation.

#### 4.5.2. 32-bit Timer (TIMER0, TIMER1)

Each timer module is independent, and includes the following features:

- Operation as a single 32-bit or two independent 16-bit timers.

- Clocking options include the APB clock, the APB clock scaled using an 8-bit prescaler, the external oscillator, or falling edges on an external input pin (synchronized to the APB clock).

- Auto-reload functionality in both 32-bit and 16-bit modes.

- Up/Down count capability, controlled by an external input pin.

- Rising and falling edge capture modes.

- Low or high pulse capture modes.

- Duty cycle capture mode.

- Square wave output mode, which is capable of toggling an external pin at a given rate with 50% duty cycle.

- 32- or 16-bit pulse-width modulation mode.

## 4.7. Analog

#### 4.7.1. 12-Bit Analog-to-Digital Converters (SARADC0, SARADC1)

The SARADC0 and SARADC1 modules on SiM3C1xx devices are Successive Approximation Register (SAR) Analog to Digital Converters (ADCs). The key features of the SARADC module are:

- Single-ended 12-bit and 10-bit modes.

- Supports an output update rate of 250 k samples per second in 12-bit mode or 1 M samples per second in 10-bit mode.

- Operation in low power modes at lower conversion speeds.

- Selectable asynchronous hardware conversion trigger with hardware channel select.

- Output data window comparator allows automatic range checking.

- Support for Burst Mode, which produces one set of accumulated data per conversion-start trigger with programmable power-on settling and tracking time.

- Conversion complete, multiple conversion complete, and FIFO overflow and underflow flags and interrupts supported.

- Flexible output data formatting.

- Sequencer allows up to 8 sources to be automatically scanned using one of four channel characteristic profiles without software intervention.

- Eight-word conversion data FIFO for DMA operations.

- Multiple SARADC modules can work together synchronously or by interleaving samples.

- Includes two internal references (1.65 V fast-settling, 1.2/2.4 V precision), support for an external reference, and support for an external signal ground.

#### 4.7.2. Sample Sync Generator (SSG0)

The SSG module includes a phase counter and a pulse generator. The phase counter is a 4-bit free-running counter clocked from the SARADC module clock. Counting-up from zero, the phase counter marks sixteen equally-spaced events for any number of SARADC modules. The ADCs can use this phase counter to start a conversion. The programmable pulse generator creates a 50% duty cycle pulse with a period of 16 phase counter ticks. Up to four programmable outputs available to external devices can be driven by the pulse generator with programmable polarity and a defined output setting when the pulse generator is stopped.

The Sample Sync Generator module has the following features:

- Connects multiple modules together to perform synchronized actions.

- Outputs a clock synchronized to the internal sampling clock used by any number of SARADC modules to pins for use by external devices.

- Includes a phase counter, pulse generator, and up to four programmable outputs.

#### 4.7.3. 10-Bit Digital-to-Analog Converter (IDAC0, IDAC1)

The IDAC takes a digital value as an input and outputs a proportional constant current on a pin. The IDAC module includes the following features:

- 10-bit current DAC with support for four timer, up to seven external I/O, on demand, and SSG0 output update triggers.

- Ability to update on rising, falling, or both edges for any of the external I/O trigger sources (DACnTx).

- Supports an output update rate greater than 600 k samples per second.

- Support for three full-scale output modes: 0.5 mA, 1.0 mA and 2.0 mA.

- Four-word FIFO to aid with high-speed waveform generation or DMA interactions.

- Individual FIFO overrun, underrun, and went-empty interrupt status sources.

- Support for multiple data packing formats, including: single 10-bit sample per word, dual 10-bit samples per word, or four 8-bit samples per word.

- Support for left- and right-justified data.

| Table 6.1. Pin Definitions and alternate | e functions for SiM3C1x7 | (Continued) |

|------------------------------------------|--------------------------|-------------|

|------------------------------------------|--------------------------|-------------|

| Din Nama                       | Torre                     | Pin Numbers TQFP-80 | Pin Numbers LGA-92 | Crossbar Capability<br>(see Port Config Section) | Port Match   | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs    | Analog or Additional<br>Functions |

|--------------------------------|---------------------------|---------------------|--------------------|--------------------------------------------------|--------------|-----------------------------------------------|---------------------------|---------------------|----------------------------|-----------------------------------|

| Pin Name<br>PB1.9/<br>TRACECLK | Type<br>Standard I/O /ETM | <b>ä</b><br>46      | <b>ā</b><br>A28    | <b>ن</b> ق<br>XBR0                               | <u>√</u>     | ά£                                            | Рс                        | õ                   | <u>ش</u>                   | <b>ਪ</b> ਛੋ<br>ADC1.9             |

| PB1.10                         | Standard I/O              | 43                  | A26                | XBR0                                             | ~            | A23m/<br>A15                                  |                           |                     | DMA0T1                     | ADC1.8                            |

| PB1.11                         | Standard I/O              | 42                  | A25                | XBR0                                             | ~            | A22m/<br>A14                                  |                           |                     | DMA0T0                     | ADC1.7                            |

| PB1.12                         | Standard I/O              | 41                  | D3                 | XBR0                                             | ~            | A21m/<br>A13                                  |                           |                     |                            | ADC1.6                            |

| PB1.13                         | Standard I/O              | 40                  | A24                | XBR0                                             | ~            | A20m/<br>A12                                  |                           |                     | ADC0T15<br>WAKE.0          | ADC1.5<br>CS0.10                  |

| PB1.14                         | Standard I/O              | 39                  | A23                | XBR0                                             | ~            | A19m/<br>A11                                  |                           |                     | ADC1T15<br>WAKE.1          | ADC1.4<br>CS0.11                  |

| PB1.15                         | Standard I/O              | 38                  | A22                | XBR0                                             | ~            | A18m/<br>A10                                  |                           |                     | WAKE.2                     | ADC1.3<br>CS0.12                  |

| PB2.0                          | Standard I/O              | 37                  | B17                | XBR1                                             | V            | A17m/<br>A9                                   | LSI0                      | Yes                 | INT0.0<br>INT1.0<br>WAKE.3 | ADC1.2<br>CS0.13                  |

| PB2.1                          | Standard I/O              | 36                  | A21                | XBR1                                             | ~            | A16m/<br>A8                                   | LSI1                      | Yes                 | INT0.1<br>INT1.1<br>WAKE.4 | ADC1.1<br>CS0.14                  |

| PB2.2                          | Standard I/O              | 35                  | B16                | XBR1                                             | ~            | AD15m/<br>A7                                  | LSI2                      | Yes                 | INT0.2<br>INT1.2<br>WAKE.5 | ADC1.0<br>CS0.15<br>PMU_Asleep    |

| PB2.3                          | Standard I/O              | 34                  | A20                | XBR1                                             | ~            | AD14m/<br>A6                                  | LSI3                      | Yes                 | INT0.3<br>INT1.3<br>WAKE.6 |                                   |

| PB2.4                          | Standard I/O              | 31                  | B14                | XBR1                                             | ~            | AD13m/<br>A5                                  | LSI4                      | Yes                 | INT0.4<br>INT1.4<br>WAKE.7 |                                   |

| PB2.5                          | Standard I/O              | 30                  | A18                | XBR1                                             | $\checkmark$ | AD12m /<br>A4                                 | LSI5                      | Yes                 | INT0.5<br>INT1.5           |                                   |

| r        |                  | 1                   |                    |                                                  | -            |                                               |                           |                     |                                      | 1                                        |

|----------|------------------|---------------------|--------------------|--------------------------------------------------|--------------|-----------------------------------------------|---------------------------|---------------------|--------------------------------------|------------------------------------------|

| Pin Name | Туре             | Pin Numbers TQFP-80 | Pin Numbers LGA-92 | Crossbar Capability<br>(see Port Config Section) | Port Match   | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs              | <b>Analog or Additional</b><br>Functions |

| PB2.6    | Standard I/O     | 29                  | B13                | XBR1                                             | ~            | AD11m/<br>A3                                  |                           | Yes                 | INT0.6<br>INT1.6                     |                                          |

| PB2.7    | Standard I/O     | 28                  | A17                | XBR1                                             | ~            | AD10m/<br>A2                                  |                           | Yes                 | INT0.7<br>INT1.7                     |                                          |

| PB2.8    | Standard I/O     | 27                  | B12                | XBR1                                             | $\checkmark$ | AD9m/<br>A1                                   |                           | Yes                 |                                      |                                          |

| PB2.9    | Standard I/O     | 26                  | A16                | XBR1                                             | $\checkmark$ | AD8m/<br>A0                                   |                           | Yes                 |                                      |                                          |

| PB2.10   | Standard I/O     | 25                  | B11                | XBR1                                             | ~            | AD7m/<br>D7                                   |                           | Yes                 |                                      |                                          |

| PB2.11   | Standard I/O     | 24                  | A15                | XBR1                                             | ~            | AD6m/<br>D6                                   |                           | Yes                 |                                      | CMP0P.0<br>CMP1P.0                       |

| PB2.12   | Standard I/O     | 23                  | A14                | XBR1                                             | $\checkmark$ | AD5m/<br>D5                                   |                           | Yes                 |                                      | CMP0N.0<br>CMP1N.0<br>RTC0TCLK_OUT       |

| PB2.13   | Standard I/O     | 22                  | A13                | XBR1                                             | $\checkmark$ | AD4m/<br>D4                                   |                           | Yes                 |                                      | CMP0P.1<br>CMP1P.1                       |

| PB2.14   | Standard I/O     | 21                  | D2                 | XBR1                                             | ~            | AD3m/<br>D3                                   |                           | Yes                 |                                      | CMP0N.1<br>CMP1N.1                       |

| PB3.0    | 5 V Tolerant I/O | 20                  | A12                | XBR1                                             | ~            | AD2m/<br>D2                                   |                           |                     |                                      | CMP0P.2<br>CMP1P.2                       |

| PB3.1    | 5 V Tolerant I/O | 19                  | A11                | XBR1                                             | $\checkmark$ | AD1m/<br>D1                                   |                           |                     |                                      | CMP0N.2<br>CMP1N.2                       |

| PB3.2    | 5 V Tolerant I/O | 18                  | A10                | XBR1                                             | $\checkmark$ | AD0m/<br>D0                                   |                           |                     | DAC0T0<br>DAC1T0<br>LPT0T0           | CMP0P.3<br>CMP1P.3                       |

| PB3.3    | 5 V Tolerant I/O | 17                  | B8                 | XBR1                                             | ~            | WR                                            |                           |                     | DAC0T1<br>DAC1T1<br>INT0.8<br>INT1.8 | CMP0N.3<br>CMP1N.3                       |

## Table 6.1. Pin Definitions and alternate functions for SiM3C1x7 (Continued)

| Pin Name                                                                                                                                                                            | Туре           | Pin Numbers TQFP-80 | Pin Numbers LGA-92 | Crossbar Capability<br>(see Port Config Section) | Port Match | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs | Analog or Additional<br>Functions |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------|--------------------|--------------------------------------------------|------------|-----------------------------------------------|---------------------------|---------------------|-------------------------|-----------------------------------|

| PB4.0                                                                                                                                                                               | High Drive I/O | 8                   | A6                 |                                                  |            |                                               | LSO0                      |                     |                         |                                   |

| PB4.1                                                                                                                                                                               | High Drive I/O | 7                   | A5                 |                                                  |            |                                               | LSO1                      |                     |                         |                                   |

| PB4.2                                                                                                                                                                               | High Drive I/O | 6                   | A4                 |                                                  |            |                                               | LSO2                      |                     |                         |                                   |

| PB4.3                                                                                                                                                                               | High Drive I/O | 3                   | A2                 |                                                  |            |                                               | LSO3                      |                     |                         |                                   |

| PB4.4                                                                                                                                                                               | High Drive I/O | 2                   | A1                 |                                                  |            |                                               | LSO4                      |                     |                         |                                   |

| PB4.5                                                                                                                                                                               | High Drive I/O | 1                   | D1                 |                                                  |            |                                               | LSO5                      |                     |                         |                                   |

| Note: All unnamed pins on the LGA-92 package are no-connect pins. They should be soldered to the PCB for mechanical stabil-<br>ity, but have no internal connections to the device. |                |                     |                    |                                                  |            |                                               |                           |                     |                         |                                   |

## Table 6.1. Pin Definitions and alternate functions for SiM3C1x7 (Continued)

| <b></b>            | 1                                           |             | r                                                |              | 1                                             | 1                         | 1                   |                         | ,                                 |

|--------------------|---------------------------------------------|-------------|--------------------------------------------------|--------------|-----------------------------------------------|---------------------------|---------------------|-------------------------|-----------------------------------|

| Pin Name           | Туре                                        | Pin Numbers | Crossbar Capability<br>(see Port Config Section) | Port Match   | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs | Analog or Additional<br>Functions |

| PB0.7              | Standard I/O                                | 50          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | RTC2                              |

| PB0.8              | Standard I/O                                | 49          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC0.9<br>VREFGND                 |

| PB0.9              | Standard I/O                                | 48          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC0.10<br>VREF                   |

| PB0.10             | Standard I/O                                | 47          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC1.6<br>IDAC0                   |

| PB0.11             | Standard I/O                                | 46          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | IDAC1                             |

| PB0.12             | Standard I/O                                | 45          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | XTAL1                             |

| PB0.13             | Standard I/O                                | 44          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | XTAL2                             |

| PB0.14/TDO/<br>SWV | Standard I/O / JTAG<br>/ Serial Wire Viewer | 43          | XBR0                                             | ~            |                                               |                           |                     |                         | ADC0.12<br>ADC1.12                |

| PB0.15/TDI         | Standard I/O / JTAG                         | 42          | XBR0                                             | ~            |                                               |                           |                     |                         | ADC0.13<br>ADC1.13                |

| PB1.0              | Standard I/O                                | 41          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC0.14<br>ADC1.14                |

| PB1.1              | Standard I/O                                | 40          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC0.15<br>ADC1.15                |

| PB1.2              | Standard I/O                                | 38          | XBR0                                             | ~            |                                               |                           |                     |                         | ADC1.11<br>CS0.8                  |

| PB1.3              | Standard I/O                                | 37          | XBR0                                             | ~            |                                               |                           |                     |                         | ADC1.10<br>CS0.9                  |

| PB1.4              | Standard I/O                                | 34          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC1.8                            |

| PB1.5              | Standard I/O                                | 33          | XBR0                                             | $\checkmark$ |                                               |                           |                     |                         | ADC1.7                            |

| PB1.6              | Standard I/O                                | 32          | XBR0                                             | ~            |                                               |                           |                     | ADC0T15<br>WAKE.0       | ADC1.5<br>CS0.10                  |

| PB1.7              | Standard I/O                                | 31          | XBR0                                             | $\checkmark$ | AD15m/<br>A7                                  |                           |                     | ADC1T15<br>WAKE.1       | ADC1.4<br>CS0.11                  |

## Table 6.2. Pin Definitions and alternate functions for SiM3C1x6 (Continued)

| Pin Name | Туре             | Pin Numbers | Crossbar Capability<br>(see Port Config Section) | Port Match | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs                                     | Analog or Additional<br>Functions |

|----------|------------------|-------------|--------------------------------------------------|------------|-----------------------------------------------|---------------------------|---------------------|-------------------------------------------------------------|-----------------------------------|

| PB3.9    | 5 V Tolerant I/O | 7           | XBR1                                             | ~          | BE0                                           |                           |                     | DAC0T6<br>DAC1T6<br>LPT0T2<br>INT0.10<br>INT1.10<br>WAKE.15 | CMP0N.5<br>CMP1N.5<br>EXREGBD     |

| PB4.0    | High Drive I/O   | 6           |                                                  |            |                                               | LSO0                      |                     |                                                             |                                   |

| PB4.1    | High Drive I/O   | 5           |                                                  |            |                                               | LSO1                      |                     |                                                             |                                   |

| PB4.2    | High Drive I/O   | 4           |                                                  |            |                                               | LSO2                      |                     |                                                             |                                   |

| PB4.3    | High Drive I/O   | 1           |                                                  |            |                                               | LSO3                      |                     |                                                             |                                   |

Table 6.2. Pin Definitions and alternate functions for SiM3C1x6 (Continued)

# SiM3C1xx

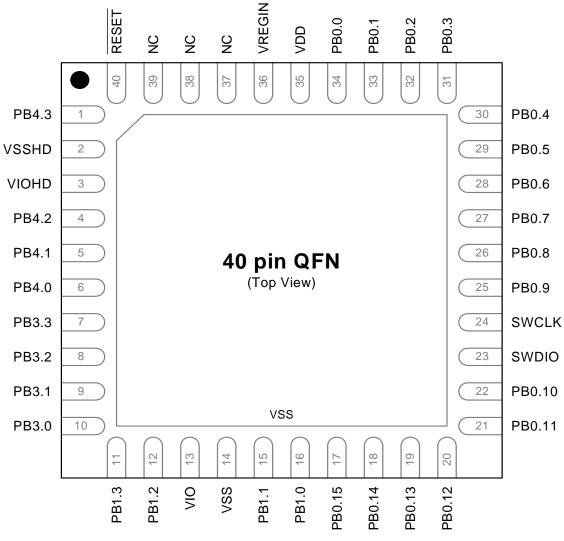

## 6.3. SiM3C1x4 Pin Definitions

Figure 6.5. SiM3C1x4-GM Pinout

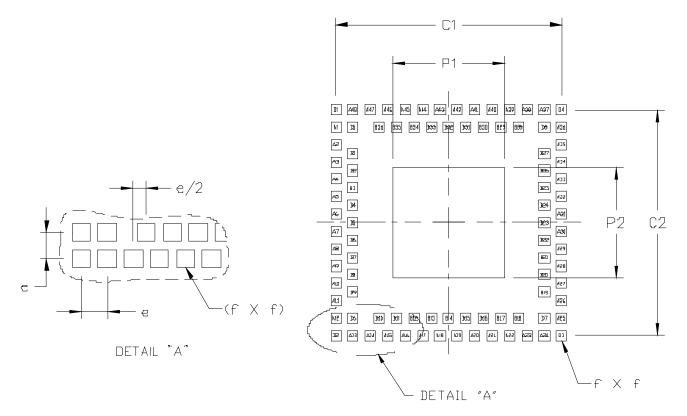

Figure 6.7. LGA-92 Landing Diagram

| Dimension                                                                                                                                                                                                                                       | Typical                                                     | Max  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|--|--|--|--|--|

| C1                                                                                                                                                                                                                                              | 6.50                                                        | —    |  |  |  |  |  |

| C2                                                                                                                                                                                                                                              | 6.50                                                        | _    |  |  |  |  |  |

| e                                                                                                                                                                                                                                               | 0.50                                                        | —    |  |  |  |  |  |

| f                                                                                                                                                                                                                                               | —                                                           | 0.35 |  |  |  |  |  |

| P1                                                                                                                                                                                                                                              | —                                                           | 3.20 |  |  |  |  |  |

| P2                                                                                                                                                                                                                                              | —                                                           | 3.20 |  |  |  |  |  |

| <ul> <li>Notes:</li> <li>1. All dimensions shown are in millimeters (mm) unless otherwise noted.</li> <li>2. All feature sizes shown are at Maximum Material Condition (MMC) and a card fabrication tolerance of 0.05 mm is assumed.</li> </ul> |                                                             |      |  |  |  |  |  |

| <ol> <li>Dimensioning an</li> </ol>                                                                                                                                                                                                             | 3. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 |      |  |  |  |  |  |

- Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 4. This land pattern design is based on the IPC-7351 guidelines.

| Dimension                                                                                                                                                                                                                                                                                                                                                                      | Min  | Nominal | Мах  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|--|--|--|--|

| aaa                                                                                                                                                                                                                                                                                                                                                                            |      | _       | 0.20 |  |  |  |  |

| bbb                                                                                                                                                                                                                                                                                                                                                                            |      | _       | 0.20 |  |  |  |  |

| ccc                                                                                                                                                                                                                                                                                                                                                                            | 0.08 |         |      |  |  |  |  |

| ddd                                                                                                                                                                                                                                                                                                                                                                            |      |         | 0.08 |  |  |  |  |

| <ol> <li>Notes:         <ol> <li>All dimensions shown are in millimeters (mm) unless otherwise noted.</li> <li>Dimensioning and Tolerancing per ANSI Y14.5M-1994.</li> <li>This package outline conforms to JEDEC MS-026, variant ACD.</li> <li>Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.</li> </ol> </li> </ol> |      |         |      |  |  |  |  |

Table 6.10. TQFP-64 Package Dimensions (Continued)

SILICON LABS

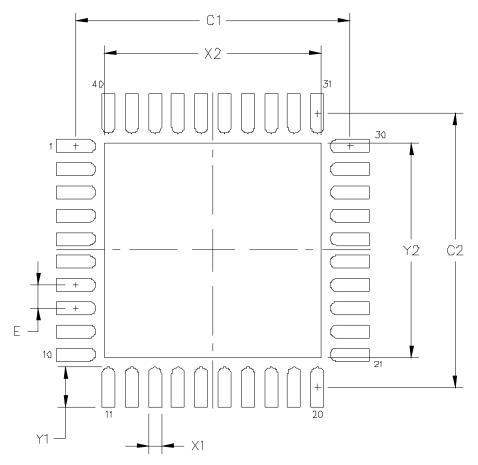

Figure 6.15. QFN-40 Landing Diagram

| Dimension | mm   |

|-----------|------|

| C1        | 5.90 |

| C2        | 5.90 |

| E         | 0.50 |

| X1        | 0.30 |

| Y1        | 0.85 |

| X2        | 4.65 |

| Y2        | 4.65 |

| Notos     |      |

## Table 6.13. QFN-40 Landing Diagram Dimensions

Notes:

- 1. All dimensions shown are in millimeters (mm).

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- **3.** All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a

- Fabrication Allowance of 0.05 mm.

# DOCUMENT CHANGE LIST

## **Revision 0.8 to Revision 1.0**

- Added block diagram to front page; updated feature bullet lists.

- Electrical Specifications Tables Additions:

- Voltage Regulator Current Sense Supply Current, Typ =  $3 \mu A$  (Table 3.2)

- Power Mode 2 Wake Time, Min = 4 clocks, Max = 5 clocks (Table 3.3)

- External Crystal Clock Frequency, Min = 0.01 MHz, Max = 30 MHz (Table 3.9)

- Added /RESET pin characteristics (Table 3.17)

- Electrical Specifications Tables Removals:

- Power Mode 3 Wake Time (Table 3.3)

- Electrical Specifications Tables Corretions/Adjustments:

- IVC Supply Current, Max = 2.5 μA (Table 3.2)

- VREG0 Output Voltage Normal Mode, Min = 3.15 V (Table 3.5)

- VREG0 Output Voltage Suspend Mode, Min = 3.15 V (Table 3.5)

- External Regulator Internal Pull-Down, Typ = 5 k $\Omega$  (Table 3.6)

- External Regulator Internal Pull-Up, Typ = 10 k $\Omega$  (Table 3.6)

- Flash Memory Endurance, Typ = 100k write/erase cycles (Table 3.7)

- Flash Memory Retention, Min = 10 Years, Typ = 100 Years (Table 3.7)

- Low Power Oscillator Frequency, Min = 19.5 MHz, Max = 20.5 MHz (Table 3.8)

- SAR Dynamic Performance : consolidated all specs. (Table 3.10)

- IDAC Full Scale Output Current 1 mA Range, Min = 0.99 mA (Table 3.11)

- IDAC Full Scale Output Current 0.5 mA Range, Min = 493 μA (Table 3.11)

- IVC Slope @ 1 mA, Min = 1.55 V/mA, Max = 1.75 V/mA (Table 3.13)

- IVC Slope @ 2 mA, Min = 795 mV/mA, Max = 860 mV/mA (Table 3.13)

- IVC Slope @ 3 mA, Min = 525 mV/mA, Max = 570 mV/mA (Table 3.13)

- IVC Slope @ 4 mA, Min = 390 mV/mA, Max = 430 mV/mA (Table 3.13)

- IVC Slope @ 5 mA, Min = 315 mV/mA (Table 3.13)

- IVC Slope @ 6 mA, Min = 260 mV/mA (Table 3.13)

- Temperature Sensor Slope Error, Type =  $\pm 120 \,\mu$ V/C (Table 3.15)

- Comparator Input Offset Voltage, Min = -10 mV, Max = 10 mV (Table 3.16)

- "4. Precision32<sup>TM</sup> SiM3C1xx System Overview":

- Updated Power Modes discussion.

- Refined and updated feature bullet lists.

- Updated and clarified RTC timer clock output. The RTC output is now referred to as "RTC0TCLK".

- "6. Pin Definitions and Packaging Information": Renamed RTC0OSC\_OUT function to RTC0TCLK\_OUT for consistency.

- "7. Revision Specific Behavior": Updated revision identification drawings to better match physical appearance of packages.