# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                 |

| Core Size                  | 32-Bit Single-Core                                              |

| Speed                      | 80MHz                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT    |

| Number of I/O              | 28                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 32K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 18x12b; D/A 2x10b                                           |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 40-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 40-QFN (6x6)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/sim3u154-b-gm |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 4.6.5. I2C (I2C0, I2C1)                                              | 43 |

|----|----------------------------------------------------------------------|----|

|    | 4.6.6. I2S (I2S0)                                                    |    |

|    | 4.7. Analog                                                          |    |

|    | 4.7.1. 12-Bit Analog-to-Digital Converters (SARADC0, SARADC1)        |    |

|    | 4.7.2. Sample Sync Generator (SSG0)                                  |    |

|    | 4.7.3. 10-Bit Digital-to-Analog Converter (IDAC0, IDAC1)             | 45 |

|    | 4.7.4. 16-Channel Capacitance-to-Digital Converter (CAPSENSE0)       |    |

|    | 4.7.5. Low Current Comparators (CMP0, CMP1)                          |    |

|    | 4.7.6. Current-to-Voltage Converter (IVC0)                           |    |

|    | 4.8. Reset Sources                                                   |    |

|    | 4.9. Security                                                        |    |

|    | 4.10.On-Chip Debugging                                               |    |

| 5. | Ordering Information                                                 |    |

|    | Pin Definitions and Packaging Information                            |    |

|    | 6.1. SiM3C1x7 Pin Definitions                                        | 51 |

|    | 6.2. SiM3C1x6 Pin Definitions                                        |    |

|    | 6.3. SiM3C1x4 Pin Definitions                                        | 66 |

|    | 6.4. LGA-92 Package Specifications                                   |    |

|    | 6.4.1. LGA-92 Solder Mask Design                                     |    |

|    | 6.4.2. LGA-92 Stencil Design                                         |    |

|    | 6.4.3. LGA-92 Card Assembly                                          |    |

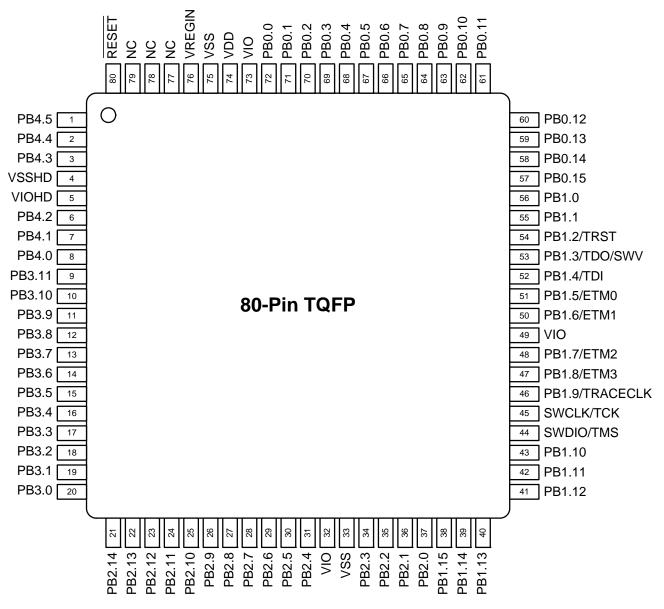

|    | 6.5. TQFP-80 Package Specifications                                  | 73 |

|    | 6.5.1. TQFP-80 Solder Mask Design                                    |    |

|    | 6.5.2. TQFP-80 Stencil Design                                        | 76 |

|    | 6.5.3. TQFP-80 Card Assembly                                         | 76 |

|    | 6.6. QFN-64 Package Specifications                                   |    |

|    | 6.6.1. QFN-64 Solder Mask Design                                     | 79 |

|    | 6.6.2. QFN-64 Stencil Design                                         |    |

|    | 6.6.3. QFN-64 Card Assembly                                          | 79 |

|    | 6.7. TQFP-64 Package Specifications                                  |    |

|    | 6.7.1. TQFP-64 Solder Mask Design                                    | 83 |

|    | 6.7.2. TQFP-64 Stencil Design                                        | 83 |

|    | 6.7.3. TQFP-64 Card Assembly                                         |    |

|    | 6.8. QFN-40 Package Specifications                                   | 84 |

|    | 6.8.1. QFN-40 Solder Mask Design                                     |    |

|    | 6.8.2. QFN-40 Stencil Design                                         |    |

|    | 6.8.3. QFN-40 Card Assembly                                          |    |

| 7. | Revision Specific Behavior                                           |    |

|    | 7.1. Revision Identification                                         | -  |

|    | 7.2. Comparator Rising/Falling Edge Flags in Debug Mode (CMP0, CMP1) |    |

|    | 7.2.1. Problem                                                       |    |

|    | 7.2.2. Impacts                                                       |    |

|    | 7.2.3. Workaround                                                    |    |

| -  | 7.2.4. Resolution                                                    |    |

|    | cument Change List                                                   |    |

| Co | Intact Information                                                   | 90 |

## Table 3.8. Internal Oscillators (Continued)

| Parameter                                   | Symbol               | Test Condition                                     | Min   | Тур  | Max   | Unit   |

|---------------------------------------------|----------------------|----------------------------------------------------|-------|------|-------|--------|

| Low Power Oscillator (LPOSC0)               |                      |                                                    | 1     | I    |       |        |

| Oscillator Frequency                        | f <sub>LPOSC</sub>   | Full Temperature and<br>Supply Range               | 19    | 20   | 21    | MHz    |

|                                             |                      | T <sub>A</sub> = 25 °C,<br>V <sub>DD</sub> = 3.3 V | 19.5  | 20   | 20.5  | MHz    |

| Divided Oscillator Frequency                | f <sub>LPOSCD</sub>  | Full Temperature and<br>Supply Range               | 2.375 | 2.5  | 2.625 | MHz    |

| Power Supply Sensitivity                    | PSS <sub>LPOSC</sub> | T <sub>A</sub> = 25 °C                             |       | 0.5  | —     | %/V    |

| Temperature Sensitivity                     | TS <sub>LPOSC</sub>  | V <sub>DD</sub> = 3.3 V                            |       | 55   |       | ppm/°C |

| Low Frequency Oscillator (LFO               | SCO)                 |                                                    |       |      | 1     |        |

| Oscillator Frequency                        | f <sub>LFOSC</sub>   | Full Temperature and<br>Supply Range               | 13.4  | 16.4 | 19.7  | kHz    |

|                                             |                      | T <sub>A</sub> = 25 °C,<br>V <sub>DD</sub> = 3.3 V | 15.8  | 16.4 | 17.3  | kHz    |

| Power Supply Sensitivity                    | PSS <sub>LFOSC</sub> | T <sub>A</sub> = 25 °C                             | _     | 2.4  |       | %/V    |

| Temperature Sensitivity                     | TS <sub>LFOSC</sub>  | V <sub>DD</sub> = 3.3 V                            | _     | 0.2  |       | %/°C   |

| RTC0 Oscillator (RTC0OSC)                   |                      |                                                    | I     |      | 1     | 4      |

| Missing Clock Detector Trigger<br>Frequency | f <sub>RTCMCD</sub>  |                                                    |       | 8    | 15    | kHz    |

| RTC Robust Duty Cycle Range                 | DC <sub>RTC</sub>    |                                                    | 25    | _    | 55    | %      |

| *Note: PLL0OSC in free-running osci         | llator mode.         | 1                                                  | 1     | 1    | 1     | 1      |

## Table 3.9. External Oscillator

| Parameter                                         | Symbol             | Test Condition | Min  | Тур | Max | Unit |  |  |  |

|---------------------------------------------------|--------------------|----------------|------|-----|-----|------|--|--|--|

| External Input CMOS Clock<br>Frequency*           | f <sub>CMOS</sub>  |                | 0    | _   | 50  | MHz  |  |  |  |

| External Input CMOS Clock High Time               | t <sub>CMOSH</sub> |                | 9    | _   |     | ns   |  |  |  |

| External Input CMOS Clock Low Time                | t <sub>CMOSL</sub> |                | 9    |     |     | ns   |  |  |  |

| External Crystal Clock Frequency                  | f <sub>XTAL</sub>  |                | 0.01 | —   | 30  | MHz  |  |  |  |

| *Note: Minimum of 10 kHz during debug operations. |                    |                |      |     |     |      |  |  |  |

#### Table 3.10. SAR ADC

| Parameter                        | Parameter Symbol Test Condition |                                                                 | Min | Min Typ |                  | Unit |  |

|----------------------------------|---------------------------------|-----------------------------------------------------------------|-----|---------|------------------|------|--|

| Resolution                       | N <sub>bits</sub>               | 12 Bit Mode                                                     |     | Bits    |                  |      |  |

|                                  |                                 | 10 Bit Mode                                                     |     | 10      |                  |      |  |

| Supply Voltage Requirements      | V <sub>ADC</sub>                | High Speed Mode                                                 | 2.2 | _       | 3.6              | V    |  |

| (VDD)                            |                                 | Low Power Mode                                                  | 1.8 | _       | 3.6              | V    |  |

| Throughput Rate                  | f <sub>S</sub>                  | 12 Bit Mode                                                     | _   | _       | 250              | ksps |  |

| (High Speed Mode)                |                                 | 10 Bit Mode                                                     |     | _       | 1                | Msps |  |

| Throughput Rate                  | f <sub>S</sub>                  | 12 Bit Mode                                                     | _   | _       | 62.5             | ksps |  |

| (Low Power Mode)                 |                                 | 10 Bit Mode                                                     | _   | _       | 250              | ksps |  |

| Tracking Time                    | t <sub>TRK</sub>                | High Speed Mode                                                 | 230 | _       |                  | ns   |  |

|                                  |                                 | Low Power Mode                                                  | 450 | _       |                  | ns   |  |

| SAR Clock Frequency              | f <sub>SAR</sub>                | High Speed Mode                                                 | _   | _       | 16.24            | MHz  |  |

|                                  |                                 | Low Power Mode                                                  | _   | _       | 4                | MHz  |  |

| Conversion Time                  | t <sub>CNV</sub>                | 10-Bit Conversion,<br>SAR Clock = 16 MHz,<br>APB Clock = 40 MHz |     | 762.5   |                  |      |  |

| Sample/Hold Capacitor            | C <sub>SAR</sub>                | Gain = 1                                                        | _   | 5       | _                | pF   |  |

|                                  |                                 | Gain = 0.5                                                      | _   | 2.5     |                  | pF   |  |

| Input Pin Capacitance            | C <sub>IN</sub>                 | High Quality Inputs                                             | _   | 18      |                  | pF   |  |

|                                  |                                 | Normal Inputs                                                   | _   | 20      |                  | pF   |  |

| Input Mux Impedance              | R <sub>MUX</sub>                | High Quality Inputs                                             | _   | 300     |                  | Ω    |  |

|                                  |                                 | Normal Inputs                                                   | _   | 550     |                  | Ω    |  |

| Voltage Reference Range          | V <sub>REF</sub>                |                                                                 | 1   | _       | V <sub>DD</sub>  | V    |  |

| Input Voltage Range <sup>1</sup> | V <sub>IN</sub>                 | Gain = 1                                                        | 0   | _       | V <sub>REF</sub> | V    |  |

|                                  |                                 | Gain = 0.5                                                      | 0   | _       | $2 x V_{REF}$    | V    |  |

| Power Supply Rejection Ratio     | PSRR <sub>ADC</sub>             |                                                                 | -   | 70      | _                | dB   |  |

| DC Performance                   | L                               |                                                                 | I   |         | ıl               |      |  |

|                                  |                                 |                                                                 |     | . 4     | 10               | LSB  |  |

| Integral Nonlinearity            | INL                             | 12 Bit Mode <sup>2</sup>                                        |     | ±1      | ±1.9             | LOD  |  |

1. Absolute input pin voltage is limited by the lower of the supply at VDD and VIO.

2. INL and DNL specifications for 12-bit mode do not include the first or last four ADC codes.

3. The maximum code in 12-bit mode is 0xFFFC. The Slope Error is referenced from the maximum code.

## Table 3.15. Temperature Sensor

| Parameter                                | Symbol           | Test Condition        | Min | Тур  | Max | Unit  |

|------------------------------------------|------------------|-----------------------|-----|------|-----|-------|

| Offset                                   | V <sub>OFF</sub> | T <sub>A</sub> = 0 °C | —   | 760  |     | mV    |

| Offset Error*                            | E <sub>OFF</sub> | T <sub>A</sub> = 0 °C | —   | ±14  |     | mV    |

| Slope                                    | М                |                       | —   | 2.8  |     | mV/°C |

| Slope Error*                             | E <sub>M</sub>   |                       | —   | ±120 |     | µV/°C |

| Linearity                                |                  |                       | —   | 1    |     | °C    |

| Turn-on Time                             |                  |                       |     | 1.8  |     | μs    |

| *Note: Represents one standard deviation | from the mea     | an.                   |     |      |     | •     |

## Table 3.16. Comparator (Continued)

| Parameter                    | Symbol             | Test Condition | Min   | Тур  | Max                   | Unit  |

|------------------------------|--------------------|----------------|-------|------|-----------------------|-------|

| Positive Hysteresis          | HYS <sub>CP+</sub> | CMPHYP = 00    |       | 1.4  | _                     | mV    |

| Mode 3 (CPMD = 11)           |                    | CMPHYP = 01    |       | 4    |                       | mV    |

|                              |                    | CMPHYP = 10    |       | 8    | —                     | mV    |

|                              |                    | CMPHYP = 11    |       | 16   | —                     | mV    |

| Negative Hysteresis          | HYS <sub>CP-</sub> | CMPHYN = 00    |       | 1.4  |                       | mV    |

| Mode 3 (CPMD = 11)           |                    | CMPHYN = 01    |       | -4   | —                     | mV    |

|                              |                    | CMPHYN = 10    |       | -8   | —                     | mV    |

|                              |                    | CMPHYN = 11    |       | -16  | —                     | mV    |

| Input Range (CP+ or CP-)     | V <sub>IN</sub>    |                | -0.25 | _    | V <sub>DD</sub> +0.25 | V     |

| Input Pin Capacitance        | C <sub>CP</sub>    | PB2 Pins       |       | 7.5  | —                     | pF    |

|                              |                    | PB3 Pins       |       | 10.5 |                       | pF    |

| Common-Mode Rejection Ratio  | CMRR <sub>CP</sub> |                |       | 75   |                       | dB    |

| Power Supply Rejection Ratio | PSRR <sub>CP</sub> |                | _     | 72   | —                     | dB    |

| Input Offset Voltage         | V <sub>OFF</sub>   |                | -10   | 0    | 10                    | mV    |

| Input Offset Tempco          | TC <sub>OFF</sub>  |                | —     | 3.5  | —                     | µV/°C |

| Reference DAC Resolution     | N <sub>Bits</sub>  |                |       | 6    |                       | bits  |

## Table 3.17. Port I/O (Continued)

| Parameter                                                    | Symbol              | Test Condition                                    | Min                     | Тур         | Max | Unit |

|--------------------------------------------------------------|---------------------|---------------------------------------------------|-------------------------|-------------|-----|------|

| Output Fall Time                                             | t <sub>F</sub>      | Slew Rate Mode 0,<br>V <sub>IOHD</sub> = 5 V      | _                       | 50          |     | ns   |

|                                                              |                     | Slew Rate Mode 1,<br>V <sub>IOHD</sub> = 5 V      |                         | 300         | —   | ns   |

|                                                              |                     | Slew Rate Mode 2,<br>V <sub>IOHD</sub> = 5 V      |                         | 1           |     | μs   |

|                                                              |                     | Slew Rate Mode 3,<br>V <sub>IOHD</sub> = 5 V      |                         | 3           |     | μs   |

| Input High Voltage                                           | V <sub>IH</sub>     | 1.8 V <u>≤</u> V <sub>IOHD</sub> <u>≤</u> 2.0 V   | 0.7 x V <sub>IOHD</sub> | _           |     | V    |

|                                                              |                     | 2.0 V <u>&lt;</u> V <sub>IOHD</sub> ≤ 6 V         | V <sub>IOHD</sub> – 0.6 | _           | _   | V    |

| Input Low Voltage                                            | V <sub>IL</sub>     |                                                   | _                       | _           | 0.6 | V    |

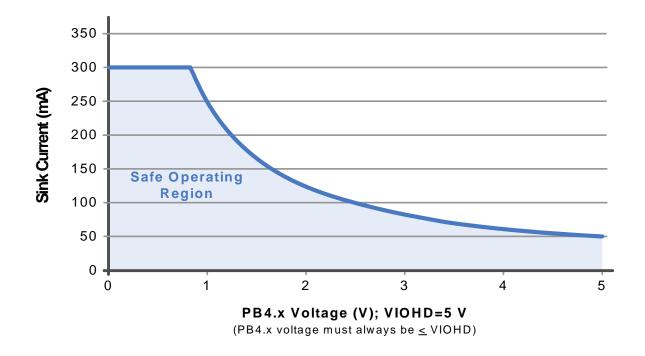

| N-Channel Sink Current Limit                                 | I <sub>SINKL</sub>  | Mode 0                                            | _                       | 1.75        |     | mA   |

| $(2.7 \text{ V} \le \text{V}_{\text{IOHD}} \le 6 \text{ V},$ |                     | Mode 1                                            | Mode 1 —                |             |     |      |

| V <sub>OL</sub> = 0.8 V)<br>See Figure 3.1                   |                     | Mode 2         —           Mode 3         —       |                         | 3.5         |     |      |

| See Figure 5.1                                               |                     |                                                   |                         | 4.75        |     |      |

|                                                              |                     | Mode 4                                            | _                       | 7           | _   |      |

|                                                              | -                   | Mode 5                                            | _                       | 9.5         |     |      |

|                                                              | -                   | Mode 6                                            |                         | 14          | _   |      |

|                                                              | -                   | Mode 7                                            |                         | 18.75       | _   |      |

|                                                              | -                   | Mode 8                                            | _                       | 28.25       |     |      |

|                                                              | -                   | Mode 9                                            | _                       | 37.5        |     |      |

|                                                              |                     | Mode 10                                           | _                       | 56.25       | _   |      |

|                                                              | -                   | Mode 11                                           | _                       | 75          |     |      |

|                                                              | -                   | Mode 12                                           |                         | 112.5       | _   |      |

|                                                              |                     | Mode 13                                           | —                       | 150         |     | 1    |

|                                                              |                     | Mode 14                                           | —                       | 225         | —   | 1    |

|                                                              |                     | Mode 15                                           | —                       | 300         | —   | 1    |

| Total N-Channel Sink Current on P4.0-P4.5 (DC)               | I <sub>SINKLT</sub> |                                                   | _                       |             | 400 | mA   |

| *Note: RESET does not drive to logic                         | high. Specific      | cations for $\overline{\text{RESET}} V_{OL}$ adhe | ere to the low dri      | ve setting. |     |      |

## Table 3.17. Port I/O (Continued)

| Parameter                                          | Symbol             | Test Condition                        | Min              | Тур           | Мах | Unit |

|----------------------------------------------------|--------------------|---------------------------------------|------------------|---------------|-----|------|

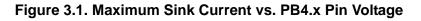

| P-Channel Source Current Limit                     | I <sub>SRCL</sub>  | Mode 0                                | _                | 0.8           |     | mA   |

| $(2.7 V \leq VIOHD \leq 6 V,$                      |                    | Mode 1                                | _                | 1.25          |     |      |

| V <sub>OH</sub> = VIOHD – 0.8 V)<br>See Figure 3.2 |                    | Mode 2                                | _                | 1.75          |     |      |

| See Figure 5.2                                     |                    | Mode 3                                | _                | 2.5           |     |      |

|                                                    |                    | Mode 4                                | _                | 3.5           |     |      |

|                                                    |                    | Mode 5                                | _                | 4.75          |     |      |

|                                                    |                    | Mode 6                                | _                | 7             |     |      |

|                                                    |                    | Mode 7                                | _                | 9.5           |     |      |

|                                                    |                    | Mode 8                                | _                | 14            |     |      |

|                                                    |                    | Mode 9                                | _                | 18.75         |     |      |

|                                                    |                    | Mode 10                               | _                | 28.25         | _   |      |

|                                                    |                    | Mode 11                               | _                | 37.5          | _   |      |

|                                                    |                    | Mode 12                               | _                | 56.25         |     |      |

|                                                    |                    | Mode 13                               | _                | 75            | _   |      |

|                                                    |                    | Mode 14                               | _                | 112.5         |     |      |

|                                                    |                    | Mode 15                               | _                | 150           |     |      |

| Total P-Channel Source Current on P4.0-P4.5 (DC)   | I <sub>SRCLT</sub> |                                       | -                | —             | 400 | mA   |

| Pin Capacitance                                    | C <sub>IO</sub>    |                                       | _                | 30            |     | pF   |

| Weak Pull-Up Current in Low Volt-<br>age Mode      | I <sub>PU</sub>    | V <sub>IOHD</sub> = 1.8 V             | -6               | -3.5          | -2  | μA   |

|                                                    |                    | V <sub>IOHD</sub> = 3.6 V             | -30              | -20           | -10 | μΑ   |

| Weak Pull-Up Current in High Volt-<br>age Mode     | I <sub>PU</sub>    | V <sub>IOHD</sub> = 2.7 V             | -15              | -10           | -5  | μA   |

|                                                    |                    | V <sub>IOHD</sub> = 6 V               | -30              | -20           | -10 | μA   |

| Input Leakage (Pullups off)                        | I <sub>LK</sub>    |                                       | -1               |               | 1   | μA   |

| *Note: RESET does not drive to logic h             | igh. Specifica     | itions for RESET V <sub>OL</sub> adhe | ere to the low d | rive setting. |     |      |

Figure 3.2. Maximum Source Current vs. PB4.x Pin Voltage

volatile data storage and allowing field upgrades of the firmware. User firmware has complete control of all peripherals and may individually shut down and gate the clocks of any or all peripherals for power savings.

The on-chip debugging interface (SWJ-DP) allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging.

Each device is specified for 1.8 to 3.6 V operation over the industrial temperature range (-40 to +85 °C). The Port I/O and RESET pins are powered from the IO supply voltage. The SiM3C1xx devices are available in 40-pin or 64-pin QFN, 64-pin or 80-pin TQFP, or 92-pin LGA packages. All package options are lead-free and RoHS compliant. See Table 5.1 for ordering information. A block diagram is included in Figure 4.1.

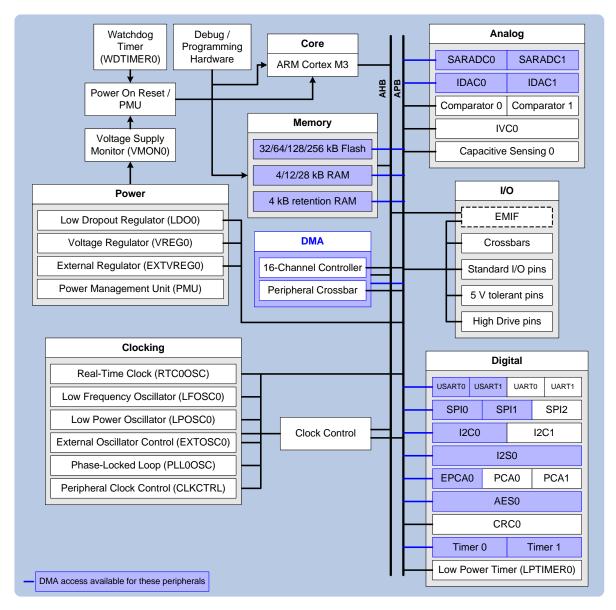

Figure 4.1. Precision32<sup>™</sup> SiM3C1xx Family Block Diagram

## 4.4. Data Peripherals

#### 4.4.1. 16-Channel DMA Controller

The DMA facilitates autonomous peripheral operation, allowing the core to finish tasks more quickly without spending time polling or waiting for peripherals to interrupt. This helps reduce the overall power consumption of the system, as the device can spend more time in low-power modes.

The DMA controller has the following features:

- Utilizes ARM PrimeCell uDMA architecture.

- Implements 16 channels.

- DMA crossbar supports SARADC0, SARADC1, IDAC0, IDAC1, I2C0, I2S0, SPI0, SPI1, USART0, USART1, AES0, EPCA0, external pin triggers, and timers.

- Supports primary, alternate, and scatter-gather data structures to implement various types of transfers.

- Access allowed to all AHB and APB memory space.

#### 4.4.2. 128/192/256-bit Hardware AES Encryption (AES0)

The basic AES block cipher is implemented in hardware. The integrated hardware support for Cipher Block Chaining (CBC) and Counter (CTR) algorithms results in identical performance, memory bandwidth, and memory footprint between the most basic Electronic Codebook (ECB) algorithm and these more complex algorithms. This hardware accelerator translates to more core bandwidth available for other functions or a power savings for low-power applications.

The AES module includes the following features:

- Operates on 4-word (16-byte) blocks.

- Supports key sizes of 128, 192, and 256 bits for both encryption and decryption.

- Generates the round key for decryption operations.

- All cipher operations can be performed without any firmware intervention for a set of 4-word blocks (up to 32 kB).

- Support for various chained and stream-ciphering configurations with XOR paths on both the input and output.

- Internal 4-word FIFOs to facilitate DMA operations.

- Integrated key storage.

- Hardware acceleration for Cipher-Block Chaining (CBC) and Counter (CTR) algorithms utilizing integrated counterblock generation and previous-block caching.

#### 4.4.3. 16/32-bit CRC (CRC0)

The CRC module is designed to provide hardware calculations for Flash memory verification and communications protocols.

The CRC module supports four common polynomials. The supported 32-bit polynomial is 0x04C11DB7 (IEEE 802.3). The three supported 16-bit polynomials are 0x1021 (CCITT-16), 0x3D65 (IEC16-MBus), and 0x8005 (ZigBee, 802.15.4, and USB).

The CRC module includes the following features:

- Support for four common polynomials (one 32-bit and three 16-bit options).

- Byte-level bit reversal for the CRC input.

- Byte-order reorientation of words for the CRC input.

- Word or half-word bit reversal of the CRC result.

- Ability to configure and seed an operation in a single register write.

- Support for single-cycle parallel (unrolled) CRC computation for 32- or 8-bit blocks.

- Capability to CRC 32 bits of data per peripheral bus (APB) clock.

- Support for DMA writes using firmware request mode.

- Internal transmit and receive FIFOs with flush capability and support for byte, half-word, and word reads and writes.

- Data bit lengths from 5 to 9 bits.

- Programmable inter-packet transmit delays.

- Auto-baud detection with support for the LIN SYNC byte.

- Automatic parity generation (with enable).

- Automatic start and stop generation.

- Transmit and receive hardware flow-control.

- Independent inversion correction for TX, RX, RTS, and CTS signals.

- IrDA modulation and demodulation with programmable pulse widths.

- Smartcard ACK/NACK support.

- Parity error, frame error, overrun, and underrun detection.

- Multi-master and half-duplex support.

- Multiple loop-back modes supported.

#### 4.6.4. SPI (SPI0, SPI1)

SPI is a 3- or 4-wire communication interface that includes a clock, input data, output data, and an optional select signal.

The SPI module includes the following features:

- Supports 3- or 4-wire master or slave modes.

- Supports up to 10 MHz clock in master mode and 5 MHz clock in slave mode.

- Support for all clock phase and slave select (NSS) polarity modes.

- 16-bit programmable clock rate.

- Programmable MSB-first or LSB-first shifting.

- 8-byte FIFO buffers for both transmit and receive data paths to support high speed transfers.

- Programmable FIFO threshold level to request data service for DMA transfers.

- Support for multiple masters on the same data lines.

#### 4.6.5. I2C (I2C0, I2C1)

The I2C interface is a two-wire, bi-directional serial bus. The two clock and data signals operate in open-drain mode with external pull-ups to support automatic bus arbitration.

Reads and writes to the interface are byte oriented with the I2C interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/8th of the APB clock as a master or slave, which can be faster than allowed by the I2C specification, depending on the clock source used. A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

The I2C interface may operate as a master and/or slave, and may function on a bus with multiple masters. The I2C provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and start/ stop control and generation.

The I2C module includes the following features:

- Standard (up to 100 kbps) and Fast (400 kbps) transfer speeds.

- Can operate down to APB clock divided by 32768 or up to APB clock divided by 8.

- Support for master, slave, and multi-master modes.

- Hardware synchronization and arbitration for multi-master mode.

- Clock low extending (clock stretching) to interface with faster masters.

- Hardware support for 7-bit slave and general call address recognition.

- Firmware support for 10-bit slave address decoding.

- Ability to disable all slave states.

- Programmable clock high and low period.

- Programmable data setup/hold times.

## 4.7. Analog

### 4.7.1. 12-Bit Analog-to-Digital Converters (SARADC0, SARADC1)

The SARADC0 and SARADC1 modules on SiM3C1xx devices are Successive Approximation Register (SAR) Analog to Digital Converters (ADCs). The key features of the SARADC module are:

- Single-ended 12-bit and 10-bit modes.

- Supports an output update rate of 250 k samples per second in 12-bit mode or 1 M samples per second in 10-bit mode.

- Operation in low power modes at lower conversion speeds.

- Selectable asynchronous hardware conversion trigger with hardware channel select.

- Output data window comparator allows automatic range checking.

- Support for Burst Mode, which produces one set of accumulated data per conversion-start trigger with programmable power-on settling and tracking time.

- Conversion complete, multiple conversion complete, and FIFO overflow and underflow flags and interrupts supported.

- Flexible output data formatting.

- Sequencer allows up to 8 sources to be automatically scanned using one of four channel characteristic profiles without software intervention.

- Eight-word conversion data FIFO for DMA operations.

- Multiple SARADC modules can work together synchronously or by interleaving samples.

- Includes two internal references (1.65 V fast-settling, 1.2/2.4 V precision), support for an external reference, and support for an external signal ground.

#### 4.7.2. Sample Sync Generator (SSG0)

The SSG module includes a phase counter and a pulse generator. The phase counter is a 4-bit free-running counter clocked from the SARADC module clock. Counting-up from zero, the phase counter marks sixteen equally-spaced events for any number of SARADC modules. The ADCs can use this phase counter to start a conversion. The programmable pulse generator creates a 50% duty cycle pulse with a period of 16 phase counter ticks. Up to four programmable outputs available to external devices can be driven by the pulse generator with programmable polarity and a defined output setting when the pulse generator is stopped.

The Sample Sync Generator module has the following features:

- Connects multiple modules together to perform synchronized actions.

- Outputs a clock synchronized to the internal sampling clock used by any number of SARADC modules to pins for use by external devices.

- Includes a phase counter, pulse generator, and up to four programmable outputs.

#### 4.7.3. 10-Bit Digital-to-Analog Converter (IDAC0, IDAC1)

The IDAC takes a digital value as an input and outputs a proportional constant current on a pin. The IDAC module includes the following features:

- 10-bit current DAC with support for four timer, up to seven external I/O, on demand, and SSG0 output update triggers.

- Ability to update on rising, falling, or both edges for any of the external I/O trigger sources (DACnTx).

- Supports an output update rate greater than 600 k samples per second.

- Support for three full-scale output modes: 0.5 mA, 1.0 mA and 2.0 mA.

- Four-word FIFO to aid with high-speed waveform generation or DMA interactions.

- Individual FIFO overrun, underrun, and went-empty interrupt status sources.

- Support for multiple data packing formats, including: single 10-bit sample per word, dual 10-bit samples per word, or four 8-bit samples per word.

- Support for left- and right-justified data.

# 5. Ordering Information

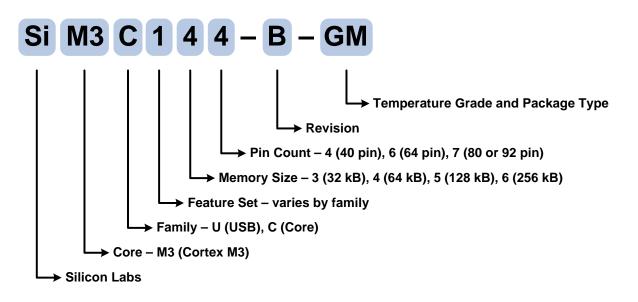

## Figure 5.1. SiM3C1xx Part Numbering

All devices in the SiM3C1xx family have the following features:

- Core: ARM Cortex-M3 with maximum operating frequency of 80 MHz.

- Flash Program Memory: 32-256 kB, in-system programmable.

- RAM: 8–32 kB SRAM, with 4 kB retention SRAM

- I/O: Up to 65 multifunction I/O pins, including high-drive and 5 V-tolerant pins.

- Clock Sources: Internal and external oscillator options.

- 16-Channel DMA Controller.

- 128/192/256-bit AES.

- 16/32-bit CRC.

- **Timers:** 2 x 32-bit (4 x 16-bit).

- Real-Time Clock.

- Low-Power Timer.

- PCA: 1 x 6 channels (Enhanced), 2 x 2 channels (Standard). PWM, capture, and clock generation capabilites.

- ADC: 2 x 12-bit 250 ksps (10-bit 1 Msps) SAR.

- **DAC:** 2 x 10-bit IDAC.

- Temperature Sensor.

- Internal VREF.

- 16-channel Capacitive Sensing (CAPSENSE).

- **Comparator:** 2 x low current.

- Current to Voltage Converter (IVC).

- Serial Buses: 2 x USART, 2 x UART, 3 x SPI, 2 x I2C, 1 x I<sup>2</sup>S.

The inclusion of some features varies across different members of the device family. The differences are detailed in Table 5.1.

# 6. Pin Definitions and Packaging Information

## 6.1. SiM3C1x7 Pin Definitions

Figure 6.1. SiM3C1x7-GQ Pinout

| Pin Name | Туре             | Pin Numbers | Crossbar Capability<br>(see Port Config Section) | Port Match | External Memory Interface<br>(m = muxed mode) | Port-Mapped Level Shifter | Output Toggle Logic | External Trigger Inputs                                     | Analog or Additional<br>Functions |

|----------|------------------|-------------|--------------------------------------------------|------------|-----------------------------------------------|---------------------------|---------------------|-------------------------------------------------------------|-----------------------------------|

| PB3.9    | 5 V Tolerant I/O | 7           | XBR1                                             | V          | BE0                                           |                           |                     | DAC0T6<br>DAC1T6<br>LPT0T2<br>INT0.10<br>INT1.10<br>WAKE.15 | CMP0N.5<br>CMP1N.5<br>EXREGBD     |

| PB4.0    | High Drive I/O   | 6           |                                                  |            |                                               | LSO0                      |                     |                                                             |                                   |

| PB4.1    | High Drive I/O   | 5           |                                                  |            |                                               | LSO1                      |                     |                                                             |                                   |

| PB4.2    | High Drive I/O   | 4           |                                                  |            |                                               | LSO2                      |                     |                                                             |                                   |

| PB4.3    | High Drive I/O   | 1           |                                                  |            |                                               | LSO3                      |                     |                                                             |                                   |

Table 6.2. Pin Definitions and alternate functions for SiM3C1x6 (Continued)

| Pin Name | Туре                | Pin Numbers | Crossbar Capability<br>(see Port Config Section) | Port Match   | Output Toggle Logic | External Trigger Inputs | Analog or Additional<br>Functions |

|----------|---------------------|-------------|--------------------------------------------------|--------------|---------------------|-------------------------|-----------------------------------|

| VSS      | Ground              | 14          |                                                  |              |                     |                         |                                   |

| VDD      | Power (Core)        | 35          |                                                  |              |                     |                         |                                   |

| VIO      | Power (I/O)         | 13          |                                                  |              |                     |                         |                                   |

| VREGIN   | Power (Regulator)   | 36          |                                                  |              |                     |                         |                                   |

| VSSHD    | Ground (High Drive) | 2           |                                                  |              |                     |                         |                                   |

| VIOHD    | Power (High Drive)  | 3           |                                                  |              |                     |                         |                                   |

| RESET    | Active-low Reset    | 40          |                                                  |              |                     |                         |                                   |

| SWCLK    | Serial Wire         | 24          |                                                  |              |                     |                         |                                   |

| SWDIO    | Serial Wire         | 23          |                                                  |              |                     |                         |                                   |

| PB0.0    | Standard I/O        | 34          | XBR0                                             | ~            |                     |                         | ADC0.8<br>CS0.7<br>RTC1           |

| PB0.1    | Standard I/O        | 33          | XBR0                                             | $\checkmark$ |                     |                         | RTC2                              |

| PB0.2    | Standard I/O        | 32          | XBR0                                             | ~            |                     |                         | ADC0.9<br>CS0.0<br>VREFGND        |

| PB0.3    | Standard I/O        | 31          | XBR0                                             | ~            |                     |                         | ADC0.10<br>CS0.1<br>VREF          |

| PB0.4    | Standard I/O        | 30          | XBR0                                             | ~            |                     |                         | ADC1.6<br>CS0.2<br>IDAC0          |

| PB0.5    | Standard I/O        | 29          |                                                  |              |                     |                         | IDAC1                             |

| PB0.6    | Standard I/O        | 28          | XBR0                                             | $\checkmark$ |                     |                         | ADC0.0<br>CS0.3<br>XTAL1          |

| PB0.7    | Standard I/O        | 27          | XBR0                                             | $\checkmark$ |                     |                         | ADC0.1<br>CS0.4<br>XTAL2          |

Table 6.3. Pin Definitions and Alternate Functions for SiM3C1x4

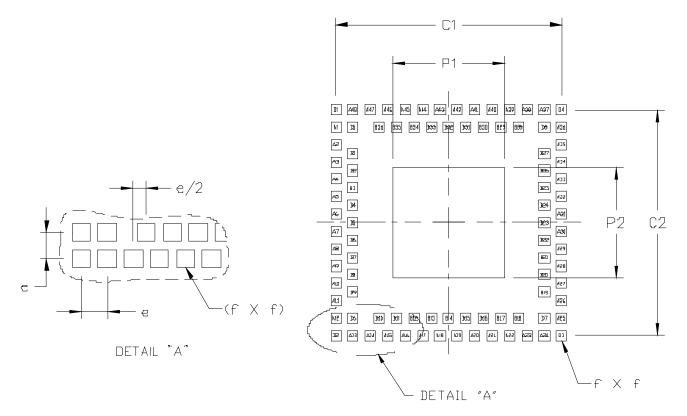

Figure 6.7. LGA-92 Landing Diagram

| Dimension                                                                                                                                                                                                                                       | Typical                                                  | Мах  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|--|--|

| C1                                                                                                                                                                                                                                              | 6.50                                                     | —    |  |  |

| C2                                                                                                                                                                                                                                              | 6.50                                                     | _    |  |  |

| e                                                                                                                                                                                                                                               | 0.50                                                     | —    |  |  |

| f                                                                                                                                                                                                                                               | —                                                        | 0.35 |  |  |

| P1                                                                                                                                                                                                                                              | —                                                        | 3.20 |  |  |

| P2                                                                                                                                                                                                                                              | —                                                        | 3.20 |  |  |

| <ul> <li>Notes:</li> <li>1. All dimensions shown are in millimeters (mm) unless otherwise noted.</li> <li>2. All feature sizes shown are at Maximum Material Condition (MMC) and a card fabrication tolerance of 0.05 mm is assumed.</li> </ul> |                                                          |      |  |  |

| <ol><li>Dimensioning an</li></ol>                                                                                                                                                                                                               | Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 |      |  |  |

- Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 4. This land pattern design is based on the IPC-7351 guidelines.

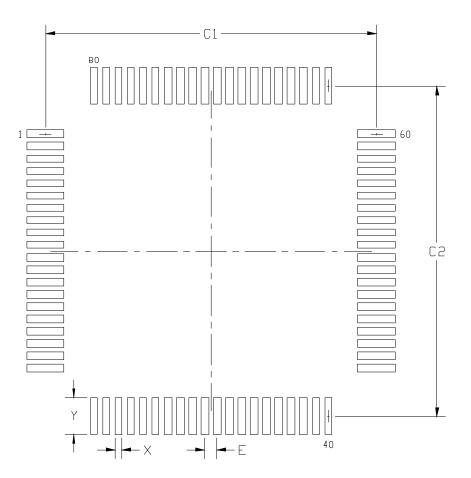

| Table 6.7. TQFP-80 Landing | <b>Diagram Dimensions</b> |

|----------------------------|---------------------------|

|----------------------------|---------------------------|

| Dimension | Min                     | Max                   |  |

|-----------|-------------------------|-----------------------|--|

| C1        | 13.30                   | 13.40                 |  |

| C2        | 13.30                   | 13.40                 |  |

| E         | 0.50 BSC                |                       |  |

| X         | 0.20                    | 0.30                  |  |

| Y         | 1.40                    | 1.50                  |  |

| noted.    | wn are in millimeters ( | (mm) unless otherwise |  |

2. This land pattern design is based on the IPC-7351 guidelines.

## 6.7. TQFP-64 Package Specifications

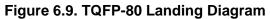

Figure 6.12. TQFP-64 Package Drawing

| Dimension | Min       | Nominal | Max  |

|-----------|-----------|---------|------|

| A         | —         | _       | 1.20 |

| A1        | 0.05      | _       | 0.15 |

| A2        | 0.95      | 1.00    | 1.05 |

| b         | 0.17      | 0.22    | 0.27 |

| с         | 0.09      | —       | 0.20 |

| D         | 12.00 BSC |         |      |

| D1        | 10.00 BSC |         |      |

| е         | 0.50 BSC  |         |      |

| E         | 12.00 BSC |         |      |

| E1        | 10.00 BSC |         |      |

| L         | 0.45      | 0.60    | 0.75 |

| Θ         | 0°        | 3.5°    | 7°   |

## Table 6.10. TQFP-64 Package Dimensions

Silicon Labs

Simplicity Studio<sup>4</sup>

#### **Simplicity Studio**

One-click access to MCU and wireless tools, documentation, software, source code libraries & more. Available for Windows, Mac and Linux!

Support and Community community.silabs.com

#### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadio®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

## http://www.silabs.com