# E·XFL

#### Zilog - ZGP323HAH4804C00TR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | Z8                                                            |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | -                                                             |

| Peripherals                | HLVD, POR, WDT                                                |

| Number of I/O              | 32                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                  |

| Program Memory Type        | OTP                                                           |

| EEPROM Size                | -                                                             |

| RAM Size                   | 237 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                     |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323hah4804c00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Capacitance

Table 8 lists the capacitances.

#### Table 8. Capacitance

| Parameter                                                                                      | Maximum |  |  |  |

|------------------------------------------------------------------------------------------------|---------|--|--|--|

| Input capacitance                                                                              | 12pF    |  |  |  |

| Output capacitance                                                                             | 12pF    |  |  |  |

| I/O capacitance                                                                                | 12pF    |  |  |  |

| Note: $T_A = 25^{\circ}$ C, $V_{CC} = GND = 0$ V, f = 1.0 MHz, unmeasured pins returned to GND |         |  |  |  |

# **DC Characteristics**

#### Table 9. GP323HS DC Characteristics

|                     |                                             |                 | T <sub>A</sub> =0°C to | o +70°C |                         |       |                                                            |       |

|---------------------|---------------------------------------------|-----------------|------------------------|---------|-------------------------|-------|------------------------------------------------------------|-------|

| Symbol              | Parameter                                   | V <sub>CC</sub> | Min                    | Typ(7)  | Max                     | Units | Conditions N                                               | lotes |

| V <sub>CC</sub>     | Supply Voltage                              |                 | 2.0                    |         | 5.5                     | V     | See Note 5 5                                               | i     |

| V <sub>CH</sub>     | Clock Input High<br>Voltage                 | 2.0-5.5         | 0.8 V <sub>CC</sub>    |         | V <sub>CC</sub> +0.3    | V     | Driven by External<br>Clock Generator                      |       |

| V <sub>CL</sub>     | Clock Input Low<br>Voltage                  | 2.0-5.5         | V <sub>SS</sub> -0.3   |         | 0.4                     | V     | Driven by External<br>Clock Generator                      |       |

| V <sub>IH</sub>     | Input High Voltage                          | 2.0-5.5         | 0.7 V <sub>CC</sub>    |         | V <sub>CC</sub> +0.3    | V     |                                                            |       |

| V <sub>IL</sub>     | Input Low Voltage                           | 2.0-5.5         | V <sub>SS</sub> -0.3   |         | 0.2 V <sub>CC</sub>     | V     |                                                            |       |

| V <sub>OH1</sub>    | Output High Voltage                         | 2.0-5.5         | V <sub>CC</sub> -0.4   |         |                         | V     | $I_{OH} = -0.5 \text{mA}$                                  |       |

| V <sub>OH2</sub>    | Output High Voltage<br>(P36, P37, P00, P01) | 2.0-5.5         | V <sub>CC</sub> -0.8   |         |                         | V     | I <sub>OH</sub> = -7mA                                     |       |

| V <sub>OL1</sub>    | Output Low Voltage                          | 2.0-5.5         |                        |         | 0.4                     | V     | I <sub>OL</sub> = 4.0mA                                    |       |

| V <sub>OL2</sub>    | Output Low Voltage<br>(P00, P01, P36, P37)  | 2.0-5.5         |                        |         | 0.8                     | V     | I <sub>OL</sub> = 10mA                                     |       |

| V <sub>OFFSET</sub> | Comparator Input<br>Offset Voltage          | 2.0-5.5         |                        |         | 25                      | mV    |                                                            |       |

| V <sub>REF</sub>    | Comparator<br>Reference<br>Voltage          | 2.0-5.5         | 0                      |         | V <sub>CC</sub><br>1.75 | V     |                                                            |       |

| Ι <sub>ΙL</sub>     | Input Leakage                               | 2.0-5.5         | -1                     |         | 1                       | μA    | V <sub>IN</sub> = 0V, V <sub>CC</sub><br>Pull-ups disabled |       |

| R <sub>PU</sub>     | Pull-up Resistance                          | 2.0V            | 225                    |         | 675                     | KΩ    | V <sub>IN</sub> = 0V; Pullups selected by mask             |       |

|                     |                                             | 3.6V            | 75                     |         | 275                     | KΩ    | option                                                     |       |

|                     |                                             | 5.0V            | 40                     |         | 160                     | KΩ    |                                                            |       |

12

|                  |                                          |                 | T <sub>A</sub> =0°C t | o +70°C |     |       |                                                        |         |

|------------------|------------------------------------------|-----------------|-----------------------|---------|-----|-------|--------------------------------------------------------|---------|

| Symbol           | Parameter                                | V <sub>CC</sub> | Min                   | Typ(7)  | Max | Units | Conditions                                             | Notes   |

| I <sub>OL</sub>  | Output Leakage                           | 2.0-5.5         | -1                    |         | 1   | μA    | $V_{IN} = 0V, V_{CC}$                                  |         |

| I <sub>CC</sub>  | Supply Current                           | 2.0V            |                       | 1       | 3   | mA    | at 8.0 MHz                                             | 1, 2    |

|                  |                                          | 3.6V            |                       | 5       | 10  | mA    | at 8.0 MHz                                             | 1, 2    |

|                  |                                          | 5.5V            |                       | 10      | 15  | mA    | at 8.0 MHz                                             | 1, 2    |

| I <sub>CC1</sub> | Standby Current                          | 2.0V            |                       | 0.5     | 1.6 | mA    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                  | 1, 2, 6 |

|                  | (HALT Mode)                              | 3.6V            |                       | 0.8     | 2.0 | mA    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                  | 1, 2, 6 |

|                  |                                          | 5.5V            |                       | 1.3     | 3.2 | mA    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                  | 1, 2, 6 |

| I <sub>CC2</sub> | Standby Current (Stop                    | 2.0V            |                       | 1.6     | 8   | μΑ    | V <sub>IN</sub> = 0 V, V <sub>CC</sub> WDT not Running | 3       |

|                  | Mode)                                    | 3.6V            |                       | 1.8     | 10  | μA    | $V_{IN} = 0 V, V_{CC} WDT not Running$                 | 3       |

|                  |                                          | 5.5V            |                       | 1.9     | 12  | μA    | $V_{IN} = 0 V, V_{CC} WDT not Running$                 | 3       |

|                  |                                          | 2.0V            |                       | 5       | 20  | μA    | V <sub>IN</sub> = 0 V, V <sub>CC</sub> WDT is Running  | 3       |

|                  |                                          | 3.6V            |                       | 8       | 30  | μA    | V <sub>IN</sub> = 0 V, V <sub>CC</sub> WDT is Running  | 3       |

|                  |                                          | 5.5V            |                       | 15      | 45  | μA    | $V_{IN} = 0 V, V_{CC} WDT$ is Running                  | 3       |

| I <sub>LV</sub>  | Standby Current<br>(Low Voltage)         |                 |                       | 1.2     | 6   | μA    | Measured at 1.3V                                       | 4       |

| V <sub>BO</sub>  | V <sub>CC</sub> Low Voltage              |                 |                       | 1.9     | 2.0 | V     | 8MHz maximum                                           |         |

|                  | Protection                               |                 |                       |         |     |       | Ext. CLK Freq.                                         |         |

| V <sub>LVD</sub> | V <sub>CC</sub> Low Voltage<br>Detection |                 |                       | 2.4     |     | V     |                                                        |         |

| V <sub>HVD</sub> | Vcc High Voltage<br>Detection            |                 |                       | 2.7     |     | V     |                                                        |         |

#### Table 9. GP323HS DC Characteristics (Continued)

#### Notes:

1. All outputs unloaded, inputs at rail.

2. CL1 = CL2 = 100 pF.

3. Oscillator stopped.

4. Oscillator stops when  $V_{CC}$  falls below  $V_{BO}$  limit.

It is strongly recommended to add a filter capacitor (minimum 0.1 μF), physically close to VCC and V<sub>SS</sub> pins if operating voltage fluctuations are anticipated, such as those resulting from driving an Infrared LED.

- 6. Comparator and Timers are on. Interrupt disabled.

- 7. Typical values shown are at 25 degrees C.

#### Table 10. GP323HE DC Characteristics

| T <sub>A</sub> = -40°C to +105°C |                             |                 |                      |        |                      |       |                                       |       |

|----------------------------------|-----------------------------|-----------------|----------------------|--------|----------------------|-------|---------------------------------------|-------|

| Symbol                           | Parameter                   | V <sub>CC</sub> | Min                  | Typ(7) | Max                  | Units | Conditions                            | Notes |

| V <sub>CC</sub>                  | Supply Voltage              |                 | 2.0                  |        | 5.5                  | V     | See Note 5                            | 5     |

| V <sub>CH</sub>                  | Clock Input High<br>Voltage | 2.0-5.5         | 0.8 V <sub>CC</sub>  |        | V <sub>CC</sub> +0.3 | V     | Driven by External<br>Clock Generator |       |

| V <sub>CL</sub>                  | Clock Input Low<br>Voltage  | 2.0-5.5         | V <sub>SS</sub> –0.3 |        | 0.4                  | V     | Driven by External<br>Clock Generator |       |

| V <sub>IH</sub>                  | Input High Voltage          | 2.0-5.5         | 0.7 V <sub>CC</sub>  |        | V <sub>CC</sub> +0.3 | V     |                                       |       |

| V <sub>IL</sub>                  | Input Low Voltage           | 2.0-5.5         | V <sub>SS</sub> -0.3 |        | 0.2 V <sub>CC</sub>  | V     |                                       |       |

| V <sub>OH1</sub>                 | Output High Voltage         | 2.0-5.5         | V <sub>CC</sub> -0.4 |        |                      | V     | $I_{OH} = -0.5 \text{mA}$             |       |

#### Table 11. GP323HA DC Characteristics (Continued)

|                  |                                     |                 | T <sub>A</sub> = -40°  | C to +125   | °C  |       |                                        |                            |

|------------------|-------------------------------------|-----------------|------------------------|-------------|-----|-------|----------------------------------------|----------------------------|

| Symbol           | Parameter                           | V <sub>CC</sub> | Min                    | Typ(7)      | Max | Units | Conditions                             | Notes                      |

| V <sub>HVD</sub> | Vcc High Voltage<br>Detection       |                 |                        | 2.7         |     | V     |                                        |                            |

| Notes:           |                                     |                 |                        |             |     |       |                                        |                            |

| 1. All o         | outputs unloaded, inpu              | ıts at rail.    |                        |             |     |       |                                        |                            |

| 2. CL1           | 1 = CL2 = 100 pF.                   |                 |                        |             |     |       |                                        |                            |

| 3. Osc           | cillator stopped.                   |                 |                        |             |     |       |                                        |                            |

| 4. Osc           | cillator stops when V <sub>CC</sub> | falls below     | V <sub>BO</sub> limit. |             |     |       |                                        |                            |

| volt             | age fluctuations are a              | nticipated, su  | ch as thos             | e resulting |     |       | cally close to VCC and<br>nfrared LED. | $V_{SS}$ pins if operating |

| 6. Cor           | mparator and Timers a               | re on. Interru  | pt disabled            | 1.          |     |       |                                        |                            |

7. Typical values shown are at 25 degrees C.

#### Table 12. EPROM/OTP Characteristics

| Symbol | Parameter                  | Min. | Тур. | Max. | Unit    | Notes |

|--------|----------------------------|------|------|------|---------|-------|

|        | Erase Time                 | 15   |      |      | Minutes | 1,3   |

|        | Data Retention @ use years |      | 10   |      | Years   | 2     |

|        | Program/Erase Endurance    | 100  |      |      | Cycles  | 1     |

Notes:

1. For windowed cerdip package only.

2. Standard: 0°C to 70°C; Extended: -40°C to +105°C; Automotive: -40°C to +125°C. Determined using the Arrhenius model, which is an industry standard for estimating data retention of floating gate technologies:

AF = exp[(Ea/k)\*(1/Tuse - 1/TStress)] Where: Ea is the intrinsic activation energy (eV; typ. 0.8) k is Boltzman's constant (8.67 x 10-5 eV/°K) °K = -273.16°C Tuse = Use Temperature in °K TStress = Stress Temperature in °K 3. At a stable UV Lamp output of 20mW/CM<sup>2</sup>

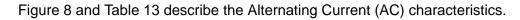

# **AC Characteristics**

Figure 8. AC Timing Diagram

### **Pin Functions**

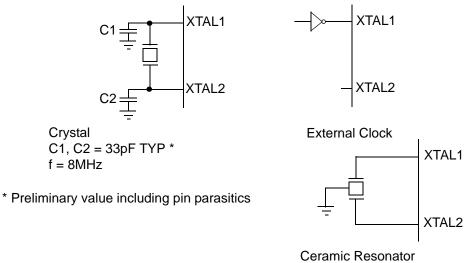

#### XTAL1 Crystal 1 (Time-Based Input)

This pin connects a parallel-resonant crystal or ceramic resonator to the on-chip oscillator input. Additionally, an optional external single-phase clock can be coded to the on-chip oscillator input.

#### XTAL2 Crystal 2 (Time-Based Output)

This pin connects a parallel-resonant crystal or ceramic resonant to the on-chip oscillator output.

#### Port 0 (P07-P00)

Port 0 is an 8-bit, bidirectional, CMOS-compatible port. These eight I/O lines are configured under software control as a nibble I/O port. The output drivers are push-pull or open-drain controlled by bit D2 in the PCON register.

If one or both nibbles are needed for I/O operation, they must be configured by writing to the Port 0 mode register. After a hardware reset, Port 0 is configured as an input port.

An optional pull-up transistor is available as a mask option on all Port 0 bits with nibble select.

**Notes:** Internal pull-ups are disabled on any given pin or group of port pins when programmed into output mode.

The Port 0 direction is reset to its default state following an SMR.

The counter/timers are mapped into ERF group D. Access is easily performed using the following:

| LD                                 | RP, #0Dh      | ; | Select ERF D |

|------------------------------------|---------------|---|--------------|

| for access to bank D               |               |   |              |

|                                    |               | ; | (working     |

| register group 0)                  |               |   |              |

| LD                                 | R0,#xx        | ; | load CTR0    |

| LD                                 | 1, #xx        | ; | load CTR1    |

| LD                                 | R1, 2         | ; | CTR2→CTR1    |

|                                    |               |   |              |

| LD                                 | RP, #0Dh      | ; | Select ERF D |

| for access to bank D               |               |   |              |

|                                    |               | ; | (working     |

| register group 0)                  |               |   |              |

| LD                                 | RP, #7Dh      | ; | Select       |

| expanded register bank             | D and working | ; | register     |

| group 7 of bank 0 for a            | ccess.        |   |              |

| LD                                 | 71h, 2        |   |              |

| ; CTRL2 $\rightarrow$ register 71h |               |   |              |

| LD                                 | R1, 2         |   |              |

| ; CTRL2 $\rightarrow$ register 71h |               |   |              |

#### **Register File**

>

The register file (bank 0) consists of 4 I/O port registers, 237 general-purpose registers, 16 control and status registers (R0–R3, R4–R239, and R240–R255, respectively), and two expanded registers groups in Banks D (see Table 15) and F. Instructions can access registers directly or indirectly through an 8-bit address field, thereby allowing a short, 4-bit register address to use the Register Pointer (Figure 17). In the 4-bit mode, the register file is divided into 16 working register groups, each occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working register group.

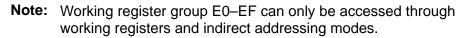

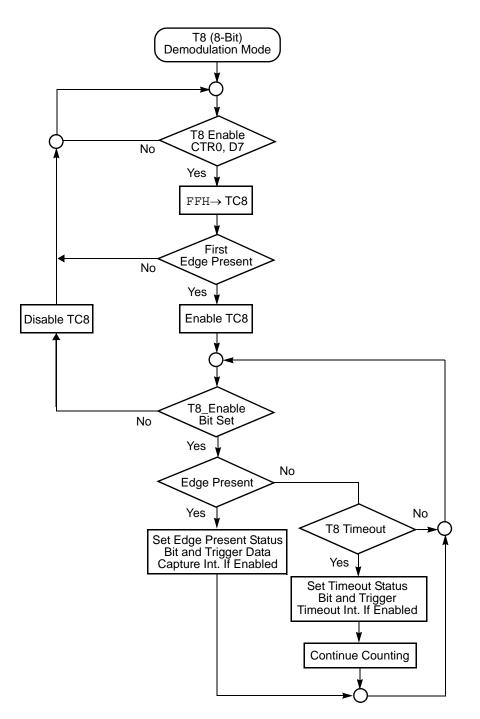

into LO8; if it is a negative edge, data is put into HI8. From that point, one of the edge detect status bits (CTR1, D1; D0) is set, and an interrupt can be generated if enabled (CTR0, D2). Meanwhile, T8 is loaded with FFh and starts counting again. If T8 reaches 0, the timeout status bit (CTR0, D5) is set, and an interrupt can be generated if enabled (CTR0, D1). T8 then continues counting from FFH (see Figure 23 and Figure 24).

Figure 23. Demodulation Mode Count Capture Flowchart

Figure 24. Demodulation Mode Flowchart

ZGP323H Product Specification

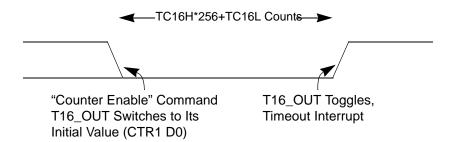

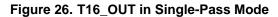

Caution: Do not load these registers at the time the values are to be loaded into the counter/timer to ensure known operation. An initial count of 1 is not allowed. An initial count of 0 causes T16 to count from 0 to FFFFH to FFFFH. Transition from 0 to FFFFH is not a timeout condition.

Figure 27. T16\_OUT in Modulo-N Mode

#### **T16 DEMODULATION Mode**

The user must program TC16L and TC16H to FFH. After T16 is enabled, and the first edge (rising, falling, or both depending on CTR1 D5; D4) is detected, T16 captures HI16 and LO16, reloads, and begins counting.

#### If D6 of CTR2 Is 0

When a subsequent edge (rising, falling, or both depending on CTR1, D5; D4) is detected during counting, the current count in T16 is complemented and put into HI16 and LO16. When data is captured, one of the edge detect status bits (CTR1, D1; D0) is set, and an interrupt is generated if enabled (CTR2, D2). T16 is loaded with FFFFH and starts again.

This T16 mode is generally used to measure space time, the length of time between bursts of carrier signal (marks).

#### 53

#### Clock

The device's on-chip oscillator has a high-gain, parallel-resonant amplifier, for connection to a crystal or ceramic resonator, or any suitable external clock source (XTAL1 = Input, XTAL2 = Output). The crystal must be AT cut, 1 MHz to 8 MHz maximum, with a series resistance (RS) less than or equal to 100  $\Omega$ . The on-chip oscillator can be driven with a suitable external clock source.

The crystal must be connected across XTAL1 and XTAL2 using the recommended capacitors (capacitance greater than or equal to 22 pF) from each pin to ground.

f = 8mHz

Figure 31. Oscillator Configuration

| FF | NOP  | ; clear the pipeline |

|----|------|----------------------|

| 6F | Stop | ; enter Stop Mode    |

| or |      |                      |

| FF | NOP  | ; clear the pipeline |

| 7F | HALT | ; enter HALT Mode    |

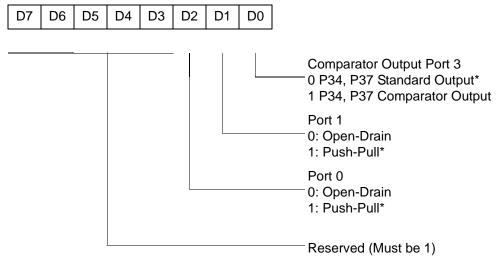

#### **Port Configuration Register**

The Port Configuration (PCON) register (Figure 32) configures the comparator output on Port 3. It is located in the expanded register 2 at Bank F, location 00.

#### PCON(FH)00H

\* Default setting after reset

#### Figure 32. Port Configuration Register (PCON) (Write Only)

#### Comparator Output Port 3 (D0)

Bit 0 controls the comparator used in Port 3. A 1 in this location brings the comparator outputs to P34 and P37, and a 0 releases the Port to its standard I/O configuration.

#### Port 1 Output Mode (D1)

Bit 1 controls the output mode of port 1. A 1 in this location sets the output to push-pull, and a 0 sets the output to open-drain.

# <mark>\_\_\_\_</mark> 62

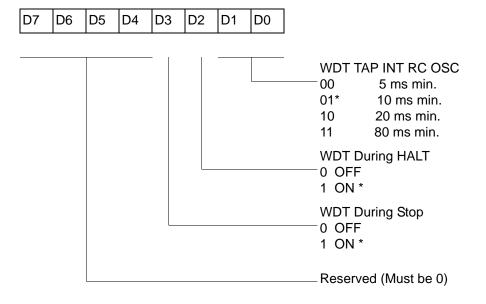

#### Watch-Dog Timer Mode Register (WDTMR)

The Watch-Dog Timer (WDT) is a retriggerable one-shot timer that resets the Z8<sup>®</sup> CPU if it reaches its terminal count. The WDT must initially be enabled by executing the WDT instruction. On subsequent executions of the WDT instruction, the WDT is refreshed. The WDT circuit is driven by an on-board RC-oscillator. The WDT instruction affects the Zero (Z), Sign (S), and Overflow (V) flags.

The POR clock source the internal RC-oscillator. Bits 0 and 1 of the WDT register control a tap circuit that determines the minimum timeout period. Bit 2 determines whether the WDT is active during HALT, and Bit 3 determines WDT activity during Stop. Bits 4 through 7 are reserved (Figure 37). This register is accessible only during the first 60 processor cycles (120 XTAL clocks) from the execution of the first instruction after Power-On-Reset, Watch-Dog Reset, or a Stop-Mode Recovery (Figure 36). After this point, the register cannot be modified by any means (intentional or otherwise). The WDTMR cannot be read. The register is located in Bank F of the Expanded Register Group at address location 0Fh. It is organized as shown in Figure 37.

WDTMR(0F)0Fh

\* Default setting after reset

#### Figure 37. Watch-Dog Timer Mode Register (Write Only)

#### WDT Time Select (D0, D1)

This bit selects the WDT time period. It is configured as indicated in Table 23.

#### WDTMR During STOP (D3)

This bit determines whether or not the WDT is active during STOP Mode. Because the XTAL clock is stopped during STOP Mode, the on-board RC has to be selected as the clock source to the WDT/POR counter. A 1 indicates active during Stop. The default is 1.

#### **EPROM Selectable Options**

There are seven EPROM Selectable Options to choose from based on ROM code requirements. These options are listed in Table 24.

#### Table 24. EPROM Selectable Options

| Port 00–03 Pull-Ups               | On/Off |

|-----------------------------------|--------|

| Port 04–07 Pull-Ups               | On/Off |

| Port 10–13 Pull-Ups               | On/Off |

| Port 14–17 Pull-Ups               | On/Off |

| Port 20–27 Pull-Ups               | On/Off |

| EPROM Protection                  | On/Off |

| Watch-Dog Timer at Power-On Reset | On/Off |

#### Voltage Brown-Out/Standby

An on-chip Voltage Comparator checks that the V<sub>DD</sub> is at the required level for correct operation of the device. Reset is globally driven when V<sub>DD</sub> falls below V<sub>BO</sub>. A small drop in V<sub>DD</sub> causes the XTAL1 and XTAL2 circuitry to stop the crystal or resonator clock. If the V<sub>DD</sub> is allowed to stay above V<sub>RAM</sub>, the RAM content is preserved. When the power level is returned to above V<sub>BO</sub>, the device performs a POR and functions normally.

69

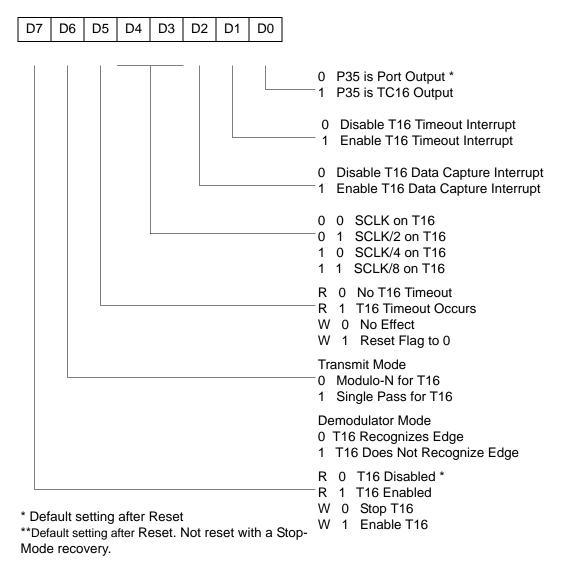

#### CTR2(0D)02H

Figure 41. T16 Control Register ((0D) 2H: Read/Write Except Where Noted)

#### CTR3(0D)03H

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                                                                                                                                                                                                                                        |

|----|----|----|----|----|----|----|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |    |    |    |    |    |    |    | Reserved<br>No effect when written<br>Always reads 11111<br>Sync Mode<br>0* Disable Sync Mode**<br>1 Enable Sync Mode<br>T <sub>8</sub> Enable<br>R 0* T <sub>8</sub> Disabled<br>R 1 T <sub>8</sub> Enabled<br>W0 Stop T <sub>8</sub> |

|    |    |    |    |    |    |    |    | W1 Enable $T_8$<br>$T_{16}$ Enable<br>$R 0^* T_{16}$ Disabled<br>$R 1 T_{16}$ Enabled<br>$W 0$ Stop $T_{16}$<br>$W 1$ Enable $T_{16}$                                                                                                  |

\* Default setting after reset. \*\* Default setting after reset. Not reset with a Stop Mode recovery.

#### Figure 42. T8/T16 Control Register (0D)03H: Read/Write (Except Where Noted)

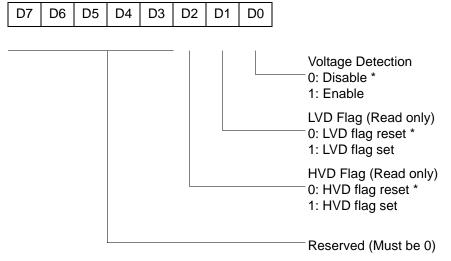

#### LVD(0D)0CH

\* Default setting after reset.

#### Figure 43. Voltage Detection Register

**Note:** Do not modify register P01M while checking a low-voltage condition. Switching noise of both ports 0 and 1 together might trigger the LVD flag.

# **Expanded Register File Control Registers (0F)**

The expanded register file control registers (0F) are depicted in Figures 44 through Figure 57.

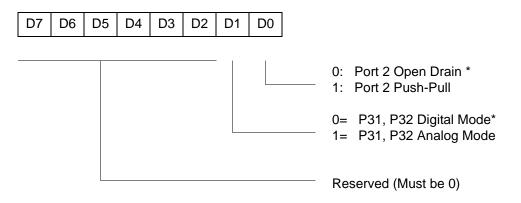

#### R247 P3M(F7H)

\* Default setting after reset. Not reset with a Stop Mode recovery.

Figure 49. Port 3 Mode Register (F7H: Write Only)

| ¥ | ≜<br>A |

|---|--------|

|   | A2 A   |

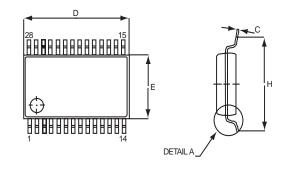

| SYMBOL | MILLIMETER |       |       | INCH       |       |       |

|--------|------------|-------|-------|------------|-------|-------|

|        | MIN        | NOM   | MAX   | MIN        | NOM   | MAX   |

| А      | 1.73       | 1.86  | 1.99  | 0.068      | 0.073 | 0.078 |

| A1     | 0.05       | 0.13  | 0.21  | 0.002      | 0.005 | 0.008 |

| A2     | 1.68       | 1.73  | 1.78  | 0.066      | 0.068 | 0.070 |

| В      | 0.25       |       | 0.38  | 0.010      |       | 0.015 |

| С      | 0.09       | -     | 0.20  | 0.004      | 0.006 | 0.008 |

| D      | 10.07      | 10.20 | 10.33 | 0.397      | 0.402 | 0.407 |

| E      | 5.20       | 5.30  | 5.38  | 0.205      | 0.209 | 0.212 |

| е      | 0.65 TYP   |       |       | 0.0256 TYP |       |       |

| Н      | 7.65       | 7.80  | 7.90  | 0.301      | 0.307 | 0.311 |

| L      | 0.63       | 0.75  | 0.95  | 0.025      | 0.030 | 0.037 |

CONTROLLING DIMENSIONS: MM LEADS ARE COPLANAR WITHIN .004 INCHES.

<u>DETAIL 'A'</u>

0-8

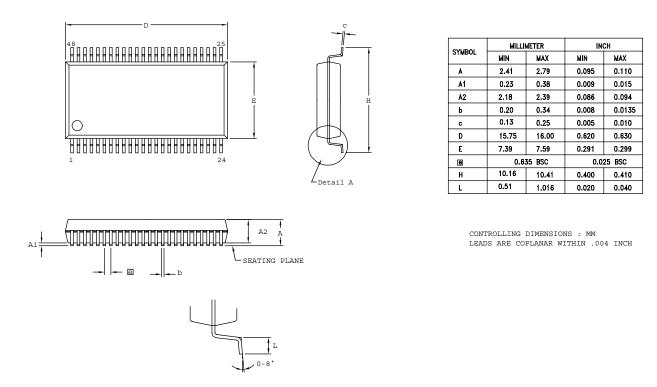

Figure 65. 28-Pin SSOP Package Diagram

| SYMBOL | MILLIN   | IETER | INCH     |       |  |

|--------|----------|-------|----------|-------|--|

| STMDUL | MIN      | MAX   | MIN      | MAX   |  |

| A1     | 0.51     | 1.02  | .020     | .040  |  |

| A2     | 3.18     | 3.94  | .125     | .155  |  |

| В      | 0.38     | 0.53  | .015     | .021  |  |

| B1     | 1.02     | 1.52  | .040     | .060  |  |

| С      | 0.23     | 0.38  | .009     | .015  |  |

| D      | 52.07    | 52.58 | 2.050    | 2.070 |  |

| E      | 15.24    | 15.75 | .600     | .620  |  |

| E1     | 13.59    | 14.22 | .535     | .560  |  |

| e      | 2.54 TYP |       | .100 TYP |       |  |

| eA     | 15.49    | 16.76 | .610     | .660  |  |

| L      | 3.05     | 3.81  | .120     | .150  |  |

| Q1     | 1.40     | 1.91  | .055     | .075  |  |

| S      | 1.52     | 2.29  | .060     | .090  |  |

CONTROLLING DIMENSIONS : INCH

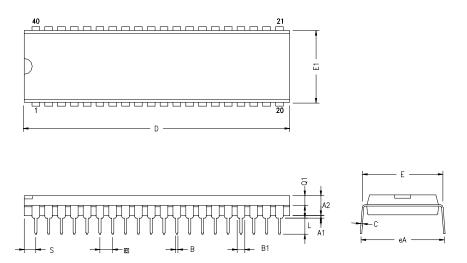

Figure 66. 40-Pin PDIP Package Diagram

Figure 68. 48-Pin SSOP Package Design

**Note:** Check with ZiLOG on the actual bonding diagram and coordinate for chip-on-board assembly.

#### 16KB Standard Temperature: 0° to +70°C

| Part Number    | Description         | Part Number    | Description         |

|----------------|---------------------|----------------|---------------------|

| ZGP323HSH4816C | 48-pin SSOP 16K OTP | ZGP323HSS2816C | 28-pin SOIC 16K OTP |

| ZGP323HSP4016C | 40-pin PDIP 16K OTP | ZGP323HSH2016C | 20-pin SSOP 16K OTP |

| ZGP323HSH2816C | 28-pin SSOP 16K OTP | ZGP323HSP2016C | 20-pin PDIP 16K OTP |

| ZGP323HSP2816C | 28-pin PDIP 16K OTP | ZGP323HSS2016C | 20-pin SOIC 16K OTP |

| 16KB Extended Temperature: -40° to +105°C |                     |                |                     |  |  |

|-------------------------------------------|---------------------|----------------|---------------------|--|--|

| Part Number                               | Description         | Part Number    | Description         |  |  |

| ZGP323HEH4816C                            | 48-pin SSOP 16K OTP | ZGP323HES2816C | 28-pin SOIC 16K OTP |  |  |

| ZGP323HEP4016C                            | 40-pin PDIP 16K OTP | ZGP323HEH2016C | 20-pin SSOP 16K OTP |  |  |

| ZGP323HEH2816C                            | 28-pin SSOP 16K OTP | ZGP323HEP2016C | 20-pin PDIP 16K OTP |  |  |

| ZGP323HEP2816C                            | 28-pin PDIP 16K OTP | ZGP323HES2016C | 20-pin SOIC 16K OTP |  |  |

# 16KB Automotive Temperature: -40° to +125°CPart NumberDescriptionPart NumberDescriptionZGP323HAH4816C48-pin SSOP 16K OTPZGP323HAS2816C28-pin SOIC 16K OTPZGP323HAP4016C40-pin PDIP 16K OTPZGP323HAH2016C20-pin SSOP 16K OTPZGP323HAH2816C28-pin SSOP 16K OTPZGP323HAP2016C20-pin PDIP 16K OTPZGP323HAP2816C28-pin PDIP 16K OTPZGP323HAS2016C20-pin SOIC 16K OTPZGP323HAP2816C28-pin PDIP 16K OTPZGP323HAS2016C20-pin SOIC 16K OTPReplace C with G for Lead-Free Packaging