Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | Z8                                                        |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | HLVD, POR, WDT                                            |

| Number of I/O              | 32                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | OTP                                                       |

| EEPROM Size                | -                                                         |

| RAM Size                   | 237 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 40-DIP (0.620", 15.75mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323hap4016g |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Tables

| Table 1.  | Revision History of this Document ii             |

|-----------|--------------------------------------------------|

| Table 2.  | Features                                         |

| Table 3.  | Power Connections 3                              |

| Table 4.  | 20-Pin PDIP/SOIC/SSOP/CDIP* Pin Identification 5 |

| Table 5.  | 28-Pin PDIP/SOIC/SSOP/CDIP* Pin Identification 6 |

| Table 6.  | 40- and 48-Pin Configuration                     |

| Table 7.  | Absolute Maximum Ratings                         |

| Table 8.  | Capacitance                                      |

| Table 9.  | GP323HS DC Characteristics                       |

| Table 10. | GP323HE DC Characteristics                       |

| Table 11. | GP323HA DC Characteristics                       |

| Table 12. | EPROM/OTP Characteristics                        |

| Table 13. | AC Characteristics                               |

| Table 14. | Port 3 Pin Function Summary                      |

| Table 15. | CTR1(0D)01H T8 and T16 Common Functions          |

| Table 16. | Interrupt Types, Sources, and Vectors 52         |

| Table 17. | IRQ Register                                     |

| Table 18. | SMR2(F)0DH:Stop Mode Recovery Register 2* 58     |

| Table 19. | Stop Mode Recovery Source 60                     |

| Table 20. | Watch-Dog Timer Time Select 63                   |

| Table 21. | EPROM Selectable Options 64                      |

PS023803-0305 List of Tables

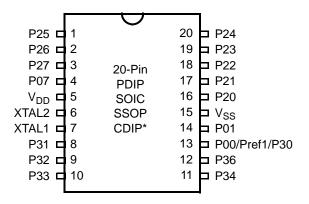

Figure 3. 20-Pin PDIP/SOIC/SSOP/CDIP\* Pin Configuration

Table 4. 20-Pin PDIP/SOIC/SSOP/CDIP\* Pin Identification

| Pin # | Symbol          | Function                                             | Direction                                   |

|-------|-----------------|------------------------------------------------------|---------------------------------------------|

| 1–3   | P25-P27         | Port 2, Bits 5,6,7                                   | Input/Output                                |

| 4     | P07             | Port 0, Bit 7                                        | Input/Output                                |

| 5     | V <sub>DD</sub> | Power Supply                                         |                                             |

| 6     | XTAL2           | Crystal Oscillator Clock                             | Output                                      |

| 7     | XTAL1           | Crystal Oscillator Clock                             | Input                                       |

| 8–10  | P31-P33         | Port 3, Bits 1,2,3                                   | Input                                       |

| 11,12 | P34. P36        | Port 3, Bits 4,6                                     | Output                                      |

| 13    | P00/Pref1/P30   | Port 0, Bit 0/Analog reference input<br>Port 3 Bit 0 | Input/Output for P00<br>Input for Pref1/P30 |

| 14    | P01             | Port 0, Bit 1                                        | Input/Output                                |

| 15    | V <sub>SS</sub> | Ground                                               |                                             |

| 16–20 | P20-P24         | Port 2, Bits 0,1,2,3,4                               | Input/Output                                |

PS023803-0305 Pin Description

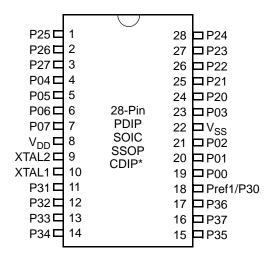

Figure 4. 28-Pin PDIP/SOIC/SSOP/CDIP\* Pin Configuration

Table 5. 28-Pin PDIP/SOIC/SSOP/CDIP\* Pin Identification

| Pin   | Symbol          | Direction    | Description                                              |

|-------|-----------------|--------------|----------------------------------------------------------|

| 1-3   | P25-P27         | Input/Output | Port 2, Bits 5,6,7                                       |

| 4-7   | P04-P07         | Input/Output | Port 0, Bits 4,5,6,7                                     |

| 8     | $V_{DD}$        |              | Power supply                                             |

| 9     | XTAL2           | Output       | Crystal, oscillator clock                                |

| 10    | XTAL1           | Input        | Crystal, oscillator clock                                |

| 11-13 | P31-P33         | Input        | Port 3, Bits 1,2,3                                       |

| 14    | P34             | Output       | Port 3, Bit 4                                            |

| 15    | P35             | Output       | Port 3, Bit 5                                            |

| 16    | P37             | Output       | Port 3, Bit 7                                            |

| 17    | P36             | Output       | Port 3, Bit 6                                            |

| 18    | Pref1/P30       | Input        | Analog ref input; connect to V <sub>CC</sub> if not used |

|       | Port 3 Bit 0    |              | Input for Pref1/P30                                      |

| 19-21 | P00-P02         | Input/Output | Port 0, Bits 0,1,2                                       |

| 22    | V <sub>SS</sub> |              | Ground                                                   |

| 23    | P03             | Input/Output | Port 0, Bit 3                                            |

| 24-28 | P20-P24         | Input/Output | Port 2, Bits 0-4                                         |

PS023803-0305 Pin Description

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 8 might cause permanent damage to the device. This rating is a stress rating only. Functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period might affect device reliability.

**Table 7. Absolute Maximum Ratings**

| Parameter                                                      | Minimum    | Maximum | Units | Notes |

|----------------------------------------------------------------|------------|---------|-------|-------|

| Ambient temperature under bias                                 | -40        | 125     | ° C   | 1     |

| Storage temperature                                            | -65        | +150    | ° C   |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3       | 7.0     | V     | 2     |

| Voltage on V <sub>DD</sub> pin with respect to V <sub>SS</sub> | -0.3       | 7.0     | V     |       |

| Maximum current on input and/or inactive output pin            | <b>-</b> 5 | +5      | μΑ    |       |

| Maximum output current from active output pin                  | -25        | +25     | mA    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |            | 75      | mA    |       |

#### Notes:

- 1. See Ordering Information.

- 2. This voltage applies to all pins except the following: V<sub>DD</sub>, P32, P33 and RESET.

# **Standard Test Conditions**

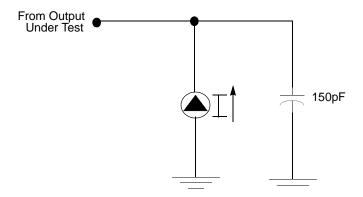

The characteristics listed in this product specification apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin (see Figure 7).

Figure 7. Test Load Diagram

# **AC Characteristics**

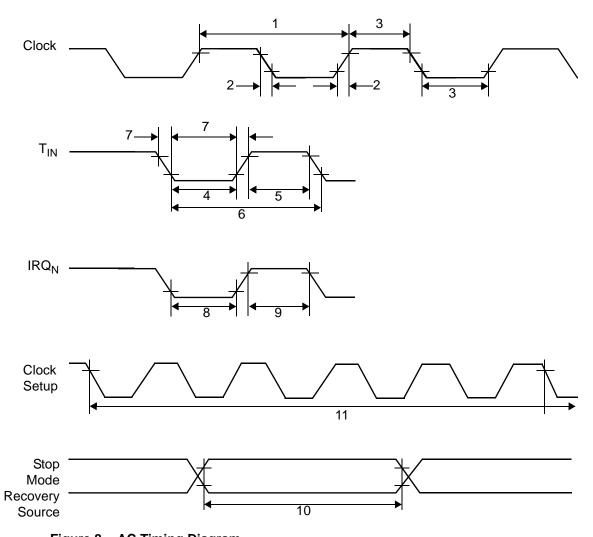

Figure 8 and Table 13 describe the Alternating Current (AC) characteristics.

Figure 8. AC Timing Diagram

PS023803-0305 AC Characteristics

21

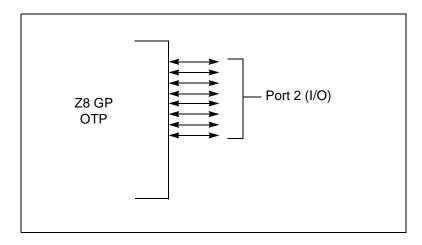

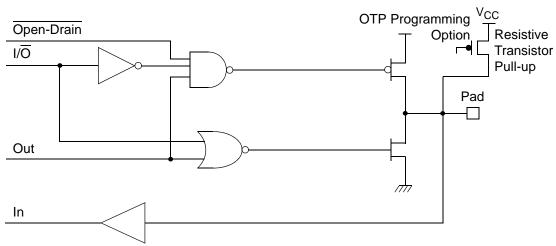

Figure 11. Port 2 Configuration

# Port 3 (P37-P30)

Port 3 is a 8-bit, CMOS-compatible fixed I/O port (see Figure 12). Port 3 consists of four fixed input (P33–P30) and four fixed output (P37–P34), which can be configured under software control for interrupt and as output from the counter/timers. P30, P31, P32, and P33 are standard CMOS inputs; P34, P35, P36, and P37 are push-pull outputs.

PS023803-0305 Pin Functions

#### **Comparator Inputs**

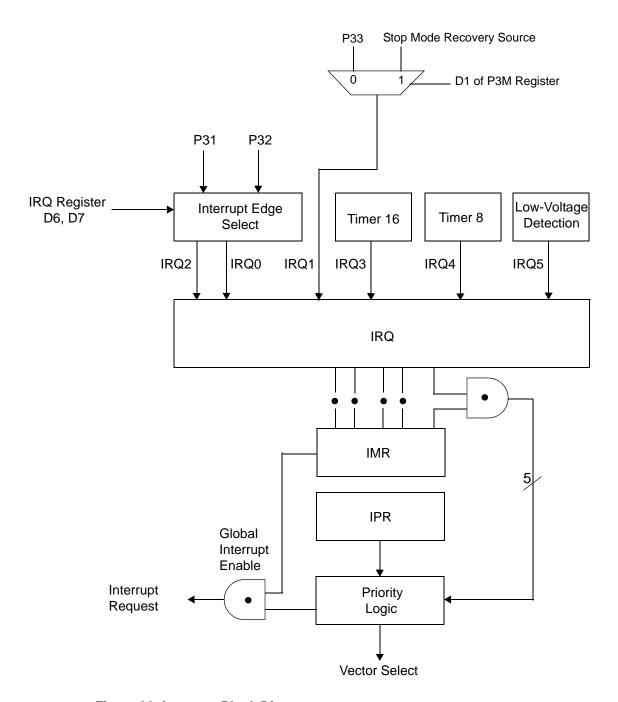

In analog mode, P31 and P32 have a comparator front end. The comparator reference is supplied to P33 and Pref1. In this mode, the P33 internal data latch and its corresponding IRQ1 are diverted to the SMR sources (excluding P31, P32, and P33) as indicated in Figure 12 on page 22. In digital mode, P33 is used as D3 of the Port 3 input register, which then generates IRQ1.

Note: Comparators are powered down by entering Stop Mode. For P31–P33 to be used in a Stop Mode Recovery source, these inputs must be placed into digital mode.

### **Comparator Outputs**

These channels can be programmed to be output on P34 and P37 through the PCON register.

# **RESET (Input, Active Low)**

Reset initializes the MCU and is accomplished either through Power-On, Watch-Dog Timer, Stop Mode Recovery, Low-Voltage detection, or external reset. During Power-On Reset and Watch-Dog Timer Reset, the internally generated reset drives the reset pin Low for the POR time. Any devices driving the external reset line must be open-drain to avoid damage from a possible conflict during reset conditions. Pull-up is provided internally.

When the Z8 GP asserts (Low) the RESET pin, the internal pull-up is disabled. The Z8 GP does not assert the RESET pin when under VBO.

Note: The external Reset does not initiate an exit from STOP mode.

# **Functional Description**

This device incorporates special functions to enhance the Z8<sup>®</sup>, functionality in consumer and battery-operated applications.

# **Program Memory**

This device addresses up to 32KB of OTP memory. The first 12 Bytes are reserved for interrupt vectors. These locations contain the six 16-bit vectors that correspond to the six available interrupts.

#### **RAM**

This device features 256B of RAM. See Figure 14.

#### **T16 Transmit Mode**

In NORMAL or PING-PONG mode, the output of T16 when not enabled, is dependent on CTR1, D0. If it is a 0, T16\_OUT is a 1; if it is a 1, T16\_OUT is 0. You can force the output of T16 to either a 0 or 1 whether it is enabled or not by programming CTR1 D3; D2 to a 10 or 11.

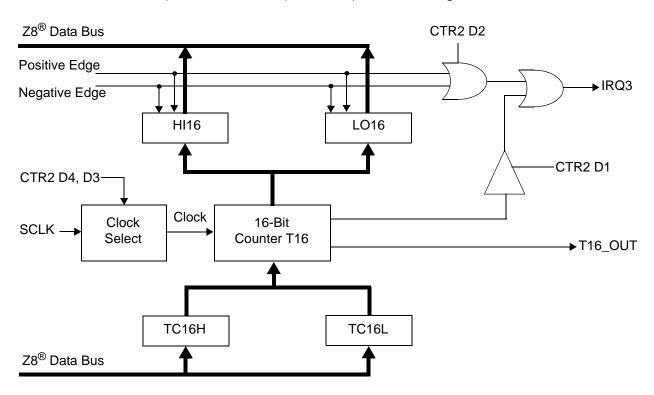

When T16 is enabled, TC16H \* 256 + TC16L is loaded, and T16\_OUT is switched to its initial value (CTR1, D0). When T16 counts down to 0, T16\_OUT is toggled (in NORMAL or PING-PONG mode), an interrupt (CTR2, D1) is generated (if enabled), and a status bit (CTR2, D5) is set. See Figure 25.

Figure 25. 16-Bit Counter/Timer Circuits

**Note:** Global interrupts override this function as described in "Interrupts" on page 50.

If T16 is in SINGLE-PASS mode, it is stopped at this point (see Figure 26). If it is in Modulo-N Mode, it is loaded with TC16H \* 256 + TC16L, and the counting continues (see Figure 27).

You can modify the values in TC16H and TC16L at any time. The new values take effect when they are loaded.

Figure 30. Interrupt Block Diagram

56

## Port 0 Output Mode (D2)

Bit 2 controls the output mode of port 0. A 1 in this location sets the output to push-pull, and a 0 sets the output to open-drain.

### **Stop-Mode Recovery Register (SMR)**

This register selects the clock divide value and determines the mode of Stop Mode Recovery (Figure 33). All bits are write only except bit 7, which is read only. Bit 7 is a flag bit that is hardware set on the condition of Stop recovery and reset by a power-on cycle. Bit 6 controls whether a low level or a high level at the XOR-gate input (Figure 35 on page 59) is required from the recovery source. Bit 5 controls the reset delay after recovery. Bits D2, D3, and D4 of the SMR register specify the source of the Stop Mode Recovery signal. Bits D0 determines if SCLK/TCLK are divided by 16 or not. The SMR is located in Bank F of the Expanded Register Group at address OBH.

**Table 22. Stop Mode Recovery Source**

| SMR:432 |    |    | Operation                          |

|---------|----|----|------------------------------------|

| D4      | D3 | D2 | Description of Action              |

| 0       | 0  | 0  | POR and/or external reset recovery |

| 0       | 0  | 1  | Reserved                           |

| 0       | 1  | 0  | P31 transition                     |

| 0       | 1  | 1  | P32 transition                     |

| 1       | 0  | 0  | P33 transition                     |

| 1       | 0  | 1  | P27 transition                     |

| 1       | 1  | 0  | Logical NOR of P20 through P23     |

| 1       | 1  | 1  | Logical NOR of P20 through P27     |

Note: Any Port 2 bit defined as an output drives the corresponding input to the default state. This condition allows the remaining inputs to control the AND/OR function. Refer to SMR2 register on page 61 for other recover sources.

### **Stop Mode Recovery Delay Select (D5)**

This bit, if Low, disables the T<sub>POR</sub> delay after Stop Mode Recovery. The default configuration of this bit is 1. If the "fast" wake up is selected, the Stop Mode Recovery source must be kept active for at least 5 TpC.

**Note:** This bit must be set to 1 if using a crystal or resonator clock source. The T<sub>POR</sub> delay allows the clock source to stabilize before executing instructions.

#### Stop Mode Recovery Edge Select (D6)

A 1 in this bit position indicates that a High level on any one of the recovery sources wakes the device from Stop Mode. A 0 indicates Low level recovery. The default is 0 on POR.

### Cold or Warm Start (D7)

This bit is read only. It is set to 1 when the device is recovered from Stop Mode. The bit is set to 0 when the device reset is other than Stop Mode Recovery (SMR).

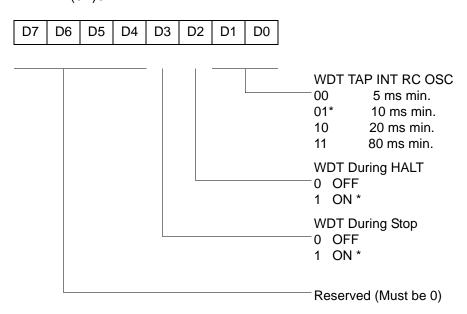

### **WDTMR During STOP (D3)**

This bit determines whether or not the WDT is active during STOP Mode. Because the XTAL clock is stopped during STOP Mode, the on-board RC has to be selected as the clock source to the WDT/POR counter. A 1 indicates active during Stop. The default is 1.

### **EPROM Selectable Options**

There are seven EPROM Selectable Options to choose from based on ROM code requirements. These options are listed in Table 24.

**Table 24. EPROM Selectable Options**

| Port 00-03 Pull-Ups               | On/Off |

|-----------------------------------|--------|

| Port 04–07 Pull-Ups               | On/Off |

| Port 10–13 Pull-Ups               | On/Off |

| Port 14–17 Pull-Ups               | On/Off |

| Port 20–27 Pull-Ups               | On/Off |

| EPROM Protection                  | On/Off |

| Watch-Dog Timer at Power-On Reset | On/Off |

### **Voltage Brown-Out/Standby**

An on-chip Voltage Comparator checks that the  $V_{DD}$  is at the required level for correct operation of the device. Reset is globally driven when  $V_{DD}$  falls below  $V_{BO}$ . A small drop in  $V_{DD}$  causes the XTAL1 and XTAL2 circuitry to stop the crystal or resonator clock. If the  $V_{DD}$  is allowed to stay above  $V_{RAM}$ , the RAM content is preserved. When the power level is returned to above  $V_{BO}$ , the device performs a POR and functions normally.

# WDTMR(0F)0FH

<sup>\*</sup> Default setting after reset. Not reset with a Stop Mode recovery.

Figure 47. Watch-Dog Timer Register ((0F) 0FH: Write Only)

# **Standard Control Registers**

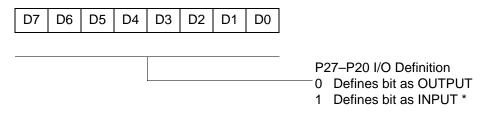

R246 P2M(F6H)

<sup>\*</sup> Default setting after reset. Not reset with a Stop Mode recovery.

Figure 48. Port 2 Mode Register (F6H: Write Only)

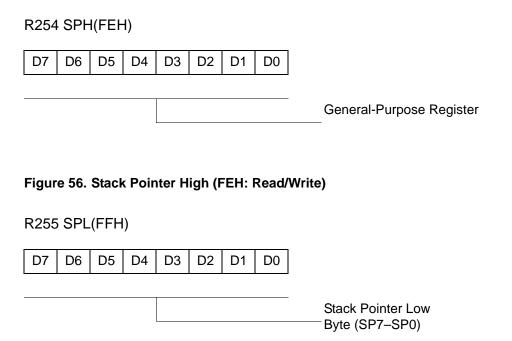

Figure 57. Stack Pointer Low (FFH: Read/Write)

# **Package Information**

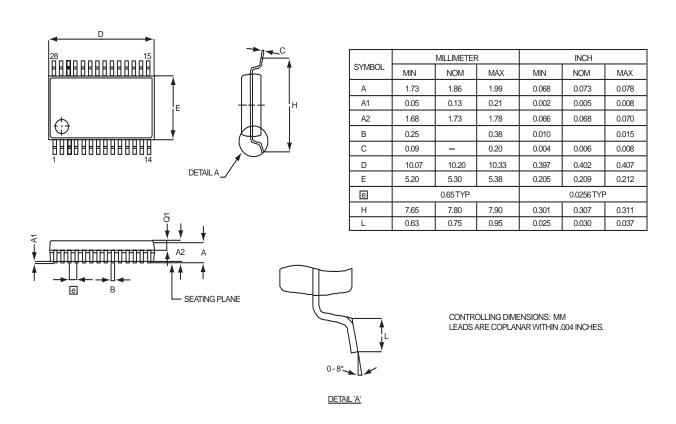

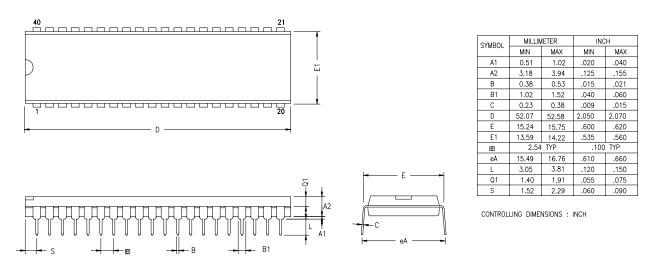

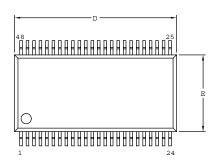

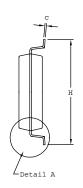

Package information for all versions of ZGP323H is depicted in Figures 59 through Figure 68.

PS023803-0305 Package Information

Figure 65. 28-Pin SSOP Package Diagram

Figure 66. 40-Pin PDIP Package Diagram

PS023803-0305 Package Information

| SYMBOL | MILLI     | MILLIMETER |       | СН     |

|--------|-----------|------------|-------|--------|

| STMBOL | MIN       | MAX        | MIN   | MAX    |

| A      | 2.41      | 2.79       | 0.095 | 0.110  |

| A1     | 0.23      | 0.38       | 0.009 | 0.015  |

| A2     | 2.18      | 2.39       | 0.086 | 0.094  |

| Ь      | 0.20      | 0.34       | 0.008 | 0.0135 |

| C      | 0.13      | 0.25       | 0.005 | 0.010  |

| D      | 15.75     | 16.00      | 0.620 | 0.630  |

| E      | 7.39      | 7.59       | 0.291 | 0.299  |

| e      | 0.635 BSC |            | 0.0   | 25 BSC |

| Н      | 10.16     | 10.41      | 0.400 | 0.410  |

| L      | 0.51      | 1.016      | 0.020 | 0.040  |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH

Figure 68. 48-Pin SSOP Package Design

**Note:** Check with ZiLOG on the actual bonding diagram and coordinate for chip-on-board assembly.

PS023803-0305 Package Information

| 16KB Standard Temperature: 0° to +70°C    |                         |                |                     |  |  |

|-------------------------------------------|-------------------------|----------------|---------------------|--|--|

| Part Number                               | Description             | Part Number    | Description         |  |  |

| ZGP323HSH4816C                            | 48-pin SSOP 16K OTP     | ZGP323HSS2816C | 28-pin SOIC 16K OTP |  |  |

| ZGP323HSP4016C                            | 40-pin PDIP 16K OTP     | ZGP323HSH2016C | 20-pin SSOP 16K OTP |  |  |

| ZGP323HSH2816C                            | 28-pin SSOP 16K OTP     | ZGP323HSP2016C | 20-pin PDIP 16K OTP |  |  |

| ZGP323HSP2816C                            | 28-pin PDIP 16K OTP     | ZGP323HSS2016C | 20-pin SOIC 16K OTP |  |  |

|                                           |                         |                |                     |  |  |

| 16KB Extended Temperature: -40° to +105°C |                         |                |                     |  |  |

| Part Number                               | Description             | Part Number    | Description         |  |  |

| ZGP323HEH4816C                            | 48-pin SSOP 16K OTP     | ZGP323HES2816C | 28-pin SOIC 16K OTP |  |  |

| ZGP323HEP4016C                            | 40-pin PDIP 16K OTP     | ZGP323HEH2016C | 20-pin SSOP 16K OTP |  |  |

| ZGP323HEH2816C                            | 28-pin SSOP 16K OTP     | ZGP323HEP2016C | 20-pin PDIP 16K OTP |  |  |

| ZGP323HEP2816C                            | 28-pin PDIP 16K OTP     | ZGP323HES2016C | 20-pin SOIC 16K OTP |  |  |

|                                           |                         |                |                     |  |  |

| 16KB Automotive T                         | emperature: -40° to +12 | 25°C           |                     |  |  |

| Part Number                               | Description             | Part Number    | Description         |  |  |

| ZGP323HAH4816C                            | 48-pin SSOP 16K OTP     | ZGP323HAS2816C | 28-pin SOIC 16K OTP |  |  |

| ZGP323HAP4016C                            | 40-pin PDIP 16K OTP     | ZGP323HAH2016C | 20-pin SSOP 16K OTP |  |  |

| ZGP323HAH2816C                            | 28-pin SSOP 16K OTP     | ZGP323HAP2016C | 20-pin PDIP 16K OTP |  |  |

| ZGP323HAP2816C                            | 28-pin PDIP 16K OTP     | ZGP323HAS2016C | 20-pin SOIC 16K OTP |  |  |

| Replace C with G for                      | r Lead-Free Packaging   |                |                     |  |  |

PS023803-0305 Ordering Information

| 8KB Standard Temperature: 0° to +70°C |                    |                |                    |

|---------------------------------------|--------------------|----------------|--------------------|

| Part Number                           | Description        | Part Number    | Description        |

| ZGP323HSH4808C                        | 48-pin SSOP 8K OTP | ZGP323HSS2808C | 28-pin SOIC 8K OTP |

| ZGP323HSP4008C                        | 40-pin PDIP 8K OTP | ZGP323HSH2008C | 20-pin SSOP 8K OTP |

| ZGP323HSH2808C                        | 28-pin SSOP 8K OTP | ZGP323HSP2008C | 20-pin PDIP 8K OTP |

| ZGP323HSP2808C                        | 28-pin PDIP 8K OTP | ZGP323HSS2008C | 20-pin SOIC 8K OTP |

| 8KB Extended Temperature: -40° to +105°C |                    |                |                    |  |

|------------------------------------------|--------------------|----------------|--------------------|--|

| Part Number                              | Description        | Part Number    | Description        |  |

| ZGP323HEH4808C                           | 48-pin SSOP 8K OTP | ZGP323HES2808C | 28-pin SOIC 8K OTP |  |

| ZGP323HEP4008C                           | 40-pin PDIP 8K OTP | ZGP323HEH2008C | 20-pin SSOP 8K OTP |  |

| ZGP323HEH2808C                           | 28-pin SSOP 8K OTP | ZGP323HEP2008C | 20-pin PDIP 8K OTP |  |

| ZGP323HEP2808C                           | 28-pin PDIP 8K OTP | ZGP323HES2008C | 20-pin SOIC 8K OTP |  |

| 8KB Automotive Temperature: -40° to +125°C |                       |                |                    |

|--------------------------------------------|-----------------------|----------------|--------------------|

| Part Number                                | Description           | Part Number    | Description        |

| ZGP323HAH4808C                             | 48-pin SSOP 8K OTP    | ZGP323HAS2808C | 28-pin SOIC 8K OTP |

| ZGP323HAP4008C                             | 40-pin PDIP 8K OTP    | ZGP323HAH2008C | 20-pin SSOP 8K OTP |

| ZGP323HAH2808C                             | 28-pin SSOP 8K OTP    | ZGP323HAP2008C | 20-pin PDIP 8K OTP |

| ZGP323HAP2808C                             | 28-pin PDIP 8K OTP    | ZGP323HAS2008C | 20-pin SOIC 8K OTP |

| Replace C with G fo                        | r Lead-Free Packaging |                |                    |

PS023803-0305 Ordering Information

| Numerics                              | demodulation mode flowchart 45          |

|---------------------------------------|-----------------------------------------|

|                                       |                                         |

| 16-bit counter/timer circuits 46      | EPROM selectable options 64             |

| 20-pin DIP package diagram 82         | glitch filter circuitry 40              |

| 20-pin SSOP package diagram 84        | halt instruction 54                     |

| 28-pin DIP package diagram 86         | input circuit 40                        |

| 28-pin SOICpackage diagram 85         | interrupt block diagram 51              |

| 28-pin SSOP package diagram 87        | interrupt types, sources and vectors 52 |

| 40-pin DIP package diagram 87         | oscillator configuration 53             |

| 48-pin SSOP package diagram 89        | output circuit 49                       |

| 8-bit counter/timer circuits 42       | ping-pong mode 48                       |

| A                                     | port configuration register 55          |

| absolute maximum ratings 10           | resets and WDT 63                       |

| AC                                    | SCLK circuit 58                         |

| characteristics 16                    | stop instruction 54                     |

| timing diagram 16                     | stop mode recovery register 57          |

| address spaces, basic 2               | stop mode recovery register 2 61        |

| architecture 2                        | stop mode recovery source 59            |

| expanded register file 28             | T16 demodulation mode 47                |

| В                                     | T16 transmit mode 46                    |

| basic address spaces 2                | T16_OUT in modulo-N mode 47             |

| block diagram, ZLP32300 functional 3  | T16_OUT in single-pass mode 47          |

| C                                     | T8 demodulation mode 43                 |

| capacitance 11                        | T8 transmit mode 40                     |

| characteristics                       | T8_OUT in modulo-N mode 43              |

| AC 16                                 | T8_OUT in single-pass mode 43           |

| DC 11                                 | transmit mode flowchart 41              |

| clock 53                              | voltage detection and flags 65          |

| comparator inputs/outputs 25          | watch-dog timer mode register 62        |

| configuration                         | watch-dog timer time select 63          |

| port 0 19                             | CTR(D)01h T8 and T16 Common Functions   |

| port 1 20                             | 35                                      |

| port 2 21                             | D                                       |

| port 3 22                             | DC characteristics 11                   |

| port 3 counter/timer 24               | demodulation mode                       |

| counter/timer                         | count capture flowchart 44              |

| 16-bit circuits 46                    | flowchart 45                            |

| 8-bit circuits 42                     | T16 47                                  |

| brown-out voltage/standby 64          | T8 43                                   |

| clock 53                              | description                             |

| demodulation mode count capture flow- | functional 25                           |

| chart 44                              | general 2                               |

# **Z8**<sup>®</sup> OTP Microcontroller with IR Timers

| The same of the sa |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 200 PM 200 PM 200 PM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 0.000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| pin 4                                       | program memory map 26                     |

|---------------------------------------------|-------------------------------------------|

| E                                           | RAM 25                                    |

| EPROM                                       | register description 65                   |

| selectable options 64                       | register file 30                          |

| expanded register file 26                   | register pointer 29                       |

| expanded register file architecture 28      | register pointer detail 31                |

| expanded register file control registers 71 | SMR2(F)0D1h register 40                   |

| flag 80                                     | stack 31                                  |

| interrupt mask register 79                  | TC16H(D)07h register 32                   |

| interrupt priority register 78              | TC16L(D)06h register 33                   |

| interrupt request register 79               | TC8H(D)05h register 33                    |

| port 0 and 1 mode register 77               | TC8L(D)04h register 33                    |

| port 2 configuration register 75            | G                                         |

| port 3 mode register 76                     | glitch filter circuitry 40                |

| port configuration register 75              | Н                                         |

| register pointer 80                         | halt instruction, counter/timer 54        |

| stack pointer high register 81              | I                                         |

| stack pointer low register 81               | input circuit 40                          |

| stop-mode recovery register 73              | interrupt block diagram, counter/timer 51 |

| stop-mode recovery register 2 74            | interrupt types, sources and vectors 52   |

| T16 control register 69                     | L                                         |

| T8 and T16 common control functions reg-    | low-voltage detection register 65         |

| ister 67                                    | M                                         |

| T8/T16 control register 70                  | memory, program 25                        |

| TC8 control register 66                     | modulo-N mode                             |

| watch-dog timer register 75                 | T16_OUT 47                                |

| F                                           | T8_OUT 43                                 |

| features                                    | 0                                         |

| standby modes 1                             | oscillator configuration 53               |

| functional description                      | output circuit, counter/timer 49          |

| counter/timer functional blocks 40          | P                                         |

| CTR(D)01h register 35                       | package information                       |

| CTR0(D)00h register 33                      | 20-pin DIP package diagram 82             |

| CTR2(D)02h register 37                      | 20-pin SSOP package diagram 84            |

| CTR3(D)03h register 39                      | 28-pin DIP package diagram 86             |

| expanded register file 26                   | 28-pin SOIC package diagram 85            |

| expanded register file architecture 28      | 28-pin SSOP package diagram 87            |

| HI16(D)09h register 32                      | 40-pin DIP package diagram 87             |

| HI8(D)0Bh register 32                       | 48-pin SSOP package diagram 89            |

| L08(D)0Ah register 32                       | pin configuration                         |

| L0I6(D)08h register 32                      | 20-pin DIP/SOIC/SSOP 5                    |