# E·XFL

#### Zilog - ZGP323HEH4816C00TR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | Z8                                                            |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | -                                                             |

| Peripherals                | HLVD, POR, WDT                                                |

| Number of I/O              | 32                                                            |

| Program Memory Size        | 16KB (16K x 8)                                                |

| Program Memory Type        | OTP                                                           |

| EEPROM Size                | -                                                             |

| RAM Size                   | 237 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                     |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323heh4816c00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in Table 1 reflects a change to this document from its previous revision. To see more detail, click the appropriate link in the table.

| Table 1. | Revision | History | of this | Document |

|----------|----------|---------|---------|----------|

|----------|----------|---------|---------|----------|

| Date             | Revision<br>Level | Section                                      | Description                                                                                                                                                                                                      | Page<br># |

|------------------|-------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| December<br>2004 | 02                | deleted mask option and 10. Added new        | consumption, STOP and HALT mode current values,<br>note, clarified temperature ranges in Tables 6 and 8<br>Tables 9 and 10. Also added Characterization data to<br>ed Program/Erase Endurance value in Table 12. | 11,12,    |

|                  |                   | Removed Preliminar                           | y designation                                                                                                                                                                                                    | All       |

| March<br>2005    | 03                | Minor change to Tab<br>pin CDIP parts in the | le 9 Electrical Characteristics. Added 20, 28 and 40-<br>ordering Section.                                                                                                                                       | 11,90     |

## ZGP323H Product Specification

| Figure 34. | SCLK Circuit                                                          | 58 |

|------------|-----------------------------------------------------------------------|----|

| Figure 35. | Stop Mode Recovery Source                                             | 59 |

| Figure 36. | Stop Mode Recovery Register 2 ((0F)DH:D2–D4, D6 Write Only)           | 61 |

| Figure 37. | Watch-Dog Timer Mode Register (Write Only)                            | 62 |

| Figure 38. | Resets and WDT                                                        | 63 |

| Figure 39. | TC8 Control Register ((0D)O0H: Read/Write Except Where Noted)         | 66 |

| Figure 40. | T8 and T16 Common Control Functions ((0D)01H: Read/Write)             | 67 |

| Figure 41. | T16 Control Register ((0D) 2H: Read/Write Except Where Noted) .       | 69 |

| Figure 42. | T8/T16 Control Register (0D)03H: Read/Write (Except Where             |    |

|            | Noted)                                                                |    |

|            | Voltage Detection Register                                            |    |

| -          | Port Configuration Register (PCON)(0F)00H: Write Only)                | 72 |

| Figure 45. | Stop Mode Recovery Register ((0F)0BH: D6–D0=Write Only, D7=Read Only) | 73 |

| Figure 46. | Stop Mode Recovery Register 2 ((0F)0DH:D2–D4, D6 Write Only)          | 74 |

| Figure 47. | Watch-Dog Timer Register ((0F) 0FH: Write Only)                       | 75 |

| Figure 48. | Port 2 Mode Register (F6H: Write Only)                                | 75 |

| Figure 49. | Port 3 Mode Register (F7H: Write Only)                                | 76 |

| Figure 50. | Port 0 and 1 Mode Register (F8H: Write Only)                          | 77 |

| Figure 51. | Interrupt Priority Register (F9H: Write Only)                         | 78 |

| Figure 52. | Interrupt Request Register (FAH: Read/Write)                          | 79 |

| Figure 53. | Interrupt Mask Register (FBH: Read/Write)                             | 79 |

| Figure 54. | Flag Register (FCH: Read/Write)                                       | 80 |

| Figure 55. | Register Pointer (FDH: Read/Write)                                    | 80 |

| Figure 56. | Stack Pointer High (FEH: Read/Write)                                  | 81 |

| Figure 57. | Stack Pointer Low (FFH: Read/Write)                                   | 81 |

| Figure 58. | 20-Pin CDIP Package                                                   | 82 |

| Figure 59. | 20-Pin PDIP Package Diagram                                           | 82 |

| Figure 60. | 20-Pin SOIC Package Diagram                                           | 83 |

| Figure 61. | 20-Pin SSOP Package Diagram                                           | 84 |

| Figure 62. | 28-Pin SOIC Package Diagram                                           | 85 |

| Figure 63. | 28-Pin CDIP Package Diagram                                           | 86 |

| Figure 64. | 28-Pin PDIP Package Diagram                                           | 86 |

| Figure 65. | 28-Pin SSOP Package Diagram                                           | 87 |

| Figure 66. | 40-Pin PDIP Package Diagram                                           | 87 |

| Figure 67. | 40-Pin CDIP Package Diagram                                           | 88 |

| -          |                                                                       |    |

## ZGP323H Product Specification

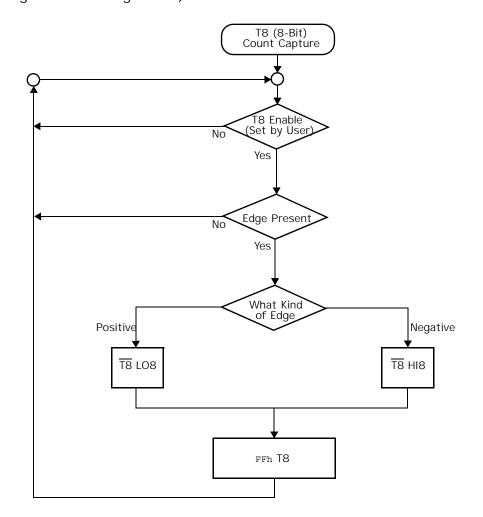

into LO8; if it is a negative edge, data is put into HI8. From that point, one of the edge detect status bits (CTR1, D1; D0) is set, and an interrupt can be generated if enabled (CTR0, D2). Meanwhile, T8 is loaded with and starts counting again. If T8 reaches 0, the timeout status bit (CTR0, D5) is set, and an interrupt can be generated if enabled (CTR0, D1). T8 then continues counting firm (see Figure 23 and Figure 24).

Figure 23. Demodulation Mode Count Capture Flowchart

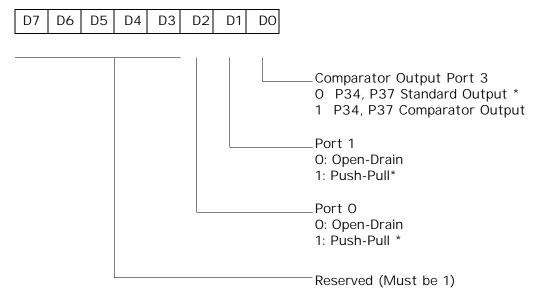

## PCON(OF)OOH

\* Default setting after reset

Figure 44. Port Configuration Register (PCON)(OF)OOH: Write Only)

## **Expanded Register File Control Registers (0D)**

The expanded register file control registers (0D) are depicted in Figure 39 through Figure 43.

### CTR0(0D)00H

|    |    |    | 1  | 1  |    | 1  |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----|----|----|----|----|----|----|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |    |    |    |    |    |    |    | <ul> <li>0 P34 as Port Output *</li> <li>1 Timer8 Output</li> <li>0 Disable T8 Timeout Interrupt * *</li> <li>1 Enable T8 Timeout Interrupt</li> <li>0 Disable T8 Data Capture Interrupt * *</li> <li>1 Enable T8 Data Capture Interrupt * *</li> <li>1 Enable T8 Data Capture Interrupt</li> <li>00 SCLK on T8* *</li> <li>01 SCLK/2 on T8</li> <li>10 SCLK/4 on T8</li> <li>11 SCLK/8 on T8</li> <li>R 0 No T8 Counter Timeout * *</li> <li>R 1 T8 Counter Timeout Occurred</li> <li>W 0 No Effect</li> <li>W 1 Reset Flag to 0</li> <li>0 Modulo-N *</li> <li>1 Single Pass</li> <li>R 0 T8 Disabled *</li> <li>R 1 T8 Enabled</li> <li>W 0 Stop T8</li> <li>W 1 Enable T8</li> </ul> |

\* Default setting after reset.

\* \* Default setting after Reset.. Not reset with a Stop-Mode recovery.

#### Figure 39. TC8 Control Register ((0D)O0H: Read/Write Except Where Noted)

## Example

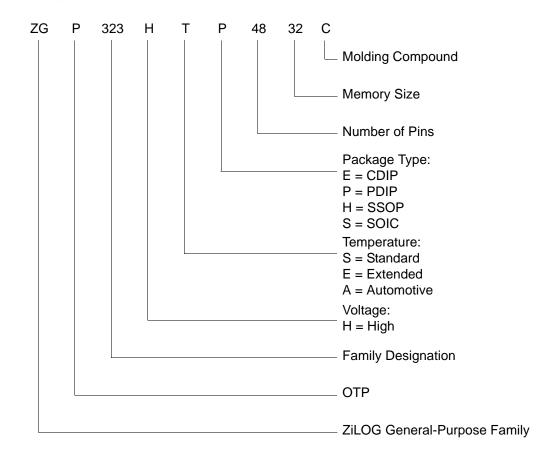

#### ZGP323H Z8<sup>®</sup> OTP Microcontroller with IR Timers

pin 4 Ε **EPROM** selectable options 64 expanded register file 26 expanded register file architecture 28 expanded register file control registers 71 flag 80 interrupt mask register 79 interrupt priority register 78 interrupt request register 79 port 0 and 1 mode register 77 port 2 configuration register 75 port 3 mode register 76 port configuration register 75 register pointer 80 stack pointer high register 81 stack pointer low register 81 stop-mode recovery register 73 stop-mode recovery register 2 74 T16 control register 69 T8 and T16 common control functions register 67 T8/T16 control register 70 TC8 control register 66 watch-dog timer register 75 F features standby modes 1 functional description counter/timer functional blocks 40 CTR(D)01h register 35 CTR0(D)00h register 33 CTR2(D)02h register 37 CTR3(D)03h register 39 expanded register file 26 expanded register file architecture 28 HI16(D)09h register 32 HI8(D)0Bh register 32 L08(D)0Ah register 32 L0I6(D)08h register 32

program memory map 26 **RAM 25** register description 65 register file 30 register pointer 29 register pointer detail 31 SMR2(F)0D1h register 40 stack 31 TC16H(D)07h register 32 TC16L(D)06h register 33 TC8H(D)05h register 33 TC8L(D)04h register 33 G glitch filter circuitry 40 Η halt instruction, counter/timer 54 input circuit 40 interrupt block diagram, counter/timer 51 interrupt types, sources and vectors 52 L low-voltage detection register 65 Μ memory, program 25 modulo-N mode T16 OUT 47 T8 OUT 43 0 oscillator configuration 53 output circuit, counter/timer 49 Ρ package information 20-pin DIP package diagram 82 20-pin SSOP package diagram 84 28-pin DIP package diagram 86 28-pin SOIC package diagram 85 28-pin SSOP package diagram 87 40-pin DIP package diagram 87 48-pin SSOP package diagram 89 pin configuration 20-pin DIP/SOIC/SSOP 5