# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | Z8                                                        |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | HLVD, POR, WDT                                            |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | OTP                                                       |

| EEPROM Size                | -                                                         |

| RAM Size                   | 237 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323hes2004c |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>-</b> : 00 |                            | 04 | ~ |

|---------------|----------------------------|----|---|

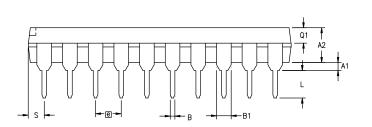

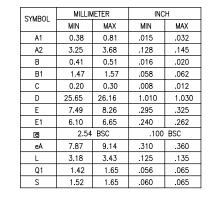

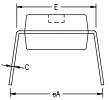

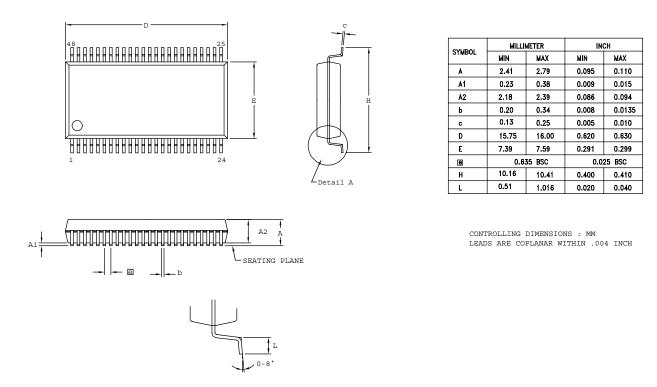

| Figure 68.    | 48-Pin SSOP Package Design |    | J |

#### Table 3. Power Connections

| Connection | Circuit         | Device          |  |

|------------|-----------------|-----------------|--|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |  |

| Ground     | GND             | V <sub>SS</sub> |  |

Note: Refer to the specific package for available pins.

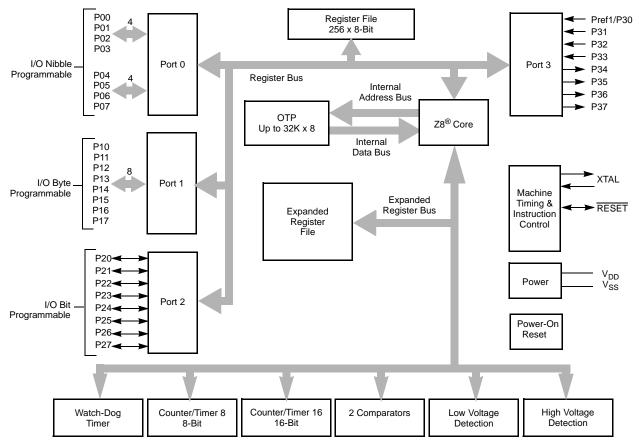

Figure 1. Functional Block Diagram

| P25<br>P26<br>P27<br>P04<br>P05<br>P07<br>V <sub>DD</sub><br>XTAL2<br>XTAL1<br>P31<br>P32<br>P34 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>2<br>3<br>14 | 28-Pin<br>PDIP<br>SOIC<br>SSOP<br>CDIP* | 28<br>27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16 | <ul> <li>P24</li> <li>P23</li> <li>P22</li> <li>P21</li> <li>P20</li> <li>P03</li> <li>V<sub>SS</sub></li> <li>P02</li> <li>P01</li> <li>P00</li> <li>Pref1/P30</li> <li>P36</li> <li>P35</li> </ul> |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P34 🗖                                                                                            | 14                                                                    |                                         | 15                                                                         | 🖵 P35                                                                                                                                                                                                |

#### Figure 4. 28-Pin PDIP/SOIC/SSOP/CDIP\* Pin Configuration

#### Table 5. 28-Pin PDIP/SOIC/SSOP/CDIP\* Pin Identification

| Pin   | Symbol          | Direction    | Description                                              |

|-------|-----------------|--------------|----------------------------------------------------------|

| 1-3   | P25-P27         | Input/Output | Port 2, Bits 5,6,7                                       |

| 4-7   | P04-P07         | Input/Output | Port 0, Bits 4,5,6,7                                     |

| 8     | V <sub>DD</sub> |              | Power supply                                             |

| 9     | XTAL2           | Output       | Crystal, oscillator clock                                |

| 10    | XTAL1           | Input        | Crystal, oscillator clock                                |

| 11-13 | P31-P33         | Input        | Port 3, Bits 1,2,3                                       |

| 14    | P34             | Output       | Port 3, Bit 4                                            |

| 15    | P35             | Output       | Port 3, Bit 5                                            |

| 16    | P37             | Output       | Port 3, Bit 7                                            |

| 17    | P36             | Output       | Port 3, Bit 6                                            |

| 18    | Pref1/P30       | Input        | Analog ref input; connect to V <sub>CC</sub> if not used |

|       | Port 3 Bit 0    |              | Input for Pref1/P30                                      |

| 19-21 | P00-P02         | Input/Output | Port 0, Bits 0,1,2                                       |

| 22    | V <sub>SS</sub> |              | Ground                                                   |

| 23    | P03             | Input/Output | Port 0, Bit 3                                            |

| 24-28 | P20-P24         | Input/Output | Port 2, Bits 0-4                                         |

|       | -          |            |    |              |

|-------|------------|------------|----|--------------|

|       |            | $\bigcirc$ |    |              |

| NC    |            |            | 40 | ⊐ NC         |

| P25   | <b>2</b>   |            | 39 | ⊐ P24        |

| P26   | <b>-</b> 3 |            | 38 | ⊐ P23        |

| P27   | 4          |            | 37 | ⊐ P22        |

| P04   | 5          |            | 36 | <b>コ</b> P21 |

| P05   | 6          |            | 35 | ⊐ P20        |

| P06   | 7          |            | 34 | □ P03        |

| P14   | 8          | 40-Pin     | 33 | <b>コ</b> P13 |

| P15   | 9          | PDIP       | 32 | ⊐ P12        |

| P07   | 10         | CDIP*      | 31 | ⊐ VSS        |

| VDD   | 11         |            | 30 | ⊐ P02        |

| P16   | 12         |            | 39 | ⊐ P11        |

| P17   | 13         |            | 28 | <b>コ</b> P10 |

| XTAL2 | 14         |            | 27 | <b>D</b> P01 |

| XTAL1 | 15         |            | 26 | <b>P</b> 00  |

| P31   | 16         |            | 25 | □ Pref1/P30  |

| P32   | 17         |            | 24 | ⊐ P36        |

| P33   | 18         |            | 23 | <b>D</b> P37 |

| P34   | 19         |            | 22 | ⊐ P35        |

| NC    | 20         |            | 21 | RESET        |

#### Figure 5. 40-Pin PDIP/CDIP\* Pin Configuration

**Note:** \*Windowed Cerdip. These units are intended to be used for engineering code development only. ZiLOG does not recommend/guarantee this package for production use.

#### ZGP323H Product Specification

| 40-Pin PDIP # | 48-Pin SSOP # | Symbol          |

|---------------|---------------|-----------------|

| 33            | 40            | P13             |

| 8             | 9             | P14             |

| 9             | 10            | P15             |

| 12            | 15            | P16             |

| 13            | 16            | P17             |

| 35            | 42            | P20             |

| 36            | 43            | P21             |

| 37            | 44            | P22             |

| 38            | 45            | P23             |

| 39            | 46            | P24             |

| 2             | 2             | P25             |

| 3             | 3             | P26             |

| 4             | 4             | P27             |

| 16            | 19            | P31             |

| 17            | 20            | P32             |

| 18            | 21            | P33             |

| 19            | 22            | P34             |

| 22            | 26            | P35             |

| 24            | 28            | P36             |

| 23            | 27            | P37             |

| 20            | 23            | NC              |

| 40            | 47            | NC              |

| 1             | 1             | NC              |

| 21            | 25            | RESET           |

| 15            | 18            | XTAL1           |

| 14            | 17            | XTAL2           |

| 11            | 12, 13        | V <sub>DD</sub> |

| 31            | 24, 37, 38    | V <sub>SS</sub> |

| 25            | 29            | Pref1/P30       |

|               | 48            | NC              |

|               | 6             | NC              |

|               | 14            | NC              |

|               | 30            | NC              |

|               | 36            | NC              |

|               |               |                 |

#### Table 6. 40- and 48-Pin Configuration (Continued)

|                     |                                             |                 | T <sub>A</sub> = -40°0 | C to +105 | °C                       |       |                                                            |         |

|---------------------|---------------------------------------------|-----------------|------------------------|-----------|--------------------------|-------|------------------------------------------------------------|---------|

| Symbol              | Parameter                                   | V <sub>CC</sub> | Min                    | Typ(7)    | Max                      | Units | Conditions                                                 | Notes   |

| V <sub>OH2</sub>    | Output High Voltage<br>(P36, P37, P00, P01) | 2.0-5.5         | V <sub>CC</sub> -0.8   |           |                          | V     | I <sub>OH</sub> = -7mA                                     |         |

| V <sub>OL1</sub>    | Output Low Voltage                          | 2.0-5.5         |                        |           | 0.4                      | V     | $I_{OL} = 4.0 \text{mA}$                                   |         |

| V <sub>OL2</sub>    | Output Low Voltage<br>(P00, P01, P36, P37)  | 2.0-5.5         |                        |           | 0.8                      | V     | I <sub>OL</sub> = 10mA                                     |         |

| V <sub>OFFSET</sub> | Comparator Input<br>Offset Voltage          | 2.0-5.5         |                        |           | 25                       | mV    |                                                            |         |

| V <sub>REF</sub>    | Comparator<br>Reference<br>Voltage          | 2.0-5.5         | 0                      |           | V <sub>DD</sub><br>-1.75 | V     |                                                            |         |

| IIL                 | Input Leakage                               | 2.0-5.5         | -1                     |           | 1                        | μA    | V <sub>IN</sub> = 0V, V <sub>CC</sub><br>Pull-ups disabled |         |

| R <sub>PU</sub>     | Pull-up Resistance                          | 2.0V            | 200.0                  |           | 700.0                    | KΩ    | V <sub>IN</sub> = 0V; Pullups selected by mask             |         |

|                     |                                             | 3.6V            | 50.0                   |           | 300.0                    | KΩ    | option                                                     |         |

|                     |                                             | 5.0V            | 25.0                   |           | 175.0                    | KΩ    | -                                                          |         |

| I <sub>OL</sub>     | Output Leakage                              | 2.0-5.5         | -1                     |           | 1                        | μA    | $V_{IN} = 0V, V_{CC}$                                      |         |

| I <sub>CC</sub>     | Supply Current                              | 2.0V            |                        | 1         | 3                        | mA    | at 8.0 MHz                                                 | 1, 2    |

|                     |                                             | 3.6V            |                        | 5         | 10                       | mA    | at 8.0 MHz                                                 | 1, 2    |

|                     |                                             | 5.5V            |                        | 10        | 15                       | mA    | at 8.0 MHz                                                 | 1, 2    |

| I <sub>CC1</sub>    | Standby Current                             | 2.0V            |                        | 0.5       | 1.6                      | mA    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                      | 1, 2, 6 |

|                     | (HALT Mode)                                 | 3.6V            |                        | 0.8       | 2.0                      | mA    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                      | 1, 2, 6 |

|                     |                                             | 5.5V            |                        | 1.3       | 3.2                      | mA    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                      | 1, 2, 6 |

| I <sub>CC2</sub>    | Standby Current (Stop                       | 2.0V            |                        | 1.6       | 12                       | μA    | V <sub>IN</sub> = 0 V, V <sub>CC</sub> WDT not Running     | 3       |

|                     | Mode)                                       | 3.6V            |                        | 1.8       | 15                       | μA    | V <sub>IN</sub> = 0 V, V <sub>CC</sub> WDT not Running     | 3       |

|                     |                                             | 5.5V            |                        | 1.9       | 18                       | μA    | $V_{IN} = 0 V, V_{CC} WDT not Running$                     | 3       |

|                     |                                             | 2.0V            |                        | 5         | 30                       | μA    | $V_{IN} = 0 V, V_{CC} WDT$ is Running                      | 3       |

|                     |                                             | 3.6V            |                        | 8         | 40                       | μA    | $V_{IN} = 0 V, V_{CC} WDT$ is Running                      | 3       |

|                     |                                             | 5.5V            |                        | 15        | 60                       | μA    | $V_{IN} = 0 V, V_{CC} WDT$ is Running                      | 3       |

| I <sub>LV</sub>     | Standby Current<br>(Low Voltage)            |                 |                        | 1.2       | 6                        | μA    | Measured at 1.3V                                           | 4       |

| V <sub>BO</sub>     | V <sub>CC</sub> Low Voltage<br>Protection   |                 |                        | 1.9       | 2.15                     | V     | 8MHz maximum<br>Ext. CLK Freq.                             |         |

| $V_{LVD}$           | V <sub>CC</sub> Low Voltage<br>Detection    |                 |                        | 2.4       |                          | V     |                                                            |         |

| V <sub>HVD</sub>    | Vcc High Voltage<br>Detection               |                 |                        | 2.7       |                          | V     |                                                            |         |

| -                   |                                             |                 |                        |           |                          |       |                                                            |         |

#### Table 10. GP323HE DC Characteristics (Continued)

Notes:

1. All outputs unloaded, inputs at rail.

2. CL1 = CL2 = 100 pF.

3. Oscillator stopped.

4. Oscillator stops when  $V_{CC}$  falls below  $V_{BO}$  limit.

It is strongly recommended to add a filter capacitor (minimum 0.1 μF), physically close to VCC and V<sub>SS</sub> pins if operating voltage fluctuations are anticipated, such as those resulting from driving an Infrared LED.

6. Comparator and Timers are on. Interrupt disabled.

7. Typical values shown are at 25 degrees C.

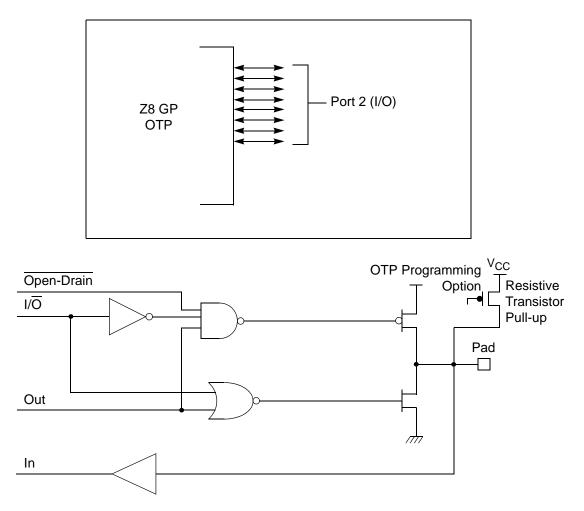

Figure 11. Port 2 Configuration

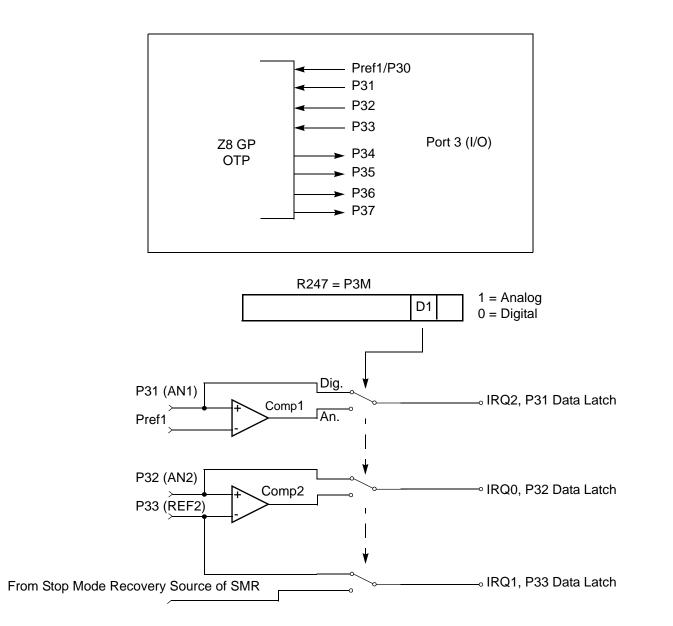

#### Port 3 (P37–P30)

Port 3 is a 8-bit, CMOS-compatible fixed I/O port (see Figure 12). Port 3 consists of four fixed input (P33–P30) and four fixed output (P37–P34), which can be configured under software control for interrupt and as output from the counter/timers. P30, P31, P32, and P33 are standard CMOS inputs; P34, P35, P36, and P37 are push-pull outputs.

#### Figure 12. Port 3 Configuration

Two on-board comparators process analog signals on P31 and P32, with reference to the voltage on Pref1 and P33. The analog function is enabled by programming the Port 3 Mode Register (bit 1). P31 and P32 are programmable as rising, falling, or both edge triggered interrupts (IRQ register bits 6 and 7). Pref1 and P33 are the comparator reference voltage inputs. Access to the Counter Timer edgedetection circuit is through P31 or P20 (see "T8 and T16 Common Functions—

CTR1(0D)01H" on page 35). Other edge detect and IRQ modes are described in Table 14.

**Note:** Comparators are powered down by entering Stop Mode. For P31–P33 to be used in a Stop Mode Recovery (SMR) source, these inputs must be placed into digital mode.

| Pin       | I/O | Counter/Timers | Comparator | Interrupt |

|-----------|-----|----------------|------------|-----------|

| Pref1/P30 | IN  |                | RF1        |           |

| P31       | IN  | IN             | AN1        | IRQ2      |

| P32       | IN  |                | AN2        | IRQ0      |

| P33       | IN  |                | RF2        | IRQ1      |

| P34       | OUT | Т8             | AO1        |           |

| P35       | OUT | T16            |            |           |

| P36       | OUT | T8/16          |            |           |

| P37       | OUT |                | AO2        |           |

| P20       | I/O | IN             |            |           |

#### Table 14. Port 3 Pin Function Summary

>

Port 3 also provides output for each of the counter/timers and the AND/OR Logic (see Figure 13). Control is performed by programming bits D5–D4 of CTR1, bit 0 of CTR0, and bit 0 of CTR2.

# 25

#### **Comparator Inputs**

In analog mode, P31 and P32 have a comparator front end. The comparator reference is supplied to P33 and Pref1. In this mode, the P33 internal data latch and its corresponding IRQ1 are diverted to the SMR sources (excluding P31, P32, and P33) as indicated in Figure 12 on page 22. In digital mode, P33 is used as D3 of the Port 3 input register, which then generates IRQ1.

**Note:** Comparators are powered down by entering Stop Mode. For P31–P33 to be used in a Stop Mode Recovery source, these inputs must be placed into digital mode.

#### **Comparator Outputs**

These channels can be programmed to be output on P34 and P37 through the PCON register.

#### **RESET (Input, Active Low)**

Reset initializes the MCU and is accomplished either through Power-On, Watch-Dog Timer, Stop Mode Recovery, Low-Voltage detection, or external reset. During Power-On Reset and Watch-Dog Timer Reset, the internally generated reset drives the reset pin Low for the POR time. Any devices driving the external reset line must be open-drain to avoid damage from a possible conflict during reset conditions. Pull-up is provided internally.

When the Z8 GP asserts (Low) the  $\overline{\text{RESET}}$  pin, the internal pull-up is disabled. The Z8 GP does not assert the  $\overline{\text{RESET}}$  pin when under VBO.

**Note:** The external Reset does not initiate an exit from STOP mode.

## **Functional Description**

This device incorporates special functions to enhance the Z8<sup>®</sup>, functionality in consumer and battery-operated applications.

#### **Program Memory**

This device addresses up to 32KB of OTP memory. The first 12 Bytes are reserved for interrupt vectors. These locations contain the six 16-bit vectors that correspond to the six available interrupts.

#### RAM

This device features 256B of RAM. See Figure 14.

#### ZGP323H Product Specification

| Leastion of C                    | 0700      | Not Accessible      |

|----------------------------------|-----------|---------------------|

| Location of 3                    | 2768<br>1 | On-Chip             |

| instruction                      |           | ROM                 |

| executed<br>after RESET          |           |                     |

|                                  | 12        | Reset Start Address |

|                                  | 11        | IRQ5                |

|                                  | 10        | IRQ5                |

|                                  | 9         | IRQ4                |

|                                  | 8         | IRQ4                |

|                                  | 7         | IRQ3                |

| Interrupt Vector<br>(Lower Byte) | 6         | IRQ3                |

|                                  | 5         | IRQ2                |

| Interrupt Vecto                  | 4<br>r    | ✓ IRQ2              |

| (Upper Byte                      |           | IRQ1                |

|                                  | 2         | IRQ1                |

|                                  | 1         | IRQ0                |

|                                  | 0         | IRQ0                |

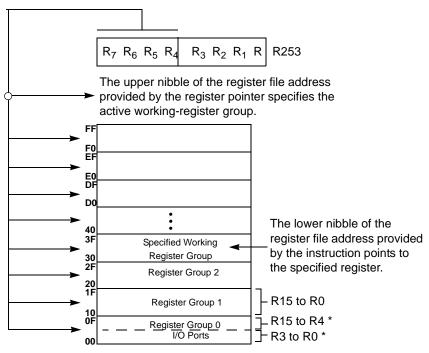

#### **Expanded Register File**

The register file has been expanded to allow for additional system control registers and for mapping of additional peripheral devices into the register address area. The Z8<sup>®</sup> register address space (R0 through R15) has been implemented as 16 banks, with 16 registers per bank. These register groups are known as the

Figure 17. Register Pointer—Detail

#### Stack

The internal register file is used for the stack. An 8-bit Stack Pointer SPL (R255) is used for the internal stack that resides in the general-purpose registers (R4–R239). SPH (R254) can be used as a general-purpose register.

40

#### Table 18. CTR3 (D)03H: T8/T16 Control Register (Continued)

| Field    | Bit Position |   | Value | Description        |

|----------|--------------|---|-------|--------------------|

| Reserved | 43210        | R | 1     | Always reads 11111 |

|          |              | W | х     | No Effect          |

\*Indicates the value upon Power-On Reset.

\*\*Indicates the value upon Power-On Reset. Not reset with a Stop Mode recovery.

#### **Counter/Timer Functional Blocks**

#### **Input Circuit**

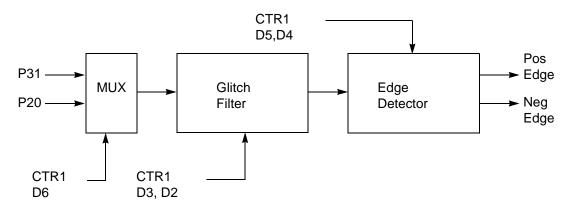

The edge detector monitors the input signal on P31 or P20. Based on CTR1 D5– D4, a pulse is generated at the Pos Edge or Neg Edge line when an edge is detected. Glitches in the input signal that have a width less than specified (CTR1 D3, D2) are filtered out (see Figure 18).

#### Figure 18. Glitch Filter Circuitry

#### **T8 Transmit Mode**

Before T8 is enabled, the output of T8 depends on CTR1, D1. If it is 0, T8\_OUT is 1; if it is 1, T8\_OUT is 0. See Figure 19.

#### 46

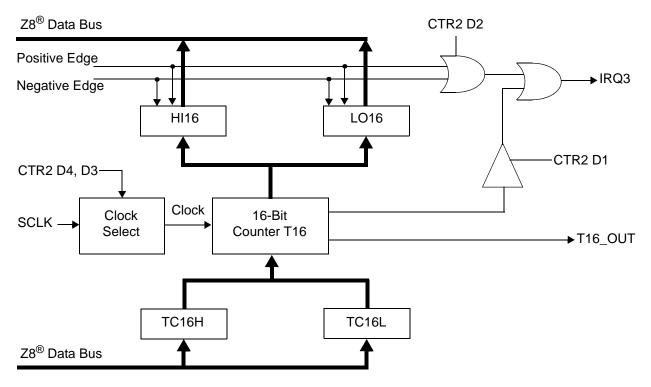

#### **T16 Transmit Mode**

In NORMAL or PING-PONG mode, the output of T16 when not enabled, is dependent on CTR1, D0. If it is a 0, T16\_OUT is a 1; if it is a 1, T16\_OUT is 0. You can force the output of T16 to either a 0 or 1 whether it is enabled or not by programming CTR1 D3; D2 to a 10 or 11.

When T16 is enabled, TC16H \* 256 + TC16L is loaded, and T16\_OUT is switched to its initial value (CTR1, D0). When T16 counts down to 0, T16\_OUT is toggled (in NORMAL or PING-PONG mode), an interrupt (CTR2, D1) is generated (if enabled), and a status bit (CTR2, D5) is set. See Figure 25.

Figure 25. 16-Bit Counter/Timer Circuits

**Note:** Global interrupts override this function as described in "Interrupts" on page 50.

If T16 is in SINGLE-PASS mode, it is stopped at this point (see Figure 26). If it is in Modulo-N Mode, it is loaded with TC16H \* 256 + TC16L, and the counting continues (see Figure 27).

You can modify the values in TC16H and TC16L at any time. The new values take effect when they are loaded.

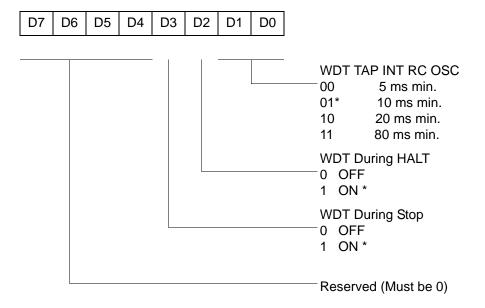

#### WDTMR(0F)0FH

\* Default setting after reset. Not reset with a Stop Mode recovery.

Figure 47. Watch-Dog Timer Register ((0F) 0FH: Write Only)

## **Standard Control Registers**

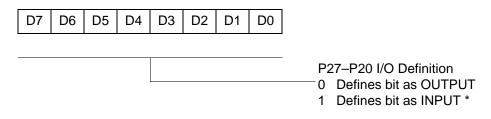

#### R246 P2M(F6H)

\* Default setting after reset. Not reset with a Stop Mode recovery.

#### Figure 48. Port 2 Mode Register (F6H: Write Only)

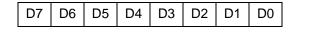

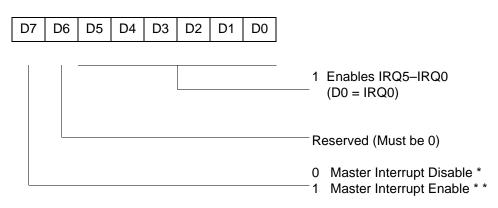

#### R250 IRQ(FAH)

#### Figure 52. Interrupt Request Register (FAH: Read/Write)

#### R251 IMR(FBH)

\* Default setting after reset

\* \* Only by using EI, DI instruction; DI is required before changing the IMR register

#### Figure 53. Interrupt Mask Register (FBH: Read/Write)

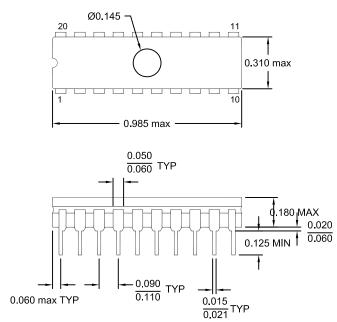

Figure 58. 20-Pin CDIP Package

Figure 59. 20-Pin PDIP Package Diagram

CONTROLLING DIMENSIONS : INCH

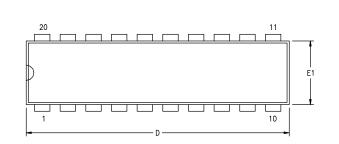

Figure 68. 48-Pin SSOP Package Design

**Note:** Check with ZiLOG on the actual bonding diagram and coordinate for chip-on-board assembly.

#### 16KB Standard Temperature: 0° to +70°C

| Part Number    | Description         | Part Number    | Description         |

|----------------|---------------------|----------------|---------------------|

| ZGP323HSH4816C | 48-pin SSOP 16K OTP | ZGP323HSS2816C | 28-pin SOIC 16K OTP |

| ZGP323HSP4016C | 40-pin PDIP 16K OTP | ZGP323HSH2016C | 20-pin SSOP 16K OTP |

| ZGP323HSH2816C | 28-pin SSOP 16K OTP | ZGP323HSP2016C | 20-pin PDIP 16K OTP |

| ZGP323HSP2816C | 28-pin PDIP 16K OTP | ZGP323HSS2016C | 20-pin SOIC 16K OTP |

| 16KB Extended Temperature: -40° to +105°C |                     |                |                     |

|-------------------------------------------|---------------------|----------------|---------------------|

| Part Number                               | Description         | Part Number    | Description         |

| ZGP323HEH4816C                            | 48-pin SSOP 16K OTP | ZGP323HES2816C | 28-pin SOIC 16K OTP |

| ZGP323HEP4016C                            | 40-pin PDIP 16K OTP | ZGP323HEH2016C | 20-pin SSOP 16K OTP |

| ZGP323HEH2816C                            | 28-pin SSOP 16K OTP | ZGP323HEP2016C | 20-pin PDIP 16K OTP |

| ZGP323HEP2816C                            | 28-pin PDIP 16K OTP | ZGP323HES2016C | 20-pin SOIC 16K OTP |

# 16KB Automotive Temperature: -40° to +125°CPart NumberDescriptionPart NumberDescriptionZGP323HAH4816C48-pin SSOP 16K OTPZGP323HAS2816C28-pin SOIC 16K OTPZGP323HAP4016C40-pin PDIP 16K OTPZGP323HAH2016C20-pin SSOP 16K OTPZGP323HAH2816C28-pin SSOP 16K OTPZGP323HAP2016C20-pin PDIP 16K OTPZGP323HAP2816C28-pin PDIP 16K OTPZGP323HAS2016C20-pin SOIC 16K OTPZGP323HAP2816C28-pin PDIP 16K OTPZGP323HAS2016C20-pin SOIC 16K OTPReplace C with G for Lead-Free Packaging

# ZGP323H Z8<sup>®</sup> OTP Microcontroller with IR Timers

Numerics 16-bit counter/timer circuits 46 20-pin DIP package diagram 82 20-pin SSOP package diagram 84 28-pin DIP package diagram 86 28-pin SOICpackage diagram 85 28-pin SSOP package diagram 87 40-pin DIP package diagram 87 48-pin SSOP package diagram 89 8-bit counter/timer circuits 42 А absolute maximum ratings 10 AC characteristics 16 timing diagram 16 address spaces, basic 2 architecture 2 expanded register file 28 В basic address spaces 2 block diagram, ZLP32300 functional 3 С capacitance 11 characteristics AC 16 DC 11 clock 53 comparator inputs/outputs 25 configuration port 0 19 port 1 20 port 2 21 port 3 22 port 3 counter/timer 24 counter/timer 16-bit circuits 46 8-bit circuits 42 brown-out voltage/standby 64 clock 53 demodulation mode count capture flowchart 44

demodulation mode flowchart 45 EPROM selectable options 64 glitch filter circuitry 40 halt instruction 54 input circuit 40 interrupt block diagram 51 interrupt types, sources and vectors 52 oscillator configuration 53 output circuit 49 ping-pong mode 48 port configuration register 55 resets and WDT 63 SCLK circuit 58 stop instruction 54 stop mode recovery register 57 stop mode recovery register 2 61 stop mode recovery source 59 T16 demodulation mode 47 T16 transmit mode 46 T16 OUT in modulo-N mode 47 T16\_OUT in single-pass mode 47 T8 demodulation mode 43 T8 transmit mode 40 T8 OUT in modulo-N mode 43 T8\_OUT in single-pass mode 43 transmit mode flowchart 41 voltage detection and flags 65 watch-dog timer mode register 62 watch-dog timer time select 63 CTR(D)01h T8 and T16 Common Functions 35 D DC characteristics 11 demodulation mode count capture flowchart 44 flowchart 45 T1647 T8 43 description functional 25 general 2