# E·XFL

# Zilog - ZGP323HSH2016C Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | Z8                                                        |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | HLVD, POR, WDT                                            |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 16KB (16K x 8)                                            |

| Program Memory Type        | OTP                                                       |

| EEPROM Size                | -                                                         |

| RAM Size                   | 237 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323hsh2016c |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>-</b> : 00 |                            | 04 | ~ |

|---------------|----------------------------|----|---|

| Figure 68.    | 48-Pin SSOP Package Design |    | J |

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 8 might cause permanent damage to the device. This rating is a stress rating only. Functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period might affect device reliability.

#### Table 7. Absolute Maximum Ratings

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | 125     | ° C   | 1     |

| Storage temperature                                 | -65     | +150    | ° C   |       |

| Voltage on any pin with respect to $V_{SS}$         | -0.3    | 7.0     | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | 7.0     | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 75      | mA    |       |

| Notos:                                              |         |         |       |       |

Notes:

1. See Ordering Information.

2. This voltage applies to all pins except the following: V<sub>DD</sub>, P32, P33 and RESET.

# **Standard Test Conditions**

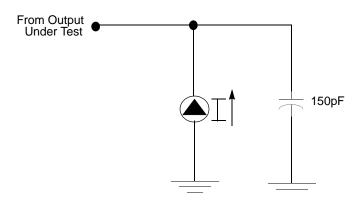

The characteristics listed in this product specification apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin (see Figure 7).

Figure 7. Test Load Diagram

|                  |                                          |                 | T <sub>A</sub> =0°C t | o +70°C |     |       |                                                        |         |

|------------------|------------------------------------------|-----------------|-----------------------|---------|-----|-------|--------------------------------------------------------|---------|

| Symbol           | Parameter                                | V <sub>CC</sub> | Min                   | Typ(7)  | Max | Units | Conditions                                             | Notes   |

| I <sub>OL</sub>  | Output Leakage                           | 2.0-5.5         | -1                    |         | 1   | μA    | $V_{IN} = 0V, V_{CC}$                                  |         |

| I <sub>CC</sub>  | Supply Current                           | 2.0V            |                       | 1       | 3   | mA    | at 8.0 MHz                                             | 1, 2    |

|                  |                                          | 3.6V            |                       | 5       | 10  | mA    | at 8.0 MHz                                             | 1, 2    |

|                  |                                          | 5.5V            |                       | 10      | 15  | mA    | at 8.0 MHz                                             | 1, 2    |

| I <sub>CC1</sub> | Standby Current                          | 2.0V            |                       | 0.5     | 1.6 | mA    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                  | 1, 2, 6 |

|                  | (HALT Mode)                              | 3.6V            |                       | 0.8     | 2.0 | mA    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                  | 1, 2, 6 |

|                  |                                          | 5.5V            |                       | 1.3     | 3.2 | mA    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                  | 1, 2, 6 |

| I <sub>CC2</sub> | Standby Current (Stop                    | 2.0V            |                       | 1.6     | 8   | μΑ    | V <sub>IN</sub> = 0 V, V <sub>CC</sub> WDT not Running | 3       |

|                  | Mode)                                    | 3.6V            |                       | 1.8     | 10  | μA    | $V_{IN} = 0 V, V_{CC} WDT not Running$                 | 3       |

|                  |                                          | 5.5V            |                       | 1.9     | 12  | μA    | $V_{IN} = 0 V, V_{CC} WDT not Running$                 | 3       |

|                  |                                          | 2.0V            |                       | 5       | 20  | μA    | V <sub>IN</sub> = 0 V, V <sub>CC</sub> WDT is Running  | 3       |

|                  |                                          | 3.6V            |                       | 8       | 30  | μA    | V <sub>IN</sub> = 0 V, V <sub>CC</sub> WDT is Running  | 3       |

|                  |                                          | 5.5V            |                       | 15      | 45  | μA    | $V_{IN} = 0 V, V_{CC} WDT$ is Running                  | 3       |

| I <sub>LV</sub>  | Standby Current<br>(Low Voltage)         |                 |                       | 1.2     | 6   | μA    | Measured at 1.3V                                       | 4       |

| V <sub>BO</sub>  | V <sub>CC</sub> Low Voltage              |                 |                       | 1.9     | 2.0 | V     | 8MHz maximum                                           |         |

|                  | Protection                               |                 |                       |         |     |       | Ext. CLK Freq.                                         |         |

| V <sub>LVD</sub> | V <sub>CC</sub> Low Voltage<br>Detection |                 |                       | 2.4     |     | V     |                                                        |         |

| V <sub>HVD</sub> | Vcc High Voltage<br>Detection            |                 |                       | 2.7     |     | V     |                                                        |         |

#### Table 9. GP323HS DC Characteristics (Continued)

#### Notes:

1. All outputs unloaded, inputs at rail.

2. CL1 = CL2 = 100 pF.

3. Oscillator stopped.

4. Oscillator stops when  $V_{CC}$  falls below  $V_{BO}$  limit.

It is strongly recommended to add a filter capacitor (minimum 0.1 μF), physically close to VCC and V<sub>SS</sub> pins if operating voltage fluctuations are anticipated, such as those resulting from driving an Infrared LED.

- 6. Comparator and Timers are on. Interrupt disabled.

- 7. Typical values shown are at 25 degrees C.

## Table 10. GP323HE DC Characteristics

| T <sub>A</sub> = -40°C to +105°C |                             |                 |                      |        |                      |       |                                       |       |

|----------------------------------|-----------------------------|-----------------|----------------------|--------|----------------------|-------|---------------------------------------|-------|

| Symbol                           | Parameter                   | V <sub>CC</sub> | Min                  | Typ(7) | Max                  | Units | Conditions                            | Notes |

| V <sub>CC</sub>                  | Supply Voltage              |                 | 2.0                  |        | 5.5                  | V     | See Note 5                            | 5     |

| V <sub>CH</sub>                  | Clock Input High<br>Voltage | 2.0-5.5         | 0.8 V <sub>CC</sub>  |        | V <sub>CC</sub> +0.3 | V     | Driven by External<br>Clock Generator |       |

| V <sub>CL</sub>                  | Clock Input Low<br>Voltage  | 2.0-5.5         | V <sub>SS</sub> –0.3 |        | 0.4                  | V     | Driven by External<br>Clock Generator |       |

| V <sub>IH</sub>                  | Input High Voltage          | 2.0-5.5         | 0.7 V <sub>CC</sub>  |        | V <sub>CC</sub> +0.3 | V     |                                       |       |

| V <sub>IL</sub>                  | Input Low Voltage           | 2.0-5.5         | V <sub>SS</sub> -0.3 |        | 0.2 V <sub>CC</sub>  | V     |                                       |       |

| V <sub>OH1</sub>                 | Output High Voltage         | 2.0-5.5         | V <sub>CC</sub> -0.4 |        |                      | V     | $I_{OH} = -0.5 \text{mA}$             |       |

|    |                  |                                      |                                          | –40°C to<br>–40°C to | o +70°C (S)<br>+105°C (E)<br>+125°C (A)<br>MHz |                      |       | Watch-Dog<br>Timer<br>Mode<br>Register |

|----|------------------|--------------------------------------|------------------------------------------|----------------------|------------------------------------------------|----------------------|-------|----------------------------------------|

| No | Symbol           | Parameter                            | V <sub>CC</sub>                          | Minimum              | Maximum                                        | Units                | Notes | (D1, D0)                               |

| 1  | ТрС              | Input Clock Period                   | 2.0–5.5                                  | 121                  | DC                                             | ns                   | 1     |                                        |

| 2  | TrC,TfC          | Clock Input Rise and Fall Times      | 2.0–5.5                                  |                      | 25                                             | ns                   | 1     |                                        |

| 3  | TwC              | Input Clock Width                    | 2.0–5.5                                  | 37                   |                                                | ns                   | 1     |                                        |

| 4  | TwTinL           | Timer Input<br>Low Width             | 2.0<br>5.5                               | 100<br>70            |                                                | ns                   | 1     |                                        |

| 5  | TwTinH           | Timer Input High<br>Width            | 2.0–5.5                                  | 3ТрС                 |                                                |                      | 1     |                                        |

| 6  | TpTin            | Timer Input Period                   | 2.0–5.5                                  | 8TpC                 |                                                |                      | 1     |                                        |

| 7  | TrTin,TfTin      | Timer Input Rise and Fall Timers     | 2.0–5.5                                  |                      | 100                                            | ns                   | 1     |                                        |

| 8  | TwIL             | Interrupt Request<br>Low Time        | 2.0<br>5.5                               | 100<br>70            |                                                | ns                   | 1, 2  |                                        |

| 9  | TwlH             | Interrupt Request<br>Input High Time | 2.0–5.5                                  | 5TpC                 |                                                |                      | 1, 2  |                                        |

| 10 | Twsm             | Stop-Mode<br>Recovery Width          | 2.0–5.5                                  | 12                   |                                                | ns                   | 3     |                                        |

|    |                  | Spec                                 |                                          | 5TpC                 |                                                |                      | 4     |                                        |

| 11 | Tost             | Oscillator<br>Start-Up Time          | 2.0–5.5                                  |                      | 5TpC                                           |                      | 4     |                                        |

| 12 | Twdt             | Watch-Dog Timer<br>Delay Time        | 2.0–5.5<br>2.0–5.5<br>2.0–5.5<br>2.0–5.5 | 5<br>10<br>20<br>80  |                                                | ms<br>ms<br>ms<br>ms |       | 0, 0<br>0, 1<br>1, 0<br>1, 1           |

| 13 | T <sub>POR</sub> | Power-On Reset                       | 2.0–5.5                                  | 2.5                  | 10                                             | ms                   |       |                                        |

#### **Table 13. AC Characteristics**

Notes:

1. Timing Reference uses 0.9  $V_{CC}$  for a logic 1 and 0.1  $V_{CC}$  for a logic 0. 2. Interrupt request through Port 3 (P33–P31).

3. SMR – D5 = 1.

4. SMR - D5 = 0.

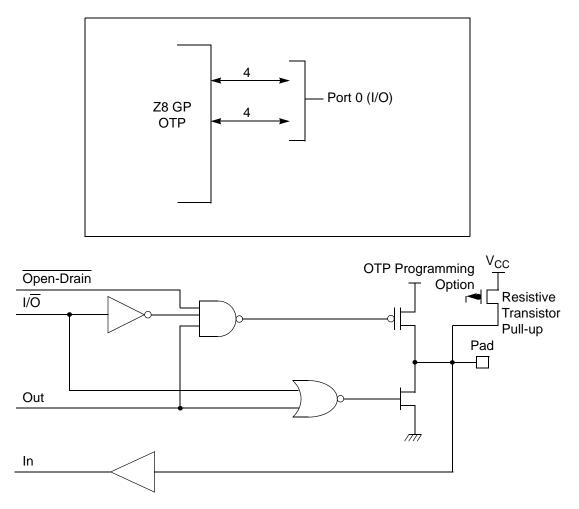

Figure 9. Port 0 Configuration

# Port 1 (P17–P10)

Port 1 (see Figure 10) Port 1 can be configured for standard port input or output mode. After POR, Port 1 is configured as an input port. The output drivers are either push-pull or open-drain and are controlled by bit D1 in the PCON register.

**Note:** The Port 1 direction is reset to its default state following an SMR.

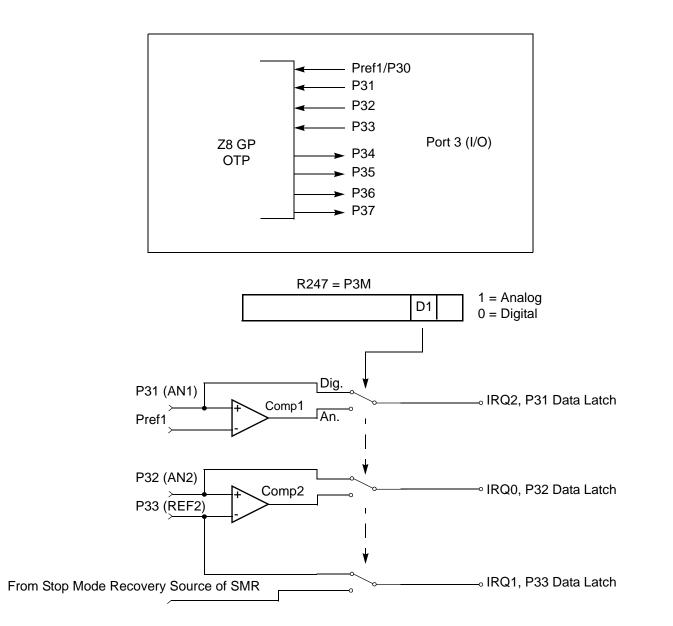

#### Figure 12. Port 3 Configuration

Two on-board comparators process analog signals on P31 and P32, with reference to the voltage on Pref1 and P33. The analog function is enabled by programming the Port 3 Mode Register (bit 1). P31 and P32 are programmable as rising, falling, or both edge triggered interrupts (IRQ register bits 6 and 7). Pref1 and P33 are the comparator reference voltage inputs. Access to the Counter Timer edgedetection circuit is through P31 or P20 (see "T8 and T16 Common Functions—

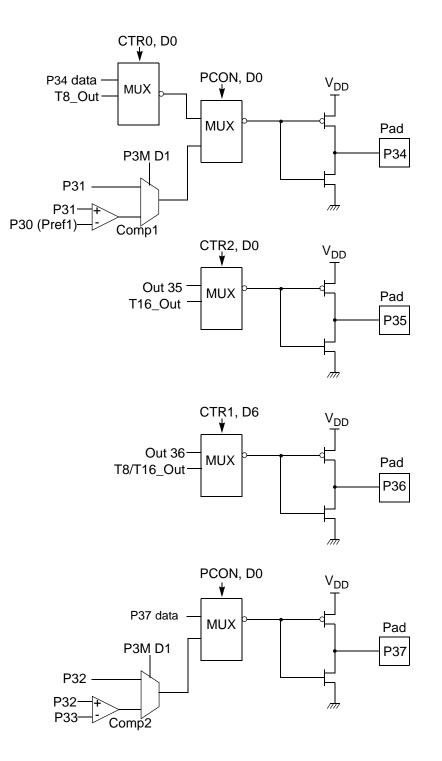

Figure 13. Port 3 Counter/Timer Output Configuration

# ZGP323H Product Specification

| Leastion of C                    | 0700      | Not Accessible      |

|----------------------------------|-----------|---------------------|

| Location of 3                    | 2768<br>1 | On-Chip             |

| instruction                      |           | ROM                 |

| executed<br>after RESET          |           |                     |

|                                  | 12        | Reset Start Address |

|                                  | 11        | IRQ5                |

|                                  | 10        | IRQ5                |

|                                  | 9         | IRQ4                |

|                                  | 8         | IRQ4                |

|                                  | 7         | IRQ3                |

| Interrupt Vector<br>(Lower Byte) | 6         | IRQ3                |

|                                  | 5         | IRQ2                |

| Interrupt Vector                 | 4<br>r    | ✓ IRQ2              |

| (Upper Byte                      |           | IRQ1                |

|                                  | 2         | IRQ1                |

|                                  | 1         | IRQ0                |

|                                  | 0         | IRQ0                |

# **Expanded Register File**

The register file has been expanded to allow for additional system control registers and for mapping of additional peripheral devices into the register address area. The Z8<sup>®</sup> register address space (R0 through R15) has been implemented as 16 banks, with 16 registers per bank. These register groups are known as the

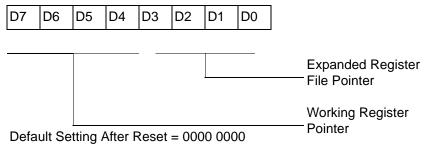

ERF (Expanded Register File). Bits 7–4 of register RP select the working register group. Bits 3–0 of register RP select the expanded register file bank.

**Note:** An expanded register bank is also referred to as an expanded register group (see Figure 15).

The upper nibble of the register pointer (see Figure 16) selects which working register group, of 16 bytes in the register file, is accessed out of the possible 256. The lower nibble selects the expanded register file bank and, in the case of the Z8 GP family, banks 0, F, and D are implemented. A OH in the lower nibble allows the normal register file (bank 0) to be addressed. Any other value from 1H to FH exchanges the lower 16 registers to an expanded register bank.

#### Figure 16. Register Pointer

#### Example: Z8 GP: (See Figure 15 on page 28)

R253 RP = 00h R0 = Port 0 R1 = Port 1 R2 = Port 2 R3 = Port 3

But if:

R253 RP = 0Dh R0 = CTR0 R1 = CTR1 R2 = CTR2R3 = Reserved

The counter/timers are mapped into ERF group D. Access is easily performed using the following:

| LD                                 | RP, #0Dh      | ; | Select ERF D |

|------------------------------------|---------------|---|--------------|

| for access to bank D               |               |   |              |

|                                    |               | ; | (working     |

| register group 0)                  |               |   |              |

| LD                                 | R0,#xx        | ; | load CTR0    |

| LD                                 | 1, #xx        | ; | load CTR1    |

| LD                                 | R1, 2         | ; | CTR2→CTR1    |

|                                    |               |   |              |

| LD                                 | RP, #0Dh      | ; | Select ERF D |

| for access to bank D               |               |   |              |

|                                    |               | ; | (working     |

| register group 0)                  |               |   |              |

| LD                                 | RP, #7Dh      | ; | Select       |

| expanded register bank             | D and working | ; | register     |

| group 7 of bank 0 for a            | ccess.        |   |              |

| LD                                 | 71h, 2        |   |              |

| ; CTRL2 $\rightarrow$ register 71h |               |   |              |

| LD                                 | R1, 2         |   |              |

| ; CTRL2 $\rightarrow$ register 71h |               |   |              |

# **Register File**

>

The register file (bank 0) consists of 4 I/O port registers, 237 general-purpose registers, 16 control and status registers (R0–R3, R4–R239, and R240–R255, respectively), and two expanded registers groups in Banks D (see Table 15) and F. Instructions can access registers directly or indirectly through an 8-bit address field, thereby allowing a short, 4-bit register address to use the Register Pointer (Figure 17). In the 4-bit mode, the register file is divided into 16 working register groups, each occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working register group.

# Timers

# T8\_Capture\_HI—HI8(D)0BH

This register holds the captured data from the output of the 8-bit Counter/Timer0. Typically, this register holds the number of counts when the input signal is 1.

| Field         | Bit Position |     | Description               |

|---------------|--------------|-----|---------------------------|

| T8_Capture_HI | [7:0]        | R/W | Captured Data - No Effect |

## T8\_Capture\_LO—L08(D)0AH

This register holds the captured data from the output of the 8-bit Counter/Timer0. Typically, this register holds the number of counts when the input signal is 0.

| Field         | Bit Position |     | Description               |  |

|---------------|--------------|-----|---------------------------|--|

| T8_Capture_L0 | [7:0]        | R/W | Captured Data - No Effect |  |

#### T16\_Capture\_HI—HI16(D)09H

This register holds the captured data from the output of the 16-bit Counter/ Timer16. This register holds the MS-Byte of the data.

| Field          | Bit Position |     | Description               |  |

|----------------|--------------|-----|---------------------------|--|

| T16_Capture_HI | [7:0]        | R/W | Captured Data - No Effect |  |

#### T16\_Capture\_LO—L016(D)08H

This register holds the captured data from the output of the 16-bit Counter/ Timer16. This register holds the LS-Byte of the data.

| Field          | Bit Position | Description                   |

|----------------|--------------|-------------------------------|

| T16_Capture_LO | [7:0]        | R/W Captured Data - No Effect |

#### Counter/Timer2 MS-Byte Hold Register—TC16H(D)07H

| Field       | Bit Position |     | Description |

|-------------|--------------|-----|-------------|

| T16_Data_HI | [7:0]        | R/W | Data        |

# T8/T16\_Logic/Edge \_Detect

In TRANSMIT Mode, this field defines how the outputs of T8 and T16 are combined (AND, OR, NOR, NAND).

In DEMODULATION Mode, this field defines which edge should be detected by the edge detector.

#### Transmit\_Submode/Glitch Filter

In Transmit Mode, this field defines whether T8 and T16 are in the PING-PONG mode or in independent normal operation mode. Setting this field to "NORMAL OPERATION Mode" terminates the "PING-PONG Mode" operation. When set to 10, T16 is immediately forced to a 0; a setting of 11 forces T16 to output a 1.

In DEMODULATION Mode, this field defines the width of the glitch that must be filtered out.

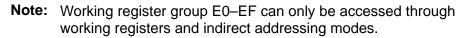

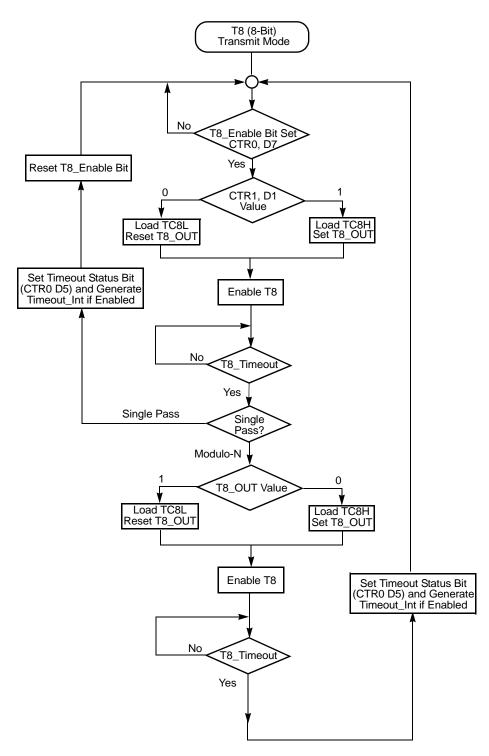

#### Initial\_T8\_Out/Rising\_Edge

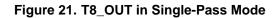

In TRANSMIT Mode, if 0, the output of T8 is set to 0 when it starts to count. If 1, the output of T8 is set to 1 when it starts to count. When the counter is not enabled and this bit is set to 1 or 0, T8\_OUT is set to the opposite state of this bit. This ensures that when the clock is enabled, a transition occurs to the initial state set by CTR1, D1.

In DEMODULATION Mode, this bit is set to 1 when a rising edge is detected in the input signal. In order to reset the mode, a 1 should be written to this location.

#### Initial\_T16 Out/Falling \_Edge

In TRANSMIT Mode, if it is 0, the output of T16 is set to 0 when it starts to count. If it is 1, the output of T16 is set to 1 when it starts to count. This bit is effective only in Normal or PING-PONG Mode (CTR1, D3; D2). When the counter is not enabled and this bit is set, T16\_OUT is set to the opposite state of this bit. This ensures that when the clock is enabled, a transition occurs to the initial state set by CTR1, D0.

In DEMODULATION Mode, this bit is set to 1 when a falling edge is detected in the input signal. In order to reset it, a 1 should be written to this location.

**Note:** Modifying CTR1 (D1 or D0) while the counters are enabled causes unpredictable output from T8/16\_OUT.

# CTR2 Counter/Timer 16 Control Register—CTR2(D)02H

Table 17 lists and briefly describes the fields for this register.

Figure 19. Transmit Mode Flowchart

Note: The letter h denotes hexadecimal values.

Transition from 0 to FFh is not a timeout condition.

**Caution:** Using the same instructions for stopping the counter/timers and setting the status bits is not recommended.

Two successive commands are necessary. First, the counter/timers must be stopped. Second, the status bits must be reset. These commands are required because it takes one counter/timer clock interval for the initiated event to actually occur. See Figure 21 and Figure 22.

Figure 22. T8\_OUT in Modulo-N Mode

# **T8 Demodulation Mode**

The user must program TC8L and TC8H to FFH. After T8 is enabled, when the first edge (rising, falling, or both depending on CTR1, D5; D4) is detected, it starts to count down. When a subsequent edge (rising, falling, or both depending on CTR1, D5; D4) is detected during counting, the current value of T8 is complemented and put into one of the capture registers. If it is a positive edge, data is put

# **During PING-PONG Mode**

The enable bits of T8 and T16 (CTR0, D7; CTR2, D7) are set and cleared alternately by hardware. The timeout bits (CTR0, D5; CTR2, D5) are set every time the counter/timers reach the terminal count.

## Interrupts

The ZGP323H features six different interrupts (Table 19). The interrupts are maskable and prioritized (Figure 30). The six sources are divided as follows: three sources are claimed by Port 3 lines P33–P31, two by the counter/timers (Table 19) and one for low voltage detection. The Interrupt Mask Register (globally or individually) enables or disables the six interrupt requests.

The source for IRQ is determined by bit 1 of the Port 3 mode register (P3M). When in digital mode, Pin P33 is the source. When in analog mode the output of the Stop mode recovery source logic is used as the source for the interrupt. See Figure 35, Stop Mode Recovery Source, on page 59.

| FF | NOP  | ; clear the pipeline |

|----|------|----------------------|

| 6F | Stop | ; enter Stop Mode    |

| or |      |                      |

| FF | NOP  | ; clear the pipeline |

| 7F | HALT | ; enter HALT Mode    |

# **Port Configuration Register**

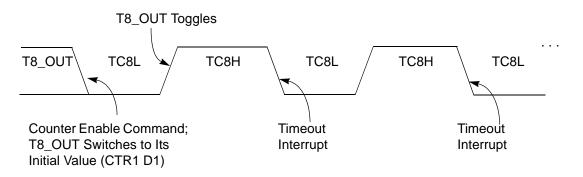

The Port Configuration (PCON) register (Figure 32) configures the comparator output on Port 3. It is located in the expanded register 2 at Bank F, location 00.

## PCON(FH)00H

\* Default setting after reset

#### Figure 32. Port Configuration Register (PCON) (Write Only)

#### Comparator Output Port 3 (D0)

Bit 0 controls the comparator used in Port 3. A 1 in this location brings the comparator outputs to P34 and P37, and a 0 releases the Port to its standard I/O configuration.

#### Port 1 Output Mode (D1)

Bit 1 controls the output mode of port 1. A 1 in this location sets the output to push-pull, and a 0 sets the output to open-drain.

#### ZGP323H Product Specification

#### Table 22. Stop Mode Recovery Source

| SMR:432 |    |    | Operation                          |  |

|---------|----|----|------------------------------------|--|

| D4      | D3 | D2 | Description of Action              |  |

| 0       | 0  | 0  | POR and/or external reset recovery |  |

| 0       | 0  | 1  | Reserved                           |  |

| 0       | 1  | 0  | P31 transition                     |  |

| 0       | 1  | 1  | P32 transition                     |  |

| 1       | 0  | 0  | P33 transition                     |  |

| 1       | 0  | 1  | P27 transition                     |  |

| 1       | 1  | 0  | Logical NOR of P20 through P23     |  |

| 1       | 1  | 1  | Logical NOR of P20 through P27     |  |

**Note:** Any Port 2 bit defined as an output drives the corresponding input to the default state. This condition allows the remaining inputs to control the AND/OR function. Refer to SMR2 register on page 61 for other recover sources.

#### Stop Mode Recovery Delay Select (D5)

This bit, if Low, disables the  $T_{POR}$  delay after Stop Mode Recovery. The default configuration of this bit is 1. If the "fast" wake up is selected, the Stop Mode Recovery source must be kept active for at least 5 TpC.

**Note:** This bit must be set to 1 if using a crystal or resonator clock source. The T<sub>POR</sub> delay allows the clock source to stabilize before executing instructions.

#### Stop Mode Recovery Edge Select (D6)

A 1 in this bit position indicates that a High level on any one of the recovery sources wakes the device from Stop Mode. A 0 indicates Low level recovery. The default is 0 on POR.

#### Cold or Warm Start (D7)

This bit is read only. It is set to 1 when the device is recovered from Stop Mode. The bit is set to 0 when the device reset is other than Stop Mode Recovery (SMR).

**Notes:** Take care in differentiating the Transmit Mode from Demodulation Mode. Depending on which of these two modes is operating, the CTR1 bit has different functions.

Changing from one mode to another cannot be performed without disabling the counter/timers.

# R254 SPH(FEH)

## Figure 56. Stack Pointer High (FEH: Read/Write)

# R255 SPL(FFH)

Stack Pointer Low Byte (SP7–SP0)

Figure 57. Stack Pointer Low (FFH: Read/Write)

# **Package Information**

Package information for all versions of ZGP323H is depicted in Figures 59 through Figure 68.