Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Obsolete                                                      |

| Core Processor             | Z8                                                            |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | -                                                             |

| Peripherals                | HLVD, POR, WDT                                                |

| Number of I/O              | 24                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                  |

| Program Memory Type        | ОТР                                                           |

| EEPROM Size                | -                                                             |

| RAM Size                   | 237 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                     |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | -                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/zgp323hss2804c00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

iii

## **Revision History**

Each instance in Table 1 reflects a change to this document from its previous revision. To see more detail, click the appropriate link in the table.

**Table 1. Revision History of this Document**

| Date             | Revision<br>Level | Section                                                                                                                                                                                                                                                                          | Description                                                              | Page<br># |

|------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------|

| December<br>2004 | 02                | Changed low power consumption, STOP and HALT mode current values deleted mask option note, clarified temperature ranges in Tables 6 and 8 and 10. Added new Tables 9 and 10. Also added Characterization data to Table 11 and changed Program/Erase Endurance value in Table 12. |                                                                          |           |

|                  |                   | Removed Preliminar                                                                                                                                                                                                                                                               | y designation                                                            | All       |

| March<br>2005    | 03                | Minor change to Tab<br>pin CDIP parts in the                                                                                                                                                                                                                                     | le 9 Electrical Characteristics. Added 20, 28 and 40-e Ordering Section. | 11,90     |

PS023803-0305 Revision History

## ZGP323H Product Specification

|   | • |

|---|---|

| v | ı |

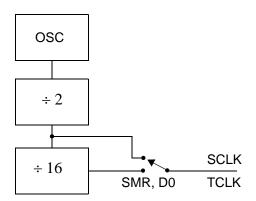

| Figure 34. SCLK Circuit                                                          | 58 |

|----------------------------------------------------------------------------------|----|

| Figure 35. Stop Mode Recovery Source                                             | 59 |

| Figure 36. Stop Mode Recovery Register 2 ((0F)DH:D2-D4, D6 Write Only) 6         | 31 |

| Figure 37. Watch-Dog Timer Mode Register (Write Only)6                           | 62 |

| Figure 38. Resets and WDT                                                        | 63 |

| Figure 39. TC8 Control Register ((0D)O0H: Read/Write Except Where Noted) 6       | 36 |

| Figure 40. T8 and T16 Common Control Functions ((0D)01H: Read/Write) 6           | 37 |

| Figure 41. T16 Control Register ((0D) 2H: Read/Write Except Where Noted) . 6     | 39 |

| Figure 42. T8/T16 Control Register (0D)03H: Read/Write (Except Where             |    |

| Noted)                                                                           |    |

| Figure 43. Voltage Detection Register                                            |    |

| Figure 44. Port Configuration Register (PCON)(0F)00H: Write Only) 7              | 72 |

| Figure 45. Stop Mode Recovery Register ((0F)0BH: D6–D0=Write Only, D7=Read Only) | 73 |

| Figure 46. Stop Mode Recovery Register 2 ((0F)0DH:D2–D4, D6 Write Only)          | 74 |

| Figure 47. Watch-Dog Timer Register ((0F) 0FH: Write Only)                       | 75 |

| Figure 48. Port 2 Mode Register (F6H: Write Only)                                | 75 |

| Figure 49. Port 3 Mode Register (F7H: Write Only)                                | 76 |

| Figure 50. Port 0 and 1 Mode Register (F8H: Write Only)                          | 77 |

| Figure 51. Interrupt Priority Register (F9H: Write Only)                         | 78 |

| Figure 52. Interrupt Request Register (FAH: Read/Write)                          | 79 |

| Figure 53. Interrupt Mask Register (FBH: Read/Write)                             | 79 |

| Figure 54. Flag Register (FCH: Read/Write)                                       | 30 |

| Figure 55. Register Pointer (FDH: Read/Write) 8                                  | 30 |

| Figure 56. Stack Pointer High (FEH: Read/Write) 8                                | 81 |

| Figure 57. Stack Pointer Low (FFH: Read/Write)                                   | 31 |

| Figure 58. 20-Pin CDIP Package 8                                                 | 82 |

| Figure 59. 20-Pin PDIP Package Diagram 8                                         | 32 |

| Figure 60. 20-Pin SOIC Package Diagram 8                                         | 33 |

| Figure 61. 20-Pin SSOP Package Diagram 8                                         | 34 |

| Figure 62. 28-Pin SOIC Package Diagram 8                                         | 35 |

| Figure 63. 28-Pin CDIP Package Diagram 8                                         | 36 |

| Figure 64. 28-Pin PDIP Package Diagram 8                                         | 36 |

| Figure 65. 28-Pin SSOP Package Diagram                                           | 37 |

| Figure 66. 40-Pin PDIP Package Diagram 8                                         | 37 |

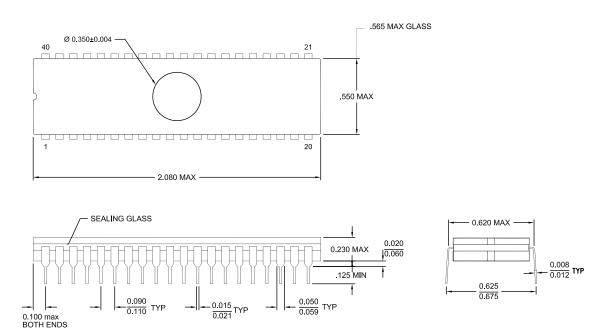

| Figure 67. 40-Pin CDIP Package Diagram                                           | 88 |

PS023803-0305 List of Figures

Table 10. GP323HE DC Characteristics (Continued)

|                     |                                             |          | T <sub>A</sub> = -40°0 | C to +105 | °C                       |       |                                                            |         |

|---------------------|---------------------------------------------|----------|------------------------|-----------|--------------------------|-------|------------------------------------------------------------|---------|

| Symbol              | Parameter                                   | $v_{cc}$ | Min                    | Typ(7)    | Max                      | Units | Conditions                                                 | Notes   |

| V <sub>OH2</sub>    | Output High Voltage<br>(P36, P37, P00, P01) | 2.0-5.5  | V <sub>CC</sub> -0.8   |           |                          | V     | $I_{OH} = -7mA$                                            |         |

| V <sub>OL1</sub>    | Output Low Voltage                          | 2.0-5.5  |                        |           | 0.4                      | V     | $I_{OL} = 4.0 \text{mA}$                                   |         |

| V <sub>OL2</sub>    | Output Low Voltage<br>(P00, P01, P36, P37)  | 2.0-5.5  |                        |           | 8.0                      | V     | I <sub>OL</sub> = 10mA                                     |         |

| V <sub>OFFSET</sub> | Comparator Input<br>Offset Voltage          | 2.0-5.5  |                        |           | 25                       | mV    |                                                            |         |

| V <sub>REF</sub>    | Comparator<br>Reference<br>Voltage          | 2.0-5.5  | 0                      |           | V <sub>DD</sub><br>-1.75 | V     |                                                            |         |

| I <sub>IL</sub>     | Input Leakage                               | 2.0-5.5  | -1                     |           | 1                        | μА    | V <sub>IN</sub> = 0V, V <sub>CC</sub><br>Pull-ups disabled |         |

| R <sub>PU</sub>     | Pull-up Resistance                          | 2.0V     | 200.0                  |           | 700.0                    | ΚΩ    | V <sub>IN</sub> = 0V; Pullups selected by mask             | (       |

|                     |                                             | 3.6V     | 50.0                   |           | 300.0                    | ΚΩ    | option                                                     |         |

|                     |                                             | 5.0V     | 25.0                   |           | 175.0                    | ΚΩ    | _                                                          | -       |

| I <sub>OL</sub>     | Output Leakage                              | 2.0-5.5  | -1                     |           | 1                        | μΑ    | $V_{IN} = 0V, V_{CC}$                                      |         |

| I <sub>CC</sub>     | Supply Current                              | 2.0V     |                        | 1         | 3                        | mA    | at 8.0 MHz                                                 | 1, 2    |

|                     |                                             | 3.6V     |                        | 5         | 10                       | mΑ    | at 8.0 MHz                                                 | 1, 2    |

|                     |                                             | 5.5V     |                        | 10        | 15                       | mA    | at 8.0 MHz                                                 | 1, 2    |

| I <sub>CC1</sub>    | Standby Current                             | 2.0V     |                        | 0.5       | 1.6                      | mΑ    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                      | 1, 2, 6 |

|                     | (HALT Mode)                                 | 3.6V     |                        | 8.0       | 2.0                      | mΑ    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                      | 1, 2, 6 |

|                     |                                             | 5.5V     |                        | 1.3       | 3.2                      | mA    | V <sub>IN</sub> = 0V, Clock at 8.0MHz                      | 1, 2, 6 |

| $I_{CC2}$           | Standby Current (Stop                       |          |                        | 1.6       | 12                       | μΑ    | $V_{IN} = 0 \text{ V}, V_{CC} \text{ WDT not Running}$     | 3       |

|                     | Mode)                                       | 3.6V     |                        | 1.8       | 15                       | μΑ    | $V_{IN} = 0 \text{ V}, V_{CC} \text{ WDT not Running}$     | 3       |

|                     |                                             | 5.5V     |                        | 1.9       | 18                       | μΑ    | $V_{IN} = 0 \text{ V}, V_{CC} \text{ WDT not Running}$     | 3       |

|                     |                                             | 2.0V     |                        | 5         | 30                       | μA    | $V_{IN} = 0 \text{ V}, V_{CC} \text{ WDT is Running}$      | 3       |

|                     |                                             | 3.6V     |                        | 8         | 40                       | μΑ    | $V_{IN} = 0 \text{ V}, V_{CC} \text{ WDT is Running}$      | 3       |

|                     |                                             | 5.5V     |                        | 15        | 60                       | μΑ    | $V_{IN} = 0 \text{ V}, V_{CC} \text{ WDT is Running}$      | 3       |

| I <sub>LV</sub>     | Standby Current (Low Voltage)               |          |                        | 1.2       | 6                        | μА    | Measured at 1.3V                                           | 4       |

| $V_{BO}$            | V <sub>CC</sub> Low Voltage<br>Protection   |          |                        | 1.9       | 2.15                     | V     | 8MHz maximum<br>Ext. CLK Freq.                             |         |

| V <sub>LVD</sub>    | V <sub>CC</sub> Low Voltage<br>Detection    |          |                        | 2.4       |                          | V     |                                                            |         |

| V <sub>HVD</sub>    | Vcc High Voltage<br>Detection               |          |                        | 2.7       |                          | V     |                                                            |         |

#### Notes:

- 1. All outputs unloaded, inputs at rail.

- 2. CL1 = CL2 = 100 pF.

- 3. Oscillator stopped.

- 4. Oscillator stops when  $\rm V_{CC}$  falls below  $\rm V_{BO}$  limit.

- 5. It is strongly recommended to add a filter capacitor (minimum 0.1  $\mu$ F), physically close to VCC and V<sub>SS</sub> pins if operating voltage fluctuations are anticipated, such as those resulting from driving an Infrared LED.

- 6. Comparator and Timers are on. Interrupt disabled.

- 7. Typical values shown are at 25 degrees C.

PS023803-0305 DC Characteristics

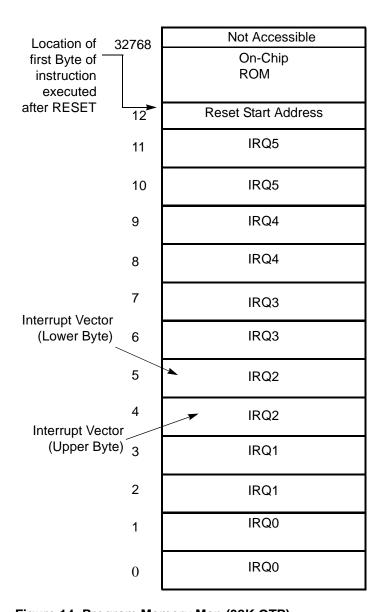

Figure 14. Program Memory Map (32K OTP)

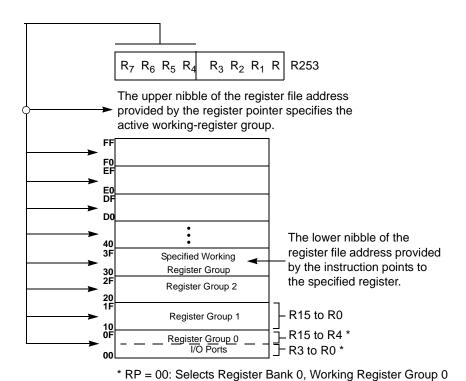

## **Expanded Register File**

The register file has been expanded to allow for additional system control registers and for mapping of additional peripheral devices into the register address area. The Z8<sup>®</sup> register address space (R0 through R15) has been implemented as 16 banks, with 16 registers per bank. These register groups are known as the

ERF (Expanded Register File). Bits 7–4 of register RP select the working register group. Bits 3–0 of register RP select the expanded register file bank.

**Note:** An expanded register bank is also referred to as an expanded register group (see Figure 15).

31

Figure 17. Register Pointer—Detail

## **Stack**

The internal register file is used for the stack. An 8-bit Stack Pointer SPL (R255) is used for the internal stack that resides in the general-purpose registers (R4–R239). SPH (R254) can be used as a general-purpose register.

#### **Timers**

#### T8\_Capture\_HI—HI8(D)0BH

This register holds the captured data from the output of the 8-bit Counter/Timer0. Typically, this register holds the number of counts when the input signal is 1.

| Field         | Bit Position |     | Description               |

|---------------|--------------|-----|---------------------------|

| T8_Capture_HI | [7:0]        | R/W | Captured Data - No Effect |

#### T8\_Capture\_LO—L08(D)0AH

This register holds the captured data from the output of the 8-bit Counter/Timer0. Typically, this register holds the number of counts when the input signal is 0.

| Field         | Bit Position |     | Description               |

|---------------|--------------|-----|---------------------------|

| T8_Capture_L0 | [7:0]        | R/W | Captured Data - No Effect |

#### T16\_Capture\_HI—HI16(D)09H

This register holds the captured data from the output of the 16-bit Counter/ Timer16. This register holds the MS-Byte of the data.

| Field          | Bit Position |     | Description               |

|----------------|--------------|-----|---------------------------|

| T16_Capture_HI | [7:0]        | R/W | Captured Data - No Effect |

#### T16\_Capture\_LO—L016(D)08H

This register holds the captured data from the output of the 16-bit Counter/ Timer16. This register holds the LS-Byte of the data.

| Field          | <b>Bit Position</b> | Description                   |

|----------------|---------------------|-------------------------------|

| T16_Capture_LO | [7:0]               | R/W Captured Data - No Effect |

#### Counter/Timer2 MS-Byte Hold Register—TC16H(D)07H

| Field       | Bit Position |     | Description |

|-------------|--------------|-----|-------------|

| T16_Data_HI | [7:0]        | R/W | Data        |

Table 18. CTR3 (D)03H: T8/T16 Control Register (Continued)

| Field    | Bit Position | Bit Position |   | Description        |

|----------|--------------|--------------|---|--------------------|

| Reserved | 43210        | R            | 1 | Always reads 11111 |

|          |              | W            | X | No Effect          |

<sup>\*</sup>Indicates the value upon Power-On Reset.

#### Counter/Timer Functional Blocks

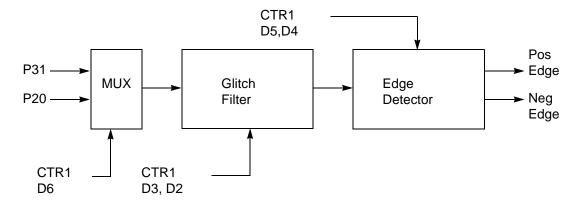

### **Input Circuit**

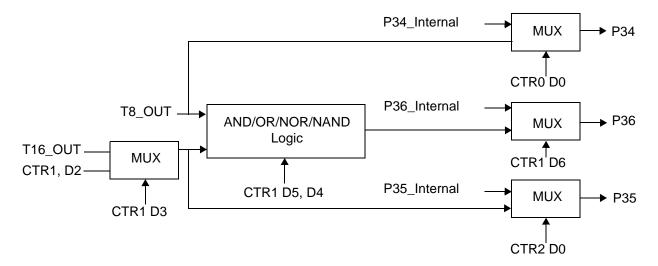

The edge detector monitors the input signal on P31 or P20. Based on CTR1 D5–D4, a pulse is generated at the Pos Edge or Neg Edge line when an edge is detected. Glitches in the input signal that have a width less than specified (CTR1 D3, D2) are filtered out (see Figure 18).

Figure 18. Glitch Filter Circuitry

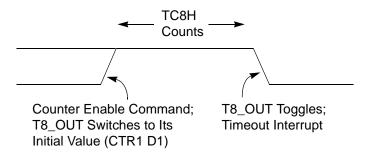

#### **T8 Transmit Mode**

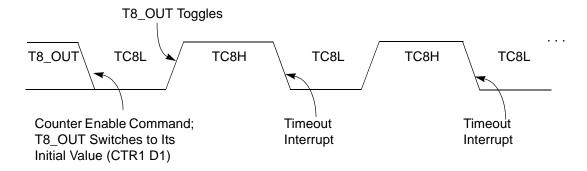

Before T8 is enabled, the output of T8 depends on CTR1, D1. If it is 0, T8\_OUT is 1; if it is 1, T8\_OUT is 0. See Figure 19.

<sup>\*\*</sup>Indicates the value upon Power-On Reset. Not reset with a Stop Mode recovery.

**Note:** The letter h denotes hexadecimal values.

Transition from 0 to FFh is not a timeout condition.

$\bigwedge$

**Caution:** Using the same instructions for stopping the counter/timers and setting the status bits is not recommended.

Two successive commands are necessary. First, the counter/timers must be stopped. Second, the status bits must be reset. These commands are required because it takes one counter/timer clock interval for the initiated event to actually occur. See Figure 21 and Figure 22.

Figure 21. T8\_OUT in Single-Pass Mode

Figure 22. T8\_OUT in Modulo-N Mode

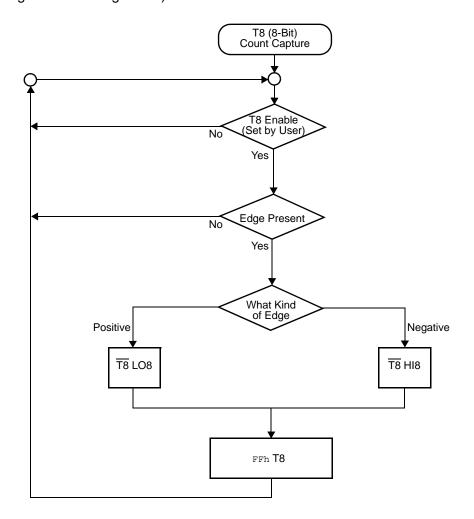

#### **T8 Demodulation Mode**

The user must program TC8L and TC8H to FFH. After T8 is enabled, when the first edge (rising, falling, or both depending on CTR1, D5; D4) is detected, it starts to count down. When a subsequent edge (rising, falling, or both depending on CTR1, D5; D4) is detected during counting, the current value of T8 is complemented and put into one of the capture registers. If it is a positive edge, data is put

into LO8; if it is a negative edge, data is put into HI8. From that point, one of the edge detect status bits (CTR1, D1; D0) is set, and an interrupt can be generated if enabled (CTR0, D2). Meanwhile, T8 is loaded with FFh and starts counting again. If T8 reaches 0, the timeout status bit (CTR0, D5) is set, and an interrupt can be generated if enabled (CTR0, D1). T8 then continues counting from FFH (see Figure 23 and Figure 24).

Figure 23. Demodulation Mode Count Capture Flowchart

48

#### If D6 of CTR2 Is 1

T16 ignores the subsequent edges in the input signal and continues counting down. A timeout of T8 causes T16 to capture its current value and generate an interrupt if enabled (CTR2, D2). In this case, T16 does not reload and continues counting. If the D6 bit of CTR2 is toggled (by writing a 0 then a 1 to it), T16 captures and reloads on the next edge (rising, falling, or both depending on CTR1, D5; D4), continuing to ignore subsequent edges.

This T16 mode generally measures mark time, the length of an active carrier signal burst.

If T16 reaches 0, T16 continues counting from FFFFh. Meanwhile, a status bit (CTR2 D5) is set, and an interrupt timeout can be generated if enabled (CTR2 D1).

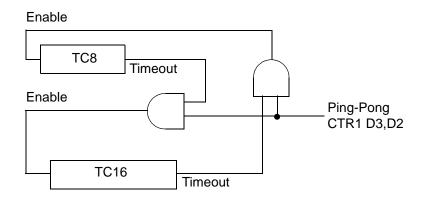

#### **Ping-Pong Mode**

This operation mode is only valid in TRANSMIT Mode. T8 and T16 must be programmed in Single-Pass mode (CTR0, D6; CTR2, D6), and Ping-Pong mode must be programmed in CTR1, D3; D2. The user can begin the operation by enabling either T8 or T16 (CTR0, D7 or CTR2, D7). For example, if T8 is enabled, T8\_OUT is set to this initial value (CTR1, D1). According to T8\_OUT's level, TC8H or TC8L is loaded into T8. After the terminal count is reached, T8 is disabled, and T16 is enabled. T16\_OUT then switches to its initial value (CTR1, D0), data from TC16H and TC16L is loaded, and T16 starts to count. After T16 reaches the terminal count, it stops, T8 is enabled again, repeating the entire cycle. Interrupts can be allowed when T8 or T16 reaches terminal control (CTR0, D1; CTR2, D1). To stop the ping-pong operation, write 00 to bits D3 and D2 of CTR1. See Figure 28.

**Note:** Enabling ping-pong operation while the counter/timers are running might cause intermittent counter/timer function. Disable the counter/timers and reset the status flags before instituting this operation.

Figure 28. Ping-Pong Mode Diagram

#### **Initiating PING-PONG Mode**

First, make sure both counter/timers are not running. Set T8 into Single-Pass mode (CTR0, D6), set T16 into SINGLE-PASS mode (CTR2, D6), and set the Ping-Pong mode (CTR1, D2; D3). These instructions can be in random order. Finally, start PING-PONG mode by enabling either T8 (CTR0, D7) or T16 (CTR2, D7). See Figure 29.

Figure 29. Output Circuit

The initial value of T8 or T16 must not be 1. Stopping the timer and restarting the timer reloads the initial value to avoid an unknown previous value.

50

#### **During PING-PONG Mode**

The enable bits of T8 and T16 (CTR0, D7; CTR2, D7) are set and cleared alternately by hardware. The timeout bits (CTR0, D5; CTR2, D5) are set every time the counter/timers reach the terminal count.

#### Interrupts

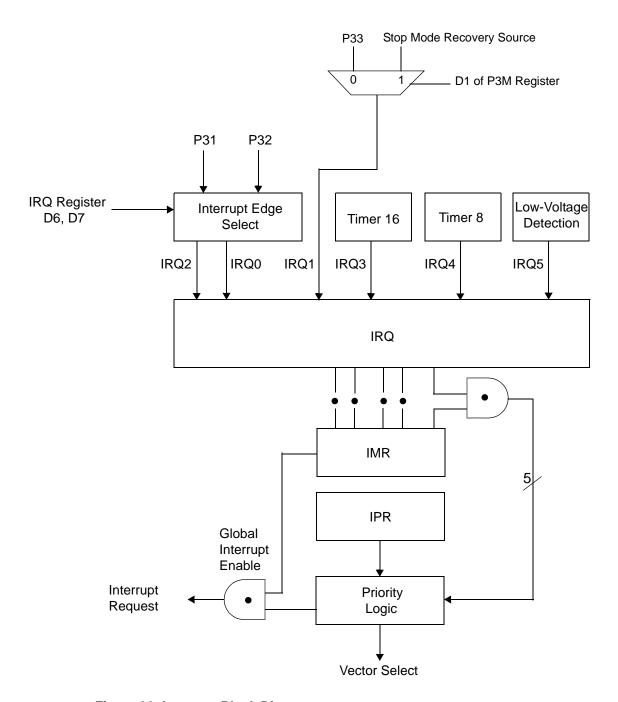

The ZGP323H features six different interrupts (Table 19). The interrupts are maskable and prioritized (Figure 30). The six sources are divided as follows: three sources are claimed by Port 3 lines P33–P31, two by the counter/timers (Table 19) and one for low voltage detection. The Interrupt Mask Register (globally or individually) enables or disables the six interrupt requests.

The source for IRQ is determined by bit 1 of the Port 3 mode register (P3M). When in digital mode, Pin P33 is the source. When in analog mode the output of the Stop mode recovery source logic is used as the source for the interrupt. See Figure 35, Stop Mode Recovery Source, on page 59.

Figure 30. Interrupt Block Diagram

Figure 34. SCLK Circuit

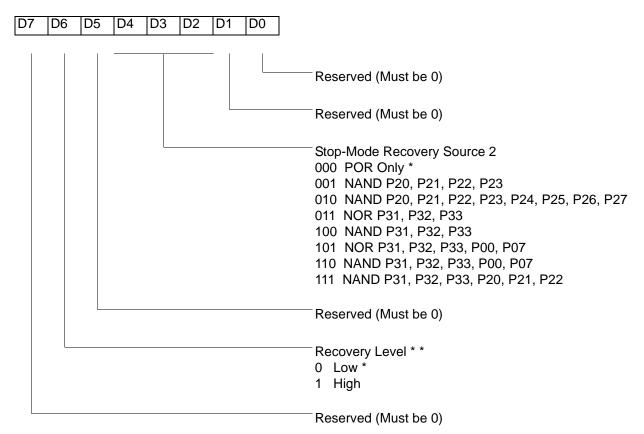

#### Stop-Mode Recovery Source (D2, D3, and D4)

These three bits of the SMR specify the wake-up source of the Stop recovery (Figure 35 and Table 22).

## Stop-Mode Recovery Register 2—SMR2(F)0DH

Table 21 lists and briefly describes the fields for this register.

Table 21.SMR2(F)0DH:Stop Mode Recovery Register 2\*

| Field          | Bit Position |   | Value            | Description                  |

|----------------|--------------|---|------------------|------------------------------|

| Reserved       | 7            |   | 0                | Reserved (Must be 0)         |

| Recovery Level | -6           | W | 0 <sup>†</sup>   | Low                          |

|                |              |   | 1                | High                         |

| Reserved       | 5            |   | 0                | Reserved (Must be 0)         |

| Source         | 432          | W | 000 <sup>†</sup> | A. POR Only                  |

|                |              |   | 001              | B. NAND of P23-P20           |

|                |              |   | 010              | C. NAND of P27-P20           |

|                |              |   | 011              | D. NOR of P33-P31            |

|                |              |   | 100              | E. NAND of P33-P31           |

|                |              |   | 101              | F. NOR of P33-P31, P00, P07  |

|                |              |   | 110              | G. NAND of P33-P31, P00, P07 |

|                |              |   | 111              | H. NAND of P33-P31, P22-P20  |

| Reserved       | 10           |   | 00               | Reserved (Must be 0)         |

#### Notes:

<sup>\*</sup> Port pins configured as outputs are ignored as a SMR recovery source. † Indicates the value upon Power-On Reset

### **Stop Mode Recovery Register 2 (SMR2)**

This register determines the mode of Stop Mode Recovery for SMR2 (Figure 36). SMR2(0F)DH

Note: If used in conjunction with SMR, either of the two specified events causes a Stop-Mode Recovery.

- \* Default setting after reset

- \* \* At the XOR gate input

Figure 36. Stop Mode Recovery Register 2 ((0F)DH:D2-D4, D6 Write Only)

If SMR2 is used in conjunction with SMR, either of the specified events causes a Stop Mode Recovery.

Note: Port pins configured as outputs are ignored as an SMR or SMR2 recovery source. For example, if the NAND or P23–P20 is selected as the recovery source and P20 is configured as an output, the remaining SMR pins (P23–P21) form the NAND equation.

Figure 67. 40-Pin CDIP Package Diagram

PS023803-0305 Package Information

# **Ordering Information**

| 32KB Standard Temperature: 0° to +70°C |                     |                |                     |

|----------------------------------------|---------------------|----------------|---------------------|

| Part Number                            | Description         | Part Number    | Description         |

| ZGP323HSH4832C                         | 48-pin SSOP 32K OTP | ZGP323HSS2832C | 28-pin SOIC 32K OTP |

| ZGP323HSP4032C                         | 40-pin PDIP 32K OTP | ZGP323HSH2032C | 20-pin SSOP 32K OTP |

| ZGP323HSK2832E                         | 28-pin CDIP 32K OTP | ZGP323HSK2032E | 20-pin CDIP 32K OTP |

| ZGP323HSK4032E                         | 40-pin CDIP 32K OTP | ZGP323HSP2032C | 20-pin PDIP 32K OTP |

| ZGP323HSH2832C                         | 28-pin SSOP 32K OTP | ZGP323HSS2032C | 20-pin SOIC 32K OTP |

| ZGP323HSP2832C                         | 28-pin PDIP 32K OTP |                |                     |

| 32KB Extended Temperature: -40° to +105°C |                     |                |                     |

|-------------------------------------------|---------------------|----------------|---------------------|

| Part Number                               | Description         | Part Number    | Description         |

| ZGP323HEH4832C                            | 48-pin SSOP 32K OTP | ZGP323HES2832C | 28-pin SOIC 32K OTP |

| ZGP323HEP4032C                            | 40-pin PDIP 32K OTP | ZGP323HEH2032C | 20-pin SSOP 32K OTP |

| ZGP323HEH2832C                            | 28-pin SSOP 32K OTP | ZGP323HEP2032C | 20-pin PDIP 32K OTP |

| ZGP323HEP2832C                            | 28-pin PDIP 32K OTP | ZGP323HES2032C | 20-pin SOIC 32K OTP |

| 32KB Automotive Temperature: -40° to +125°C |                       |                |                     |

|---------------------------------------------|-----------------------|----------------|---------------------|

| Part Number                                 | Description           | Part Number    | Description         |

| ZGP323HAH4832C                              | 48-pin SSOP 32K OTP   | ZGP323HAS2832C | 28-pin SOIC 32K OTP |

| ZGP323HAP4032C                              | 40-pin PDIP 32K OTP   | ZGP323HAH2032C | 20-pin SSOP 32K OTP |

| ZGP323HAH2832C                              | 28-pin SSOP 32K OTP   | ZGP323HAP2032C | 20-pin PDIP 32K OTP |

| ZGP323HAP2832C                              | 28-pin PDIP 32K OTP   | ZGP323HAS2032C | 20-pin SOIC 32K OTP |

| Replace C with G fo                         | r Lead-Free Packaging |                |                     |

|                                             |                       |                |                     |

PS023803-0305 Ordering Information

93

| 4ND Standard Telli                                 | perature: 0° to +70°C                    | T                                                  |                                          |

|----------------------------------------------------|------------------------------------------|----------------------------------------------------|------------------------------------------|

| Part Number                                        | Description                              | Part Number                                        | Description                              |

| ZGP323HSH4804C                                     | 48-pin SSOP 4K OTP                       | ZGP323HSS2804C                                     | 28-pin SOIC 4K OTP                       |

| ZGP323HSP4004C                                     | 40-pin PDIP 4K OTP                       | ZGP323HSH2004C                                     | 20-pin SSOP 4K OTP                       |

| ZGP323HSH2804C                                     | 28-pin SSOP 4K OTP                       | ZGP323HSP2004C                                     | 20-pin PDIP 4K OTP                       |

| ZGP323HSP2804C                                     | 28-pin PDIP 4K OTP                       | ZGP323HSS2004C                                     | 20-pin SOIC 4K OTP                       |

|                                                    |                                          |                                                    |                                          |

| 4KB Extended Tem                                   | perature: -40° to +105°0                 |                                                    |                                          |

| Dord Number                                        | Deceriation                              | David Manuali au                                   |                                          |

| Part Number                                        | Description                              | Part Number                                        | Description                              |

| ZGP323HEH4804C                                     |                                          |                                                    | Description 28-pin SOIC 4K OTP           |

| ZGP323HEH4804C                                     |                                          | ZGP323HES2804C                                     |                                          |

| ZGP323HEH4804C<br>ZGP323HEP4004C                   | 48-pin SSOP 4K OTP                       | ZGP323HES2804C<br>ZGP323HEH2004C                   | 28-pin SOIC 4K OTP                       |

| ZGP323HEH4804C<br>ZGP323HEP4004C<br>ZGP323HEH2804C | 48-pin SSOP 4K OTP<br>40-pin PDIP 4K OTP | ZGP323HES2804C<br>ZGP323HEH2004C<br>ZGP323HEP2004C | 28-pin SOIC 4K OTP<br>20-pin SSOP 4K OTP |

| 4KB Automotive Temperature: -40° to +125°C |                     |                |                    |

|--------------------------------------------|---------------------|----------------|--------------------|

| Part Number                                | Description         | Part Number    | Description        |

| ZGP323HAH4804C                             | 48-pin SSOP 4K OTP  | ZGP323HAS2804C | 28-pin SOIC 4K OTP |

| ZGP323HAP4004C                             | 40-pin PDIP 4K OTP  | ZGP323HAH2004C | 20-pin SSOP 4K OTP |

| ZGP323HAH2804C                             | 28-pin SSOP 4K OTP  | ZGP323HAP2004C | 20-pin PDIP 4K OTP |

| ZGP323HAP2804C                             | 28-pin PDIP 4K OTP  | ZGP323HAS2004C | 20-pin SOIC 4K OTP |

| Replace C with G for                       | Lead-Free Packaging |                |                    |

| Additional Components                          |                     |                              |                    |

|------------------------------------------------|---------------------|------------------------------|--------------------|

| Part Number                                    | Description         | Part Number                  | Description        |

| ZGP323ICE01ZEM<br>(For 3.6V Emulation<br>only) | Emulator/programmer | ZGP32300100ZPR<br>(Ethernet) | Programming system |

|                                                |                     | ZGP32300200ZPR<br>(USB)      | Programming system |

PS023803-0305 Ordering Information

| T8_Capture_LO 32                              |

|-----------------------------------------------|

| register file 30                              |

| expanded 26                                   |

| register pointer 29                           |

| detail 31                                     |

| reset pin function 25                         |

| resets and WDT 63                             |

| S                                             |

| SCLK circuit 58                               |

| single-pass mode                              |

| T16_OUT 47                                    |

| T8_OUT 43                                     |

| stack 31                                      |

| standard test conditions 10                   |

| standby modes 1                               |

| stop instruction, counter/timer 54            |

| stop mode recovery                            |

| 2 register 61                                 |

| source 59                                     |

| stop mode recovery 2 61                       |

| stop mode recovery register 57                |

| T                                             |

| T16 transmit mode 46                          |

| T16_Capture_HI 32                             |

| T8 transmit mode 40                           |

| T8_Capture_HI 32                              |

| test conditions, standard 10                  |

| test load diagram 10                          |

| timing diagram, AC 16                         |

| transmit mode flowchart 41                    |

| V                                             |

| VCC 5                                         |

| voltage                                       |

| brown-out/standby 64                          |

| detection and flags 65                        |

| voltage detection register 71<br>W            |

| watch-dog timer                               |

| mode registerwatch-dog timer mode register 62 |

| time select 63                                |

X XTAL1 5 XTAL1 pin function 18 XTAL2 5 XTAL2 pin function 18