Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 36MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                               |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | ·                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f101rct6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8 | Revis | sion his | tory                                                             | 16 |

|---|-------|----------|------------------------------------------------------------------|----|

| 7 | Part  | number   | ing1                                                             | 15 |

|   |       | 6.4.2    | Evaluating the maximum junction temperature for an application 1 | 14 |

|   |       | 6.4.1    | Reference document 1                                             | 13 |

|   | 6.4   | Therma   | l characteristics1                                               | 13 |

|   | 6.3   | LQFP6    | 4 information                                                    | 10 |

| Timer                           | Counter resolution | Counter<br>type         | Prescaler<br>factor                   | DMA request generation | Capture/compare<br>channels | Complementary<br>outputs |

|---------------------------------|--------------------|-------------------------|---------------------------------------|------------------------|-----------------------------|--------------------------|

| TIM2,<br>TIM3,<br>TIM4,<br>TIM5 | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | No                       |

| TIM6,<br>TIM7                   | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 0                           | No                       |

Table 4. Timer feature comparison

### General-purpose timers (TIMx)

There are up to 4 synchronizable general-purpose timers (TIM2, TIM3, TIM4 and TIM5) embedded in the STM32F101xC, STM32F101xD and STM32F101xE access line devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures / output compares / PWMs on the largest packages.

The general-purpose timers can work together with the advanced-control timer via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 2.3.22 ADC (analog to digital converter)

A 12-bit analog-to-digital converter is embedded into STM32F101xC, STM32F101xD and STM32F101xE access line devices. It has up to 16 external channels, performing conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start trigger and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

### 2.3.23 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Seven DAC trigger inputs are used in the STM32F101xC, STM32F101xD and STM32F101xE access line family. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

### 2.3.24 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V <  $V_{DDA}$  < 3.6 V. The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

### 2.3.25 Serial wire JTAG debug port (SWJ-DP)

The ARM<sup>®</sup> SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

DocID14610 Rev 9

## 2.3.26 Embedded Trace Macrocell™

The ARM<sup>®</sup> Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F10xxx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

|         | Pins   | abie    | 5. 5110521 101AC/STN | 521                 | 1012                       |                                                  | Alternate functions <sup>(4)</sup>                                                    |                    |  |  |

|---------|--------|---------|----------------------|---------------------|----------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------|--------------------|--|--|

|         | F1115  |         |                      |                     |                            |                                                  | Alternate functi                                                                      |                    |  |  |

| LQFP144 | LQFP64 | LQFP100 | Pin name             | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                               | Remap              |  |  |

| 12      | -      | -       | PF2                  | I/O                 | FT                         | PF2                                              | FSMC_A2                                                                               | -                  |  |  |

| 13      | -      | -       | PF3                  | I/O                 | FT                         | PF3                                              | FSMC_A3                                                                               | -                  |  |  |

| 14      | -      | -       | PF4                  | I/O                 | FT                         | PF4                                              | FSMC_A4                                                                               | -                  |  |  |

| 15      | -      | -       | PF5                  | I/O                 | FT                         | PF5                                              | FSMC_A5                                                                               | -                  |  |  |

| 16      | -      | 10      | V <sub>SS_5</sub>    | S                   | -                          | V <sub>SS_5</sub>                                | -                                                                                     | -                  |  |  |

| 17      | -      | 11      | V <sub>DD_5</sub>    | S                   | -                          | V <sub>DD_5</sub>                                | -                                                                                     | -                  |  |  |

| 18      | -      | -       | PF6                  | I/O                 | -                          | PF6                                              | FSMC_NIORD                                                                            | -                  |  |  |

| 19      | -      | -       | PF7                  | I/O                 | -                          | PF7                                              | FSMC_NREG                                                                             | -                  |  |  |

| 20      | -      | -       | PF8                  | I/O                 | -                          | PF8                                              | FSMC_NIOWR                                                                            | -                  |  |  |

| 21      | -      | -       | PF9                  | I/O                 | -                          | PF9                                              | FSMC_CD                                                                               | -                  |  |  |

| 22      | -      | -       | PF10                 | I/O                 | -                          | PF10                                             | FSMC_INTR                                                                             | -                  |  |  |

| 23      | 5      | 12      | OSC_IN               | Ι                   | -                          | OSC_IN                                           | -                                                                                     | PD0 <sup>(7)</sup> |  |  |

| 24      | 6      | 13      | OSC_OUT              | 0                   | -                          | OSC_OUT                                          | -                                                                                     | PD1 <sup>(7)</sup> |  |  |

| 25      | 7      | 14      | NRST                 | I/O                 | -                          | NRST                                             | -                                                                                     | -                  |  |  |

| 26      | 8      | 15      | PC0                  | I/O                 | -                          | PC0                                              | ADC_IN10                                                                              | -                  |  |  |

| 27      | 9      | 16      | PC1                  | I/O                 | -                          | PC1                                              | ADC_IN11                                                                              | -                  |  |  |

| 28      | 10     | 17      | PC2                  | I/O                 | -                          | PC2                                              | ADC_IN12                                                                              | -                  |  |  |

| 29      | 11     | 18      | PC3                  | I/O                 | -                          | PC3                                              | ADC_IN13                                                                              | -                  |  |  |

| 30      | 12     | 19      | V <sub>SSA</sub>     | S                   | -                          | V <sub>SSA</sub>                                 | -                                                                                     | -                  |  |  |

| 31      | -      | 20      | V <sub>REF-</sub>    | S                   | -                          | V <sub>REF-</sub>                                | -                                                                                     | -                  |  |  |

| 32      | -      | 21      | V <sub>REF+</sub>    | S                   | -                          | V <sub>REF+</sub>                                | -                                                                                     | -                  |  |  |

| 33      | 13     | 22      | V <sub>DDA</sub>     | S                   | -                          | V <sub>DDA</sub>                                 | -                                                                                     | -                  |  |  |

| 34      | 14     | 23      | PA0-WKUP             | I/O                 | -                          | PA0                                              | WKUP/ USART2_CTS <sup>(8)</sup> /<br>ADC_IN0/TIM5_CH1/<br>TIM2_CH1_ETR <sup>(8)</sup> | -                  |  |  |

| 35      | 15     | 24      | PA1                  | I/O                 | -                          | PA1                                              | USART2_RTS <sup>(8)</sup> /<br>ADC_IN1/TIM5_CH2<br>TIM2_CH2 <sup>(8)</sup>            | -                  |  |  |

| 36      | 16     | 25      | PA2                  | I/O                 | -                          | PA2                                              | USART2_TX <sup>(8)</sup> /<br>TIM5_CH3/ADC_IN2/<br>TIM2_CH3 <sup>(8)</sup>            | -                  |  |  |

# 4 Memory mapping

The memory map is shown in *Figure* 6.

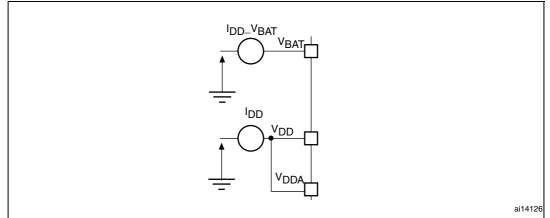

### 5.1.7 Current consumption measurement

### Figure 10. Current consumption measurement scheme

# 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 7: Voltage characteristics*, *Table 8: Current characteristics*, and *Table 9: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                         | Ratings                                                               | Min                                                                         | Max                   | Unit |

|--------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|------|

| $V_{DD} - V_{SS}$              | External main supply voltage (including $V_{DDA}$ and $V_{DD})^{(1)}$ | -0.3                                                                        | 4.0                   |      |

| V <sub>IN</sub> <sup>(2)</sup> | (2) Input voltage on five volt tolerant pin                           |                                                                             | V <sub>DD</sub> + 4.0 | V    |

| VIN Y                          | Input voltage on any other pin                                        | V <sub>SS</sub> – 0.3                                                       | 4.0                   |      |

| $ \Delta V_{DDx} $             | Variations between different V <sub>DD</sub> power pins               | -                                                                           | 50                    |      |

| $ V_{SSX} - V_{SS} $           | Variations between all the different ground pins                      | -                                                                           | 50                    | mV   |

| V <sub>ESD(HBM)</sub>          | Electrostatic discharge voltage (human body model)                    | see Section 5.3.12: Absolute<br>maximum ratings (electrical<br>sensitivity) |                       |      |

### Table 7. Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 8: Current characteristics* for the maximum allowed injected current values.

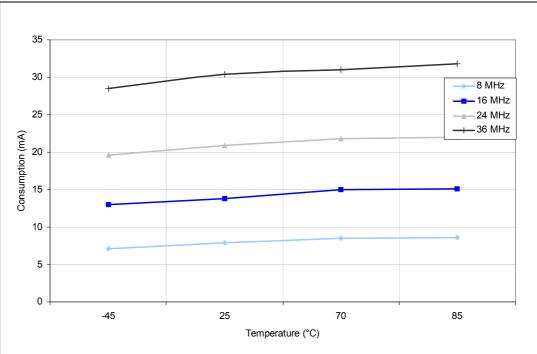

Figure 11. Typical current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals enabled

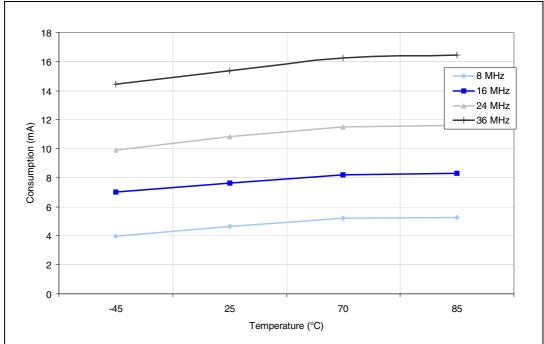

Figure 12. Typical current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals disabled

| Symbol | Parameter                       | Conditions                                               | £                 | Max <sup>(1)</sup>     | Unit |  |

|--------|---------------------------------|----------------------------------------------------------|-------------------|------------------------|------|--|

| Symbol | Parameter                       | Conditions                                               | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | Unit |  |

|        |                                 |                                                          | 36 MHz            | 24                     |      |  |

|        | Supply current in<br>Sleep mode | External clock <sup>(2)</sup> all peripherals enabled    | 24 MHz            | 17                     |      |  |

|        |                                 |                                                          | 16 MHz            | 12.5                   |      |  |

|        |                                 |                                                          | 8 MHz             | 8                      | m 4  |  |

| IDD    |                                 | External clock <sup>(2)</sup> , all peripherals disabled | 36 MHz            | 6                      | mA   |  |

|        |                                 |                                                          | 24 MHz            | 5                      |      |  |

|        |                                 |                                                          | 16 MHz            | 4.5                    |      |  |

|        |                                 |                                                          | 8 MHz             | 4                      |      |  |

Table 16. Maximum current consumption in Sleep mode, code running from Flash or RAM

1. Guaranteed by characterization results, tested in production at V<sub>DD</sub> max, f<sub>HCLK</sub> max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

|                      |                                 |                                                                                                                                                |                                                  | Тур <sup>(1)</sup>                               |                            | Max                       |      |

|----------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------------------|---------------------------|------|

| Symbol               | Parameter                       | Conditions                                                                                                                                     | V <sub>DD</sub> /<br>V <sub>BAT</sub> =<br>2.0 V | V <sub>DD</sub> /<br>V <sub>BAT</sub> =<br>2.4 V | $V_{DD}/V_{BA}$<br>= 3.3 V | T <sub>A</sub> =<br>85 °C | Unit |

|                      | Supply current<br>in Stop mode  | Regulator in Run mode,<br>Low-speed and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog)       | -                                                | 34.5                                             | 35                         | 379                       |      |

|                      |                                 | Regulator in Low-power mode,<br>Low-speed and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog) | -                                                | 24.5                                             | 25                         | 365                       |      |

| I <sub>DD</sub>      |                                 | Low-speed internal RC oscillator and independent watchdog ON                                                                                   | -                                                | 3                                                | 3.8                        | -                         | μA   |

|                      | Supply current<br>in Standby    | Low-speed internal RC oscillator ON, independent watchdog OFF                                                                                  | -                                                | 2.8                                              | 3.6                        | -                         |      |

|                      | mode                            | Low-speed internal RC oscillator and<br>independent watchdog OFF, low-speed<br>oscillator and RTC OFF                                          | -                                                | 1.9                                              | 2.1                        | 5 <sup>(2)</sup>          |      |

| I <sub>DD_VBAT</sub> | Backup domain<br>supply current | Low-speed oscillator and RTC ON                                                                                                                | 1.05                                             | 1.1                                              | 1.4                        | 2 <sup>(2)</sup>          |      |

Table 17. Typical and maximum current consumptions in Stop and Standby modes

1. Typical values are measured at T<sub>A</sub> = 25 °C.

2. Guaranteed by characterization results, not tested in production.

### Typical current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- All peripherals are disabled except if it is explicitly mentioned

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 36 MHz)

- Prefetch is on (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled f<sub>PCLK1</sub> = f<sub>HCLK/4</sub>, f<sub>PCLK2</sub> = f<sub>HCLK/2</sub>, f<sub>ADCCLK</sub> = f<sub>PCLK2</sub>/4

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}$ ,  $f_{PCLK2} = f_{HCLK}$ ,  $f_{ADCCLK} = f_{PCLK2}/2$

The parameters given in *Table 18* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| Symbol Paramoto |                                  |                                  |                   | Тур <sup>(1)</sup>                        | Тур <sup>(1)</sup>          |      |

|-----------------|----------------------------------|----------------------------------|-------------------|-------------------------------------------|-----------------------------|------|

| Symbol          | Parameter                        | Conditions                       | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled | Unit |

|                 |                                  |                                  | 36 MHz            | 26.6                                      | 16.2                        |      |

|                 |                                  |                                  | 24 MHz            | 18.5                                      | 11.4                        |      |

|                 |                                  |                                  | 16 MHz            | 12.8                                      | 8.2                         |      |

|                 |                                  |                                  | 8 MHz             | 7.2                                       | 5                           |      |

|                 |                                  | External<br>clock <sup>(3)</sup> | 4 MHz             | 4.2                                       | 3.1                         |      |

|                 | Supply<br>current in<br>Run mode |                                  | 2 MHz             | 2.7                                       | 2.1                         |      |

|                 |                                  |                                  | 1 MHz             | 2                                         | 1.7                         | mA   |

|                 |                                  |                                  | 500 kHz           | 1.6                                       | 1.4                         |      |

|                 |                                  |                                  | 125 kHz           | 1.3                                       | 1.2                         |      |

| I <sub>DD</sub> |                                  | Running on<br>high speed         | 36 MHz            | 26                                        | 15.6                        | ШA   |

|                 |                                  |                                  | 24 MHz            | 17.9                                      | 10.8                        |      |

|                 |                                  |                                  | 16 MHz            | 12.2                                      | 7.6                         |      |

|                 |                                  | internal RC                      | 8 MHz             | 6.6                                       | 4.4                         |      |

|                 |                                  | (HSI), AHB<br>prescaler          | 4 MHz             | 3.6                                       | 2.5                         |      |

|                 |                                  | used to                          | 2 MHz             | 2.1                                       | 1.5                         |      |

|                 |                                  | reduce the<br>frequency          | 1 MHz             | 1.4                                       | 1.1                         |      |

|                 |                                  |                                  | 500 kHz           | 1                                         | 0.8                         |      |

|                 |                                  |                                  | 125 kHz           | 0.7                                       | 0.6                         |      |

# Table 18. Typical current consumption in Run mode, code with data processingrunning from Flash

1. Typical values are measures at  $T_A = 25$  °C,  $V_{DD} = 3.3$  V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

DocID14610 Rev 9

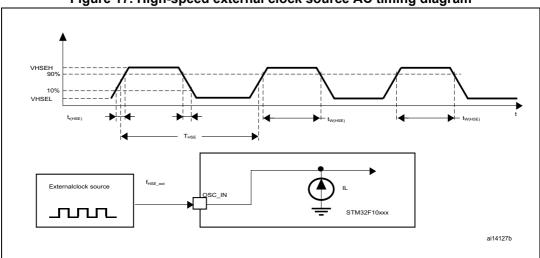

Figure 17. High-speed external clock source AC timing diagram

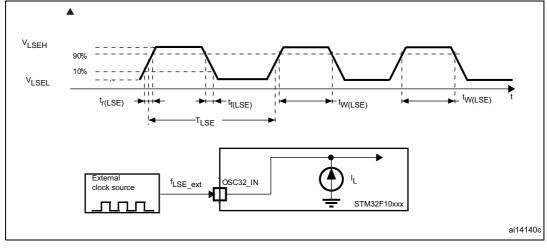

Figure 18. Low-speed external clock source AC timing diagram

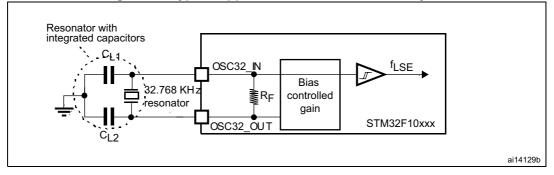

- Note: For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

- **Caution:** To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

**Example:** if you choose a resonator with a load capacitance of  $C_L = 6 \text{ pF}$ , and  $C_{stray} = 2 \text{ pF}$ , then  $C_{L1} = C_{L2} = 8 \text{ pF}$ .

### 5.3.7 Internal clock source characteristics

The parameters given in *Table 25* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                           | Co                                                   | Min                           | Тур  | Мах | Unit             |     |  |  |

|-------------------------------------|-------------------------------------|------------------------------------------------------|-------------------------------|------|-----|------------------|-----|--|--|

| f <sub>HSI</sub>                    | Frequency                           | -                                                    |                               | -    | 8   | -                | MHz |  |  |

| DuCy <sub>(HSI)</sub>               | Duty cycle                          | -                                                    |                               | 45   | -   | 55               | %   |  |  |

|                                     |                                     | User-trimmed with the RCC_CR register <sup>(2)</sup> |                               | -    | -   | 1 <sup>(3)</sup> | %   |  |  |

|                                     | Accuracy of the HSI oscillator      | Factory-<br>calibrated <sup>(4)</sup>                | $T_A = -40$ to 105 °C         | -2   | -   | 2.5              | %   |  |  |

| ACC <sub>HSI</sub>                  |                                     |                                                      | T <sub>A</sub> = −10 to 85 °C | -1.5 | -   | 2.2              | %   |  |  |

|                                     |                                     |                                                      | $T_A = 0$ to 70 °C            | -1.3 | -   | 2                | %   |  |  |

|                                     |                                     |                                                      | T <sub>A</sub> = 25 °C        | -1.1 | -   | 1.8              | %   |  |  |

| t <sub>su(HSI)</sub> <sup>(4)</sup> | HSI oscillator startup time         | -                                                    |                               | 1    | -   | 2                | μs  |  |  |

| I <sub>DD(HSI)</sub> <sup>(4)</sup> | HSI oscillator power<br>consumption | -                                                    | -                             | 80   | 100 | μA               |     |  |  |

Table 25. HSI oscillator characteristics<sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 85 °C unless otherwise specified.

57

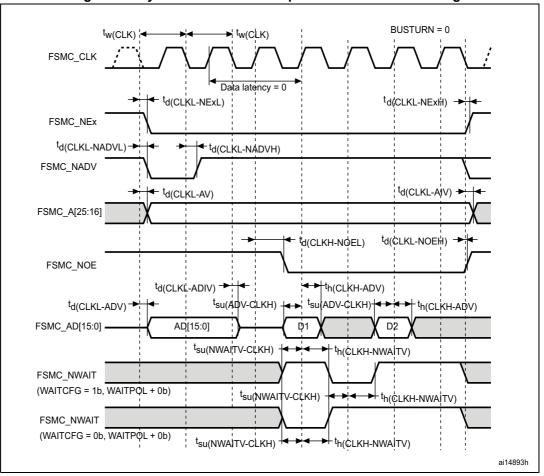

| Symbol                       | Parameter                                         | Min  | Max | Unit |

|------------------------------|---------------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                                   | 55.5 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)             | -    | 1.5 | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)            | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low                     | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high                    | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)          | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625)        | 2    | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>    | FSMC_CLK high to FSMC_NOE low                     | -    | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>    | FSMC_CLK low to FSMC_NOE high                     | 0.5  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>     | FSMC_CLK low to FSMC_AD[15:0] valid               | -    | 12  | ns   |

| t <sub>d(CLKL-ADIV)</sub>    | FSMC_CLK low to FSMC_AD[15:0] invalid             | 0    | -   | ns   |

| t <sub>su(ADV-CLKH)</sub>    | FSMC_A/D[15:0] valid data before FSMC_CLK<br>high | 6    | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>     | FSMC_A/D[15:0] valid data after FSMC_CLK high     | 0    | -   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high             | 8    | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high              | 2    | -   | ns   |

Table 35. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 15 pF.

2. Guaranteed by characterization results, not tested in production..

Figure 28. Synchronous non-multiplexed PSRAM write timings

## Table 38. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                       | Parameter                                  | Min  | Мах | Unit |

|------------------------------|--------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                            | 55.5 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)      | -    | 2   | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)     | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low              | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high             | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)   | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625) | 2    | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>    | FSMC_CLK low to FSMC_NWE low               | -    | 1   | ns   |

| t <sub>d(CLKL-NWEH)</sub>    | FSMC_CLK low to FSMC_NWE high              | 1    | -   | ns   |

| t <sub>d(CLKL-Data)</sub>    | FSMC_D[15:0] valid data after FSMC_CLK low | -    | 6   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high      | 7    | -   | ns   |

DocID14610 Rev 9

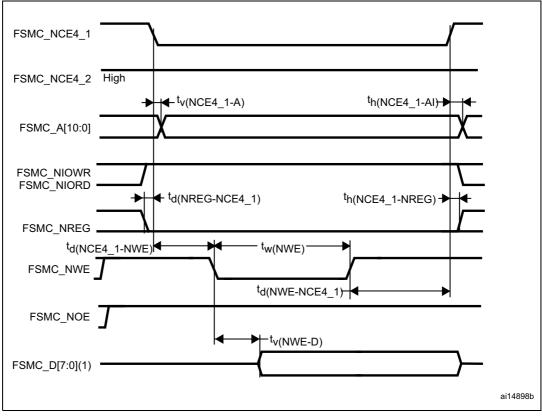

Figure 32. PC Card/CompactFlash controller waveforms for attribute memory write access

1. Only data bits 0...7 are driven (bits 8...15 remains HiZ).

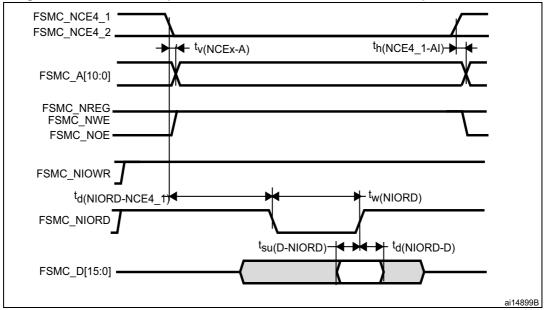

### Figure 33. PC Card/CompactFlash controller waveforms for I/O space read access

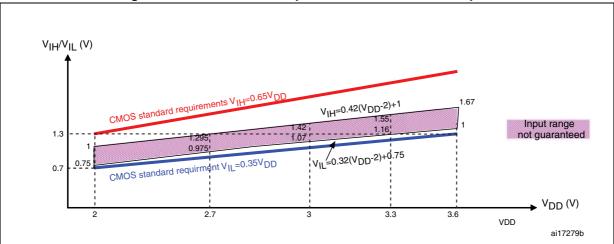

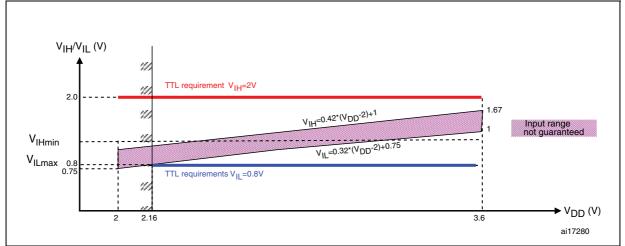

Figure 41. 5 V tolerant I/O input characteristics - CMOS port

Figure 42. 5 V tolerant I/O input characteristics - TTL port

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to ±8 mA, and sink or source up to ± 20 mA (with a relaxedV<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to ±3 mA. When using the GPIOs PC13 to PC15 in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 8*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 8*).

### 5.3.16 TIM timer characteristics

The parameters given in Table 50 are guaranteed by design.

Refer to Section 5.3.13: I/O current injection characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Table 00. Think & Characteristics |                                                                   |                               |        |                         |                      |  |

|-----------------------------------|-------------------------------------------------------------------|-------------------------------|--------|-------------------------|----------------------|--|

| Symbol                            | Parameter                                                         | Conditions                    | Min    | Мах                     | Unit                 |  |

| t <sub>res(TIM)</sub>             | Timer resolution time                                             | -                             | 1      | -                       | t <sub>TIMxCLK</sub> |  |

|                                   |                                                                   | f <sub>TIMxCLK</sub> = 36 MHz | 27.8   | -                       | ns                   |  |

| f <sub>EXT</sub>                  | Timer external clock<br>frequency on CH1 to CH4                   | -                             | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |

|                                   |                                                                   | f <sub>TIMxCLK</sub> = 36 MHz | 0      | 18                      | MHz                  |  |

| Res <sub>TIM</sub>                | Timer resolution                                                  | -                             | -      | 16                      | bit                  |  |

| t <sub>COUNTER</sub>              | 16-bit counter clock period<br>when internal clock is<br>selected | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |

|                                   |                                                                   | f <sub>TIMxCLK</sub> = 36 MHz | 0.0278 | 1820                    | μs                   |  |

| t <sub>MAX_COUNT</sub>            | Maximum possible count                                            | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |

|                                   |                                                                   | f <sub>TIMxCLK</sub> = 36 MHz | -      | 119.2                   | S                    |  |

Table 50. TIMx<sup>(1)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM1, TIM2, TIM3 and TIM4 timers.

## 5.3.17 Communications interfaces

### I<sup>2</sup>C interface characteristics

The STM32F101xC, STM32F101xD and STM32F101xE access line I<sup>2</sup>C interface meets the requirements of the standard I<sup>2</sup>C communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 51*. Refer also to *Section 5.3.13: I/O current injection characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

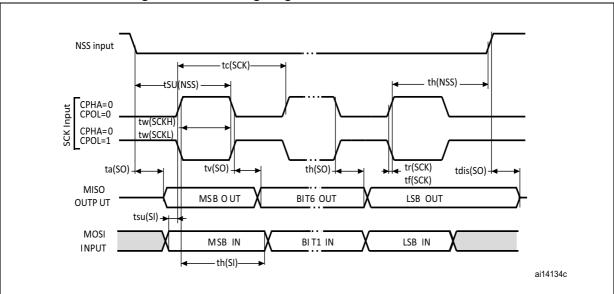

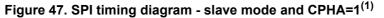

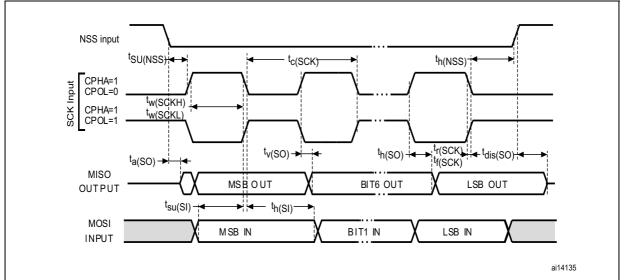

Figure 46. SPI timing diagram - slave mode and CPHA=0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

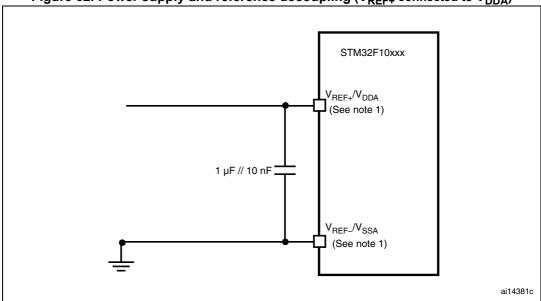

Figure 52. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are available only on 100-pin packages.

## 5.3.19 DAC electrical specifications

| Table | 59. | DAC  | characteristics |

|-------|-----|------|-----------------|

| Iabio |     | 57.0 | 01101000        |

| Symbol                           | Parameter                                 | Min | Тур | Max <sup>(1)</sup>          | Unit | Comments                                                                                                                                |  |  |  |

|----------------------------------|-------------------------------------------|-----|-----|-----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>DDA</sub>                 | Analog supply voltage                     | 2.4 | -   | 3.6                         | V    |                                                                                                                                         |  |  |  |

| V <sub>REF+</sub>                | Reference supply voltage                  | 2.4 | -   | 3.6                         | V    | V <sub>REF+</sub> must always be below V <sub>DDA</sub>                                                                                 |  |  |  |

| V <sub>SSA</sub>                 | Ground                                    | 0   | -   | 0                           | V    |                                                                                                                                         |  |  |  |

| R <sub>LOAD</sub> <sup>(2)</sup> | Resistive load with buffer ON             | 5   | -   | -                           | kΩ   |                                                                                                                                         |  |  |  |

| R <sub>0</sub> <sup>(2)</sup>    | Impedance output with buffer<br>OFF       | -   | -   | 15                          | kΩ   | When the buffer is OFF, the minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$                 |  |  |  |

| C <sub>LOAD</sub> <sup>(2)</sup> | Capacitive load                           | -   | -   | 50                          | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                         |  |  |  |

| DAC_OUT<br>min <sup>(2)</sup>    | Lower DAC_OUT voltage with<br>buffer ON   | 0.2 | -   | -                           | v    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input cod<br>(0x0E0) to (0xF1C) at V <sub>REF+</sub> = |  |  |  |

| DAC_OUT<br>max <sup>(2)</sup>    | Higher DAC_OUT voltage with<br>buffer ON  | -   | -   | V <sub>DDA</sub> –<br>0.2   | V    | 3.6 V and (0x155) and (0xEAB) at<br>V <sub>REF+</sub> = 2.4 V.                                                                          |  |  |  |

| DAC_OUT<br>min <sup>(2)</sup>    | Lower DAC_OUT voltage with<br>buffer OFF  | -   | 0.5 | -                           | mV   | It gives the maximum output excursion of the DAC.                                                                                       |  |  |  |

| DAC_OUT<br>max <sup>(2)</sup>    | Higher DAC_OUT voltage with<br>buffer OFF | -   |     | V <sub>REF+</sub> –<br>1LSB | V    |                                                                                                                                         |  |  |  |

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур    | Мах   | Min                   | Тур    | Мах    |  |

| E3     | -           | 12.000 | -     | -                     | 0.4724 | -      |  |

| е      | -           | 0.500  | -     | -                     | 0.0197 | -      |  |

| L      | 0.450       | 0.600  | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000  | -     | -                     | 0.0394 | -      |  |

| k      | 0°          | 3.5°   | 7°    | 0°                    | 3.5°   | 7°     |  |

| CCC    | -           | -      | 0.080 | -                     | -      | 0.0031 |  |

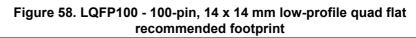

# Table 62. LQPF100 – 14 x 14 mm, 100-pin low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.