Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 36MHz                                                                   |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                      |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                               |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f101ret6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8 | Revis | sion his | tory                                                             | 16 |

|---|-------|----------|------------------------------------------------------------------|----|

| 7 | Part  | number   | ing1                                                             | 15 |

|   |       | 6.4.2    | Evaluating the maximum junction temperature for an application 1 | 14 |

|   |       | 6.4.1    | Reference document 1                                             | 13 |

|   | 6.4   | Therma   | l characteristics1                                               | 13 |

|   | 6.3   | LQFP6    | 4 information                                                    | 10 |

| Table 46. | I/O static characteristics                                                |

|-----------|---------------------------------------------------------------------------|

| Table 47. | Output voltage characteristics                                            |

| Table 48. | I/O AC characteristics                                                    |

| Table 49. | NRST pin characteristics                                                  |

| Table 50. | TIMx characteristics                                                      |

| Table 51. | I <sup>2</sup> C characteristics                                          |

| Table 52. | SCL frequency ( $f_{PCLK1}$ = 36 MHz, $V_{DD}$ = $V_{DD   12C}$ = 3.3 V)  |

| Table 53. | STM32F10xxx SPI characteristics                                           |

| Table 54. | SPI characteristics                                                       |

| Table 55. | ADC characteristics                                                       |

| Table 56. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz                        |

| Table 57. | ADC accuracy - limited test conditions                                    |

| Table 58. | ADC accuracy                                                              |

| Table 59. | DAC characteristics                                                       |

| Table 60. | TS characteristics                                                        |

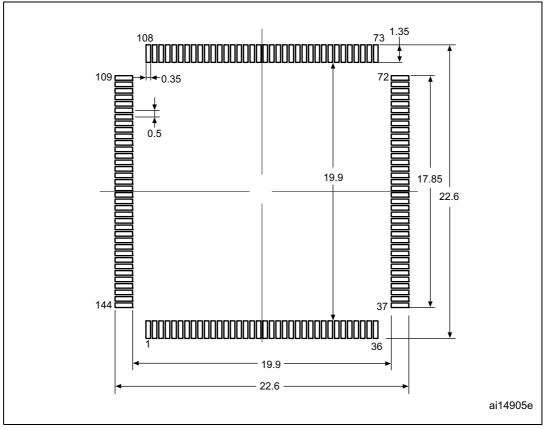

| Table 61. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package               |

|           | mechanical data                                                           |

| Table 62. | LQPF100 – 14 x 14 mm, 100-pin low-profile guad flat                       |

|           | package mechanical data                                                   |

| Table 63. | LQFP64 – 10 x 10 mm, 64 pin low-profile quad flat package mechanical data |

| Table 64. | Package thermal characteristics                                           |

| Table 65. | Ordering information scheme                                               |

# 2.3.11 Power supply schemes

- $V_{DD}$  = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the ADC or DAC is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 9: Power supply scheme*.

# 2.3.12 **Power supply supervisor**

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software. Refer to *Table 12: Embedded reset and power control block characteristics* for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

# 2.3.13 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop modes.

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode.

# 2.3.14 Low-power modes

The STM32F101xC, STM32F101xD and STM32F101xE access line supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

DocID14610 Rev 9

| Timer                           | Counter resolution | Counter<br>type         | Prescaler<br>factor                   | DMA request generation | Capture/compare<br>channels | Complementary<br>outputs |

|---------------------------------|--------------------|-------------------------|---------------------------------------|------------------------|-----------------------------|--------------------------|

| TIM2,<br>TIM3,<br>TIM4,<br>TIM5 | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | No                       |

| TIM6,<br>TIM7                   | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 0                           | No                       |

Table 4. Timer feature comparison

# General-purpose timers (TIMx)

There are up to 4 synchronizable general-purpose timers (TIM2, TIM3, TIM4 and TIM5) embedded in the STM32F101xC, STM32F101xD and STM32F101xE access line devices. These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler and feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures / output compares / PWMs on the largest packages.

The general-purpose timers can work together with the advanced-control timer via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs. They all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

# 2.3.26 Embedded Trace Macrocell™

The ARM<sup>®</sup> Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F10xxx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

| Table 5. STM32F101xC/STM32F101xD/STM32F101xE pin definitions (c<br>Pins Alternate fu |        |         |                   |                     |                            | Alternate functi                                 | -                                                                                     |                    |

|--------------------------------------------------------------------------------------|--------|---------|-------------------|---------------------|----------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------|--------------------|

|                                                                                      | F1115  |         |                   |                     |                            |                                                  | Alternate functi                                                                      |                    |

| LQFP144                                                                              | LQFP64 | LQFP100 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                               | Remap              |

| 12                                                                                   | -      | -       | PF2               | I/O                 | FT                         | PF2                                              | FSMC_A2                                                                               | -                  |

| 13                                                                                   | -      | -       | PF3               | I/O                 | FT                         | PF3                                              | FSMC_A3                                                                               | -                  |

| 14                                                                                   | -      | -       | PF4               | I/O                 | FT                         | PF4                                              | FSMC_A4                                                                               | -                  |

| 15                                                                                   | -      | -       | PF5               | I/O                 | FT                         | PF5                                              | FSMC_A5                                                                               | -                  |

| 16                                                                                   | -      | 10      | V <sub>SS_5</sub> | S                   | -                          | V <sub>SS_5</sub>                                | -                                                                                     | -                  |

| 17                                                                                   | -      | 11      | V <sub>DD_5</sub> | S                   | -                          | V <sub>DD_5</sub>                                | -                                                                                     | -                  |

| 18                                                                                   | -      | -       | PF6               | I/O                 | -                          | PF6                                              | FSMC_NIORD                                                                            | -                  |

| 19                                                                                   | -      | -       | PF7               | I/O                 | -                          | PF7                                              | FSMC_NREG                                                                             | -                  |

| 20                                                                                   | -      | -       | PF8               | I/O                 | -                          | PF8                                              | FSMC_NIOWR                                                                            | -                  |

| 21                                                                                   | -      | -       | PF9               | I/O                 | -                          | PF9                                              | FSMC_CD                                                                               | -                  |

| 22                                                                                   | -      | -       | PF10              | I/O                 | -                          | PF10                                             | FSMC_INTR                                                                             | -                  |

| 23                                                                                   | 5      | 12      | OSC_IN            | Ι                   | -                          | OSC_IN                                           | -                                                                                     | PD0 <sup>(7)</sup> |

| 24                                                                                   | 6      | 13      | OSC_OUT           | 0                   | -                          | OSC_OUT                                          | -                                                                                     | PD1 <sup>(7)</sup> |

| 25                                                                                   | 7      | 14      | NRST              | I/O                 | -                          | NRST                                             | -                                                                                     | -                  |

| 26                                                                                   | 8      | 15      | PC0               | I/O                 | -                          | PC0                                              | ADC_IN10                                                                              | -                  |

| 27                                                                                   | 9      | 16      | PC1               | I/O                 | -                          | PC1                                              | ADC_IN11                                                                              | -                  |

| 28                                                                                   | 10     | 17      | PC2               | I/O                 | -                          | PC2                                              | ADC_IN12                                                                              | -                  |

| 29                                                                                   | 11     | 18      | PC3               | I/O                 | -                          | PC3                                              | ADC_IN13                                                                              | -                  |

| 30                                                                                   | 12     | 19      | V <sub>SSA</sub>  | S                   | -                          | V <sub>SSA</sub>                                 | -                                                                                     | -                  |

| 31                                                                                   | -      | 20      | V <sub>REF-</sub> | S                   | -                          | V <sub>REF-</sub>                                | -                                                                                     | -                  |

| 32                                                                                   | -      | 21      | V <sub>REF+</sub> | S                   | -                          | V <sub>REF+</sub>                                | -                                                                                     | -                  |

| 33                                                                                   | 13     | 22      | V <sub>DDA</sub>  | S                   | -                          | V <sub>DDA</sub>                                 | -                                                                                     | -                  |

| 34                                                                                   | 14     | 23      | PA0-WKUP          | I/O                 | -                          | PA0                                              | WKUP/ USART2_CTS <sup>(8)</sup> /<br>ADC_IN0/TIM5_CH1/<br>TIM2_CH1_ETR <sup>(8)</sup> | -                  |

| 35                                                                                   | 15     | 24      | PA1               | I/O                 | -                          | PA1                                              | USART2_RTS <sup>(8)</sup> /<br>ADC_IN1/TIM5_CH2 -<br>TIM2_CH2 <sup>(8)</sup>          |                    |

| 36                                                                                   | 16     | 25      | PA2               | I/O                 | -                          | PA2                                              | USART2_TX <sup>(8)</sup> /<br>TIM5_CH3/ADC_IN2/<br>TIM2_CH3 <sup>(8)</sup>            | -                  |

| Symbol | Parameter                     |                                                          |        | Max <sup>(1)</sup>     | Unit |

|--------|-------------------------------|----------------------------------------------------------|--------|------------------------|------|

|        | Parameter                     | Conditions                                               | fhclk  | T <sub>A</sub> = 85 °C | Unit |

|        |                               |                                                          | 36 MHz | 39                     |      |

|        | Supply current<br>in Run mode | External clock <sup>(2)</sup> , all peripherals enabled  | 24 MHz | 27                     | - mA |

|        |                               |                                                          | 16 MHz | 20                     |      |

|        |                               |                                                          | 8 MHz  | 11                     |      |

| IDD    |                               | External clock <sup>(2)</sup> , all peripherals disabled | 36 MHz | 22                     |      |

|        |                               |                                                          | 24 MHz | 16.5                   |      |

|        |                               |                                                          | 16 MHz | 12.5                   |      |

|        |                               |                                                          | 8 MHz  | 8                      |      |

# Table 14. Maximum current consumption in Run mode, code with data processingrunning from Flash

1. Guaranteed by characterization results, not tested in production.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

| Table 15. Maximum current consumption in Run mode, code with data processing           running from RAM |  |  |  |                    |  |  |

|---------------------------------------------------------------------------------------------------------|--|--|--|--------------------|--|--|

|                                                                                                         |  |  |  | Max <sup>(1)</sup> |  |  |

| Symbol | <b>D</b>                      | Conditions                                              | £      | Max <sup>(1)</sup>     | Unit |  |

|--------|-------------------------------|---------------------------------------------------------|--------|------------------------|------|--|

| Symbol | Parameter                     | Conditions                                              | fhclk  | T <sub>A</sub> = 85 °C | Unit |  |

|        |                               |                                                         | 36 MHz | 34                     |      |  |

|        | Supply current in<br>Run mode | External clock <sup>(2)</sup> , all peripherals enabled | 24 MHz | 24                     | mA   |  |

|        |                               |                                                         | 16 MHz | 17                     |      |  |

|        |                               |                                                         | 8 MHz  | 10                     |      |  |

| IDD    |                               | External clock <sup>(2)</sup> all peripherals disabled  | 36 MHz | 18                     |      |  |

|        |                               |                                                         | 24 MHz | 13                     |      |  |

|        |                               |                                                         | 16 MHz | 10                     |      |  |

|        |                               |                                                         | 8 MHz  | 6                      |      |  |

1. Guaranteed by characterization results, tested in production at  $V_{\text{DD}}$  max,  $f_{\text{HCLK}}$  max.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

## Typical current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- All peripherals are disabled except if it is explicitly mentioned

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 36 MHz)

- Prefetch is on (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled f<sub>PCLK1</sub> = f<sub>HCLK/4</sub>, f<sub>PCLK2</sub> = f<sub>HCLK/2</sub>, f<sub>ADCCLK</sub> = f<sub>PCLK2</sub>/4

- When the peripherals are enabled  $f_{PCLK1} = f_{HCLK}$ ,  $f_{PCLK2} = f_{HCLK}$ ,  $f_{ADCCLK} = f_{PCLK2}/2$

The parameters given in *Table 18* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

|                 |                                  |                                  |                   | Тур <sup>(1)</sup>                        | Тур <sup>(1)</sup>          |      |

|-----------------|----------------------------------|----------------------------------|-------------------|-------------------------------------------|-----------------------------|------|

| Symbol          | Parameter                        | Conditions                       | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled | Unit |

|                 |                                  |                                  | 36 MHz            | 26.6                                      | 16.2                        |      |

|                 |                                  |                                  | 24 MHz            | 18.5                                      | 11.4                        |      |

|                 |                                  |                                  | 16 MHz            | 12.8                                      | 8.2                         |      |

|                 |                                  |                                  | 8 MHz             | 7.2                                       | 5                           |      |

|                 | Supply<br>current in<br>Run mode | External<br>clock <sup>(3)</sup> | 4 MHz             | 4.2                                       | 3.1                         |      |

|                 |                                  |                                  | 2 MHz             | 2.7                                       | 2.1                         | mA   |

|                 |                                  |                                  | 1 MHz             | 2                                         | 1.7                         |      |

|                 |                                  |                                  | 500 kHz           | 1.6                                       | 1.4                         |      |

|                 |                                  |                                  | 125 kHz           | 1.3                                       | 1.2                         |      |

| I <sub>DD</sub> |                                  | Running on<br>high speed         | 36 MHz            | 26                                        | 15.6                        | ШA   |

|                 |                                  |                                  | 24 MHz            | 17.9                                      | 10.8                        |      |

|                 |                                  |                                  | 16 MHz            | 12.2                                      | 7.6                         |      |

|                 |                                  | internal RC                      | 8 MHz             | 6.6                                       | 4.4                         |      |

|                 |                                  | (HSI), AHB<br>prescaler          | 4 MHz             | 3.6                                       | 2.5                         |      |

|                 |                                  | used to                          | 2 MHz             | 2.1                                       | 1.5                         |      |

|                 |                                  | reduce the<br>frequency          | 1 MHz             | 1.4                                       | 1.1                         |      |

|                 |                                  |                                  | 500 kHz           | 1                                         | 0.8                         |      |

|                 |                                  |                                  | 125 kHz           | 0.7                                       | 0.6                         |      |

# Table 18. Typical current consumption in Run mode, code with data processingrunning from Flash

1. Typical values are measures at  $T_A = 25$  °C,  $V_{DD} = 3.3$  V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

DocID14610 Rev 9

|                 |                                    |                                 |                   | Тур <sup>(1)</sup>                        | Тур <sup>(1)</sup>          | Unit |

|-----------------|------------------------------------|---------------------------------|-------------------|-------------------------------------------|-----------------------------|------|

| Symbol          | Parameter                          | Conditions                      | <sup>f</sup> нс∟к | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled |      |

|                 |                                    |                                 | 36 MHz            | 15.1                                      | 3.6                         |      |

|                 |                                    |                                 | 24 MHz            | 10.4                                      | 2.6                         |      |

|                 |                                    |                                 | 16 MHz            | 7.2                                       | 2                           |      |

|                 |                                    |                                 | 8 MHz             | 3.9                                       | 1.3                         |      |

|                 |                                    | External clock <sup>(3)</sup>   | 4 MHz             | 2.6                                       | 1.2                         |      |

|                 | Supply<br>current in<br>Sleep mode |                                 | 2 MHz             | 1.85                                      | 1.15                        |      |

|                 |                                    |                                 | 1 MHz             | 1.5                                       | 1.1                         |      |

|                 |                                    |                                 | 500 kHz           | 1.3                                       | 1.05                        |      |

| 1               |                                    |                                 | 125 kHz           | 1.2                                       | 1.05                        | mA   |

| I <sub>DD</sub> |                                    | Running on High                 | 36 MHz            | 14.5                                      | 3                           |      |

|                 |                                    |                                 | 24 MHz            | 9.8                                       | 2                           |      |

|                 |                                    |                                 | 16 MHz            | 6.6                                       | 1.4                         |      |

|                 |                                    | Speed Internal                  | 8 MHz             | 3.3                                       | 0.7                         |      |

|                 |                                    | RC (HSI), AHB prescaler used to | 4 MHz             | 2                                         | 0.6                         |      |

|                 |                                    | reduce the                      | 2 MHz             | 1.25                                      | 0.55                        |      |

|                 |                                    | frequency                       | 1 MHz             | 0.9                                       | 0.5                         |      |

|                 |                                    |                                 | 500 kHz           | 0.7                                       | 0.45                        |      |

|                 |                                    |                                 | 125 kHz           | 0.6                                       | 0.45                        |      |

Table 19. Typical current consumption in Sleep mode, code running from Flash or RAM

1. Typical values are measures at  $T_A = 25 \text{ °C}$ ,  $V_{DD} = 3.3 \text{ V}$ .

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

# On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 20*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 7.

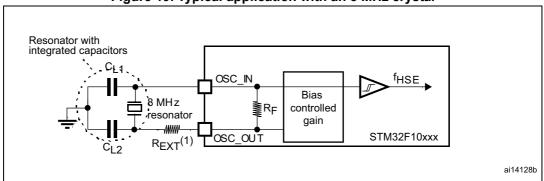

Figure 19. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 24*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter Conditions                                                                                    |                                         | Min                     | Тур | Max | Unit |      |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------|-----|-----|------|------|

| R <sub>F</sub>                      | Feedback resistor                                                                                       | -                                       | -                       | -   | 5   | -    | MΩ   |

| С                                   | Recommended load capacitance<br>versus equivalent serial<br>resistance of the crystal (R <sub>S</sub> ) | R <sub>S</sub> = 30 KΩ                  | -                       | -   | -   | 15   | pF   |

| I <sub>2</sub>                      | LSE driving current                                                                                     | $V_{DD}$ = 3.3 V<br>$V_{IN}$ = $V_{SS}$ | -                       | -   | -   | 1.4  | μA   |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                             | -                                       | -                       | 5   | -   | -    | µA/V |

|                                     |                                                                                                         | V <sub>DD</sub> is<br>stabilized        | T <sub>A</sub> = 50 °C  | -   | 1.5 | -    |      |

|                                     |                                                                                                         |                                         | T <sub>A</sub> = 25 °C  | -   | 2.5 | -    |      |

|                                     |                                                                                                         |                                         | T <sub>A</sub> = 10 °C  | -   | 4   | -    |      |

| + (3)                               |                                                                                                         |                                         | T <sub>A</sub> = 0 °C   | -   | 6   | -    |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                                                                                            |                                         | T <sub>A</sub> = -10 °C | -   | 10  | -    | S    |

|                                     |                                                                                                         |                                         | T <sub>A</sub> = -20 °C | -   | 17  | -    |      |

|                                     |                                                                                                         |                                         | T <sub>A</sub> = -30 °C | -   | 32  | -    |      |

|                                     |                                                                                                         |                                         | T <sub>A</sub> = -40 °C | -   | 60  | -    |      |

Table 24. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz)<sup>(1) (2)</sup>

1. Guaranteed by characterization results, not tested in production.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

- 2. Refer to application note AN2868 "STM32F10xxx internal RC oscillator (HSI) calibration" available from the ST website <a href="https://www.st.com">www.st.com</a>

- 3. Guaranteed by design, not tested in production.

- 4. Guaranteed by characterization results, not tested in production.

## Low-speed internal (LSI) RC oscillator

| Table 26. LSI oscillator characteristics ( | 1) | ) |

|--------------------------------------------|----|---|

|--------------------------------------------|----|---|

| Symbol                              | Parameter                        | Min | Тур  | Мах | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 30  | 40   | 60  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.65 | 1.2 | μA   |

1.  $V_{DD}$  = 3 V, T<sub>A</sub> = -40 to 85 °C unless otherwise specified.

2. Guaranteed by characterization results, not tested in production.

3. Guaranteed by design, not tested in production.

#### Wakeup time from low-power mode

The wakeup times given in *Table 27* are measured on a wakeup phase with an 8-MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| Symbol                              | Parameter                                           | Тур | Unit |

|-------------------------------------|-----------------------------------------------------|-----|------|

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                              | 1.8 | μs   |

| t <sub>WUSTOP</sub> <sup>(1)</sup>  | Wakeup from Stop mode (regulator in run mode)       | 3.6 |      |

|                                     | Wakeup from Stop mode (regulator in low-power mode) | 5.4 | μs   |

| twustdby <sup>(1)</sup>             | Wakeup from Standby mode                            | 50  | μs   |

Table 27. Low-power mode wakeup timings

1. The wakeup times are measured from the wakeup event to the point at which the user application code reads the first instruction.

# 5.3.8 PLL characteristics

The parameters given in *Table 28* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| Symbol               | Parameter                      |                    | 11  |                    |      |

|----------------------|--------------------------------|--------------------|-----|--------------------|------|

|                      |                                | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

| f <sub>PLL_IN</sub>  | PLL input clock <sup>(2)</sup> | 1                  | 8.0 | 25                 | MHz  |

|                      | PLL input clock duty cycle     | 40                 | -   | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16                 | -   | 36                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -                  | -   | 200                | μs   |

| Jitter               | Cycle-to-cycle jitter          | -                  | -   | 300                | ps   |

1. Guaranteed by characterization results, not tested in production.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\mathsf{PLL}_\mathsf{OUT}}$ .

# 5.3.9 Memory characteristics

# **Flash memory**

The characteristics are given at  $T_A = -40$  to 85 °C unless otherwise specified.

| Symbol             | Parameter               | Conditions                                                                            | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | $T_A = -40$ to +85 °C                                                                 | 40  | 52.5 | 70                 | μs   |

| t <sub>ERASE</sub> | Page (2 KB) erase time  | $T_A = -40$ to +85 °C                                                                 | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | $T_A = -40$ to +85 °C                                                                 | 20  | -    | 40                 | ms   |

| I <sub>DD</sub>    | Supply current          | Read mode<br>f <sub>HCLK</sub> = 36 MHz with 1<br>wait state, V <sub>DD</sub> = 3.3 V | -   | -    | 28                 | mA   |

|                    |                         | Write mode<br>f <sub>HCLK</sub> = 36 MHz, V <sub>DD</sub> =<br>3.3 V                  | -   | -    | 7                  | mA   |

|                    |                         | Erase mode<br>f <sub>HCLK</sub> = 36 MHz, V <sub>DD</sub> =<br>3.3 V                  | -   | -    | 5                  | mA   |

|                    |                         | Power-down mode / Halt,<br>V <sub>DD</sub> = 3.0 to 3.6 V                             | -   | -    | 50                 | μA   |

| V <sub>prog</sub>  | Programming voltage     |                                                                                       | 2   | -    | 3.6                | V    |

### Table 29. Flash memory characteristics

1. Guaranteed by design, not tested in production.

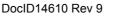

Figure 24. Asynchronous multiplexed NOR/PSRAM write waveforms

| Table 34. Asynchronous | multiplexed NOR/P | SRAM write timings <sup>(1)(2)</sup> |

|------------------------|-------------------|--------------------------------------|

|                        |                   |                                      |

| Symbol                    | Parameter                                                 | Min                     | Мах                     | Unit |

|---------------------------|-----------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                          | 5t <sub>HCLK</sub> – 1  | 5t <sub>HCLK</sub> + 2  | ns   |

| t <sub>v(NWE_NE)</sub>    | FSMC_NEx low to FSMC_NWE low                              | 1t <sub>HCLK</sub>      | 1t <sub>HCLK</sub> + 1  | ns   |

| t <sub>w(NWE)</sub>       | FSMC_NWE low time                                         | 3t <sub>HCLK</sub> – 1  | 2                       | ns   |

| t <sub>h(NE_NWE)</sub>    | FSMC_NWE high to FSMC_NE high hold time                   | t <sub>HCLK</sub> – 1   | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                              | -                       | 7                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                             | 3                       | 5                       | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                        | t <sub>HCLK</sub> – 1   | t <sub>HCLK</sub> + 1   | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD (address) valid hold time after<br>FSMC_NADV high | t <sub>HCLK</sub> – 3   | -                       | ns   |

| t <sub>h(A_NWE)</sub>     | Address hold time after FSMC_NWE high                     | 1t <sub>HCLK</sub>      | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                             | -                       | 1.6                     | ns   |

| t <sub>h(BL_NWE)</sub>    | FSMC_BL hold time after FSMC_NWE high                     | t <sub>HCLK</sub> – 1.5 | -                       | ns   |

| t <sub>v(Data_NADV)</sub> | FSMC_NADV high to Data valid                              | -                       | t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FSMC_NWE high                        | t <sub>HCLK</sub> – 5   | -                       | ns   |

1. C<sub>L</sub> = 15 pF.

2. Guaranteed by characterization results, not tested in production..

| Symbol                       | Parameter                                         | Min  | Max | Unit |

|------------------------------|---------------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                                   | 55.5 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)             | -    | 1.5 | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)            | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low                     | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high                    | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)          | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625)        | 2    | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>    | FSMC_CLK high to FSMC_NOE low                     | -    | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>    | FSMC_CLK low to FSMC_NOE high                     | 0.5  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>     | FSMC_CLK low to FSMC_AD[15:0] valid               | -    | 12  | ns   |

| t <sub>d(CLKL-ADIV)</sub>    | FSMC_CLK low to FSMC_AD[15:0] invalid             | 0    | -   | ns   |

| t <sub>su(ADV-CLKH)</sub>    | FSMC_A/D[15:0] valid data before FSMC_CLK<br>high | 6    | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>     | FSMC_A/D[15:0] valid data after FSMC_CLK high     | 0    | -   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high             | 8    | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high              | 2    | -   | ns   |

Table 35. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 15 pF.

2. Guaranteed by characterization results, not tested in production..

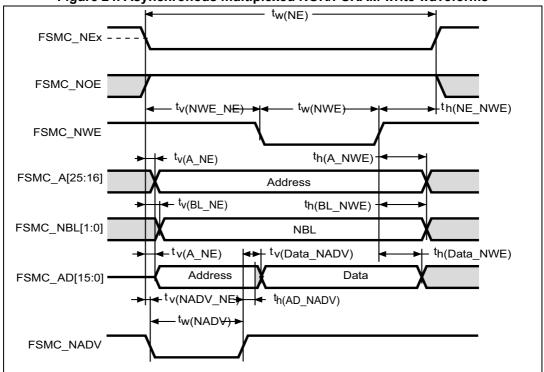

Figure 27. Synchronous non-multiplexed NOR/PSRAM read timings

# Table 37. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

| Symbol                       | Parameter                                    | Min  | Мах | Unit |

|------------------------------|----------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                              | 55.5 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)        | -    | 1.5 | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)       | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low                | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high               | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 025)      | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 025)    | 4    | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>    | FSMC_CLK high to FSMC_NOE low                | -    | 1.5 | ns   |

| t <sub>d(CLKL-NOEH)</sub>    | FSMC_CLK low to FSMC_NOE high                | 1.5  | -   | ns   |

| t <sub>su(DV-CLKH)</sub>     | FSMC_D[15:0] valid data before FSMC_CLK high | 6.5  | -   | ns   |

| t <sub>h(CLKH-DV)</sub>      | FSMC_D[15:0] valid data after FSMC_CLK high  | 7    | -   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_SMCLK high      | 7    | -   | ns   |

| t <sub>h(CLKH-NWAITV)</sub>  | FSMC_NWAIT valid after FSMC_CLK high         | 2    | -   | ns   |

1. C<sub>L</sub> = 15 pF.

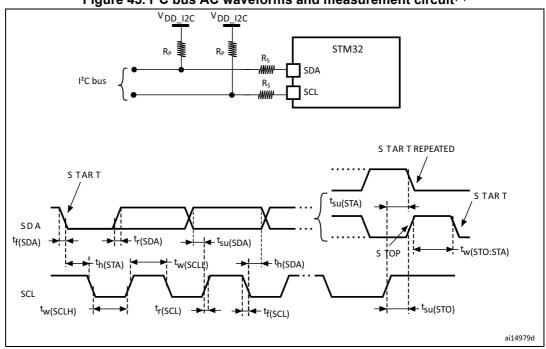

Figure 45. I<sup>2</sup>C bus AC waveforms and measurement circuit<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}.$

- 1.  $R_S$  = series protection resistor.

- 2.  $R_P$  = external pull-up resistor.

- 3.  $V_{DD\_I2C}$  is the I2C bus power supply.

| f <sub>SCL</sub> | I2C_CCR value           |

|------------------|-------------------------|

| (kHz)            | R <sub>P</sub> = 4.7 kΩ |

| 400              | 0x801E                  |

| 300              | 0x8028                  |

| 200              | 0x803C                  |

| 100              | 0x00B4                  |

| 50               | 0x0168                  |

| 20               | 0x0384                  |

# Table 52. SCL frequency $(f_{PCLK1} = 36 \text{ MHz}, V_{DD} = V_{DD | 12C} = 3.3 \text{ V})^{(1)(2)}$

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed.

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

# **SPI interface characteristics**

Unless otherwise specified, the parameters given in *Table 53Table 54* are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

Refer to *Section 5.3.13: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                               | Conditions                                            | Min                | Max                | Unit   |

|----------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------|--------------------|--------------------|--------|

| f <sub>SCK</sub>                                                           |                                         | Master mode                                           | -                  | 10                 | MHz    |

| 1/t <sub>c(SCK)</sub>                                                      | SPI clock frequency                     | Slave mode                                            | -                  | 10                 | IVITIZ |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>                                 | SPI clock rise and fall time            | Capacitive load: C = 30 pF                            | -                  | 8                  |        |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                                        | NSS setup time                          | Slave mode                                            | 4t <sub>PCLK</sub> | -                  |        |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                                         | NSS hold time                           | Slave mode                                            | 73                 | -                  |        |

| t <sub>w(SCKH)</sub> <sup>(1)</sup><br>t <sub>w(SCKL)</sub> <sup>(1)</sup> | SCK high and low time                   | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | 50                 | 60                 |        |

|                                                                            |                                         | Master mode - SPI1                                    | 3                  | -                  |        |

| t <sub>su(MI)</sub> <sup>(1)</sup><br>t <sub>su(SI)</sub> <sup>(1)</sup>   | Data input setup time                   | Master mode - SPI2                                    | 5                  | -                  |        |

| (SI)                                                                       |                                         | Slave mode                                            | 4                  | -                  |        |

| ▲ (1)                                                                      |                                         | Master mode - SPI1                                    | 4                  | -                  |        |

| t <sub>h(MI)</sub> <sup>(1)</sup>                                          | Data input hold time Master mode - SPI2 | Master mode - SPI2                                    | 6                  | -                  |        |

| t <sub>h(SI)</sub> <sup>(1)</sup>                                          |                                         | Slave mode                                            | 5                  | -                  | ns     |

| t <sub>a(SO)</sub> <sup>(1)(2)</sup>                                       | Data output access                      | Slave mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4  | 0                  | 55                 |        |

| u(00)                                                                      | time                                    | Slave mode, f <sub>PCLK</sub> = 20 MHz                | -                  | 4t <sub>PCLK</sub> |        |

| t <sub>dis(SO)</sub> <sup>(1)(3)</sup>                                     | Data output disable time                | Slave mode                                            | 10                 | -                  |        |

| t <sub>v(SO)</sub> <sup>(1)</sup>                                          | Data output valid<br>time               | Slave mode (after enable edge)                        | -                  | 25                 |        |

| t <sub>v(MO)</sub> <sup>(1)</sup>                                          | Data output valid<br>time               | Master mode (after enable edge)                       | -                  | 6                  |        |

| t <sub>h(SO)</sub> <sup>(1)</sup>                                          | Data output hold                        | Slave mode (after enable edge)                        | 25                 | -                  |        |

| t <sub>h(MO)</sub> <sup>(1)</sup>                                          | time                                    | Master mode (after enable edge)                       | 6                  | -                  |        |

Table 53. STM32F10xxx SPI characteristics

1. Guaranteed by characterization results, not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

Figure 55. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package footprint

1. Dimensions are expressed in millimeters.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| θ      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

# Table 63. LQFP64 – 10 x 10 mm, 64 pin low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

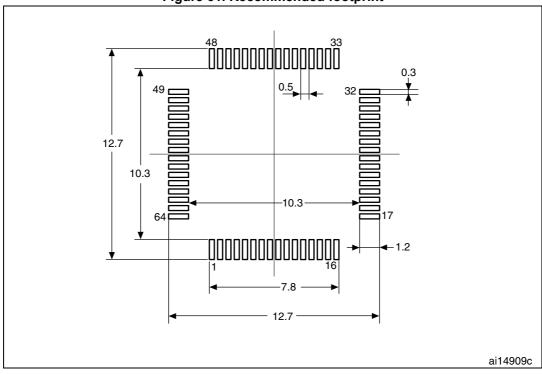

## Figure 61. Recommended footprint

1. Dimensions are in millimeters.

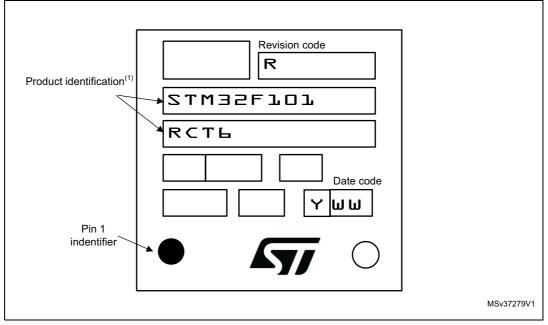

# **Device marking for LQFP64**

The following figure gives an example of topside marking and pin 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.