# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 36MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                             |

| Number of I/O              | 80                                                                    |

| Program Memory Size        | 384KB (384K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 48K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f101vdt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.3.11 Power supply schemes

- $V_{DD}$  = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the ADC or DAC is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 9: Power supply scheme*.

# 2.3.12 **Power supply supervisor**

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software. Refer to *Table 12: Embedded reset and power control block characteristics* for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

# 2.3.13 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop modes.

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode.

## 2.3.14 Low-power modes

The STM32F101xC, STM32F101xD and STM32F101xE access line supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

# SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

# 2.3.18 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multi-master and slave modes. They support standard and fast modes.

They support 7/10-bit addressing mode and 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded. They can be served by DMA and they support SMBus 2.0/PMBus.

# 2.3.19 Universal synchronous/asynchronous receiver transmitters (USARTs)

The STM32F101xC, STM32F101xD and STM32F101xE access line embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3) and two universal asynchronous receiver transmitters (UART4 and UART5).

These five interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The five interfaces are able to communicate at speeds of up to 2.25 Mbit/s.

USART1, USART2 and USART3 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller except for UART5.

# 2.3.20 Serial peripheral interface (SPI)

Up to three SPIs are able to communicate up to 18 Mbits/s in slave and master modes in full-duplex and simplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

All SPIs can be served by the DMA controller.

# 2.3.21 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current-capable.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

# 3 Pinouts and pin descriptions

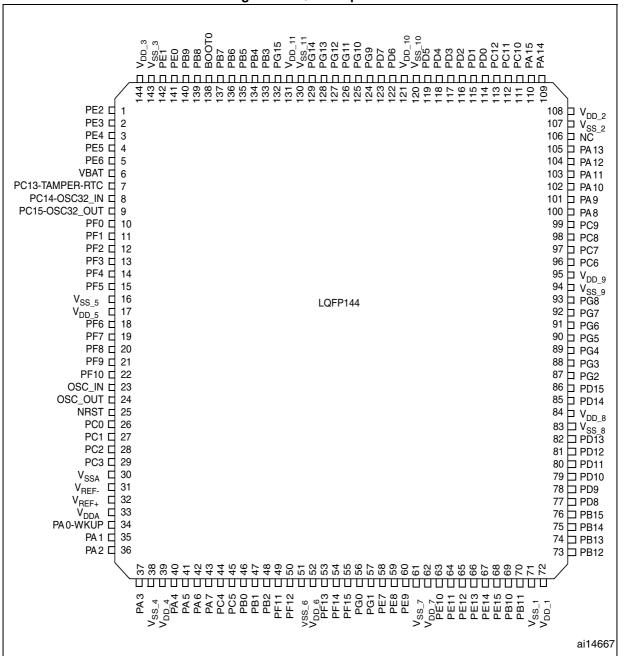

Figure 3. LQFP144 pinout

1. The above figure shows the package top view.

|         | Pins   | abie    | 5. 5110121 101AC/STN | 521                 | 1012                       |                                                  | F101xE pin definitions (continued) Alternate functions <sup>(4)</sup>                 |                    |  |  |

|---------|--------|---------|----------------------|---------------------|----------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------|--------------------|--|--|

|         | F1115  |         |                      |                     |                            |                                                  | Alternate functi                                                                      |                    |  |  |

| LQFP144 | LQFP64 | LQFP100 | Pin name             | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                               | Remap              |  |  |

| 12      | -      | -       | PF2                  | I/O                 | FT                         | PF2                                              | FSMC_A2                                                                               | -                  |  |  |

| 13      | -      | -       | PF3                  | I/O                 | FT                         | PF3                                              | FSMC_A3                                                                               | -                  |  |  |

| 14      | -      | -       | PF4                  | I/O                 | FT                         | PF4                                              | FSMC_A4                                                                               | -                  |  |  |

| 15      | -      | -       | PF5                  | I/O                 | FT                         | PF5                                              | FSMC_A5                                                                               | -                  |  |  |

| 16      | -      | 10      | V <sub>SS_5</sub>    | S                   | -                          | V <sub>SS_5</sub>                                | -                                                                                     | -                  |  |  |

| 17      | -      | 11      | V <sub>DD_5</sub>    | S                   | -                          | V <sub>DD_5</sub>                                | -                                                                                     | -                  |  |  |

| 18      | -      | -       | PF6                  | I/O                 | -                          | PF6                                              | FSMC_NIORD                                                                            | -                  |  |  |

| 19      | -      | -       | PF7                  | I/O                 | -                          | PF7                                              | FSMC_NREG                                                                             | -                  |  |  |

| 20      | -      | -       | PF8                  | I/O                 | -                          | PF8                                              | FSMC_NIOWR                                                                            | -                  |  |  |

| 21      | -      | -       | PF9                  | I/O                 | -                          | PF9                                              | FSMC_CD                                                                               | -                  |  |  |

| 22      | -      | -       | PF10                 | I/O                 | -                          | PF10                                             | FSMC_INTR                                                                             | -                  |  |  |

| 23      | 5      | 12      | OSC_IN               | Ι                   | -                          | OSC_IN                                           | -                                                                                     | PD0 <sup>(7)</sup> |  |  |

| 24      | 6      | 13      | OSC_OUT              | 0                   | -                          | OSC_OUT                                          | -                                                                                     | PD1 <sup>(7)</sup> |  |  |

| 25      | 7      | 14      | NRST                 | I/O                 | -                          | NRST                                             | -                                                                                     | -                  |  |  |

| 26      | 8      | 15      | PC0                  | I/O                 | -                          | PC0                                              | ADC_IN10                                                                              | -                  |  |  |

| 27      | 9      | 16      | PC1                  | I/O                 | -                          | PC1                                              | ADC_IN11                                                                              | -                  |  |  |

| 28      | 10     | 17      | PC2                  | I/O                 | -                          | PC2                                              | ADC_IN12                                                                              | -                  |  |  |

| 29      | 11     | 18      | PC3                  | I/O                 | -                          | PC3                                              | ADC_IN13                                                                              | -                  |  |  |

| 30      | 12     | 19      | V <sub>SSA</sub>     | S                   | -                          | V <sub>SSA</sub>                                 | -                                                                                     | -                  |  |  |

| 31      | -      | 20      | V <sub>REF-</sub>    | S                   | -                          | V <sub>REF-</sub>                                | -                                                                                     | -                  |  |  |

| 32      | -      | 21      | V <sub>REF+</sub>    | S                   | -                          | V <sub>REF+</sub>                                | -                                                                                     | -                  |  |  |

| 33      | 13     | 22      | V <sub>DDA</sub>     | S                   | -                          | V <sub>DDA</sub>                                 | -                                                                                     | -                  |  |  |

| 34      | 14     | 23      | PA0-WKUP             | I/O                 | -                          | PA0                                              | WKUP/ USART2_CTS <sup>(8)</sup> /<br>ADC_IN0/TIM5_CH1/<br>TIM2_CH1_ETR <sup>(8)</sup> | -                  |  |  |

| 35      | 15     | 24      | PA1                  | I/O                 | -                          | PA1                                              | USART2_RTS <sup>(8)</sup> /<br>ADC_IN1/TIM5_CH2<br>TIM2_CH2 <sup>(8)</sup>            | -                  |  |  |

| 36      | 16     | 25      | PA2                  | I/O                 | -                          | PA2                                              | USART2_TX <sup>(8)</sup> /<br>TIM5_CH3/ADC_IN2/<br>TIM2_CH3 <sup>(8)</sup>            | -                  |  |  |

|         | Pins   |         |                   |                     |                            |                                                  | Alternate funct          | -                               |

|---------|--------|---------|-------------------|---------------------|----------------------------|--------------------------------------------------|--------------------------|---------------------------------|

| LQFP144 | LQFP64 | LQFP100 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                  | Remap                           |

| 88      | -      | -       | PG3               | I/O                 | FT                         | PG3                                              | FSMC_A13                 | -                               |

| 89      | -      | -       | PG4               | I/O                 | FT                         | PG4                                              | FSMC_A14                 | -                               |

| 90      | -      | -       | PG5               | I/O                 | FT                         | PG5                                              | FSMC_A15                 | -                               |

| 91      | -      | -       | PG6               | I/O                 | FT                         | PG6                                              | FSMC_INT2                | -                               |

| 92      | -      | -       | PG7               | I/O                 | FT                         | PG7                                              | FSMC_INT3                | -                               |

| 93      | -      | -       | PG8               | I/O                 | FT                         | PG8                                              | -                        | -                               |

| 94      | -      | -       | V <sub>SS_9</sub> | S                   | -                          | V <sub>SS_9</sub>                                | -                        | -                               |

| 95      | -      | -       | V <sub>DD_9</sub> | S                   | -                          | V <sub>DD_9</sub>                                | -                        | -                               |

| 96      | 37     | 63      | PC6               | I/O                 | FT                         | PC6                                              | -                        | TIM3_CH1                        |

| 97      | 38     | 64      | PC7               | I/O                 | FT                         | PC7                                              | -                        | TIM3_CH2                        |

| 98      | 39     | 65      | PC8               | I/O                 | FT                         | PC8                                              | -                        | TIM3_CH3                        |

| 99      | 40     | 66      | PC9               | I/O                 | FT                         | PC9                                              | -                        | TIM3_CH4                        |

| 100     | 41     | 67      | PA8               | I/O                 | FT                         | PA8                                              | USART1_CK/ MCO           | -                               |

| 101     | 42     | 68      | PA9               | I/O                 | FT                         | PA9                                              | USART1_TX <sup>(8)</sup> | -                               |

| 102     | 43     | 69      | PA10              | I/O                 | FT                         | PA10                                             | USART1_RX <sup>(8)</sup> | -                               |

| 103     | 44     | 70      | PA11              | I/O                 | FT                         | PA11                                             | USART1_CTS               | -                               |

| 104     | 45     | 71      | PA12              | I/O                 | FT                         | PA12                                             | USART1_RTS               | -                               |

| 105     | 46     | 72      | PA13              | I/O                 | FT                         | JTMS-SWDIO                                       | -                        | PA13                            |

| 106     | -      | 73      |                   |                     |                            | Not conne                                        | cted                     |                                 |

| 107     | 47     | 74      | V <sub>SS_2</sub> | s                   | -                          | V <sub>SS_2</sub>                                | -                        | -                               |

| 108     | 48     | 75      | V <sub>DD_2</sub> | s                   | -                          | V <sub>DD_2</sub>                                | -                        | -                               |

| 109     | 49     | 76      | PA14              | I/O                 | FT                         | JTCK-SWCLK                                       | -                        | PA14                            |

| 110     | 50     | 77      | PA15              | I/O                 | FT                         | JTDI                                             | SPI3_NSS                 | TIM2_CH1_ETR/<br>PA15 /SPI1_NSS |

| 111     | 51     | 78      | PC10              | I/O                 | FT                         | PC10                                             | UART4_TX                 | USART3_TX                       |

| 112     | 52     | 79      | PC11              | I/O                 | FT                         | PC11                                             | UART4_RX                 | USART3_RX                       |

| 113     | 53     | 80      | PC12              | I/O                 | FT                         | PC12                                             | UART5_TX                 | USART3_CK                       |

| 114     | -      | 81      | PD0               | I/O                 | FT                         | OSC_IN <sup>(8)</sup>                            | FSMC_D2 <sup>(9)</sup>   | -                               |

| 115     | -      | 82      | PD1               | I/O                 | FT                         | OSC_OUT <sup>(8)</sup>                           | FSMC_D3 <sup>(9)</sup>   | -                               |

Table 5. STM32F101xC/STM32F101xD/STM32F101xE pin definitions (continued)

| Symbol                               | Ratings                                                                                  | Max.  | Unit |

|--------------------------------------|------------------------------------------------------------------------------------------|-------|------|

| $\Sigma I_{VDD}$                     | $\Sigma I_{VDD}$ Total current into $V_{DD}/V_{DDA}$ power lines (source) <sup>(1)</sup> |       |      |

| $\Sigma I_{VSS}$                     | Total current out of $V_{SS}$ ground lines $(sink)^{(1)}$                                | 150   |      |

| -                                    | Output current sunk by any I/O and control pin                                           | 25    |      |

| Ι <sub>ΙΟ</sub>                      | Output current source by any I/Os and control pin                                        | - 25  | mA   |

| ı (2)                                | Injected current on five volt tolerant pins <sup>(3)</sup>                               | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                                         | ± 5   |      |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(5)</sup>                  | ± 25  |      |

#### **Table 8. Current characteristics**

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See note 3 below Table 58 on page 98.

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 7: Voltage characteristics* for the maximum allowed input voltage values.

A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 7: Voltage characteristics* for the maximum allowed input voltage values.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

#### **Table 9. Thermal characteristics**

# 5.3.4 Embedded reference voltage

The parameters given in *Table 13* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

| Symbol                                | Parameter                                                     | Conditions                       | Min  | Тур  | Max                 | Unit       |

|---------------------------------------|---------------------------------------------------------------|----------------------------------|------|------|---------------------|------------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                    | –40 °C < T <sub>A</sub> < +85 °C | 1.16 | 1.20 | 1.24                | V          |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the internal reference voltage | -                                | -    | 5.1  | 17.1 <sup>(2)</sup> | μs         |

| V <sub>RERINT</sub> <sup>(2)</sup>    | Internal reference voltage spread over the temperature range  | V <sub>DD</sub> = 3 V ±10 mV     | -    | -    | 10                  | mV         |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                       | -                                | -    | -    | 100                 | ppm/<br>°C |

| Table 13. Embedded internal reference volta | ige |

|---------------------------------------------|-----|

|---------------------------------------------|-----|

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design, not tested in production.

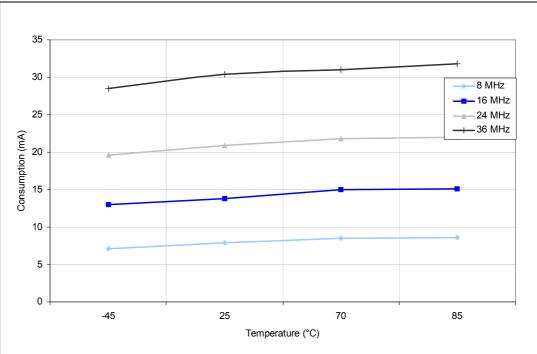

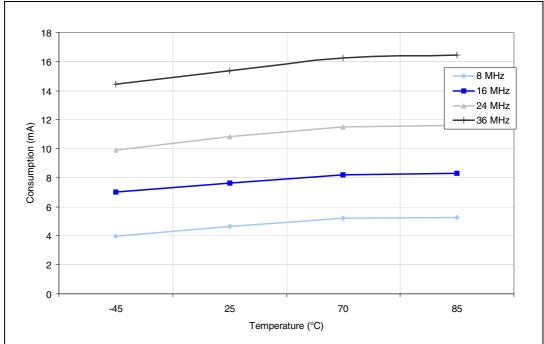

# 5.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 10: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code.

## Maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except if it is explicitly mentioned

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 36 MHz)

- Prefetch in on (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled f<sub>PCLK1</sub> = f<sub>HCLK/2</sub>, f<sub>PCLK2</sub> = f<sub>HCLK</sub>

The parameters given in *Table 14* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

Figure 11. Typical current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals enabled

Figure 12. Typical current consumption in Run mode versus frequency (at 3.6 V) - code with data processing running from RAM, peripherals disabled

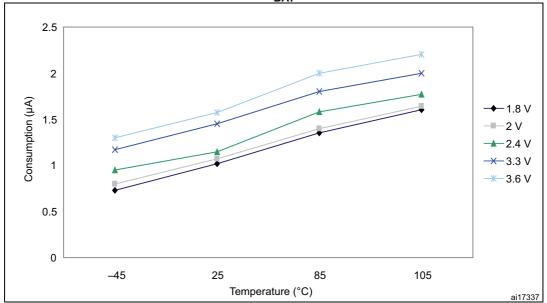

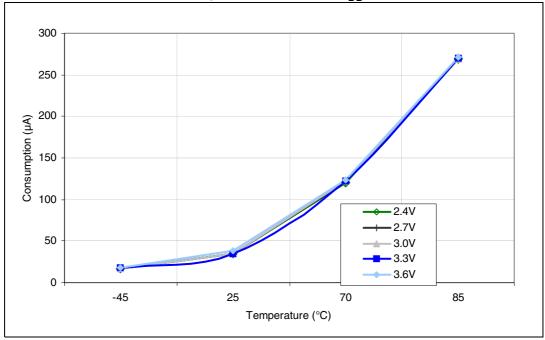

Figure 13. Typical current consumption on  $\rm V_{BAT}$  with RTC on vs. temperature at different  $\rm V_{BAT}$  values

Figure 14. Typical current consumption in Stop mode with regulator in run mode versus temperature at different V<sub>DD</sub> values

|                 |                                    |                                   |                   | Тур <sup>(1)</sup>                        | Тур <sup>(1)</sup>          |      |

|-----------------|------------------------------------|-----------------------------------|-------------------|-------------------------------------------|-----------------------------|------|

| Symbol          | Parameter                          | Conditions                        | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled | Unit |

|                 |                                    |                                   | 36 MHz            | 15.1                                      | 3.6                         |      |

|                 |                                    |                                   | 24 MHz            | 10.4                                      | 2.6                         |      |

|                 |                                    |                                   | 16 MHz            | 7.2                                       | 2                           |      |

|                 |                                    |                                   | 8 MHz             | 3.9                                       | 1.3                         |      |

|                 |                                    | External clock <sup>(3)</sup>     | 4 MHz             | 2.6                                       | 1.2                         |      |

|                 | Supply<br>current in<br>Sleep mode |                                   | 2 MHz             | 1.85                                      | 1.15                        | mA   |

|                 |                                    |                                   | 1 MHz             | 1.5                                       | 1.1                         |      |

|                 |                                    |                                   | 500 kHz           | 1.3                                       | 1.05                        |      |

| 1               |                                    |                                   | 125 kHz           | 1.2                                       | 1.05                        |      |

| I <sub>DD</sub> |                                    | Running on High<br>Speed Internal | 36 MHz            | 14.5                                      | 3                           |      |

|                 |                                    |                                   | 24 MHz            | 9.8                                       | 2                           |      |

|                 |                                    |                                   | 16 MHz            | 6.6                                       | 1.4                         |      |

|                 |                                    |                                   | 8 MHz             | 3.3                                       | 0.7                         |      |

|                 |                                    | RC (HSI), AHB prescaler used to   | 4 MHz             | 2                                         | 0.6                         |      |

|                 |                                    | reduce the<br>frequency           | 2 MHz             | 1.25                                      | 0.55                        |      |

|                 |                                    |                                   | 1 MHz             | 0.9                                       | 0.5                         |      |

|                 |                                    |                                   | 500 kHz           | 0.7                                       | 0.45                        |      |

|                 |                                    |                                   | 125 kHz           | 0.6                                       | 0.45                        |      |

Table 19. Typical current consumption in Sleep mode, code running from Flash or RAM

1. Typical values are measures at  $T_A = 25 \text{ °C}$ ,  $V_{DD} = 3.3 \text{ V}$ .

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

# On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 20*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 7.

| Symbol                    | Parameter                             | Min                     | Max | Unit |

|---------------------------|---------------------------------------|-------------------------|-----|------|

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high | t <sub>HCLK</sub>       | -   | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high | 0                       | -   | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid         | -                       | 0   | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time      | 2t <sub>HCLK</sub> + 24 | -   | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time      | 2t <sub>HCLK</sub> + 25 | -   | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high    | 0                       | -   | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high    | 0                       | -   | ns   |

Table 33. Asynchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 15 pF.

2. Guaranteed by characterization results, not tested in production.

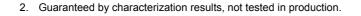

Figure 28. Synchronous non-multiplexed PSRAM write timings

# Table 38. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                       | Parameter                                  | Min  | Мах | Unit |

|------------------------------|--------------------------------------------|------|-----|------|

| t <sub>w(CLK)</sub>          | FSMC_CLK period                            | 55.5 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>    | FSMC_CLK low to FSMC_NEx low (x = 02)      | -    | 2   | ns   |

| t <sub>d(CLKL-NExH)</sub>    | FSMC_CLK low to FSMC_NEx high (x = 02)     | 2    | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>   | FSMC_CLK low to FSMC_NADV low              | -    | 4   | ns   |

| t <sub>d(CLKL-NADVH)</sub>   | FSMC_CLK low to FSMC_NADV high             | 5    | -   | ns   |

| t <sub>d(CLKL-AV)</sub>      | FSMC_CLK low to FSMC_Ax valid (x = 1625)   | -    | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>     | FSMC_CLK low to FSMC_Ax invalid (x = 1625) | 2    | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>    | FSMC_CLK low to FSMC_NWE low               | -    | 1   | ns   |

| t <sub>d(CLKL-NWEH)</sub>    | FSMC_CLK low to FSMC_NWE high              | 1    | -   | ns   |

| t <sub>d(CLKL-Data)</sub>    | FSMC_D[15:0] valid data after FSMC_CLK low | -    | 6   | ns   |

| t <sub>su(NWAITV-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high      | 7    | -   | ns   |

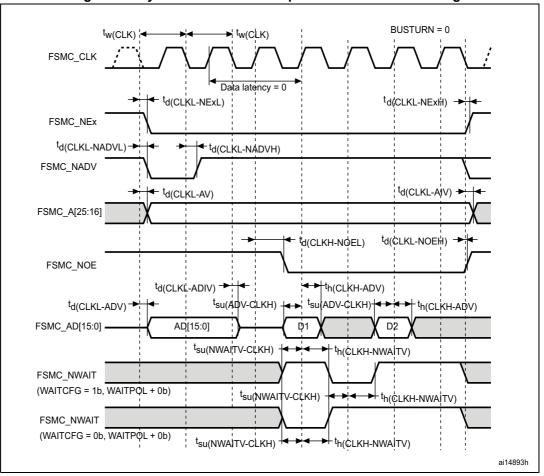

## Figure 34. PC Card/CompactFlash controller waveforms for I/O space write access

| Symbol                                                    | Parameter                                                                                                                      | Min                     | Мах                      | Unit |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------|------|

| t <sub>v(NCEx-A)</sub><br>t <sub>v(NCE4_1-A)</sub>        | FSMC_NCEx low (x = 4_1/4_2) to FSMC_Ay valid (y = 010)<br>FSMC_NCE4_1 low (x = 4_1/4_2) to FSMC_Ay valid (y = 010)             | -                       | 0                        | ns   |

| t <sub>h(NCEx-AI)</sub><br>t <sub>h(NCE4_1-AI)</sub>      | FSMC_NCEx high (x = $4_1/4_2$ ) to FSMC_Ax invalid (x = 010)<br>FSMC_NCE4_1 high (x = $4_1/4_2$ ) to FSMC_Ax invalid (x = 010) | 2.5                     | -                        | ns   |

| t <sub>d(NREG-NCEx)</sub><br>t <sub>d(NREG-NCE4_1)</sub>  | FSMC_NCEx low to FSMC_NREG valid<br>FSMC_NCE4_1 low to FSMC_NREG valid                                                         | -                       | 5                        | ns   |

| t <sub>h(NCEx-NREG)</sub><br>t <sub>h(NCE4_</sub> 1-NREG) | FSMC_NCEx high to FSMC_NREG invalid<br>FSMC_NCE4_1 high to FSMC_NREG invalid                                                   | t <sub>HCLK</sub> + 3   | -                        | ns   |

| t <sub>d(NCE4_1-NOE)</sub>                                | FSMC_NCE4_1 low to FSMC_NOE low                                                                                                | -                       | 5t <sub>HCLK</sub> + 2   | ns   |

| t <sub>w(NOE)</sub>                                       | FSMC_NOE low width                                                                                                             | 8t <sub>HCLK</sub> –1.5 | 8t <sub>HCLK</sub> + 1   | ns   |

| t <sub>d(NOE-NCE4_1</sub>                                 | FSMC_NOE high to FSMC_NCE4_1 high                                                                                              | 5t <sub>HCLK</sub> + 2  | -                        | ns   |

| t <sub>su(D-NOE)</sub>                                    | FSMC_D[15:0] valid data before FSMC_NOE high                                                                                   | 25                      | -                        | ns   |

| t <sub>h(NOE-D)</sub>                                     | FSMC_D[15:0] valid data after FSMC_NOE high                                                                                    | 15                      | -                        | ns   |

| t <sub>w(NWE)</sub>                                       | FSMC_NWE low width                                                                                                             | 8t <sub>HCLK</sub> – 1  | 8t <sub>HCLK</sub> + 2   | ns   |

| t <sub>d(NWE-NCE4_1)</sub>                                | FSMC_NWE high to FSMC_NCE4_1 high                                                                                              | 5t <sub>HCLK</sub> + 2  | -                        | ns   |

| t <sub>d(NCE4_1-NWE)</sub>                                | FSMC_NCE4_1 low to FSMC_NWE low                                                                                                | -                       | 5t <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>v(NWE-D)</sub>                                     | FSMC_NWE low to FSMC_D[15:0] valid                                                                                             | -                       | 0                        | ns   |

| t <sub>h(NWE-D)</sub>                                     | FSMC_NWE high to FSMC_D[15:0] invalid                                                                                          | 11t <sub>HCLK</sub>     | -                        | ns   |

The formula above (Equation 1) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.11                | 0.4                       |

| 7.5                     | 0.54                | 5.9                       |

| 13.5                    | 0.96                | 11.4                      |

| 28.5                    | 2.04                | 25.2                      |

| 41.5                    | 2.96                | 37.2                      |

| 55.5                    | 3.96                | 50                        |

| 71.5                    | 5.11                | NA                        |

| 239.5                   | 17.1                | NA                        |

| Table 56. R <sub>AIN</sub> max for f <sub>ADC</sub> = 14 MHz <sup>(1)</sup> | Table 56. | R <sub>AIN</sub> max | for fADC = | = 14 MHz <sup>(1)</sup> |

|-----------------------------------------------------------------------------|-----------|----------------------|------------|-------------------------|

|-----------------------------------------------------------------------------|-----------|----------------------|------------|-------------------------|

1. Guaranteed by design, not tested in production.

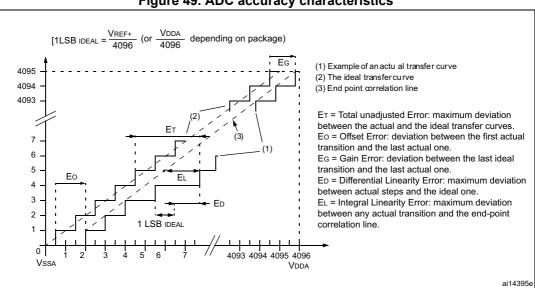

| Symbol | Parameter                    | Test conditions                                                                                              | Тур  | Max <sup>(3)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       | $f_{PCLK2} = 28 \text{ MHz},$                                                                                | ±1.3 | ±2                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ,<br>V <sub>DDA</sub> = 3 V to 3.6 V, T <sub>A</sub> = 25 | ±1   | ±1.5               |      |

| EG     | Gain error                   | °C                                                                                                           | ±0.5 | ±1.5               | LSB  |

| ED     | Differential linearity error | Measurements made after<br>ADC calibration                                                                   | ±0.7 | ±1                 |      |

| EL     | Integral linearity error     | $V_{\text{REF+}} = V_{\text{DDA}}$                                                                           | ±0.8 | ±1.5               |      |

1. ADC DC accuracy values are measured after internal calibration.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in *Section 5.3.13* does not affect the ADC accuracy. 2.

3. Guaranteed by characterization results, not tested in production.

| Symbol | Parameter                    | Test conditions                                                                      | Тур  | Max <sup>(4)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                      | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>PCLK2</sub> = 28 MHz,<br>f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ, | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | $V_{DDA} = 2.4 V \text{ to } 3.6 V$                                                  | ±1.5 | ±3                 | LSB  |

| ED     | Differential linearity error | Measurements made after<br>ADC calibration                                           | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                      | ±1.5 | ±3                 |      |

## Table 58 ADC accuracy<sup>(1)</sup> (2)(3)

1. ADC DC accuracy values are measured after internal calibration.

2. Better performance could be achieved in restricted V<sub>DD</sub>, frequency, V<sub>REF</sub> and temperature ranges.

3. ADC accuracy vs. negative injection current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.13 does not affect the ADC accuracy.

Guaranteed by characterization results, not tested in production. 4.

## Figure 49. ADC accuracy characteristics

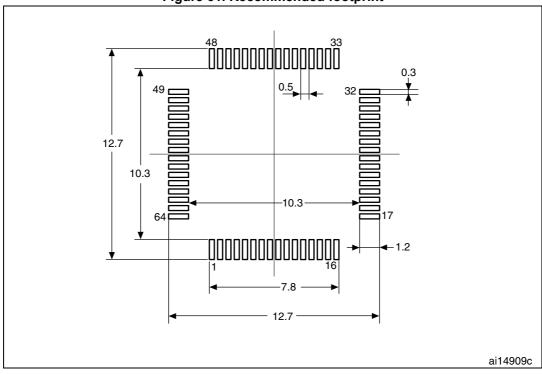

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| θ      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

# Table 63. LQFP64 – 10 x 10 mm, 64 pin low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## Figure 61. Recommended footprint

1. Dimensions are in millimeters.

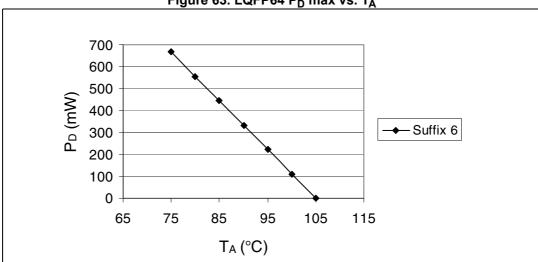

#### 6.4.2 Evaluating the maximum junction temperature for an application

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in Table 65: Ordering information scheme.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature. Here, only temperature range 6 is available (-40 to 85 °C).

The following example shows how to calculate the temperature range needed for a given application, making it possible to check whether the required temperature range is compatible with the STM32F10xxx junction temperature range.

## **Example: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature T<sub>Amax</sub> = 82 °C (measured according to JESD51-2),  $I_{DDmax}$  = 50 mA,  $V_{DD}$  = 3.5 V, maximum 20 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V and maximum 8 I/Os used at the same time in output mode at low level with  $I_{OL}$  = 20 mA,  $V_{OL}$ = 1.3 V P<sub>INTmax</sub> = 50 mA × 3.5 V= 175 mW

P<sub>IOmax</sub> = 20 × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives: P<sub>INTmax</sub> = 175 mW and P<sub>IOmax</sub> = 272 mW

P<sub>Dmax</sub> = 175 + 272 = 447 mW

Thus: P<sub>Dmax</sub> = 447 mW

Using the values obtained in Table 65  $T_{Jmax}$  is calculated as follows:

For LQFP64, 45 °C/W

T<sub>Jmax</sub> = 82 °C + (45 °C/W × 447 mW) = 82 °C + 20.1 °C = 102.1 °C

This is within the junction temperature range of the STM32F10xxx ( $-40 < T_J < 105 \text{ °C}$ ).

Figure 63. LQFP64 P<sub>D</sub> max vs. T<sub>A</sub>

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                     |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |          | Document status promoted from Preliminary Data to full datasheet.<br><i>FSMC (flexible static memory controller) on page 15</i> modified.<br><i>Power supply supervisor on page 17</i> modified and V <sub>DDA</sub> added to<br><i>Table 10: General operating conditions on page 40</i> . |

|             |          | Table notes revised in Section 5: Electrical characteristics.<br>Capacitance modified in Figure 9: Power supply scheme on page 37.<br>Table 52: SCL frequency ( $f_{PCLK1}$ = 36 MHz, $V_{DD} = V_{DD_12C} = 3.3$ V) updated.                                                               |

|             |          | <i>Table 54: SPI characteristics</i> modified, t <sub>h(NSS)</sub> modified in <i>Figure 46: SPI timing diagram - slave mode and CPHA=0 on page 94.</i>                                                                                                                                     |

|             |          | Minimum SDA and SCL fall time value for Fast mode removed from <i>Table 51: I<sup>2</sup>C characteristics on page 90</i> , note 1 modified.                                                                                                                                                |

| 21-Jul-2008 | 3        | I <sub>DD_VBAT</sub> values added to <i>Table 17: Typical and maximum current consumptions in Stop and Standby modes on page 45.</i>                                                                                                                                                        |

|             |          | <i>Table 30: Flash memory endurance and data retention on page 59</i> updated.                                                                                                                                                                                                              |

|             |          | f <sub>HCLK</sub> corrected in <i>Table 41: EMS characteristics</i> .                                                                                                                                                                                                                       |

|             |          | t <sub>su(NSS)</sub> modified in <i>Table 54: SPI characteristics</i> .                                                                                                                                                                                                                     |

|             |          | EO corrected in <i>Table 58: ADC accuracy on page 98</i> , f <sub>PCLK2</sub> corrected in <i>Table 57: ADC accuracy - limited test conditions</i> and <i>Table 58: ADC accuracy</i> .                                                                                                      |

|             |          | <i>Figure 50: Typical connection diagram using the ADC on page 99</i> and note below corrected.                                                                                                                                                                                             |

|             |          | Typical T <sub>S_temp</sub> value removed from <i>Table 60: TS characteristics on page 102</i> .                                                                                                                                                                                            |

|             |          | Section 6.1: LQFP144 package information on page 103 updated,<br>Small text changes.                                                                                                                                                                                                        |

|             |          | General-purpose timers (TIMx) on page 19 updated, Table 3:<br>STM32F101xx family updated to show the low-density family,<br>Table 4: Timer feature comparison added<br>Figure 1: STM32F101xC, STM32F101xD and STM32F101xE access<br>line block diagram updated.                             |

|             |          | <i>Note 9</i> added, main function after reset and <i>Note 5</i> updated in <i>Table 5:</i><br><i>STM32F101xC/STM32F101xD/STM32F101xE pin definitions</i> .                                                                                                                                 |

|             |          | <i>Note 2</i> modified below <i>Table 7: Voltage characteristics on page 38</i> , $ \Delta V_{DDx} $ min and $ \Delta V_{DDx} $ min removed.                                                                                                                                                |

| 12-Dec-2008 | 4        | Measurement conditions specified in <i>Section 5.3.5: Supply current characteristics on page 42.</i>                                                                                                                                                                                        |

|             |          | General input/output characteristics on page 82 modified.                                                                                                                                                                                                                                   |

|             |          | Max values at $T_A = 85$ °C updated in <i>Table 17: Typical and maximum current consumptions in Stop and Standby modes on page 45.</i>                                                                                                                                                      |

|             |          | Section 5.3.10: FSMC characteristics on page 59 revised.                                                                                                                                                                                                                                    |

|             |          | Values added to Table 42: EMI characteristics on page 80.                                                                                                                                                                                                                                   |

|             |          | I <sub>VREF</sub> added to <i>Table 55: ADC characteristics on page 96</i> .                                                                                                                                                                                                                |

|             |          | <i>Table 64: Package thermal characteristics on page 113</i> updated, Small text changes.                                                                                                                                                                                                   |

Table 66.

Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19-Apr-2011 | 8        | Updated footnotes below Table 7: Voltage characteristics on page 38<br>and Table 8: Current characteristics on page 39<br>Updated tw min in Table 21: High-speed external user clock<br>characteristics on page 51<br>Updated startup time in Table 24: LSE oscillator characteristics ( $f_{LSE}$ =<br>32.768 kHz) on page 55<br>Updated Table 31: Asynchronous non-multiplexed<br>SRAM/PSRAM/NOR read timings on page 60<br>Updated FSMC sync data latency in Figure 25 thru Figure 28<br>Updated Figure 38: NAND controller waveforms for common memory<br>write access and Table 40: Switching characteristics for NAND Flash<br>read and write cycles on page 78<br>Updated Figure 44: Recommended NRST pin protection<br>Added Section 5.3.13: I/O current injection characteristics<br>Updated note 2 in Table 51: I <sup>2</sup> C characteristics on page 90<br>Updated Figure 45: I <sup>2</sup> C bus AC waveforms and measurement circuit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15-May-2015 | 9        | Added OSC_IN/OSC_OUT remap functions and updated PD0/PD1 in<br>Table 5: STM32F101xC/STM32F101xD/STM32F101xE pin definitions.<br>Modified Section 2.3.21: GPIOs (general-purpose inputs/outputs) on<br>page 20.<br>Updated notes related to parameters not tested in production in the<br>whole document.<br>Updated Table 20: Peripheral current consumption on page 50.<br>Updated CDM standard and values in Section : Electrostatic discharge<br>(ESD).<br>Modified Section : Output driving current on page 84.<br>Updated Figure 43: I/O AC characteristics definition.<br>Updated conditions related to Section : I <sup>2</sup> C interface characteristics.<br>Modified Table 51: I <sup>2</sup> C characteristics on page 90, updated Figure 45:<br>I <sup>2</sup> C bus AC waveforms and measurement circuit <sup>(1)</sup> and V <sub>DD</sub> /V <sub>DD_12C</sub><br>conditions in Table 52: SCL frequency (f <sub>PCLK1</sub> = 36 MHz, V <sub>DD</sub> = V <sub>DD_12C</sub><br>= 3.3 V) on page 91.<br>Modified Figure 48: SPI timing diagram - master mode <sup>(1)</sup> on page 95.<br>Modified note 3 in Table 58: ADC accuracy on page 98.<br>Updated I <sub>DDA</sub> definition in Table 59: DAC characteristics on page 100<br>and removed comment related to the offset parameter for ±10 mV.<br>Corrected "CLKL-NOEL" in Section 5.3.10: FSMC characteristics on<br>page 59.<br>Updated Section 6.1: LQFP144 package information on page 103 and<br>added Section : Device marking for LQFP144 on page 106.<br>Updated Section 6.2: LQFP100 package information on page 107 and<br>added Section 6.3: LQFP64 information on page 110 and added<br>Section : Device marking for LQFP144 on page 110. |

Table 66. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved