Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 36MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                               |

| Number of I/O              | 80                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f101vet6tr |

| Figure 41. | 5 V tolerant I/O input characteristics - CMOS port                                           | 84  |

|------------|----------------------------------------------------------------------------------------------|-----|

| Figure 42. | 5 V tolerant I/O input characteristics - TTL port                                            | 84  |

| Figure 43. | I/O AC characteristics definition                                                            | 87  |

| Figure 44. | Recommended NRST pin protection                                                              |     |

| Figure 45. | I <sup>2</sup> C bus AC waveforms and measurement circuit <sup>(1)</sup>                     | 91  |

| Figure 46. | SPI timing diagram - slave mode and CPHA=0                                                   | 94  |

| Figure 47. | SPI timing diagram - slave mode and CPHA=1 <sup>(1)</sup>                                    | 94  |

| Figure 48. | SPI timing diagram - master mode <sup>(1)</sup>                                              | 95  |

| Figure 49. | ADC accuracy characteristics                                                                 |     |

| Figure 50. | Typical connection diagram using the ADC                                                     | 99  |

| Figure 51. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) | 99  |

| Figure 52. | Power supply and reference decoupling (VREF+ connected to VDDA)                              | 100 |

| Figure 53. | 12-bit buffered /non-buffered DAC                                                            | 102 |

| Figure 54. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline                          | 103 |

| Figure 55. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package                                  |     |

|            | footprint                                                                                    | 105 |

| Figure 56. | LQFP144 marking (package top view)                                                           | 106 |

| Figure 57. | LQFP100 – 14 x 14 mm, 100-pin low-profile quad flat package outline                          | 107 |

| Figure 58. | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat                                          |     |

|            | recommended footprint                                                                        | 108 |

| Figure 59. | LQFP100 marking (package top view)                                                           | 109 |

| Figure 60. | LQFP64 – 10 x 10 mm, 64 pin low-profile quad flat package outline                            | 110 |

| Figure 61. | Recommended footprint                                                                        | 111 |

| Figure 62. | LQFP64 marking (package top view)                                                            | 112 |

| Figure 63. | LQFP64 P <sub>D</sub> max vs. T <sub>A</sub>                                                 | 114 |

|            |                                                                                              |     |

## 2.3.11 Power supply schemes

- $V_{DD}$  = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through  $V_{DD}$  pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the ADC or DAC is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- $V_{BAT}$  = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when  $V_{DD}$  is not present.

For more details on how to connect power pins, refer to Figure 9: Power supply scheme.

# 2.3.12 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software. Refer to Table 12: Embedded reset and power control block characteristics for the values of  $V_{POR/PDR}$  and  $V_{PVD}$ .

# 2.3.13 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop modes.

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode.

#### 2.3.14 Low-power modes

The STM32F101xC, STM32F101xD and STM32F101xE access line supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

## SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

#### 2.3.18 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multi-master and slave modes. They support standard and fast modes.

They support 7/10-bit addressing mode and 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

## 2.3.19 Universal synchronous/asynchronous receiver transmitters (USARTs)

The STM32F101xC, STM32F101xD and STM32F101xE access line embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3) and two universal asynchronous receiver transmitters (UART4 and UART5).

These five interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The five interfaces are able to communicate at speeds of up to 2.25 Mbit/s.

USART1, USART2 and USART3 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller except for UART5.

## 2.3.20 Serial peripheral interface (SPI)

Up to three SPIs are able to communicate up to 18 Mbits/s in slave and master modes in full-duplex and simplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

All SPIs can be served by the DMA controller.

# 2.3.21 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current-capable.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

20/121 DocID14610 Rev 9

# 3 Pinouts and pin descriptions

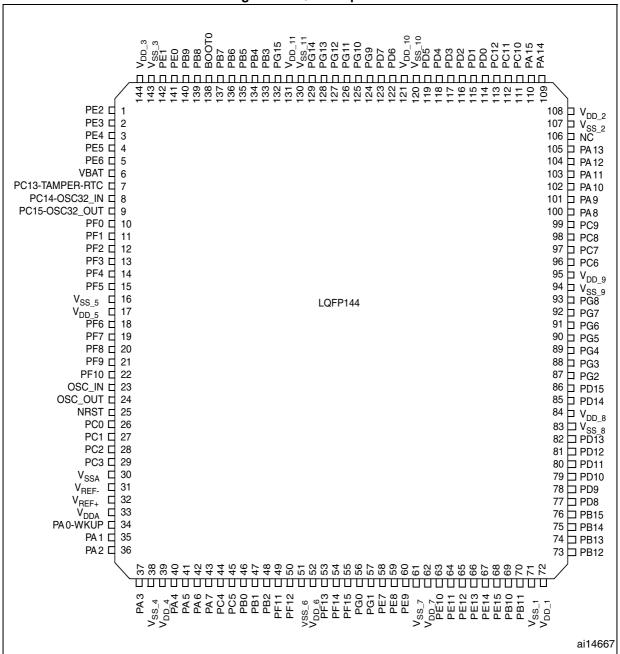

Figure 3. LQFP144 pinout

1. The above figure shows the package top view.

VBAT ☐ 1 PC13-TAMPER-RTC 45 PA 12 44 PA 11 43 PA 10 42 PA 9 PD1-OS C\_OUT NRST 41 PA 8 40 PC9 39 PC8 LQFP64 38 PC7 37 PC6 12 13 Vssa 36 PB 15 VDDA 35 PB 14 34 PB 13 PA 0-WKUP 14 PA 1 15 PA 2 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 PB 12 PA 3 VSS\_4 VDD\_4 PA 4 PA 5 PA 6 PA 7 PC 7 PC 9 PB 1 ai14392

Figure 5. LQFP64 pinout

1. The above figure shows the package top view.

Table 5. STM32F101xC/STM32F101xD/STM32F101xE pin definitions

|         | Pins   |         |                                |                     |    |                                                  | Alternate functi   | ons <sup>(4)</sup> |

|---------|--------|---------|--------------------------------|---------------------|----|--------------------------------------------------|--------------------|--------------------|

| LQFP144 | LQFP64 | LQFP100 | Pin name                       | Type <sup>(1)</sup> |    | Main<br>function <sup>(3)</sup><br>(after reset) | Default            | Remap              |

| 1       | -      | 1       | PE2                            | I/O                 | FT | PE2                                              | TRACECLK/ FSMC_A23 | -                  |

| 2       | i      | 2       | PE3                            | I/O                 | FT | PE3                                              | TRACED0/FSMC_A19   | -                  |

| 3       | i      | 3       | PE4                            | I/O                 | FT | PE4                                              | TRACED1/FSMC_A20   | -                  |

| 4       | ı      | 4       | PE5                            | I/O                 | FT | PE5                                              | TRACED2/FSMC_A21   | -                  |

| 5       | -      | 5       | PE6                            | I/O                 | FT | PE6                                              | TRACED3/FSMC_A22   | -                  |

| 6       | 1      | 6       | $V_{BAT}$                      | S                   | -  | $V_{BAT}$                                        | -                  | -                  |

| 7       | 2      | 7       | PC13-TAMPER-RTC <sup>(5)</sup> | I/O                 | -  | PC13 <sup>(6)</sup>                              | TAMPER-RTC         | -                  |

| 8       | 3      | 8       | PC14-OSC32_IN <sup>(5)</sup>   | I/O                 | -  | PC14 <sup>(6)</sup>                              | OSC32_IN           | -                  |

| 9       | 4      | 9       | PC15-OSC32_OUT <sup>(5)</sup>  | I/O                 | -  | PC15 <sup>(6)</sup>                              | OSC32_OUT          | -                  |

| 10      | -      | -       | PF0                            | I/O                 | FT | PF0                                              | FSMC_A0            | -                  |

| 11      | -      | -       | PF1                            | I/O                 | FT | PF1                                              | FSMC_A1            | -                  |

Table 5. STM32F101xC/STM32F101xD/STM32F101xE pin definitions (continued)

|         | Pins   |         |                   |                     |                            |                                                  | Alternate functions <sup>(4)</sup> |                                 |

|---------|--------|---------|-------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------|---------------------------------|

| LQFP144 | LQFP64 | LQFP100 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                            | Remap                           |

| 88      | -      | 1       | PG3               | I/O                 | FT                         | PG3                                              | FSMC_A13                           | -                               |

| 89      | -      | -       | PG4               | I/O                 | FT                         | PG4                                              | FSMC_A14                           | -                               |

| 90      | -      | -       | PG5               | I/O                 | FT                         | PG5                                              | FSMC_A15                           | -                               |

| 91      | -      | -       | PG6               | I/O                 | FT                         | PG6                                              | FSMC_INT2                          | -                               |

| 92      | -      | 1       | PG7               | I/O                 | FT                         | PG7                                              | FSMC_INT3                          | -                               |

| 93      | -      | 1       | PG8               | I/O                 | FT                         | PG8                                              | -                                  | -                               |

| 94      | -      | 1       | V <sub>SS_9</sub> | S                   | -                          | V <sub>SS_9</sub>                                | -                                  | -                               |

| 95      | -      | 1       | V <sub>DD_9</sub> | S                   | -                          | V <sub>DD_9</sub>                                | -                                  | -                               |

| 96      | 37     | 63      | PC6               | I/O                 | FT                         | PC6                                              | -                                  | TIM3_CH1                        |

| 97      | 38     | 64      | PC7               | I/O                 | FT                         | PC7                                              | -                                  | TIM3_CH2                        |

| 98      | 39     | 65      | PC8               | I/O                 | FT                         | PC8                                              | -                                  | TIM3_CH3                        |

| 99      | 40     | 66      | PC9               | I/O                 | FT                         | PC9                                              | -                                  | TIM3_CH4                        |

| 100     | 41     | 67      | PA8               | I/O                 | FT                         | PA8                                              | USART1_CK/ MCO                     | -                               |

| 101     | 42     | 68      | PA9               | I/O                 | FT                         | PA9                                              | USART1_TX <sup>(8)</sup>           | -                               |

| 102     | 43     | 69      | PA10              | I/O                 | FT                         | PA10                                             | USART1_RX <sup>(8)</sup>           | -                               |

| 103     | 44     | 70      | PA11              | I/O                 | FT                         | PA11                                             | USART1_CTS                         | -                               |

| 104     | 45     | 71      | PA12              | I/O                 | FT                         | PA12                                             | USART1_RTS                         | -                               |

| 105     | 46     | 72      | PA13              | I/O                 | FT                         | JTMS-SWDIO                                       | -                                  | PA13                            |

| 106     | -      | 73      |                   |                     |                            | Not conne                                        | cted                               |                                 |

| 107     | 47     | 74      | V <sub>SS_2</sub> | S                   | -                          | V <sub>SS_2</sub>                                | -                                  | -                               |

| 108     | 48     | 75      | V <sub>DD_2</sub> | S                   | -                          | V <sub>DD_2</sub>                                | -                                  | -                               |

| 109     | 49     | 76      | PA14              | I/O                 | FT                         | JTCK-SWCLK                                       | -                                  | PA14                            |

| 110     | 50     | 77      | PA15              | I/O                 | FT                         | JTDI                                             | SPI3_NSS                           | TIM2_CH1_ETR/<br>PA15 /SPI1_NSS |

| 111     | 51     | 78      | PC10              | I/O                 | FT                         | PC10                                             | UART4_TX                           | USART3_TX                       |

| 112     | 52     | 79      | PC11              | I/O                 | FT                         | PC11                                             | UART4_RX                           | USART3_RX                       |

| 113     | 53     | 80      | PC12              | I/O                 | FT                         | PC12                                             | UART5_TX                           | USART3_CK                       |

| 114     | -      | 81      | PD0               | I/O                 | FT                         | OSC_IN <sup>(8)</sup>                            | FSMC_D2 <sup>(9)</sup>             | -                               |

| 115     | -      | 82      | PD1               | I/O                 | FT                         | OSC_OUT <sup>(8)</sup>                           | FSMC_D3 <sup>(9)</sup>             | _                               |

Alternate functions(4) **Pins** O Level<sup>(2)</sup> Main -QFP144 function<sup>(3)</sup> LQFP100 LQFP64 Pin name Default (after reset) Remap 96 TIM4 CH4 (8) 140 62 PB9 I/O FT PB9 I2C1 SDA TIM4 ETR(8)/ PE0 141 97 I/C FT PE0 FSMC NBL0 FSMC\_NBL1 142 98 PE1 I/O FT PE1 \_ 143 63 99 S \_ V<sub>SS 3</sub> V<sub>SS 3</sub> 144 100 S 64  $V_{DD 3}$ \_  $V_{DD_3}$ \_ \_

Table 5. STM32F101xC/STM32F101xD/STM32F101xE pin definitions (continued)

- 1. I = input, O = output, S = supply.

- 2 FT = 5 V tolerant

- 3. Function availability depends on the chosen device.

- 4. If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral should be enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).

- PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these IOs must not be used as a current source (e.g. to drive an LED).

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- 7. For the LQFP64 package, the pins number 5 and 6 are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For the LQFP100 and LQFP144 packages, PD0 and PD1 are available by default, so there is no need for remapping. For more details, refer to Alternate function I/O and debug configuration section in the STM32F10xxx reference manual

- This alternate function can be remapped by software to some other port pins (if available on the used package). For more

details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual, available

from the STMicroelectronics website: www.st.com.

- 9. For devices delivered in LQFP64 packages, the FSMC function is not available.

Table 6. FSMC pin definition

| FSMC |        |        |                    |                  |             |                        |

|------|--------|--------|--------------------|------------------|-------------|------------------------|

| Pins | CF     | CF/IDE | NOR/PSRAM/<br>SRAM | NOR/PSRAM<br>Mux | NAND 16 bit | LQFP100 <sup>(1)</sup> |

| PE2  | -      | -      | A23                | A23              | -           | Yes                    |

| PE3  | -      | -      | A19                | A19              | -           | Yes                    |

| PE4  | -      | -      | A20                | A20              | _           | Yes                    |

| PE5  | -      | -      | A21                | A21              | -           | Yes                    |

| PE6  | -      | -      | A22                | A22              | _           | Yes                    |

| PF0  | A0     | A0     | A0                 | -                | -           | -                      |

| PF1  | A1     | A1     | A1                 | -                | -           | -                      |

| PF2  | A2     | A2     | A2                 | -                | -           | -                      |

| PF3  | A3     | -      | А3                 | -                | -           | -                      |

| PF4  | A4     | -      | A4                 | -                | -           | -                      |

| PF5  | A5     | -      | A5                 | -                | -           | -                      |

| PF6  | NIORD  | NIORD  | -                  | -                | -           | -                      |

| PF7  | NREG   | NREG   | -                  | -                | -           | -                      |

| PF8  | NIOWR  | NIOWR  | -                  | -                | -           | -                      |

| PF9  | CD     | CD     | -                  | -                | -           | -                      |

| PF10 | INTR   | INTR   | -                  | -                | -           | -                      |

| PF11 | NIOS16 | NIOS16 | -                  | -                | -           | -                      |

| PF12 | A6     | -      | A6                 | -                | _           | -                      |

| PF13 | A7     | -      | A7                 | -                | -           | -                      |

| PF14 | A8     | -      | A8                 | -                | -           | -                      |

| PF15 | A9     | -      | A9                 | -                | -           | -                      |

| PG0  | A10    | -      | A10                | -                | -           | -                      |

| PG1  | -      | -      | A11                | -                | -           | -                      |

| PE7  | D4     | D4     | D4                 | DA4              | D4          | Yes                    |

| PE8  | D5     | D5     | D5                 | DA5              | D5          | Yes                    |

| PE9  | D6     | D6     | D6                 | DA6              | D6          | Yes                    |

| PE10 | D7     | D7     | D7                 | DA7              | D7          | Yes                    |

| PE11 | D8     | D8     | D8                 | DA8              | D8          | Yes                    |

| PE12 | D9     | D9     | D9                 | DA9              | D9          | Yes                    |

| PE13 | D10    | D10    | D10                | DA10             | D10         | Yes                    |

| PE14 | D11    | D11    | D11                | DA11             | D11         | Yes                    |

| PE15 | D12    | D12    | D12                | DA12             | D12         | Yes                    |

| PD8  | D13    | D13    | D13                | DA13             | D13         | Yes                    |

# 5.1.7 Current consumption measurement

IDD\_VBAT VBAT VDD VDD VDDA

Figure 10. Current consumption measurement scheme

# 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 7: Voltage characteristics*, *Table 8: Current characteristics*, and *Table 9: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                                                         | Min                                                                         | Max                   | Unit |

|------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|------|

| V <sub>DD</sub> – V <sub>SS</sub>  | External main supply voltage (including $V_{DDA}$ and $V_{DD}$ ) <sup>(1)</sup> | -0.3                                                                        | 4.0                   | .,   |

| V <sub>IN</sub> <sup>(2)</sup>     | Input voltage on five volt tolerant pin                                         | V <sub>SS</sub> - 0.3                                                       | V <sub>DD</sub> + 4.0 | V    |

|                                    | Input voltage on any other pin                                                  | V <sub>SS</sub> - 0.3                                                       | 4.0                   |      |

| $ \Delta V_{DDx} $                 | Variations between different V <sub>DD</sub> power pins                         | -                                                                           | 50                    |      |

| V <sub>SSX</sub> - V <sub>SS</sub> | Variations between all the different ground pins                                | -                                                                           | 50                    | mV   |

| V <sub>ESD(HBM)</sub>              | Electrostatic discharge voltage (human body model)                              | see Section 5.3.12: Absolute<br>maximum ratings (electrical<br>sensitivity) |                       |      |

**Table 7. Voltage characteristics**

38/121 DocID14610 Rev 9

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

<sup>2.</sup> V<sub>IN</sub> maximum must always be respected. Refer to *Table 8: Current characteristics* for the maximum allowed injected current values.

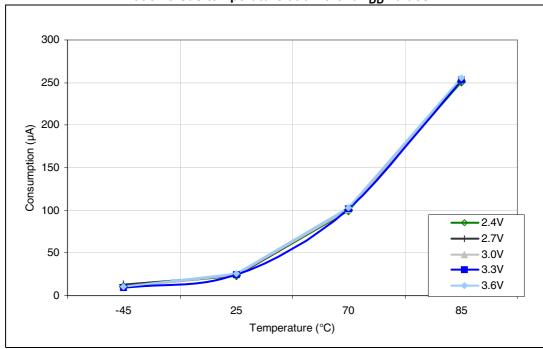

Figure 15. Typical current consumption in Stop mode with regulator in low-power mode versus temperature at different  $V_{DD}$  values

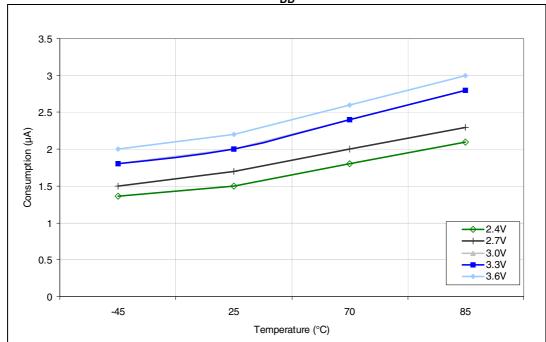

Figure 16. Typical current consumption in Standby mode versus temperature at different  $V_{\rm DD}$  values

μA/MHz **Peripherals** APB2-Bridge 4.17 **GPIOA** 8.47 **GPIOB** 8.47 **GPIOC** 6.53 **GPIOD** 8.47 **GPIOE** 6.53 APB2 (up to 36 MHz) **GPIOF** 6.53 **GPIOG** 6.11 SPI1 4.72 USART1 12.50 TIM1 22.92 TIM8 22.92 ADC1<sup>(5)(6)</sup> 17.32

Table 20. Peripheral current consumption<sup>(1)</sup> (continued)

- 1.  $f_{HCLK}$  = 36 MHz,  $f_{APB1}$  =  $f_{HCLK/2}$ ,  $f_{APB2}$  =  $f_{HCLK}$ , default prescaler value for each peripheral.

- 2. The BusMatrix is automatically active when at least one master peripheral is ON.

- 3. When the I2S is enabled, a current consumption of 0.02 mA must be added.

- 4. When DAC\_OUT1 or DAC\_OUT2 is enabled, a current consumption of 0.36 mA must be added.

- 5. Specific conditions for ADC:  $f_{HCLK}$  = 28 MHz,  $f_{APB1}$  =  $f_{HCLK/2}$ ,  $f_{APB2}$  =  $f_{HCLK}$ ,  $f_{ADCCLK}$  =  $f_{APB2}$ /2. When ADON bit in the ADC\_CR2 register is set to 1, the current consumption is equal to 0.54 mA.

- 6. When the ADC is enabled, a current consumption of 0.08 mA must be added.

#### 5.3.6 External clock source characteristics

## High-speed external user clock generated from an external source

The characteristics given in *Table 21* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 10*.

Table 21. High-speed external user clock characteristics

| Symbol                                                               | Parameter                                           | Conditions | Min                | Тур | Max                | Unit |

|----------------------------------------------------------------------|-----------------------------------------------------|------------|--------------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                                                 | User external clock source frequency <sup>(1)</sup> |            | 1                  | 8   | 25                 | MHz  |

| V <sub>HSEH</sub>                                                    | OSC_IN input pin high level voltage                 |            | 0.7V <sub>DD</sub> | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                                                    | OSC_IN input pin low level voltage                  | -          | V <sub>SS</sub>    | ı   | 0.3V <sub>DD</sub> | V    |

| $\begin{matrix} t_{w(\text{HSE})} \\ t_{w(\text{HSE})} \end{matrix}$ | OSC_IN high or low time <sup>(1)</sup>              |            | 5                  | ı   | -                  | ns   |

| t <sub>r(HSE)</sub>                                                  | OSC_IN rise or fall time <sup>(1)</sup>             |            | -                  | -   | 20                 | 113  |

Note:

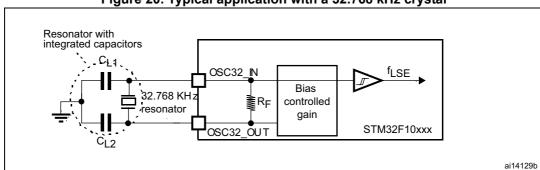

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ .

Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

Caution:

To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

**Example:** if you choose a resonator with a load capacitance of  $C_L = 6$  pF, and  $C_{stray} = 2$  pF, then  $C_{L1} = C_{L2} = 8$  pF.

Figure 20. Typical application with a 32.768 kHz crystal

#### 5.3.7 Internal clock source characteristics

The parameters given in *Table 25* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 10*.

#### High-speed internal (HSI) RC oscillator

Table 25. HSI oscillator characteristics<sup>(1)</sup>

| Symbol                              | Parameter                        | Conditions                            |                                              | Min  | Тур | Max              | Unit |

|-------------------------------------|----------------------------------|---------------------------------------|----------------------------------------------|------|-----|------------------|------|

| f <sub>HSI</sub>                    | Frequency                        | -                                     |                                              | -    | 8   | -                | MHz  |

| DuCy <sub>(HSI)</sub>               | Duty cycle                       | -                                     |                                              | 45   | -   | 55               | %    |

|                                     |                                  | User-trimmed register <sup>(2)</sup>  | d with the RCC_CR                            | -    | -   | 1 <sup>(3)</sup> | %    |

|                                     | Accuracy of the HSI oscillator   | Factory-<br>calibrated <sup>(4)</sup> | $T_A = -40 \text{ to } 105 ^{\circ}\text{C}$ | -2   | -   | 2.5              | %    |

| ACC <sub>HSI</sub>                  |                                  |                                       | $T_A = -10 \text{ to } 85 ^{\circ}\text{C}$  | -1.5 | -   | 2.2              | %    |

|                                     |                                  |                                       | T <sub>A</sub> = 0 to 70 °C                  | -1.3 | -   | 2                | %    |

|                                     |                                  |                                       | T <sub>A</sub> = 25 °C                       | -1.1 | -   | 1.8              | %    |

| t <sub>su(HSI)</sub> <sup>(4)</sup> | HSI oscillator startup time      | -                                     |                                              | 1    | -   | 2                | μs   |

| I <sub>DD(HSI)</sub> <sup>(4)</sup> | HSI oscillator power consumption | -                                     |                                              | -    | 80  | 100              | μΑ   |

<sup>1.</sup>  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 85 °C unless otherwise specified.

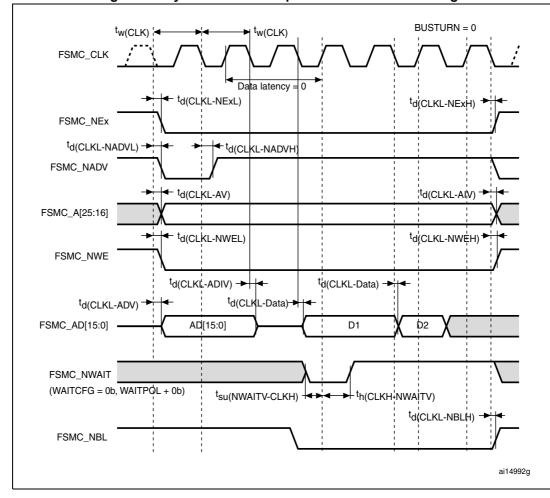

Figure 26. Synchronous multiplexed PSRAM write timings

Table 38. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup> (continued)

| Symbol                      | Parameter                            | Min | Max | Unit |

|-----------------------------|--------------------------------------|-----|-----|------|

| t <sub>h(CLKH-NWAITV)</sub> | FSMC_NWAIT valid after FSMC_CLK high | 2   | -   | ns   |

| t <sub>d(CLKL-NBLH)</sub>   | FSMC_CLK low to FSMC_NBL high        | 1   | -   | ns   |

<sup>1.</sup>  $C_L = 15 pF$ .

## PC Card/CompactFlash controller waveforms and timings

*Figure 29* through *Figure 34* represent synchronous waveforms and *Table 39* provides the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x04;

- COM.FSMC WaitSetupTime = 0x07;

- COM.FSMC\_HoldSetupTime = 0x04;

- COM.FSMC\_HiZSetupTime = 0x00;

- ATT.FSMC SetupTime = 0x04;

- ATT.FSMC\_WaitSetupTime = 0x07;

- ATT.FSMC\_HoldSetupTime = 0x04;

- ATT.FSMC HiZSetupTime = 0x00;

- IO.FSMC\_SetupTime = 0x04;

- IO.FSMC WaitSetupTime = 0x07;

- IO.FSMC HoldSetupTime = 0x04;

- IO.FSMC\_HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

<sup>2.</sup> Guaranteed by characterization results, not tested in production.

## Functional EMS (Electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports), the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- **Electrostatic discharge (ESD)** (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 41*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                     | Level/Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{DD} = 3.3$ V, LQFP144,<br>$T_A = +25$ °C, $f_{HCLK} = 36$ MHz<br>conforms to IEC 61000-4-2 | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{DD} = 3.3$ V, LQFP144,<br>$T_A = +25$ °C, $f_{HCLK} = 36$ MHz<br>conforms to IEC 61000-4-4 | 4A          |

**Table 41. EMS characteristics**

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and pre qualification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second. To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

## 5.3.14 I/O port characteristics

## General input/output characteristics

Unless otherwise specified, the parameters given in *Table 46* are derived from tests performed under the conditions summarized in *Table 10*. All I/Os are CMOS and TTL compliant.

Table 46. I/O static characteristics

| Symbol           | Parameter                                                           | Conditions                                                           | Min                               | Тур | Max                               | Unit |

|------------------|---------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------|-----|-----------------------------------|------|

| $V_{IL}$         | Standard IO input low level voltage                                 |                                                                      | -0.3                              |     | 0.28*(V <sub>DD</sub> -2 V)+0.8 V | V    |

|                  | IO FT <sup>(1)</sup> input low level voltage                        | -                                                                    | -0.3                              |     | 0.32*(V <sub>DD</sub> -2V)+0.75 V | ٧    |

|                  | Standard IO input high level voltage                                |                                                                      | 0.41*(V <sub>DD</sub> -2 V)+1.3 V |     | V <sub>DD</sub> +0.3              | ٧    |

| $V_{IH}$         | IO FT <sup>(1)</sup> input high level                               | V <sub>DD</sub> > 2 V                                                | 0.42*// 2.1/)+4.1/                |     | 5.5                               | V    |

|                  | voltage                                                             | 114711/00-2111                                                       |                                   |     | 5.2                               | V    |

| $V_{hys}$        | Standard IO Schmitt<br>trigger voltage<br>hysteresis <sup>(2)</sup> | -                                                                    | 200                               |     | -                                 | mV   |

| ,0               | IO FT Schmitt trigger voltage hysteresis <sup>(2)</sup>             |                                                                      | 5% V <sub>DD</sub> <sup>(3)</sup> |     | -                                 | mV   |

|                  | Input leakage current <sup>(4)</sup>                                | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub><br>Standard I/Os | -                                 |     | ±1                                |      |

| l <sub>lkg</sub> | input leakage current V                                             | V <sub>IN</sub> = 5 V<br>I/O FT                                      | -                                 |     | 3                                 | μA   |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>                     | $V_{IN} = V_{SS}$                                                    | 30                                | 40  | 50                                | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup>                   | $V_{IN} = V_{DD}$                                                    | 30                                | 40  | 50                                | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                                 | -                                                                    | -                                 | 5   | -                                 | pF   |

FT = Five-volt tolerant. In order to sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 39* and *Figure 40* for standard I/Os, and in *Figure 41* and *Figure 42* for 5 V tolerant I/Os.

82/121 DocID14610 Rev 9

<sup>2.</sup> Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results, not tested in production.

<sup>3.</sup> With a minimum of 100 mV.

<sup>4.</sup> Leakage could be higher than maximum value if negative current is injected on adjacent pins.

<sup>5.</sup> Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimum (~10% order).

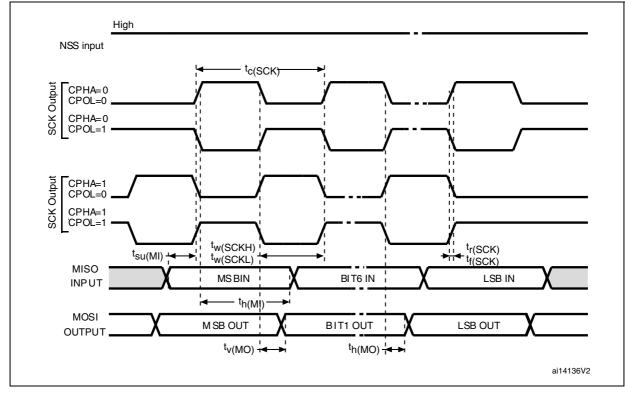

**Table 54. SPI characteristics**

| Symbol                                               | Parameter                        | Conditions                                            | Min                | Max                | Unit  |

|------------------------------------------------------|----------------------------------|-------------------------------------------------------|--------------------|--------------------|-------|

| f <sub>SCK</sub>                                     | CDI alogic fraguency             | Master mode                                           | -                  | 18                 | MHz   |

| 1/t <sub>c(SCK)</sub>                                | SPI clock frequency              | Slave mode                                            | -                  | 18                 | IVITZ |

| t <sub>r(SCK)</sub>                                  | SPI clock rise and fall time     | Capacitive load: C = 30 pF                            | -                  | 8                  | ns    |

| DuCy(SCK)                                            | SPI slave input clock duty cycle | Slave mode                                            | 30                 | 70                 | %     |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                  | NSS setup time                   | Slave mode                                            | 4t <sub>PCLK</sub> | -                  |       |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                   | NSS hold time                    | Slave mode                                            | 2t <sub>PCLK</sub> | -                  |       |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1) | SCK high and low time            | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | 50                 | 60                 |       |

| t <sub>su(MI)</sub> (1)                              | Data input setup time            | Master mode                                           | 5                  | -                  |       |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)   |                                  | Slave mode                                            | 5                  | -                  |       |

| t <sub>h(MI)</sub> (1)                               | Data input hold time             | Master mode                                           | 5                  | -                  |       |

| t <sub>h(SI)</sub> <sup>(1)</sup>                    | Data iriput riolu tirrie         | Slave mode                                            | 4                  | -                  | ns    |

| t <sub>a(SO)</sub> <sup>(1)(2)</sup>                 | Data output access time          | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0                  | 3t <sub>PCLK</sub> |       |

| t <sub>dis(SO)</sub> (1)(3)                          | Data output disable time         | Slave mode                                            | 2                  | 10                 |       |

| t <sub>v(SO)</sub> (1)(1)                            | Data output valid time           | Slave mode (after enable edge)                        | -                  | 25                 |       |

| t <sub>v(MO)</sub> <sup>(1)(1)</sup>                 | Data output valid time           | Master mode (after enable edge)                       | -                  | 5                  |       |

| t <sub>h(SO)</sub> <sup>(1)</sup>                    | Data output hold time            | Slave mode (after enable edge)                        | 15                 | -                  |       |

| t <sub>h(MO)</sub> <sup>(1)</sup>                    | Data output noid time            | Master mode (after enable edge)                       | 2                  | -                  |       |

<sup>1.</sup> Guaranteed by characterization results not tested in production.

<sup>2.</sup> Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

<sup>3.</sup> Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

Figure 48. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

#### 5.3.18 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 55* are values derived from tests performed under ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 10*.

Note: It is recommended to perform a calibration after each power-up.

## **Device marking for LQFP144**

The following figure gives an example of topside marking and pin 1 position identifier location.

Product identification(1)

Revision code

R

STM32F101ZCTL

Date code

Y W W

MSv37277V1

Figure 56. LQFP144 marking (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics - All rights reserved