# E·XFL

### NXP USA Inc. - KMSC7118VF1200 Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                               |

|-------------------------|------------------------------------------------------------------------|

| Туре                    | Fixed Point                                                            |

| Interface               | Host Interface, I <sup>2</sup> C, UART                                 |

| Clock Rate              | 300MHz                                                                 |

| Non-Volatile Memory     | ROM (8kB)                                                              |

| On-Chip RAM             | 464kB                                                                  |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.20V                                                                  |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                     |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 400-LFBGA                                                              |

| Supplier Device Package | 400-LFBGA (17x17)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmsc7118vf1200 |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1 | Pin A  | ssignments                           |

|---|--------|--------------------------------------|

|   | 1.1    | MAP-BGA Ball Layout Diagrams         |

|   | 1.2    | Signal List By Ball Location         |

| 2 | Electi | rical Characteristics                |

|   | 2.1    | Maximum Ratings                      |

|   | 2.2    | Recommended Operating Conditions     |

|   | 2.3    | Thermal Characteristics              |

|   | 2.4    | DC Electrical Characteristics        |

|   | 2.5    | AC Timings                           |

| 3 | Hard   | ware Design Considerations           |

|   | 3.1    | Thermal Design Considerations        |

|   | 3.2    | Power Supply Design Considerations40 |

|   | 3.3    | Estimated Power Usage Calculations47 |

|   | 3.4    | Reset and Boot                       |

|   | 3.5    | DDR Memory System Guidelines         |

| 4 | Orde   | ring Information                     |

| 5 | Packa  | age Information                      |

| 6 | Produ  | uct Documentation                    |

| 7 | Revis  | ion History                          |

|   |        | Figures                              |

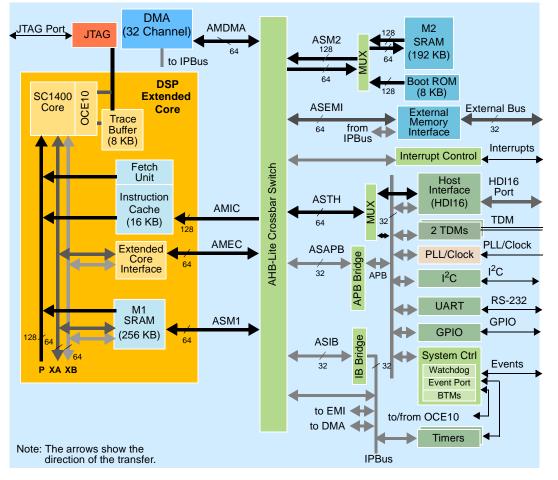

| Figure 1. | MSC7118 Block Diagram                             |

|-----------|---------------------------------------------------|

| Figure 2. | MSC7118 Molded Array Process-Ball Grid Array      |

|           | (MAP-BGA), Top View 4                             |

| Figure 3. | MSC7118 Molded Array Process-Ball Grid Array      |

|           | (MAP-BGA), Bottom View 5                          |

| Figure 4. | Timing Diagram for a Reset Configuration Write 25 |

| Figure 5. | DDR DRAM Input Timing Diagram                     |

|           |                                                   |

| Figure 6.  | DDR DRAM Output Timing Diagram                 |

|------------|------------------------------------------------|

| Figure 7.  | DDR DRAM AC Test Load                          |

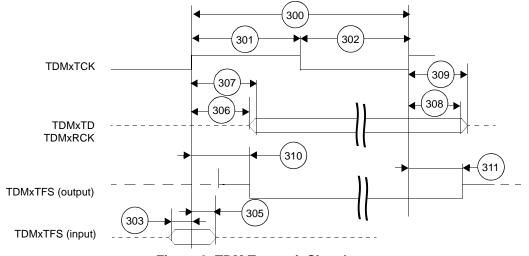

| Figure 8.  | TDM Receive Signals                            |

| Figure 9.  | TDM Transmit Signals                           |

| Figure 10. | Read Timing Diagram, Single Data Strobe        |

| Figure 11. | Read Timing Diagram, Double Data Strobe        |

| Figure 12. | Write Timing Diagram, Single Data Strobe       |

| Figure 13. | Write Timing Diagram, Double Data Strobe       |

| Figure 14. | Host DMA Read Timing Diagram, HPCR[OAD] = 033  |

| Figure 15. | Host DMA Write Timing Diagram, HPCR[OAD] = 033 |

| Figure 16. | I2C Timing Diagram                             |

| Figure 17. | UART Input Timing                              |

| Figure 18. | UART Output Timing                             |

| Figure 19. | EE Pin Timing                                  |

| Figure 20. | EVNT Pin Timing                                |

| Figure 21. | GPI/GPO Pin Timing                             |

| Figure 22. | Test Clock Input Timing Diagram 37             |

| Figure 23. | Boundary Scan (JTAG) Timing Diagram            |

| Figure 24. | Test Access Port Timing Diagram                |

| Figure 25. | TRST Timing Diagram                            |

| Figure 26. | Voltage Sequencing Case 1 41                   |

| Figure 27. | Voltage Sequencing Case 2 42                   |

| Figure 28. | Voltage Sequencing Case 3 43                   |

| Figure 29. | Voltage Sequencing Case 4 44                   |

| Figure 30. | Voltage Sequencing Case 5 45                   |

| Figure 31. | PLL Power Supply Filter Circuits               |

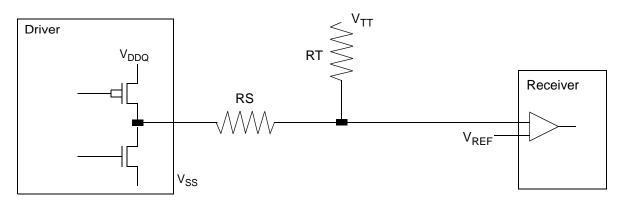

| Figure 32. | SSTL Termination Techniques 52                 |

| Figure 33. | SSTL Power Value                               |

Figure 1. MSC7118 Block Diagram

ssignments

|        | Signal Names |                          |                      |             |                     |           |  |

|--------|--------------|--------------------------|----------------------|-------------|---------------------|-----------|--|

| Number |              | Software Controlled      |                      |             | Hardware Controlled |           |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary             | Alternate |  |

| D10    |              |                          | V                    | DDM         |                     | ·         |  |

| D11    |              |                          | V                    | DDIO        |                     |           |  |

| D12    |              |                          |                      | DDIO        |                     |           |  |

| D13    |              |                          | V                    | DDIO        |                     |           |  |

| D14    |              |                          | V                    | DDIO        |                     |           |  |

| D15    |              |                          | V                    | DDIO        |                     |           |  |

| D16    |              |                          | V                    | DDIO        |                     |           |  |

| D17    |              |                          | V                    | DDC         |                     |           |  |

| D18    |              |                          |                      | NC          |                     |           |  |

| D19    |              |                          |                      | NC          |                     |           |  |

| D20    |              |                          |                      | NC          |                     |           |  |

| E1     |              |                          | G                    | ND          |                     |           |  |

| E2     |              |                          | [                    | 026         |                     |           |  |

| E3     |              |                          | [                    | 031         |                     |           |  |

| E4     |              |                          | V                    | DDM         |                     |           |  |

| E5     |              |                          | V                    | DDM         |                     |           |  |

| E6     |              |                          | V                    | DDC         |                     |           |  |

| E7     |              |                          |                      | DDC         |                     |           |  |

| E8     |              |                          |                      | DDC         |                     |           |  |

| E9     |              |                          |                      | DDC         |                     |           |  |

| E10    |              |                          |                      | DDM         |                     |           |  |

| E11    |              |                          | V                    | DDIO        |                     |           |  |

| E12    |              |                          |                      | DDIO        |                     |           |  |

| E13    |              |                          | V                    | DDIO        |                     |           |  |

| E14    |              |                          |                      | DDIO        |                     |           |  |

| E15    |              |                          | V                    | DDIO        |                     |           |  |

| E16    |              |                          |                      | DDC         |                     |           |  |

| E17    |              |                          |                      | DDC         |                     |           |  |

| E18    |              | NC                       |                      |             |                     |           |  |

| E19    |              | NC                       |                      |             |                     |           |  |

| E20    |              | NC                       |                      |             |                     |           |  |

| F1     |              |                          | V                    | DDM         |                     |           |  |

| F2     | D15          |                          |                      |             |                     |           |  |

| F3     | D29          |                          |                      |             |                     |           |  |

| F4     |              |                          | V                    | DDC         |                     |           |  |

| F5     |              |                          |                      | DDC         |                     |           |  |

## Table 1. MSC7118 Signals by Ball Designator (continued)

|        | Signal Names      |                          |                      |             |                     |           |  |

|--------|-------------------|--------------------------|----------------------|-------------|---------------------|-----------|--|

| Number |                   | Software Controlled      |                      |             | Hardware Controlled |           |  |

|        | End of Reset      | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary             | Alternate |  |

| F6     |                   |                          | V <sub>C</sub>       | DC          |                     |           |  |

| F7     |                   |                          | GI                   | ND          |                     |           |  |

| F8     |                   |                          | GI                   | ND          |                     |           |  |

| F9     |                   |                          | GI                   | ND          |                     |           |  |

| F10    |                   |                          | VD                   | DM          |                     |           |  |

| F11    |                   |                          | V <sub>D</sub>       | DM          |                     |           |  |

| F12    |                   |                          | GI                   | ND          |                     |           |  |

| F13    |                   |                          | GI                   | ND          |                     |           |  |

| F14    |                   |                          | GI                   | ND          |                     |           |  |

| F15    |                   |                          | V <sub>D</sub>       | DIO         |                     |           |  |

| F16    |                   |                          | V <sub>D</sub>       | DC          |                     |           |  |

| F17    |                   |                          |                      | DC          |                     |           |  |

| F18    |                   |                          |                      | С           |                     |           |  |

| F19    |                   |                          | N                    | С           |                     |           |  |

| F20    |                   |                          | N                    | С           |                     |           |  |

| G1     |                   | GND                      |                      |             |                     |           |  |

| G2     |                   | D13                      |                      |             |                     |           |  |

| G3     |                   |                          | GI                   | ND          |                     |           |  |

| G4     |                   |                          | VD                   | DM          |                     |           |  |

| G5     |                   |                          |                      | DM          |                     |           |  |

| G6     |                   | GND                      |                      |             |                     |           |  |

| G7     |                   | GND                      |                      |             |                     |           |  |

| G8     |                   | GND                      |                      |             |                     |           |  |

| G9     |                   | GND                      |                      |             |                     |           |  |

| G10    |                   | GND                      |                      |             |                     |           |  |

| G11    |                   | GND                      |                      |             |                     |           |  |

| G12    |                   |                          | GI                   | ND          |                     |           |  |

| G13    | 1                 |                          | GI                   | ND          |                     |           |  |

| G14    | 1                 | GND                      |                      |             |                     |           |  |

| G15    |                   | V <sub>DDIO</sub>        |                      |             |                     |           |  |

| G16    | V <sub>DDIO</sub> |                          |                      |             |                     |           |  |

| G17    | 1                 |                          |                      | IDC         |                     |           |  |

| G18    | 1                 | NC                       |                      |             |                     |           |  |

| G19    | NC                |                          |                      |             |                     |           |  |

| G20    | NC                |                          |                      |             |                     |           |  |

| H1     | D14               |                          |                      |             |                     |           |  |

## Table 1. MSC7118 Signals by Ball Designator (continued)

ssignments

|        | Signal Names |                          |                      |             |                     |           |  |  |

|--------|--------------|--------------------------|----------------------|-------------|---------------------|-----------|--|--|

| Number |              | Software Controlled      |                      |             | Hardware Controlled |           |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary             | Alternate |  |  |

| V18    | GPI          | A24                      | IRQ24                | GPOA24      | TX_                 | EN        |  |  |

| V19    |              | rese                     | rved                 |             | CF                  | RS        |  |  |

| V20    |              | TDI                      |                      |             |                     |           |  |  |

| W1     |              |                          | C                    | SND         |                     |           |  |  |

| W2     |              |                          | V                    | DDM         |                     |           |  |  |

| W3     |              |                          | ,                    | A12         |                     |           |  |  |

| W4     |              |                          |                      | A8          |                     |           |  |  |

| W5     |              |                          |                      | A7          |                     |           |  |  |

| W6     |              |                          |                      | A6          |                     |           |  |  |

| W7     |              |                          |                      | A3          |                     |           |  |  |

| W8     |              |                          |                      | NC          |                     |           |  |  |

| W9     | GPI          | A17                      | IRQ13                | GPOA17      | EVNT1               | CLKO      |  |  |

| W10    | BM0          | GPI                      | C14                  | GPOC14      | EVI                 | NT2       |  |  |

| W11    | GPI          | A10 IRQ5 GPOA10 TORFS    |                      |             |                     | RFS       |  |  |

| W12    | GP           | IA7                      | IRQ7                 | GPOA7       | тот                 | TFS       |  |  |

| W13    | GP           | IA3                      | IRQ8                 | GPOA3       | T1I                 | RD        |  |  |

| W14    | GP           | IA1                      | IRQ10                | GPOA1       | T17                 | TFS       |  |  |

| W15    |              | GPID4                    |                      | GPOD4       | TXD2                | reserved  |  |  |

| W16    | GPI          | A27                      | IRQ18                | GPOA27      | RXD3                | reserved  |  |  |

| W17    | GPI          | A19                      | IRQ19                | GPOA19      | ТХ                  | D1        |  |  |

| W18    | GPI          | A23                      | IRQ23                | GPOA23      | TXCLK or            | REFCLK    |  |  |

| W19    | GPI          | A26                      | IRQ26                | GPOA26      | RX_                 | _ER       |  |  |

| W20    | H8BIT        |                          | reserved             |             | M                   | C         |  |  |

| Y1     |              |                          | V                    | DDM         |                     |           |  |  |

| Y2     |              |                          | C                    | SND         |                     |           |  |  |

| Y3     |              |                          |                      | A9          |                     |           |  |  |

| Y4     |              |                          |                      | A1          |                     |           |  |  |

| Y5     |              |                          |                      | A0          |                     |           |  |  |

| Y6     |              |                          |                      | A4          |                     |           |  |  |

| Y7     |              |                          | E                    | BA1         |                     |           |  |  |

| Y8     | rese         | rved                     | NMI                  |             | reserved            |           |  |  |

| Y9     | BM1          | GPI                      | C15                  | GPOC15      | EVM                 | NT3       |  |  |

| Y10    | GPI          | A11                      | IRQ4                 | GPOA11      | TOR                 | СK        |  |  |

| Y11    |              | GPIA9                    |                      | GPOA9       | TO                  | RD        |  |  |

| Y12    |              | GPIA6 GPOA6 T0TD         |                      |             |                     |           |  |  |

| Y13    | GP           | IA5                      | IRQ0                 | GPOA5       | T1R                 | RCK       |  |  |

Table 1. MSC7118 Signals by Ball Designator (continued)

### rical Characteristics

Table 2 describes the maximum electrical ratings for the MSC7118.

| Table 2 | Absolute | Maximum | Ratings |

|---------|----------|---------|---------|

|---------|----------|---------|---------|

| Rating                        | Symbol             | Value              | Unit |

|-------------------------------|--------------------|--------------------|------|

| Core supply voltage           | V <sub>DDC</sub>   | 1.5                | V    |

| Memory supply voltage         | V <sub>DDM</sub>   | 4.0                | V    |

| PLL supply voltage            | V <sub>DDPLL</sub> | 1.5                | V    |

| I/O supply voltage            | V <sub>DDIO</sub>  | -0.2 to 4.0        | V    |

| Input voltage                 | V <sub>IN</sub>    | (GND – 0.2) to 4.0 | V    |

| Reference voltage             | V <sub>REF</sub>   | 4.0                | V    |

| Maximum operating temperature | TJ                 | 105                | °C   |

| Minimum operating temperature | T <sub>A</sub>     | -40                | °C   |

| Storage temperature range     | T <sub>STG</sub>   | -55 to +150        | °C   |

Notes: 1. Functional operating conditions are given in Table 3.

2. Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the listed limits may affect device reliability or cause permanent damage.

3. Section 3.1, Thermal Design Considerations includes a formula for computing the chip junction temperature (T<sub>J</sub>).

## 2.2 Recommended Operating Conditions

Table 3 lists recommended operating conditions. Proper device operation outside of these conditions is not guaranteed.

### **Table 3. Recommended Operating Conditions**

| Rating                      | Symbol                           | Value                        | Unit     |

|-----------------------------|----------------------------------|------------------------------|----------|

| Core supply voltage         | V <sub>DDC</sub>                 | 1.14 to 1.26                 | V        |

| Memory supply voltage       | V <sub>DDM</sub>                 | 2.38 to 2.63                 | V        |

| PLL supply voltage          | V <sub>DDPLL</sub>               | 1.14 to 1.26                 | V        |

| I/O supply voltage          | V <sub>DDIO</sub>                | 3.14 to 3.47                 | V        |

| Reference voltage           | V <sub>REF</sub>                 | 1.19 to 1.31                 | V        |

| Operating temperature range | T <sub>J</sub><br>T <sub>A</sub> | maximum: 105<br>minimum: –40 | 0°<br>0° |

## 2.5 AC Timings

This section presents timing diagrams and specifications for individual signals and parallel I/O outputs and inputs. All AC timings are based on a 30 pF load, except where noted otherwise, and a 50  $\Omega$  transmission line. For any additional pF, use the following equations to compute the delay:

- Standard interface:  $2.45 + (0.054 \times C_{load})$  ns

- DDR interface:  $1.6 + (0.002 \times C_{load})$  ns

## 2.5.1 Clock and Timing Signals

The following tables describe clock signal characteristics. **Table 6** shows the maximum frequency values for internal (core, reference, and peripherals) and external (CLKO) clocks. You must ensure that maximum frequency values are not exceeded (see **Section 2.5.2** for the allowable ranges when using the PLL).

### **Table 6. Maximum Frequencies**

| Characteristic                         | Maximum in MHz |  |  |

|----------------------------------------|----------------|--|--|

| Core clock frequency (CLOCK)           | 300            |  |  |

| External output clock frequency (CLKO) | 75             |  |  |

| Memory clock frequency (CK, CK)        | 150            |  |  |

| TDM clock frequency (TxRCK, TxTCK)     | 50             |  |  |

### Table 7. Clock Frequencies in MHz

| Characteristic                                                         | Symbol             | Min | Max |

|------------------------------------------------------------------------|--------------------|-----|-----|

| CLKIN frequency                                                        | F <sub>CLKIN</sub> | 10  | 100 |

| CLOCK frequency                                                        | F <sub>CORE</sub>  | —   | 300 |

| CK, CK frequency                                                       | F <sub>CK</sub>    | —   | 150 |

| TDMxRCK, TDMxTCK frequency                                             | F <sub>TDMCK</sub> | —   | 50  |

| CLKO frequency                                                         | F <sub>СКО</sub>   | —   | 75  |

| AHB/IPBus/APB clock frequency                                          | F <sub>BCK</sub>   | —   | 150 |

| Note: The rise and fall time of external clocks should be 5 ns maximum |                    |     |     |

### **Table 8. System Clock Parameters**

| Characteristic                        | Min | Мах  | Unit |

|---------------------------------------|-----|------|------|

| CLKIN frequency                       | 10  | 100  | MHz  |

| CLKIN slope                           | —   | 5    | ns   |

| CLKIN frequency jitter (peak-to-peak) | —   | 1000 | ps   |

| CLKO frequency jitter (peak-to-peak)  | —   | 150  | ps   |

rical Characteristics

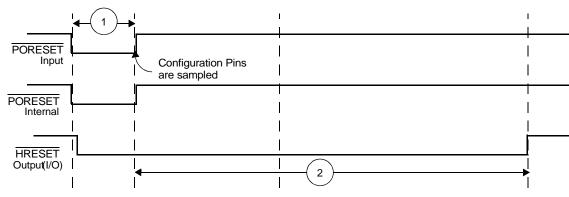

## 2.5.3 Reset Timing

The MSC7118 device has several inputs to the reset logic. All MSC7118 reset sources are fed into the reset controller, which takes different actions depending on the source of the reset. The reset status register indicates the most recent sources to cause a reset. **Table 14** describes the reset sources.

| Name                                       | Direction     | Description                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset<br>(PORESET)                | Input         | Initiates the power-on reset flow that resets the MSC7118 and configures various attributes of the MSC7118. On PORESET, the entire MSC7118 device is reset. SPLL and DLL states are reset, HRESET is driven, the SC1400 extended core is reset, and system configuration is sampled. The system is configured only when PORESET is asserted. |

| External Hard<br>reset (HRESET)            | Input/ Output | Initiates the hard reset flow that configures various attributes of the MSC7118. While HRESET is asserted, HRESET is an open-drain output. Upon hard reset, HRESET is driven and the SC1400 extended core is reset.                                                                                                                          |

| Software<br>watchdog reset                 | Internal      | When the MSC7118 watchdog count reaches zero, a software watchdog reset is signalled. The enabled software watchdog event then generates an internal hard reset sequence.                                                                                                                                                                    |

| Bus monitor reset                          | Internal      | When the MSC7118 bus monitor count reaches zero, a bus monitor hard reset is asserted. The enabled bus monitor event then generates an internal hard reset sequence.                                                                                                                                                                         |

| JTAG EXTEST,<br>CLAMP, or<br>HIGHZ command | Internal      | When a Test Access Port (TAP) executes an EXTEST, CLAMP, or HIGHZ command, the TAP logic asserts an internal reset signal that generates an internal soft reset sequence.                                                                                                                                                                    |

Table 15 summarizes the reset actions that occur as a result of the different reset sources.

|                                                                           | Po <u>wer-On Re</u> set<br>(PORESET) | H <u>ard Rese</u> t<br>(HRESET)                                  | S <u>oft Rese</u> t<br>(SRESET)             |  |

|---------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------|---------------------------------------------|--|

| Reset Action/Reset Source                                                 | External only                        | External or<br>Internal (Software<br>Watchdog or Bus<br>Monitor) | JTAG Command:<br>EXTEST, CLAMP,<br>or HIGHZ |  |

| Configuration pins sampled (refer to <b>Section 2.5.3.1</b> for details). | Yes                                  | No                                                               | No                                          |  |

| PLL and clock synthesis states Reset                                      | Yes                                  | No                                                               | No                                          |  |

| HRESET Driven                                                             | Yes                                  | Yes                                                              | No                                          |  |

| Software watchdog and bus time-out monitor registers                      | Yes                                  | Yes                                                              | Yes                                         |  |

| Clock synthesis modules (STOPCTRL, HLTREQ, and HLTACK) reset              | Yes                                  | Yes                                                              | Yes                                         |  |

| Extended core reset                                                       | Yes                                  | Yes                                                              | Yes                                         |  |

| Peripheral modules reset                                                  | Yes                                  | Yes                                                              | Yes                                         |  |

## 2.5.3.1 Power-On Reset (PORESET) Pin

Asserting  $\overrightarrow{\text{PORESET}}$  initiates the power-on reset flow.  $\overrightarrow{\text{PORESET}}$  must be asserted externally for at least 16 CLKIN cycles after external power to the MSC7118 reaches at least 2/3 V<sub>DD</sub>.

The MSC7118 has two mechanisms for writing the reset configuration:

- From a host through the host interface (HDI16)

- From memory through the I<sup>2</sup>C interface

Five signal levels (see **Chapter 1** for signal description details) are sampled on **PORESET** deassertion to define the boot and operating conditions:

- BM[0–1]

- SWTE

- H8BIT

- HDSP

## 2.5.3.3 Reset Timing Tables

Table 16 and Figure 4 describe the reset timing for a reset configuration write.

### Table 16. Timing for a Reset Configuration Write

| No.   | Characteristics                                       | Expression             | Unit   |

|-------|-------------------------------------------------------|------------------------|--------|

| 1     | Required external PORESET duration minimum            | 16/F <sub>CLKIN</sub>  | clocks |

| 2     | Delay from PORESET deassertion to HRESET deassertion  | 521/F <sub>CLKIN</sub> | clocks |

| Note: | Timings are not tested, but are guaranteed by design. |                        |        |

Figure 4. Timing Diagram for a Reset Configuration Write

#### **Electrical Characteristics**

Figure 9. TDM Transmit Signals

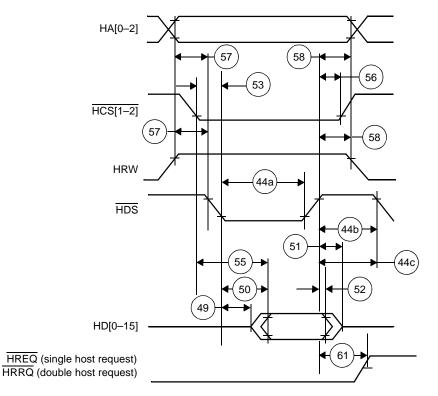

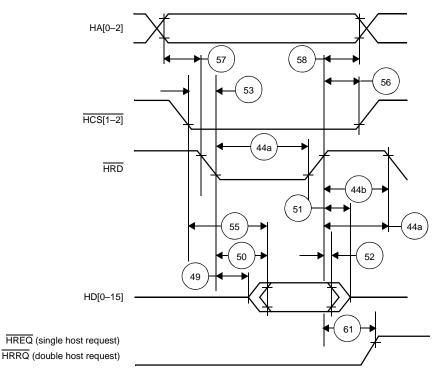

Figure 10 and Figure 11 show HDI16 read signal timing. Figure 12 and Figure 13 show HDI16 write signal timing.

Figure 10. Read Timing Diagram, Single Data Strobe

Figure 11. Read Timing Diagram, Double Data Strobe

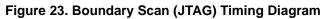

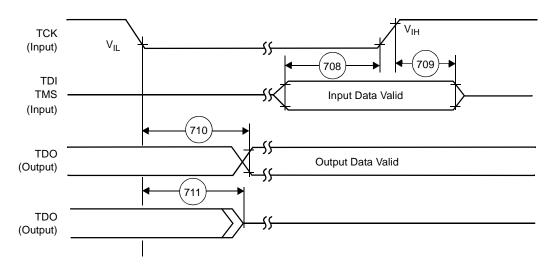

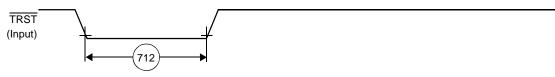

## 2.5.12 JTAG Signals

| No.   | Characteristics                                                                                                                                                                                                                   | All freq | 11-11 |      |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|------|--|

| 110.  | Characteristics                                                                                                                                                                                                                   | Min      | Max   | Unit |  |

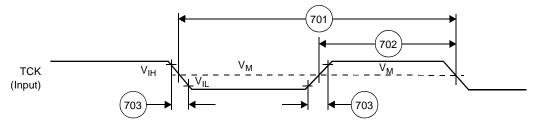

| 700   | TCK frequency of operation $(1/(T_C \times 3))$<br><b>Note:</b> $T_C = 1/CLOCK$ which is the period of the core clock. The TCK<br>frequency must less than 1/3 of the core frequency with an absolute<br>maximum limit of 40 MHz. | 0.0      | 40.0  | MHz  |  |

| 701   | TCK cycle time                                                                                                                                                                                                                    | 25.0     | _     | ns   |  |

| 702   | TCK clock pulse width measured at $V_{M=}$ 1.6 V                                                                                                                                                                                  | 11.0     | _     | ns   |  |

| 703   | TCK rise and fall times                                                                                                                                                                                                           | 0.0      | 3.0   | ns   |  |

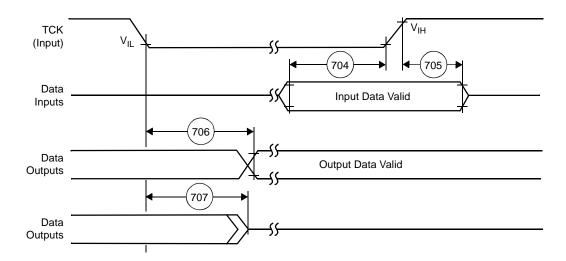

| 704   | Boundary scan input data set-up time                                                                                                                                                                                              | 5.0      | _     | ns   |  |

| 705   | Boundary scan input data hold time                                                                                                                                                                                                | 14.0     | _     | ns   |  |

| 706   | TCK low to output data valid                                                                                                                                                                                                      | 0.0      | 20.0  | ns   |  |

| 707   | TCK low to output high impedance                                                                                                                                                                                                  | 0.0      | 20.0  | ns   |  |

| 708   | TMS, TDI data set-up time                                                                                                                                                                                                         | 5.0      | _     | ns   |  |

| 709   | TMS, TDI data hold time                                                                                                                                                                                                           | 14.0     | _     | ns   |  |

| 710   | TCK low to TDO data valid                                                                                                                                                                                                         | 0.0      | 24.0  | ns   |  |

| 711   | TCK low to TDO high impedance                                                                                                                                                                                                     | 0.0      | 10.0  | ns   |  |

| 712   | TRST assert time                                                                                                                                                                                                                  | 100.0    | _     | ns   |  |

| Note: | All timings apply to OCE module data transfers as the OCE module uses the JTAG port as an interface.                                                                                                                              |          |       |      |  |

Table 27. JTAG Timing

Figure 22. Test Clock Input Timing Diagram

Figure 24. Test Access Port Timing Diagram

Figure 25. TRST Timing Diagram

NP

ware Design Considerations

### 3.3.2 Peripheral Power

Peripherals include the DDR memory controller, DMA controller, HDI16, TDM, UART, timers, GPIOs, and the I<sup>2</sup>C module. Basic power consumption by each module is assumed to be the same and is computed by using the following equation which assumes an effective load of 20 pF, core voltage swing of 1.2 V, and a switching frequency of 100 MHz. This yields:

$$P_{PERIPHERAL} = 20 \ pF \times (1.2 \ V)^2 \times 150 \ MHz \times 10^{-3} = 4.32 \ mW \ per \ peripheral$$

Eqn. 6

Multiply this value by the number of peripherals used in the application to compute the total peripheral power consumption.

## 3.3.3 External Memory Power

Estimation of power consumption by the DDR memory system is complex. It varies based on overall system signal line usage, termination and load levels, and switching rates. Because the DDR memory includes terminations external to the MSC7118 device, the 2.5 V power source provides the power for the termination, which is a static value of 16 mA per signal driven high. The dynamic power is computed, however, using a differential voltage swing of  $\pm 0.200$  V, yielding a peak-to-peak swing of 0.4 V. The equations for computing the DDR power are:

$$P_{DDRIO} = P_{STATIC} + P_{DYNAMIC} \qquad Eqn. 7$$

$$P_{STATIC} = (unused pins \times \% driven high) \times 16 mA \times 2.5 V$$

Eqn. 8

$$P_{DYNAMIC} = (pin \ activity \ value) \times 20 \ pF \times (0.4 \ V)^2 \times 300 \ MHz \times 10^{-3} \ mW$$

Eqn. 9

pin activity value = (active data lines  $\times$  % activity  $\times$  % data switching) + (active address lines  $\times$  % activity) Eqn. 10

As an example, assume the following:

unused pins = 16 (DDR uses 16-pin mode) % driven high = 50% active data lines = 16 % activity = 60% % data switching = 50% active address lines = 3

In this example, the DDR memory power consumption is:

$$P_{DDRIO} = ((16 \times 0.5) \times 16 \times 2.5) + (((16 \times 0.6 \times 0.5) + (3 \times 0.6)) \times 20 \times (0.4)^2 \times 300 \times 10^{-3}) = 326.3 \text{ mW}$$

Eqn. 11

### 3.3.4 External I/O Power

The estimation of the I/O power is similar to the computation of the peripheral power estimates. The power consumption per signal line is computed assuming a maximum load of 20 pF, a voltage swing of 3.3 V, and a switching frequency of 25 MHz, which yields:

$$P_{IO} = 20 \ pF \times (3.3 \ V)^2 \times 25 \ MHz \times 10^{-3} = 5.44 \ mW \ per I/O \ line$$

Eqn. 12

Multiply this number by the number of I/O signal lines used in the application design to compute the total I/O power.

**Note:** The signal loading depends on the board routing. For systems using a single DDR device, the load could be as low as 7 pF.

### 3.3.5 Leakage Power

The leakage power is for all power supplies combined at a specific temperature. The value is temperature dependent. The observed leakage value at room temperature is 64 mW.

## 3.3.6 Example Total Power Consumption

Using the examples in this section and assuming four peripherals and 10 I/O lines active, a total power consumption value is estimated as the following:

$$P_{TOTAL} = 324.0 + (4 \times 4.32) + 326.3 + (10 \times 5.44) + 64 = 784.98 \, mW$$

Eqn. 13

## 3.4 Reset and Boot

This section describes the recommendations for configuring the MSC7118 at reset and boot.

## 3.4.1 Reset Circuit

**HRESET** is a bidirectional signal and, if driven as an input, should be driven with an open collector or open-drain device. For an open-drain output such as **HRESET**, take care when driving many buffers that implement input bus-hold circuitry. The bus-hold currents can cause enough voltage drop across the pull-up resistor to change the logic level to low. Either a smaller value of pull-up or less current loading from the bus-hold drivers overcomes this issue. To avoid exceeding the MSC7118 output current, the pull-up value should not be too small (a 1 K $\Omega$  pull-up resistor is used in the MSC711xADS reference design).

## 3.4.2 Reset Configuration Pins

**Table 30** shows the MSC7118 reset configuration signals. These signals are sampled at the deassertion (rising edge) of PORESET. For details, refer to the Reset chapter of the *MSC711x Reference Manual*.

| Signal  | Description                        | Settings                                      |  |  |

|---------|------------------------------------|-----------------------------------------------|--|--|

| BM[3–0] | Determines boot mode.              | See Table 31 for details.                     |  |  |

| SWTE    | Determines watchdog functionality. | 0 Watchdog timer disabled.                    |  |  |

|         |                                    | 1 Watchdog timer enabled.                     |  |  |

| HDSP    | Configures HDI16 strobe polarity.  | 0 Host Data strobes active low.               |  |  |

|         |                                    | 1 Host Data strobes active high.              |  |  |

| H8BIT   | Configures HDI16 operation mode.   | 0 HDI16 port configured for 16-bit operation. |  |  |

|         |                                    | 1 HDI16 port configured for 8-bit operation.  |  |  |

#### **Table 30. Reset Configuration Signals**

Figure 33. SSTL Power Value

## 3.5.1 V<sub>REF</sub> and V<sub>TT</sub> Design Constraints

$V_{TT}$  and  $V_{REF}$  are isolated power supplies at the same voltage, with  $V_{TT}$  as a high current power source. This section outlines the voltage supply design needs and goals:

- Minimize the noise on both rails.

- V<sub>TT</sub> must track variation in the V<sub>REF</sub> DC offsets. Although they are isolated supplies, one possible solution is to use a single IC to generate both signals.

- Both references should have minimal drift over temperature and source supply.

- It is important to minimize the noise from coupling onto V<sub>REF</sub> as follows:

- Isolate V<sub>REF</sub> and shield it with a ground trace.

- Use 15–20 mm track.

- Use 20–30 mm clearance between other traces for isolating.

- Use the outer layer route when possible.

- Use distributed decoupling to localize transient currents and return path and decouple with an inductance less than 3 nH.

- Max source/sink transient currents of up to 1.8 A for a 32-bit data bus.

- Use a wide island trace on the outer layer:

- Place the island at the end of the bus.

- Decouple both ends of the bus.

- Use distributed decoupling across the island.

- Place SSTL termination resistors inside the V<sub>TT</sub> island and ensure a good, solid connection.

- Place the V<sub>TT</sub> regulator as closely as possible to the termination island.

- Reduce inductance and return path.

- Tie current sense pin at the midpoint of the island.

## 3.5.2 Decoupling

The DDR decoupling considerations are as follows:

- DDR memory requires significantly more burst current than previous SDRAMs.

- In the worst case, up to 64 drivers may be switching states.

- Pay special attention and decouple discrete ICs per manufacturer guidelines.

- Leverage V<sub>TT</sub> island topology to minimize the number of capacitors required to supply the burst current needs of the termination rail.

- See the Micron DesignLine publication entitled *Decoupling Capacitor Calculation for a DDR Memory Channel* (http://download.micron.com/pdf/pubs/designline/3Q00dll-4.pdf).

ware Design Considerations

## 3.5.3 General Routing

The general routing considerations for the DDR are as follows:

- All DDR signals must be routed next to a solid reference:

- For data, next to solid ground planes.

- For address/command, power planes if necessary.

- All DDR signals must be impedance controlled. This is system dependent, but typical values are 50-60 ohm.

- Minimize other cross-talk opportunities. As possible, maintain at least a four times the trace width spacing between all DDR signals to non-DDR signals.

- Keep the number of vias to a minimum to eliminate additional stubs and capacitance.

- Signal group routing priorities are as follows:

- DDR clocks.

- Route MVTT/MVREF.

- Data group.

- Command/address.

- Minimize data bit jitter by trace matching.

## 3.5.4 Routing Clock Distribution

The DDR clock distribution considerations are as follows:

- DDR controller supports six clock pairs:

- 2 DIMM modules.

- Up to 36 discrete chips.

- For route traces as for any other differential signals:

- Maintain proper difference pair spacing.

- Match pair traces within 25 mm.

- Match all clock traces to within 100 mm.

- Keep all clocks equally loaded in the system.

- Route clocks on inner critical layers.

## 3.5.5 Data Routing

The DDR data routing considerations are as follows:

- Route each data group (8-bits data + DQS + DM) on the same layer. Avoid switching layers within a byte group.

- Take care to match trace lengths, which is extremely important.

- To make trace matching easier, let adjacent groups be routed on alternate critical layers.

- Pin swap bits within a byte group to facilitate routing (discrete case).

- Tight trace matching is recommended within the DDR data group. Keep each 8-bit datum and its DM signal within ± 25 mm of its respective strobe.

- Minimize lengths across the entire DDR channel:

- Between all groups maintain a delta of no more than 500 mm.

- Allows greater flexibility in the design for readjustments as needed.

- DDR data group separation:

- If stack-up allows, keep DDR data groups away from the address and control nets.

- Route address and control on separate critical layers.

- If resistor networks (RNs) are used, attempt to keep data and command lines in separate packages.

## 3.6 Connectivity Guidelines

This section summarizes the connections and special conditions, such as pull-up or pull-down resistors, for the MSC7118 device. Following are guidelines for signal groups and configuration settings:

- Clock and reset signals.

- SWTE is used to configure the MSC7118 device and is sampled on the deassertion of PORESET, so it should be tied to V<sub>DDC</sub> or GND either directly or through pull-up or pull-down resistors until PORESET is deasserted. After PORESET, this signal can be left floating.

- BM[0–1] configure the MSC7118 device and are sampled until PORESET is deasserted, so they should be tied to V<sub>DDIO</sub> or GND either directly or through pull-up or pull-down resistors.

- **HRESET** should be pulled up.

- *Interrupt signals*. When used, **IRQ** pins must be pulled up.

- HDI16 signals.

- When they are configured for open-drain, the HREQ/HREQ or HTRQ/HTRQ signals require a pull-up resistor. However, these pins are also sampled at power-on reset to determine the HDI16 boot mode and may need to be pulled down. When these pins must be pulled down on reset and pulled up otherwise, a buffer can be used with the HRESET signal as the enable.

- When the device boots through the HDI16, the HDDS, HDSP and H8BIT pins should be pulled up or down, depending on the required boot mode settings.

- $I^2C$  signals. The SCL and SDA signals, when programmed for  $I^2C$ , requires an external pull-up resistor.

- *General-purpose I/O (GPIO) signals*. An unused GPIO pin can be disconnected. After boot, program it as an output pin.

- Other signals.

- The  $\overline{\mathsf{TEST0}}$  pin must be connected to ground.

- The TPSEL pin should be pulled up to enable debug access via the EOnCE port and pulled down for boundary scan.

- Pins labelled NO CONNECT (NC) must not be connected.

- When a 16-pin double data rate (DDR) interface is used, the 16 unused data pins should be no connects (floating) if the used lines are terminated.

- Do not connect DBREQ to DONE (as you would for the MSC8101 device). Connect DONE to one of the EVNT pins, and DBREQ to HRRQ.

## 4 Ordering Information

Consult a Freescale Semiconductor sales office or authorized distributor to determine product availability and place an order.

| Part    | Supply Voltage             | Package Type                                      | Pin<br>Count | Core<br>Frequency<br>(MHz) | Solder Spheres | Order Number  |

|---------|----------------------------|---------------------------------------------------|--------------|----------------------------|----------------|---------------|

| MSC7118 | 1.2 V core<br>2.5 V memory | Molded Array Process-Ball Grid<br>Array (MAP-BGA) | 400          | 300                        | Lead-free      | MSC7118VM1200 |

|         | 3.3 V I/O                  |                                                   |              |                            | Lead-bearing   | MSC7118VF1200 |

MSC7118 Low-Cost 16-bit DSP with DDR Controller Data Sheet, Rev. 7

#### How to Reach Us:

Home Page: www.freescale.com

## Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Document Number: MSC7118 Rev. 7 4/2008 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale™, the Freescale logo, CodeWarrior, fieldBIST, and StarCore are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2004, 2008. All rights reserved.