# E·XFL

#### NXP USA Inc. - KMSC7118VM1200 Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Betans                  |                                                                        |

|-------------------------|------------------------------------------------------------------------|

| Product Status          | Obsolete                                                               |

| Туре                    | Fixed Point                                                            |

| Interface               | Host Interface, I <sup>2</sup> C, UART                                 |

| Clock Rate              | 300MHz                                                                 |

| Non-Volatile Memory     | ROM (8kB)                                                              |

| On-Chip RAM             | 464kB                                                                  |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.20V                                                                  |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                     |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 400-LFBGA                                                              |

| Supplier Device Package | 400-LFBGA (17x17)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmsc7118vm1200 |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

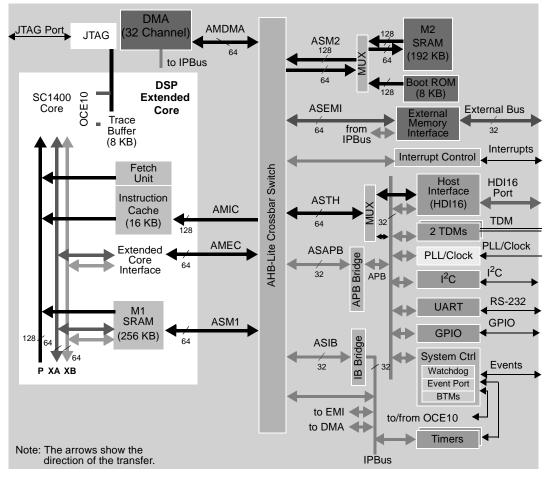

Figure 1. MSC7118 Block Diagram

NP

ssignments

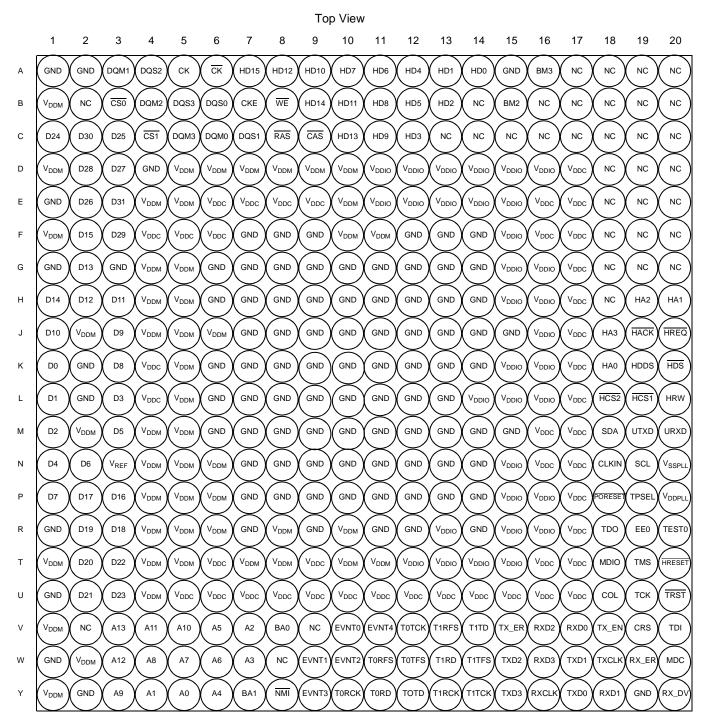

# 1 Pin Assignments

This section includes diagrams of the MSC7118 package ball grid array layouts and pinout allocation tables.

# 1.1 MAP-BGA Ball Layout Diagrams

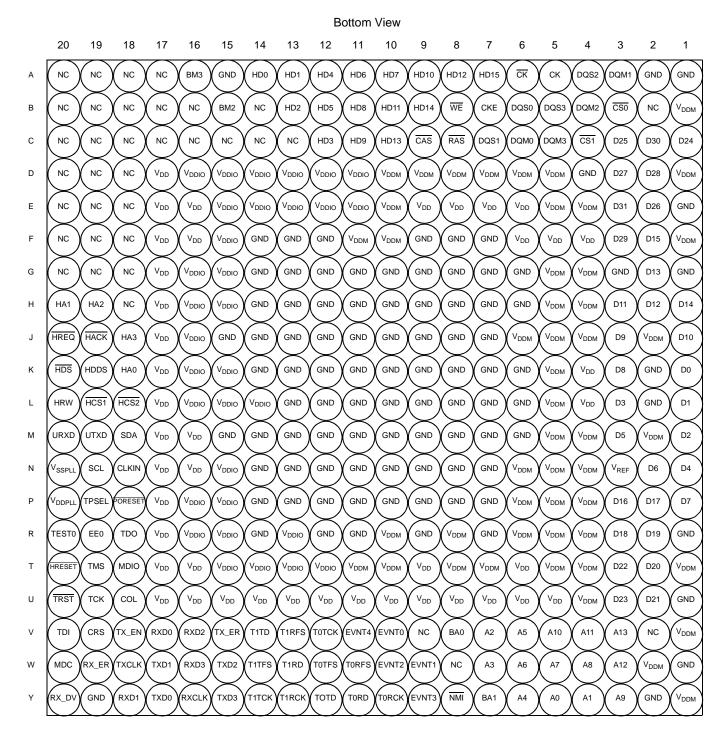

Top and bottom views of the MAP-BGA package are shown in Figure 2 and Figure 3 with their ball location index numbers.

Pin Assignments

Figure 3. MSC7118 Molded Array Process-Ball Grid Array (MAP-BGA), Bottom View

|        |              | Signal Names             |                      |             |          |            |

|--------|--------------|--------------------------|----------------------|-------------|----------|------------|

| Number |              | S                        | oftware Controlle    | ed          | Hardware | Controlled |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |

| B14    |              |                          | Ν                    | IC          |          |            |

| B15    | BM2          | GP                       | ID7                  | GPOD7       | rese     | erved      |

| B16    |              |                          | Ν                    | IC          |          |            |

| B17    |              |                          | Ν                    | IC          |          |            |

| B18    |              |                          | Ν                    | IC          |          |            |

| B19    |              |                          | Ν                    | IC          |          |            |

| B20    |              |                          | Ν                    | IC          |          |            |

| C1     |              |                          | D                    | 24          |          |            |

| C2     |              |                          | D                    | 30          |          |            |

| C3     |              |                          | D                    | 25          |          |            |

| C4     |              |                          | C                    | <u>S1</u>   |          |            |

| C5     |              |                          | DG                   | 2M3         |          |            |

| C6     |              |                          | DG                   | 2M0         |          |            |

| C7     |              |                          | DC                   | QS1         |          |            |

| C8     |              |                          | R                    | AS          |          |            |

| C9     |              | CAS                      |                      |             |          |            |

| C10    |              | GPIC5 GPOC5 HD13         |                      |             |          |            |

| C11    |              | GPIC1 GPOC1 HD9          |                      |             |          |            |

| C12    |              | reserved HD3             |                      |             |          |            |

| C13    |              | NC                       |                      |             |          |            |

| C14    |              | NC                       |                      |             |          |            |

| C15    | NC           |                          |                      |             |          |            |

| C16    |              | NC                       |                      |             |          |            |

| C17    |              |                          | Ν                    | IC          |          |            |

| C18    |              |                          |                      | IC          |          |            |

| C19    |              | NC                       |                      |             |          |            |

| C20    |              | NC                       |                      |             |          |            |

| D1     |              | V <sub>DDM</sub>         |                      |             |          |            |

| D2     |              | D28                      |                      |             |          |            |

| D3     |              | D27                      |                      |             |          |            |

| D4     | GND          |                          |                      |             |          |            |

| D5     |              | V <sub>DDM</sub>         |                      |             |          |            |

| D6     |              | V <sub>DDM</sub>         |                      |             |          |            |

| D7     |              | V <sub>DDM</sub>         |                      |             |          |            |

| D8     |              |                          |                      | DM          |          |            |

| D9     |              |                          |                      | DM          |          |            |

### Table 1. MSC7118 Signals by Ball Designator (continued)

|        |              | Signal Names             |                      |             |          |            |  |

|--------|--------------|--------------------------|----------------------|-------------|----------|------------|--|

| Number |              | S                        | oftware Controlle    | d           | Hardware | Controlled |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |

| F6     |              |                          | V <sub>C</sub>       | DC          |          |            |  |

| F7     |              |                          | GI                   | ND          |          |            |  |

| F8     |              |                          | GI                   | ND          |          |            |  |

| F9     |              |                          | GI                   | ND          |          |            |  |

| F10    |              |                          | VD                   | DM          |          |            |  |

| F11    |              |                          | V <sub>D</sub>       | DM          |          |            |  |

| F12    |              |                          | GI                   | ND          |          |            |  |

| F13    |              |                          | GI                   | ND          |          |            |  |

| F14    |              |                          | GI                   | ND          |          |            |  |

| F15    |              |                          | V <sub>D</sub>       | DIO         |          |            |  |

| F16    |              |                          | V <sub>D</sub>       | DC          |          |            |  |

| F17    |              |                          |                      | DC          |          |            |  |

| F18    |              |                          |                      | С           |          |            |  |

| F19    |              |                          | N                    | С           |          |            |  |

| F20    |              | NC                       |                      |             |          |            |  |

| G1     |              | GND                      |                      |             |          |            |  |

| G2     |              | D13                      |                      |             |          |            |  |

| G3     |              | GND                      |                      |             |          |            |  |

| G4     |              | V <sub>DDM</sub>         |                      |             |          |            |  |

| G5     |              | V <sub>DDM</sub>         |                      |             |          |            |  |

| G6     |              | GND                      |                      |             |          |            |  |

| G7     |              | GND                      |                      |             |          |            |  |

| G8     |              | GND                      |                      |             |          |            |  |

| G9     |              | GND                      |                      |             |          |            |  |

| G10    |              | GND                      |                      |             |          |            |  |

| G11    |              | GND                      |                      |             |          |            |  |

| G12    |              |                          | GI                   | ND          |          |            |  |

| G13    | 1            | GND                      |                      |             |          |            |  |

| G14    | 1            | GND                      |                      |             |          |            |  |

| G15    |              | V <sub>DDIO</sub>        |                      |             |          |            |  |

| G16    |              | V <sub>DDIO</sub>        |                      |             |          |            |  |

| G17    | 1            | V <sub>DDC</sub>         |                      |             |          |            |  |

| G18    | NC           |                          |                      |             |          |            |  |

| G19    | 1            | NC                       |                      |             |          |            |  |

| G20    | 1            |                          |                      | С           |          |            |  |

| H1     | 1            |                          |                      | 14          |          |            |  |

### Table 1. MSC7118 Signals by Ball Designator (continued)

|        |                    | Signal Names             |                      |             |          |            |  |

|--------|--------------------|--------------------------|----------------------|-------------|----------|------------|--|

| Number |                    | S                        | oftware Controlle    | d           | Hardware | Controlled |  |

|        | End of Reset       | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |

| N10    |                    |                          | GI                   | ND          |          |            |  |

| N11    |                    |                          | GI                   | ND          |          |            |  |

| N12    |                    |                          | GI                   | ND          |          |            |  |

| N13    |                    |                          | GI                   | ND          |          |            |  |

| N14    |                    |                          | GI                   | ND          |          |            |  |

| N15    |                    |                          | V <sub>D</sub>       | DIO         |          |            |  |

| N16    |                    |                          | V <sub>D</sub>       | DC          |          |            |  |

| N17    |                    |                          | V <sub>D</sub>       | DC          |          |            |  |

| N18    |                    |                          |                      | KIN         |          |            |  |

| N19    | GPI                | A15                      | IRQ14                | GPOA15      | S        | SCL        |  |

| N20    |                    |                          | V <sub>SS</sub>      | SPLL        |          |            |  |

| P1     |                    |                          |                      | 7           |          |            |  |

| P2     |                    |                          | D                    | 17          |          |            |  |

| P3     |                    |                          | D                    | 16          |          |            |  |

| P4     |                    |                          | VD                   | DM          |          |            |  |

| P5     |                    | V <sub>DDM</sub>         |                      |             |          |            |  |

| P6     |                    | V <sub>DDM</sub>         |                      |             |          |            |  |

| P7     |                    | GND                      |                      |             |          |            |  |

| P8     |                    | GND                      |                      |             |          |            |  |

| P9     |                    | GND                      |                      |             |          |            |  |

| P10    |                    | GND                      |                      |             |          |            |  |

| P11    |                    | GND                      |                      |             |          |            |  |

| P12    |                    | GND                      |                      |             |          |            |  |

| P13    |                    | GND                      |                      |             |          |            |  |

| P14    |                    |                          |                      | ND          |          |            |  |

| P15    |                    |                          |                      | DIO         |          |            |  |

| P16    |                    | V <sub>DDIO</sub>        |                      |             |          |            |  |

| P17    | V <sub>DDC</sub>   |                          |                      |             |          |            |  |

| P18    | PORESET            |                          |                      |             |          |            |  |

| P19    | TPSEL              |                          |                      |             |          |            |  |

| P20    | V <sub>DDPLL</sub> |                          |                      |             |          |            |  |

| R1     | GND                |                          |                      |             |          |            |  |

| R2     | D19                |                          |                      |             |          |            |  |

| R3     |                    | D18                      |                      |             |          |            |  |

| R4     |                    |                          |                      | DM          |          |            |  |

| R5     |                    |                          |                      | DM          |          |            |  |

### Table 1. MSC7118 Signals by Ball Designator (continued)

ssignments

|          |              | _                        | Signa                | l Names     |                 |            |

|----------|--------------|--------------------------|----------------------|-------------|-----------------|------------|

| Number   |              | Software Controlled      |                      |             | Hardware        | Controlled |

| End of R | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary         | Alternate  |

| V18      | GPI          | A24                      | IRQ24                | GPOA24      | TX_             | EN         |

| V19      |              | rese                     | rved                 |             | CF              | RS         |

| V20      |              |                          |                      | ГDI         |                 |            |

| W1       |              |                          | C                    | SND         |                 |            |

| W2       |              |                          | V                    | DDM         |                 |            |

| W3       |              |                          | ,                    | A12         |                 |            |

| W4       |              |                          |                      | A8          |                 |            |

| W5       |              |                          |                      | A7          |                 |            |

| W6       |              |                          |                      | A6          |                 |            |

| W7       |              |                          |                      | A3          |                 |            |

| W8       |              |                          |                      | NC          |                 |            |

| W9       | GPI          | A17                      | IRQ13                | GPOA17      | EVNT1           | CLKO       |

| W10      | BM0          | GPI                      | C14                  | GPOC14      | EVI             | NT2        |

| W11      | GPI          | GPIA10 IRQ5 GPOA10 TORFS |                      |             |                 |            |

| W12      | GP           | IA7                      | IRQ7                 | GPOA7       | тот             | TFS        |

| W13      | GP           | IA3                      | IRQ8                 | GPOA3       | T1I             | RD         |

| W14      | GP           | IA1                      | IRQ10                | GPOA1       | T17             | TFS        |

| W15      |              | GPID4                    |                      | GPOD4       | TXD2            | reserved   |

| W16      | GPI          | A27                      | IRQ18                | GPOA27      | RXD3            | reserved   |

| W17      | GPI          | A19                      | IRQ19                | GPOA19      | ТХ              | D1         |

| W18      | GPI          | A23                      | IRQ23                | GPOA23      | TXCLK or        | REFCLK     |

| W19      | GPI          | A26                      | IRQ26                | GPOA26      | RX_             | _ER        |

| W20      | H8BIT        |                          | reserved             |             | M               | C          |

| Y1       |              |                          | V                    | DDM         |                 |            |

| Y2       |              |                          | C                    | SND         |                 |            |

| Y3       |              |                          |                      | A9          |                 |            |

| Y4       |              |                          |                      | A1          |                 |            |

| Y5       |              |                          |                      | A0          |                 |            |

| Y6       | A4           |                          |                      |             |                 |            |

| Y7       |              |                          | E                    | 3A1         |                 |            |

| Y8       | rese         | rved                     | NMI                  |             | reserved        |            |

| Y9       | BM1          | GPI                      | C15                  | GPOC15      | EVM             | NT3        |

| Y10      | GPI          | A11                      | IRQ4                 | GPOA11      | TOR             | СK         |

| Y11      |              | GPIA9                    |                      | GPOA9       | TO              | RD         |

| Y12      |              | GPIA6                    |                      | GPOA6       | T0 <sup>-</sup> | TD         |

| Y13      | GP           | IA5                      | IRQ0                 | GPOA5       | T1R             | RCK        |

Table 1. MSC7118 Signals by Ball Designator (continued)

Table 2 describes the maximum electrical ratings for the MSC7118.

| Table 2 | Absolute | Maximum | Ratings |

|---------|----------|---------|---------|

|---------|----------|---------|---------|

| Rating                        | Symbol             | Value              | Unit |

|-------------------------------|--------------------|--------------------|------|

| Core supply voltage           | V <sub>DDC</sub>   | 1.5                | V    |

| Memory supply voltage         | V <sub>DDM</sub>   | 4.0                | V    |

| PLL supply voltage            | V <sub>DDPLL</sub> | 1.5                | V    |

| I/O supply voltage            | V <sub>DDIO</sub>  | -0.2 to 4.0        | V    |

| Input voltage                 | V <sub>IN</sub>    | (GND – 0.2) to 4.0 | V    |

| Reference voltage             | V <sub>REF</sub>   | 4.0                | V    |

| Maximum operating temperature | TJ                 | 105                | °C   |

| Minimum operating temperature | T <sub>A</sub>     | -40                | °C   |

| Storage temperature range     | T <sub>STG</sub>   | -55 to +150        | °C   |

Notes: 1. Functional operating conditions are given in Table 3.

2. Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the listed limits may affect device reliability or cause permanent damage.

3. Section 3.1, Thermal Design Considerations includes a formula for computing the chip junction temperature (T<sub>J</sub>).

# 2.2 Recommended Operating Conditions

Table 3 lists recommended operating conditions. Proper device operation outside of these conditions is not guaranteed.

#### **Table 3. Recommended Operating Conditions**

| Rating                      | Symbol                           | Value                        | Unit     |

|-----------------------------|----------------------------------|------------------------------|----------|

| Core supply voltage         | V <sub>DDC</sub>                 | 1.14 to 1.26                 | V        |

| Memory supply voltage       | V <sub>DDM</sub>                 | 2.38 to 2.63                 | V        |

| PLL supply voltage          | V <sub>DDPLL</sub>               | 1.14 to 1.26                 | V        |

| I/O supply voltage          | V <sub>DDIO</sub>                | 3.14 to 3.47                 | V        |

| Reference voltage           | V <sub>REF</sub>                 | 1.19 to 1.31                 | V        |

| Operating temperature range | T <sub>J</sub><br>T <sub>A</sub> | maximum: 105<br>minimum: –40 | 0°<br>0° |

# 2.5 AC Timings

This section presents timing diagrams and specifications for individual signals and parallel I/O outputs and inputs. All AC timings are based on a 30 pF load, except where noted otherwise, and a 50  $\Omega$  transmission line. For any additional pF, use the following equations to compute the delay:

- Standard interface:  $2.45 + (0.054 \times C_{load})$  ns

- DDR interface:  $1.6 + (0.002 \times C_{load})$  ns

# 2.5.1 Clock and Timing Signals

The following tables describe clock signal characteristics. **Table 6** shows the maximum frequency values for internal (core, reference, and peripherals) and external (CLKO) clocks. You must ensure that maximum frequency values are not exceeded (see **Section 2.5.2** for the allowable ranges when using the PLL).

#### **Table 6. Maximum Frequencies**

| Characteristic                         | Maximum in MHz |

|----------------------------------------|----------------|

| Core clock frequency (CLOCK)           | 300            |

| External output clock frequency (CLKO) | 75             |

| Memory clock frequency (CK, CK)        | 150            |

| TDM clock frequency (TxRCK, TxTCK)     | 50             |

#### Table 7. Clock Frequencies in MHz

| Characteristic                                                         | Symbol             | Min | Max |  |

|------------------------------------------------------------------------|--------------------|-----|-----|--|

| CLKIN frequency                                                        | F <sub>CLKIN</sub> | 10  | 100 |  |

| CLOCK frequency                                                        | F <sub>CORE</sub>  | —   | 300 |  |

| CK, CK frequency                                                       | F <sub>CK</sub>    | —   | 150 |  |

| TDMxRCK, TDMxTCK frequency                                             | F <sub>TDMCK</sub> | —   | 50  |  |

| CLKO frequency                                                         | F <sub>СКО</sub>   | —   | 75  |  |

| AHB/IPBus/APB clock frequency                                          | F <sub>BCK</sub>   | —   | 150 |  |

| Note: The rise and fall time of external clocks should be 5 ns maximum |                    |     |     |  |

#### **Table 8. System Clock Parameters**

| Characteristic                        | Min | Мах  | Unit |

|---------------------------------------|-----|------|------|

| CLKIN frequency                       | 10  | 100  | MHz  |

| CLKIN slope                           | —   | 5    | ns   |

| CLKIN frequency jitter (peak-to-peak) | —   | 1000 | ps   |

| CLKO frequency jitter (peak-to-peak)  | —   | 150  | ps   |

### 2.5.2 Configuring Clock Frequencies

This section describes important requirements for configuring clock frequencies in the MSC7118 device when using the PLL block. To configure the device clocking, you must program four fields in the Clock Control Register (CLKCTL):

- *PLLDVF field*. Specifies the PLL division factor (PLLDVF + 1) to divide the input clock frequency F<sub>CLKIN</sub>. The output of the divider block is the input to the multiplier block.

- PLLMLTF field. Specifies the PLL multiplication factor (PLLMLTF + 1). The output from the multiplier block is the loop frequency F<sub>LOOP</sub>.

- *RNG field.* Selects the available PLL frequency range for  $F_{VCO}$ , either  $F_{LOOP}$  when the RNG bit is set (1) or  $F_{LOOP}/2$  when the RNG bit is cleared (0).

- *CKSEL field*. Selects  $F_{CLKIN}$ ,  $F_{VCO}$ , or  $F_{VCO}/2$  as the source for the core clock.

There are restrictions on the frequency range permitted at the beginning of the multiplication portion of the PLL that affect the allowable values for the PLLDVF and PLLMLTF fields. The following sections define these restrictions and provide guidelines to configure the device clocking when using the PLL. Refer to the Clock and Power Management chapter in the *MSC711x Reference Manual* for details on the clock programming model.

### 2.5.2.1 PLL Multiplier Restrictions

There are two restrictions for correct usage of the PLL block:

- The input frequency to the PLL multiplier block (that is, the output of the divider) must be in the range 10–25 MHz.

- The output frequency of the PLL multiplier must be in the range 266–532 MHz.

When programming the PLL for a desired output frequency using the PLLDVF, PLLMLTF, and RNG fields, you must meet these constraints.

### 2.5.2.2 Input Division Factors and Corresponding CLKIN Frequency Range

The value of the PLLDVF field determines the allowable CLKIN frequency range, as shown in Table 9.

| PLLDVF<br>Field Value | Input Divide<br>Factor | CLKIN Frequency Range               | Comments                                    |

|-----------------------|------------------------|-------------------------------------|---------------------------------------------|

| 0x00                  | 1                      | 10 to 25 MHz                        | Input Division by 1                         |

| 0x01                  | 2                      | 20 to 50 MHz                        | Input Division by 2                         |

| 0x02                  | 3                      | 30 to 75 MHz                        | Input Division by 3                         |

| 0x03                  | 4                      | 40 to 100 MHz                       | Input Division by 4                         |

| 0x04                  | 5                      | 50 to 100 MHz                       | Input Division by 5                         |

| 0x05                  | 6                      | 60 to 100 MHz                       | Input Division by 6                         |

| 0x06                  | 7                      | 70 to 100 MHz                       | Input Division by 7                         |

| 0x07                  | 8                      | 80 to 100 MHz                       | Input Division by 8                         |

| 0x08                  | 9                      | 90 to 100 MHz                       | Input Division by 9                         |

| 0x09                  | 10                     | 100 MHz                             | Input Division by 10                        |

| Note: The ma          | aximum CLKIN freq      | uency is 100 MHz. Therefore, the Pl | LLDVF value must be in the range from 1–10. |

#### Table 9. CLKIN Frequency Ranges by Divide Factor Value

### 2.5.2.3 Multiplication Factor Range

The multiplier block output frequency ranges depend on the divided input clock frequency as shown in Table 10.

| Multiplier Block (Loop) Output Range |                                                                                                                   | Minimum PLLMLTF Value            | Maximum PLLMLTF Value      |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------|

|                                      | $266 \leq$ [Divided Input Clock × (PLLMLTF + 1)] $\leq$ 532 MHz                                                   | 266/Divided Input Clock          | 532/Divided Input Clock    |

| Note:                                | This table results from the allowed range for F <sub>Loop</sub> . The minim frequency of the Divided Input Clock. | um and maximum multiplication fa | ctors are dependent on the |

#### Table 10. PLLMLTF Ranges

### 2.5.2.4 Allowed Core Clock Frequency Range

The frequency delivered to the core, extended core, and peripherals depends on the value of the CLKCTRL[RNG] bit as shown in **Table 11**.

| Table 11. F <sub>vcc</sub> | Frequency | Ranges |

|----------------------------|-----------|--------|

|----------------------------|-----------|--------|

| CLKCTRL[RNG] Value |                                                                                                                       | Allowed Range of F <sub>vco</sub>     |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|

|                    | 1                                                                                                                     | $266 \le F_{vco} \le 532 \text{ MHz}$ |  |

|                    | 0                                                                                                                     | $133 \le F_{vco} \le 266 \text{ MHz}$ |  |

| Note:              | This table results from the allowed range for F <sub>vco</sub> , which is F <sub>Loop</sub> modified by CLKCTRL[RNG]. |                                       |  |

This bit along with the CKSEL determines the frequency range of the core clock.

| CLKCT | RL[CKSEL]                                                                                                            | CLKCTRL[RNG] | Resulting<br>Division<br>Factor | Allowed Range<br>of Core Clock        | Comments                             |  |

|-------|----------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------|---------------------------------------|--------------------------------------|--|

|       | 11                                                                                                                   | 1            | 1                               | $266 \le core \ clock \le 300 \ MHz$  | Limited by maximum core<br>frequency |  |

|       | 11                                                                                                                   | 0            | 2                               | $133 \le core \ clock \le 266 \ MHz$  | Limited by range of PLL              |  |

|       | 01                                                                                                                   | 1            | 2                               | $133 \le core \ clock \le 266 \ MHz$  | Limited by range of PLL              |  |

|       | 01                                                                                                                   | 0            | 4                               | $66.5 \le core \ clock \le 133 \ MHz$ | Limited by range of PLL              |  |

| Note: | This table results from the allowed range for F <sub>OUT</sub> , which depends on clock selected via CLKCTRL[CKSEL]. |              |                                 |                                       |                                      |  |

### 2.5.2.5 Core Clock Frequency Range When Using DDR Memory

The core clock can also be limited by the frequency range of the DDR devices in the system. **Table 13** summarizes this restriction.

| DDR Type          | Allowed Frequency<br>Range for DDR CK | Corresponding Range<br>for the Core Clock | Comments                                                |

|-------------------|---------------------------------------|-------------------------------------------|---------------------------------------------------------|

| DDR 200 (PC-1600) | 83–100 MHz                            | $166 \le core \ clock \le 200 \ MHz$      | Core limited to 2 × maximum DDR frequency               |

| DDR 266 (PC-2100) | 83–133 MHz                            | $166 \le core \ clock \le 266 \ MHz$      | Core limited to $2 \times \text{maximum DDR}$ frequency |

| DDR 333 (PC-2600) | 83–150 MHz                            | $166 \le core \ clock \le 300 \ MHz$      | Core limited to $2 \times \text{maximum DDR}$ frequency |

Table 13. Core Clock Ranges When Using DDR

### 2.5.3 Reset Timing

The MSC7118 device has several inputs to the reset logic. All MSC7118 reset sources are fed into the reset controller, which takes different actions depending on the source of the reset. The reset status register indicates the most recent sources to cause a reset. **Table 14** describes the reset sources.

| Name                                       | Direction     | Description                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset<br>(PORESET)                | Input         | Initiates the power-on reset flow that resets the MSC7118 and configures various attributes of the MSC7118. On PORESET, the entire MSC7118 device is reset. SPLL and DLL states are reset, HRESET is driven, the SC1400 extended core is reset, and system configuration is sampled. The system is configured only when PORESET is asserted. |

| External Hard<br>reset (HRESET)            | Input/ Output | Initiates the hard reset flow that configures various attributes of the MSC7118. While HRESET is asserted, HRESET is an open-drain output. Upon hard reset, HRESET is driven and the SC1400 extended core is reset.                                                                                                                          |

| Software<br>watchdog reset                 | Internal      | When the MSC7118 watchdog count reaches zero, a software watchdog reset is signalled. The enabled software watchdog event then generates an internal hard reset sequence.                                                                                                                                                                    |

| Bus monitor reset                          | Internal      | When the MSC7118 bus monitor count reaches zero, a bus monitor hard reset is asserted. The enabled bus monitor event then generates an internal hard reset sequence.                                                                                                                                                                         |

| JTAG EXTEST,<br>CLAMP, or<br>HIGHZ command | Internal      | When a Test Access Port (TAP) executes an EXTEST, CLAMP, or HIGHZ command, the TAP logic asserts an internal reset signal that generates an internal soft reset sequence.                                                                                                                                                                    |

#### Table 14. Reset Sources

Table 15 summarizes the reset actions that occur as a result of the different reset sources.

#### Table 15. Reset Actions for Each Reset Source

|                                                                           | Po <u>wer-On Re</u> set<br>(PORESET) | H <u>ard Rese</u> t<br>(HRESET)                                  | S <u>oft Rese</u> t<br>(SRESET)             |

|---------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------|---------------------------------------------|

| Reset Action/Reset Source                                                 | External only                        | External or<br>Internal (Software<br>Watchdog or Bus<br>Monitor) | JTAG Command:<br>EXTEST, CLAMP,<br>or HIGHZ |

| Configuration pins sampled (refer to <b>Section 2.5.3.1</b> for details). | Yes                                  | No                                                               | No                                          |

| PLL and clock synthesis states Reset                                      | Yes                                  | No                                                               | No                                          |

| HRESET Driven                                                             | Yes                                  | Yes                                                              | No                                          |

| Software watchdog and bus time-out monitor registers                      | Yes                                  | Yes                                                              | Yes                                         |

| Clock synthesis modules (STOPCTRL, HLTREQ, and HLTACK) reset              | Yes                                  | Yes                                                              | Yes                                         |

| Extended core reset                                                       | Yes                                  | Yes                                                              | Yes                                         |

| Peripheral modules reset                                                  | Yes                                  | Yes                                                              | Yes                                         |

### 2.5.3.1 Power-On Reset (PORESET) Pin

Asserting  $\overrightarrow{\text{PORESET}}$  initiates the power-on reset flow.  $\overrightarrow{\text{PORESET}}$  must be asserted externally for at least 16 CLKIN cycles after external power to the MSC7118 reaches at least 2/3 V<sub>DD</sub>.

### 2.5.4 DDR DRAM Controller Timing

This section provides the AC electrical characteristics for the DDR DRAM interface.

### 2.5.4.1 DDR DRAM Input AC Timing Specifications

Table 17 provides the input AC timing specifications for the DDR DRAM interface.

### Table 17. DDR DRAM Input AC Timing

| No.    | Parameter                                                                                                                                                                                                                                                                                                                            | Symbol          | Min                     | Мах                     | Unit |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|-------------------------|------|

| —      | AC input low voltage                                                                                                                                                                                                                                                                                                                 | V <sub>IL</sub> |                         | V <sub>REF</sub> – 0.31 | V    |

| _      | AC input high voltage                                                                                                                                                                                                                                                                                                                | V <sub>IH</sub> | V <sub>REF</sub> + 0.31 | V <sub>DDM</sub> + 0.3  | V    |

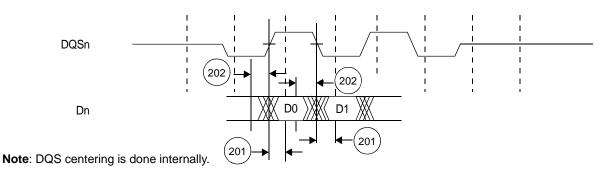

| 201    | Maximum Dn input setup skew relative to DQSn input                                                                                                                                                                                                                                                                                   | _               | _                       | 900                     | ps   |

| 202    | Maximum Dn input hold skew relative to DQSn input                                                                                                                                                                                                                                                                                    | _               | _                       | 900                     | ps   |

| Notes: | <ol> <li>Maximum possible skew between a data strobe (DQSn) and any corresponding bit of data (D[8n + {07}] if 0 ≤ n ≤ 7).</li> <li>See Table 18 for t<sub>CK</sub> value.</li> <li>Dn should be driven at the same time as DQSn. This is necessary because the DQSn centering on the DQn data tenure is done internally.</li> </ol> |                 |                         |                         |      |

Figure 5. DDR DRAM Input Timing Diagram

### 2.5.4.2 DDR DRAM Output AC Timing Specifications

Table 18 and Table 19 list the output AC timing specifications and measurement conditions for the DDR DRAM interface.

| Table 18. DDR DRAM Output A | C Timing |

|-----------------------------|----------|

|-----------------------------|----------|

| No. | Parameter                                                                                            | Symbol              | Min                       | Max | Unit     |

|-----|------------------------------------------------------------------------------------------------------|---------------------|---------------------------|-----|----------|

| 200 | CK cycle time, (CK/ <del>CK</del> crossing) <sup>1</sup><br>• 100 MHz (DDR200)<br>• 150 MHz (DDR300) | tск                 | 10<br>6.67                |     | ns<br>ns |

| 204 | An/RAS/CAS/WE/CKE output setup with respect to CK                                                    | t <sub>DDKHAS</sub> | $0.5 	imes t_{CK} - 1000$ | _   | ps       |

| 205 | An/RAS/CAS/WE/CKE output hold with respect to CK                                                     | t <sub>DDKHAX</sub> | $0.5 	imes t_{CK} - 1000$ | _   | ps       |

| 206 | CSn output setup with respect to CK                                                                  | t <sub>DDKHCS</sub> | $0.5 	imes t_{CK} - 1000$ | _   | ps       |

| 207 | CSn output hold with respect to CK                                                                   | t <sub>DDKHCX</sub> | $0.5 	imes t_{CK} - 1000$ | _   | ps       |

| 208 | CK to DQSn <sup>2</sup>                                                                              | t <sub>DDKHMH</sub> | -600                      | 600 | ps       |

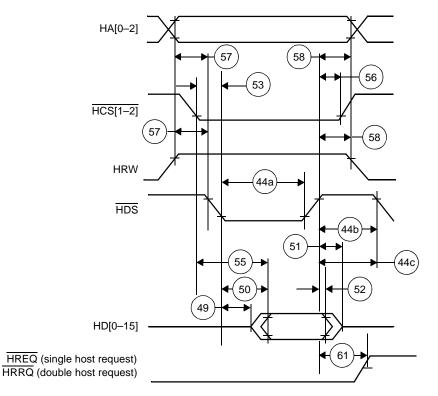

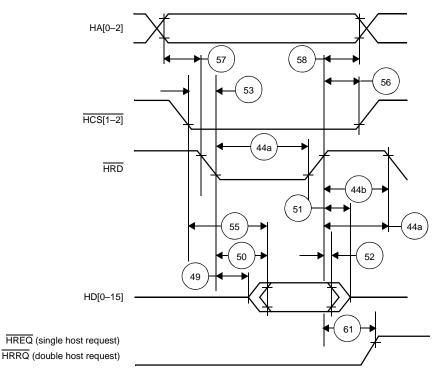

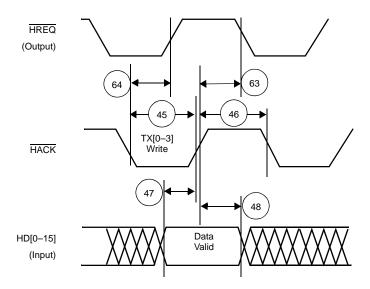

Figure 10 and Figure 11 show HDI16 read signal timing. Figure 12 and Figure 13 show HDI16 write signal timing.

Figure 10. Read Timing Diagram, Single Data Strobe

Figure 11. Read Timing Diagram, Double Data Strobe

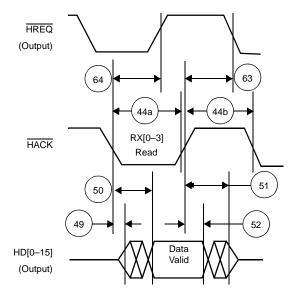

Figure 14. Host DMA Read Timing Diagram, HPCR[OAD] = 0

Figure 15. Host DMA Write Timing Diagram, HPCR[OAD] = 0

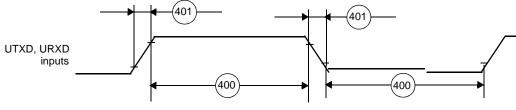

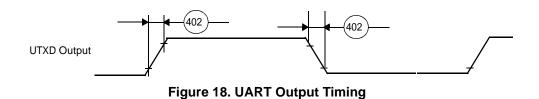

# 2.5.8 UART Timing

| No. | Characteristics                        | Expression               | Min    | Max | Unit |

|-----|----------------------------------------|--------------------------|--------|-----|------|

| —   | Internal bus clock (APBCLK)            | F <sub>CORE</sub> /2     | _      | 150 | MHz  |

| _   | Internal bus clock period (1/APBCLK)   | T <sub>APBCLK</sub>      | 6.67   | _   | ns   |

| 400 | URXD and UTXD inputs high/low duration | 16 × T <sub>APBCLK</sub> | 106.67 | _   | ns   |

| 401 | URXD and UTXD inputs rise/fall time    |                          | —      | 5   | ns   |

| 402 | UTXD output rise/fall time             |                          |        | 5   | ns   |

Figure 17. UART Input Timing

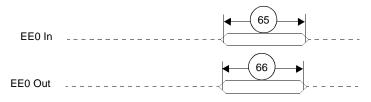

# 2.5.9 EE Timing

#### Table 24. EE0 Timing

| Number                |                                                                                                                                                                                                                                                                                                                                                              | Characteristics          | Туре                      | Min                  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------|----------------------|

| 65                    |                                                                                                                                                                                                                                                                                                                                                              | EE0 input to the core    | Asynchronous              | 4 core clock periods |

| 66                    |                                                                                                                                                                                                                                                                                                                                                              | EE0 output from the core | Synchronous to core clock | 1 core clock period  |

| Notes: 1.<br>2.<br>3. | <ol> <li>The core clock is the SC1400 core clock. The ratio between the core clock and CLKOUT is configured during power-on-reset.</li> <li>Configure the direction of the EE pin in the EE_CTRL register (see the SC140/SC1400 Core Reference Manual for details.</li> <li>Refer to Table 1-11 on page 1-16 for details on EE pin functionality.</li> </ol> |                          |                           |                      |

Figure 20 shows the signal behavior of the EE pin.

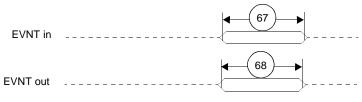

# 2.5.10 Event Timing

| Table | 25. | EVNT | Signal | Timing |

|-------|-----|------|--------|--------|

|-------|-----|------|--------|--------|

| Number                                                                                                                                                                                                                                                                                                         | Characteristics | Туре                      | Min                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------|-----------------------------|

| 67                                                                                                                                                                                                                                                                                                             | EVNT as input   | Asynchronous              | $1.5 \times APBCLK$ periods |

| 68                                                                                                                                                                                                                                                                                                             | EVNT as output  | Synchronous to core clock | 1 APBCLK period             |

| <ol> <li>Notes: 1. Refer to Table 23 for a definition of the APBCLK period.</li> <li>2. Direction of the EVNT signal is configured through the GPIO and Event port registers.</li> <li>3. Refer to the signal chapter in the <i>MSC711x Reference Manual</i> for details on EVNT pin functionality.</li> </ol> |                 |                           |                             |

Figure 20 shows the signal behavior of the EVNT pins.

### Figure 20. EVNT Pin Timing

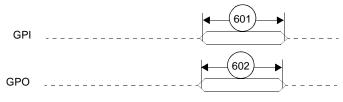

### 2.5.11 GPIO Timing

### Table 26. GPIO Signal Timing<sup>1,2,3</sup>

| Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Characteristics                  | Туре                      | Min                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------|---------------------------------|

| 601                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | GPI <sup>4.5</sup>               | Asynchronous              | $1.5 \times APBCLK$ periods     |

| 602                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | GPO <sup>5</sup>                 | Synchronous to core clock | 1 APBCLK period                 |

| 603                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Port A edge-sensitive interrupt  | Asynchronous              | $1.5 \times APBCLK$ periods     |

| 604                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Port A level-sensitive interrupt | Asynchronous              | 3 × APBCLK periods <sup>6</sup> |

| <ol> <li>Notes: 1. Refer to Table 23 for a definition of the APBCLK period.</li> <li>Direction of the GPIO signal is configured through the GPIO port registers.</li> <li>3. Refer to Section 1.5 for details on GPIO pin functionality.</li> <li>4. GPI data is synchronized to the APBCLK internally and the minimum listed is the capability of the hardware to capture data into a register when the GPADR is read. The specification is not tested due to the asynchronous nature of the input and dependence on the state of the DSP core. It is guaranteed by design.</li> <li>5. The output signals cannot toggle faster than 75 MHz.</li> <li>6. Level-sensitive interrupts should be held low until the system determines (via the service routine) that the interrupt is acknowledged.</li> </ol> |                                  |                           |                                 |

Figure 21 shows the signal behavior of the GPI/GPO pins.

NP .

ware Design Considerations

# 3.2 **Power Supply Design Considerations**

This section outlines the MSC7118 power considerations: power supply, power sequencing, power planes, decoupling, power supply filtering, and power consumption. It also presents a recommended power supply design and options for low-power consumption. For information on AC/DC electrical specifications and thermal characteristics, refer to **Section 2**.

### 3.2.1 Power Supply

The MSC7118 requires four input voltages, as shown in Table 28.

| Voltage   | Symbol            | Value  |

|-----------|-------------------|--------|

| Core      | V <sub>DDC</sub>  | 1.2 V  |

| Memory    | V <sub>DDM</sub>  | 2.5 V  |

| Reference | V <sub>REF</sub>  | 1.25 V |

| I/O       | V <sub>DDIO</sub> | 3.3 V  |

#### Table 28. MSC7118 Voltages

You should supply the MSC7118 core voltage via a variable switching supply or regulator to allow for compatibility with possible core voltage changes on future silicon revisions. The core voltage is supplied with 1.2 V (+5% and -10%) across V<sub>DDC</sub> and GND and the I/O section is supplied with 3.3 V ( $\pm$  10%) across V<sub>DDIO</sub> and GND. The memory and reference voltages supply the DDR memory controller block. The memory voltage is supplied with 2.5 V across V<sub>DDM</sub> and GND. The reference voltage is supplied across V<sub>REF</sub> and GND and must be between 0.49 × V<sub>DDM</sub> and 0.51 × V<sub>DDM</sub>. Refer to the JEDEC standard JESD8 (*Stub Series Terminated Logic for 2.5 Volts* (STTL\_2)) for memory voltage supply requirements.

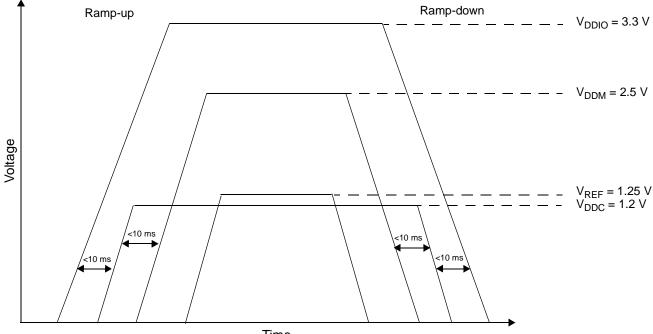

## 3.2.2 Power Sequencing

One consequence of multiple power supplies is that the voltage rails ramp up at different rates when power is initially applied. The rates depend on the power supply, the type of load on each power supply, and the way different voltages are derived. It is extremely important to observe the power up and power down sequences at the board level to avoid latch-up, forward biasing of ESD devices, and excessive currents, which all lead to severe device damage.

**Note:** There are five possible power-up/power-down sequence cases. The first four cases listed in the following sections are recommended for new designs. The fifth case is not recommended for new designs and must be carefully evaluated for current spike risks based on actual information for the specific application.

### 3.2.2.1 Case 1

The power-up sequence is as follows:

- 1. Turn on the  $V_{DDIO}$  (3.3 V) supply first.

- 2. Turn on the  $V_{DDC}$  (1.2 V) supply second.

- 3. Turn on the  $V_{DDM}$  (2.5 V) supply third.

- 4. Turn on the  $V_{REF}$  (1.25 V) supply fourth (last).

The power-down sequence is as follows:

- 1. Turn off the  $V_{REF}$  (1.25 V) supply first.

- 2. Turn off the  $V_{DDM}$  (2.5 V) supply second.

- 3. Turn off the  $V_{DDC}$  (1.2 V) supply third.

- 4. Turn of the  $V_{DDIO}$  (3.3 V) supply fourth (last).

Use the following guidelines:

- Make sure that the time interval between the ramp-down of  $V_{DDIO}$  and  $V_{DDC}$  is less than 10 ms.

- Make sure that the time interval between the ramp-up or ramp-down for  $V_{DDC}$  and  $V_{DDM}$  is less than 10 ms for power-up and power-down.

- Refer to **Figure 26** for relative timing for power sequencing case 1.

Time Figure 26. Voltage Sequencing Case 1

NP

ware Design Considerations

### 3.3.2 Peripheral Power

Peripherals include the DDR memory controller, DMA controller, HDI16, TDM, UART, timers, GPIOs, and the I<sup>2</sup>C module. Basic power consumption by each module is assumed to be the same and is computed by using the following equation which assumes an effective load of 20 pF, core voltage swing of 1.2 V, and a switching frequency of 100 MHz. This yields:

$$P_{PERIPHERAL} = 20 \ pF \times (1.2 \ V)^2 \times 150 \ MHz \times 10^{-3} = 4.32 \ mW \ per \ peripheral$$

Eqn. 6

Multiply this value by the number of peripherals used in the application to compute the total peripheral power consumption.

### 3.3.3 External Memory Power

Estimation of power consumption by the DDR memory system is complex. It varies based on overall system signal line usage, termination and load levels, and switching rates. Because the DDR memory includes terminations external to the MSC7118 device, the 2.5 V power source provides the power for the termination, which is a static value of 16 mA per signal driven high. The dynamic power is computed, however, using a differential voltage swing of  $\pm 0.200$  V, yielding a peak-to-peak swing of 0.4 V. The equations for computing the DDR power are:

$$P_{DDRIO} = P_{STATIC} + P_{DYNAMIC} \qquad Eqn. 7$$

$$P_{STATIC} = (unused pins \times \% driven high) \times 16 mA \times 2.5 V$$

Eqn. 8

$$P_{DYNAMIC} = (pin \ activity \ value) \times 20 \ pF \times (0.4 \ V)^2 \times 300 \ MHz \times 10^{-3} \ mW$$

Eqn. 9

pin activity value = (active data lines  $\times$  % activity  $\times$  % data switching) + (active address lines  $\times$  % activity) Eqn. 10

As an example, assume the following:

unused pins = 16 (DDR uses 16-pin mode) % driven high = 50% active data lines = 16 % activity = 60% % data switching = 50% active address lines = 3

In this example, the DDR memory power consumption is:

$$P_{DDRIO} = ((16 \times 0.5) \times 16 \times 2.5) + (((16 \times 0.6 \times 0.5) + (3 \times 0.6)) \times 20 \times (0.4)^2 \times 300 \times 10^{-3}) = 326.3 \text{ mW}$$

Eqn. 11

### 3.3.4 External I/O Power

The estimation of the I/O power is similar to the computation of the peripheral power estimates. The power consumption per signal line is computed assuming a maximum load of 20 pF, a voltage swing of 3.3 V, and a switching frequency of 25 MHz, which yields:

$$P_{IO} = 20 \ pF \times (3.3 \ V)^2 \times 25 \ MHz \times 10^{-3} = 5.44 \ mW \ per I/O \ line$$

Eqn. 12

Multiply this number by the number of I/O signal lines used in the application design to compute the total I/O power.

**Note:** The signal loading depends on the board routing. For systems using a single DDR device, the load could be as low as 7 pF.

### 3.3.5 Leakage Power

The leakage power is for all power supplies combined at a specific temperature. The value is temperature dependent. The observed leakage value at room temperature is 64 mW.