Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 54                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 30x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1526-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

# 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a  $32K \times 14$  program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1526/7 family. Accessing a location above these boundaries will cause a

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device                    | Program Memory<br>Space (Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |  |  |

|---------------------------|---------------------------------|--------------------------------|-------------------------------------------------------------|--|--|

| PIC16F1526<br>PIC16LF1526 | 8,192                           | 1FFFh                          | 1F80h-1FFFh                                                 |  |  |

| PIC16F1527<br>PIC16LF1527 | 16,384                          | 3FFFh                          | 3F80h-3FFFh                                                 |  |  |

Note 1: High-endurance Flash applies to the low byte of each address in the range.

wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1 and Figure 3-2).

# 3.2 High Endurance Flash

This device has a 128-byte section of high-endurance Program Flash Memory (PFM) in lieu of data EEPROM. This area is especially well suited for nonvolatile data storage that is expected to be updated frequently over the life of the end product. See **Section 11.2** "**Flash Program Memory Overview**" for more information on writing data to PFM. Refer to section **Section 3.2.1.2** "**Indirect Read with FSR**" for more information about using the FSR registers to read byte data stored in PFM.

#### 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### 3.4 **Register Definitions: Status**

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 24.0 "Instruction Set Summary").

Note 1: The C and DC bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

| U-0             | U-0                                                                | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |  |  |

|-----------------|--------------------------------------------------------------------|-----|-------|-------|---------|-------------------|------------------|--|--|

| —               | _                                                                  |     | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |

| bit 7 bit 0     |                                                                    |     |       |       |         |                   |                  |  |  |

|                 |                                                                    |     |       |       |         |                   |                  |  |  |

| Legend:         |                                                                    |     |       |       |         |                   |                  |  |  |

| R = Readable bi | = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |       |       |         |                   |                  |  |  |

#### STATUS: STATUS REGISTER **REGISTER 3-1:**

| u = Bit is u | inchanged                                           | x = Bit is unknown             | -n/n = Value at POR and BOR/Value at all other Resets    |

|--------------|-----------------------------------------------------|--------------------------------|----------------------------------------------------------|

| '1' = Bit is | set                                                 | '0' = Bit is cleared           | q = Value depends on condition                           |

|              |                                                     |                                |                                                          |

| bit 7-5      | Unimplem                                            | ented: Read as '0'             |                                                          |

| bit 4        | TO: Time-C                                          | Out bit                        |                                                          |

|              |                                                     | ower-up, CLRWDT instruction    | n or SLEEP instruction                                   |

|              | 0 = A WDT                                           | time-out occurred              |                                                          |

| bit 3        | PD: Power                                           | Down bit                       |                                                          |

|              |                                                     | ower-up or by the CLRWDT in    |                                                          |

|              | -                                                   | cution of the SLEEP instruct   | ion                                                      |

| bit 2        | Z: Zero bit                                         |                                |                                                          |

|              |                                                     | sult of an arithmetic or logic |                                                          |

|              |                                                     | sult of an arithmetic or logic |                                                          |

| bit 1        | •                                                   |                                | F, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>      |

|              | -                                                   | -out from the 4th low-order    |                                                          |

|              |                                                     | y-out from the 4th low-orde    |                                                          |

| bit 0        | -                                                   |                                | JBLW, SUBWF instructions) <sup>(1)</sup>                 |

|              | •                                                   | -out from the Most Significa   |                                                          |

|              |                                                     | y-out norm the Most Signing    | ant bit of the result occurred                           |

| Note 1:      | For $\overline{\text{Borrow}}$ , the second operand | . ,                            | action is executed by adding the two's complement of the |

# 5.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate the internal system clock sources: the 16 MHz High-Frequency Internal Oscillator and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

#### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See Section 5.3 "Clock Switching" for more information.

#### 5.2.1.1 EC Mode

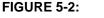

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- High power, 4-20 MHz (FOSC = 111)

- Medium power, 0.5-4 MHz (FOSC = 110)

- Low power, 0-0.5 MHz (FOSC = 101)

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

## 5.2.1.2 LP, XT, HS Modes

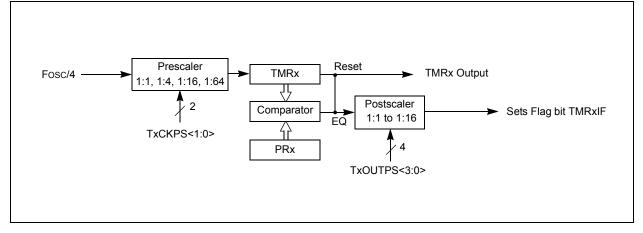

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 5-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 5-3 and Figure 5-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

| R/W-0/0<br>CCP6IE                                                                                                                                        | R/W-0/0      | R/W-0/0                                      | R/W-0/0         | R/W-0/0       | R/W-0/0         | R/W-0/0  | R/W-0/0     |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------|-----------------|---------------|-----------------|----------|-------------|--|--|--|

|                                                                                                                                                          | CCP5IE       | CCP4IE                                       | CCP3IE          | TMR6IE        | TMR5IE          | TMR4IE   | TMR3IE      |  |  |  |

| bit 7                                                                                                                                                    |              |                                              |                 |               |                 |          | bit         |  |  |  |

| Logondy                                                                                                                                                  |              |                                              |                 |               |                 |          |             |  |  |  |

| Legend:<br>R = Readable                                                                                                                                  | bit          | W = Writable                                 | hit             | II – Unimpler | nented bit read | l as '0' |             |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other F |              |                                              |                 |               |                 |          | thar Pasats |  |  |  |

| '1' = Bit is set                                                                                                                                         | langeu       | $(0)^{2} = Bit is cle$                       |                 |               |                 |          |             |  |  |  |

|                                                                                                                                                          |              |                                              | urcu            |               |                 |          |             |  |  |  |

| bit 7                                                                                                                                                    | CCP6IE: CC   | P6 Interrupt En                              | able bit        |               |                 |          |             |  |  |  |

|                                                                                                                                                          |              | the CCP6 inter<br>the CCP6 inte              | •               |               |                 |          |             |  |  |  |

| bit 6                                                                                                                                                    |              | P5 Interrupt En                              | •               |               |                 |          |             |  |  |  |

|                                                                                                                                                          |              | the CCP5 inter                               |                 |               |                 |          |             |  |  |  |

|                                                                                                                                                          | 0 = Disables | the CCP5 inte                                | rrupt           |               |                 |          |             |  |  |  |

| bit 5                                                                                                                                                    |              | P4 Interrupt En                              |                 |               |                 |          |             |  |  |  |

|                                                                                                                                                          |              | the CCP4 inter                               |                 |               |                 |          |             |  |  |  |

| L:1 4                                                                                                                                                    |              | the CCP4 inte                                | •               |               |                 |          |             |  |  |  |

| bit 4                                                                                                                                                    |              | P3 Interrupt En<br>the CCP3 inter            |                 |               |                 |          |             |  |  |  |

|                                                                                                                                                          |              | the CCP3 inte                                | •               |               |                 |          |             |  |  |  |

| bit 3                                                                                                                                                    | TMR6IE: TM   | R6 to PR6 Mat                                | ch Interrupt Er | nable bit     |                 |          |             |  |  |  |

|                                                                                                                                                          |              | the TMR6 to P                                |                 |               |                 |          |             |  |  |  |

|                                                                                                                                                          |              | 0 = Disables the TMR6 to PR6 Match interrupt |                 |               |                 |          |             |  |  |  |

| bit 2                                                                                                                                                    |              | er5 Overflow Ir                              |                 |               |                 |          |             |  |  |  |

|                                                                                                                                                          |              | the Timer5 ove<br>the Timer5 ove             |                 |               |                 |          |             |  |  |  |

| bit 1                                                                                                                                                    |              | R4 to PR4 Mat                                |                 |               |                 |          |             |  |  |  |

|                                                                                                                                                          |              | the TMR4 to P                                |                 |               |                 |          |             |  |  |  |

|                                                                                                                                                          |              | the TMR4 to F                                |                 |               |                 |          |             |  |  |  |

| bit 0                                                                                                                                                    | TMR3IE: Tim  | er3 Overflow Ir                              | nterrupt Enable | e bit         |                 |          |             |  |  |  |

|                                                                                                                                                          |              | the Timer3 ove                               |                 |               |                 |          |             |  |  |  |

|                                                                                                                                                          | 0 = Disables | the Timer3 ove                               | erriow interrup | τ             |                 |          |             |  |  |  |

| Noto: Dit                                                                                                                                                |              |                                              | must be         |               |                 |          |             |  |  |  |

|                                                                                                                                                          |              | TCON register<br>peripheral inter            |                 |               |                 |          |             |  |  |  |

# REGISTER 7-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

# 12.15 PORTG Registers

#### 12.15.1 DATA REGISTER

PORTG is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISG (Register 12-29). Setting a TRISG bit (= 1) will make the corresponding PORTG pin an input (i.e., disable the output driver). Clearing a TRISG bit (= 0) will make the corresponding PORTG pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RG5, which is input only and its TRIS bit will always read as '1'. Example 12-1 shows how to initialize an I/O port.

Reading the PORTG register (Register 12-28) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATG).

#### 12.15.2 DIRECTION CONTROL

The TRISG register (Register 12-29) controls the PORTG pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISG register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

## 12.15.3 ANALOG CONTROL

The ANSELG register (Register 12-31) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELG bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELG bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELG bits default to the Analog        |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|

|       | mode after Reset. To use any pins as         |  |  |  |  |  |  |  |

|       | digital general purpose or peripheral        |  |  |  |  |  |  |  |

|       | inputs, the corresponding ANSEL bits         |  |  |  |  |  |  |  |

|       | must be initialized to '0' by user software. |  |  |  |  |  |  |  |

# 12.15.4 PORTG FUNCTIONS AND OUTPUT PRIORITIES

Each PORTG pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-16.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority list.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RG0      | CCP3<br>RG0                      |

| RG1      | CK2<br>TX2<br>RG1                |

| RG2      | DT2<br>RG2                       |

| RG3      | CCP4<br>RG3                      |

| RG4      | CCP5<br>RG4                      |

| RG5      | Input only pin                   |

#### TABLE 12-16: PORTG OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

# 13.0 INTERRUPT-ON-CHANGE

The PORTB pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTB pin, or combination of PORTB pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

## 13.1 Enabling the Module

To allow individual PORTB pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 13.2 Individual Pin Configuration

For each PORTB pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCBPx bit of the IOCBP register is set. To enable a pin to detect a falling edge, the associated IOCBNx bit of the IOCBN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCBPx bit and the IOCBNx bit of the IOCBP and IOCBN registers, respectively.

## 13.3 Interrupt Flags

The IOCBFx bits located in the IOCBF register are status flags that correspond to the Interrupt-on-change pins of PORTB. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCBFx bits.

# 13.4 Clearing Interrupt Flags

The individual status flags, (IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

# 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCBF register will be updated prior to the first instruction executed out of Sleep.

#### 18.6.6 TIMER1/3/5 GATE EVENT INTERRUPT

When Timer1/3/5 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of TxGVAL occurs, the TMRxGIF flag bit in the PIR1 register will be set. If the TMRxGIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMRxGIF flag bit operates even when the Timer1/3/5 gate is not enabled (TMRxGE bit is cleared).

# 18.7 Timer1/3/5 Interrupt

The Timer1/3/5 register pair (TMRxH:TMRxL) increments to FFFFh and rolls over to 0000h. When Timer1/3/5 rolls over, the Timer1/3/5 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMRxON bit of the TxCON register

- TMRxIE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMRxIF bit in the Interrupt Service Routine.

Note: The TMRxH:TMRxL register pair and the TMRxIF bit should be cleared before enabling interrupts.

# 18.8 Timer1/3/5 Operation During Sleep

Timer1/3/5 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMRxON bit of the TxCON register must be set

- TMRxIE bit of the PIE1 register must be set

- · PEIE bit of the INTCON register must be set

- TxSYNC bit of the TxCON register must be set

- TMRxCS bits of the TxCON register must be configured

- SOSCEN bit of the TxCON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1/3/5 oscillator will continue to operate in Sleep regardless of the  $\overline{\text{TxSYNC}}$  bit setting.

## 18.9 ECCP/CCP Capture/Compare Time Base

The CCP module uses the TMRxH:TMRxL register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMRxH:TMRxL register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMRxH:TMRxL register pair. This event can be a Special Event Trigger.

For more information, see Section 20.0 "Capture/Compare/PWM Modules".

# 18.10 ECCP/CCP Special Event Trigger

When the CCP is configured to trigger a special event, the trigger will clear the TMRxH:TMRxL register pair. This special event does not cause a Timer1/3/5 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1/3/5.

Timer1/3/5 should be synchronized and FOSC/4 should be selected as the clock source in order to utilize the Special Event Trigger. Asynchronous operation of Timer1/3/5 can cause a Special Event Trigger to be missed.

In the event that a write to TMRxH or TMRxL coincides with a Special Event Trigger from the CCP, the write will take precedence.

For more information, see **Section 16.2.5** "**Special Event Trigger**".

# 19.0 TIMER2/4/6/8/10 MODULES

There are up to five identical Timer2-type modules available. To maintain pre-existing naming conventions, the Timers are called Timer2, Timer4, Timer6, Timer8 and Timer10 (also Timer2/4/6/8/10).

| Note: | The 'x' variable used in this section is |

|-------|------------------------------------------|

|       | used to designate Timer2, Timer4,        |

|       | Timer6, Timer8 or Timer10. For example,  |

|       | TxCON references T2CON, T4CON,           |

|       | T6CON, T8CON or T10CON. PRx              |

|       | references PR2, PR4, PR6, PR8 or PR10.   |

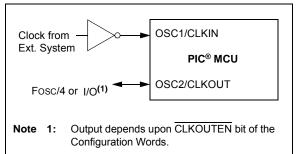

The Timer2/4/6/8/10 modules incorporate the following features:

- 8-bit Timer and Period registers (TMR2/4/6/8/10 and PR2/4/6/8/10, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2/4/6/8/10 match with PR2/4/6/8/10, respectively

- Optional use as the shift clock for the MSSPx modules (Timer2 only)

See Figure 19-1 for a block diagram of Tim-er2/4/6/8/10.

# FIGURE 19-1: TIMER2/4/6/8/10 BLOCK DIAGRAM

# 21.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a chip select known as Slave Select.

The SPI bus specifies four signal connections:

- · Serial Clock (SCKx)

- Serial Data Out (SDOx)

- Serial Data In (SDIx)

- Slave Select (SSx)

Figure 21-1 shows the block diagram of the MSSPx module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 21-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 21-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDOx output pin which is connected to, and received by, the slave's SDIx input pin. The slave device transmits information out on its SDOx output pin, which is connected to, and received by, the master's SDIx input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register.

During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on

its SDOx pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDOx pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After 8 bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

#### 21.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSPx clock is much faster than the system clock.

In Slave mode, when MSSPx interrupts are enabled, after the master completes sending data, an MSSPx interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSPx interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSPx interrupt flag bit will be set and if enabled, will wake the device.

| Name     | Bit 7                                  | Bit 6           | Bit 5         | Bit 4  | Bit 3                             | Bit 2       | Bit 1  | Bit 0  | Register<br>on Page |  |

|----------|----------------------------------------|-----------------|---------------|--------|-----------------------------------|-------------|--------|--------|---------------------|--|

| ANSELF   | ANSF7                                  | ANSF6           | ANSF5         | ANSF4  | ANSF3                             | ANSF2       | ANSF1  | ANSF0  | 130                 |  |

| INTCON   | GIE                                    | PEIE            | TMR0IE        | INTE   | IOCIE                             | TMR0IF      | INTF   | IOCIF  | 76                  |  |

| PIE1     | TMR1GIE                                | ADIE            | RC1IE         | TX1IE  | SSP1IE                            | CCP1IE      | TMR2IE | TMR1IE | 77                  |  |

| PIE4     | CCP10IE                                | CCP9IE          | RC2IE         | TX2IE  | CCP8IE                            | CCP7IE      | BCL2IE | SSP2IE | 80                  |  |

| PIR1     | TMR1GIF                                | ADIF            | RC1IF         | TX1IF  | SSP1IF                            | CCP1IF      | TMR2IF | TMR1IF | 81                  |  |

| PIR4     | CCP10IF                                | CCP9IF          | RC2IF         | TX2IF  | TX2IF CCP8IF CCP7IF BCL2IF SSP2IF |             |        | 84     |                     |  |

| SSP1BUF  | MSSPx Receive Buffer/Transmit Register |                 |               |        |                                   |             |        |        |                     |  |

| SSP2BUF  | MSSPx Reco                             | eive Buffer/Tra | ansmit Regist | er     |                                   |             |        |        | 197*                |  |

| SSP1CON1 | WCOL                                   | SSPOV           | SSPEN         | CKP    |                                   | SSPM        | <3:0>  |        | 244                 |  |

| SSP2CON1 | WCOL                                   | SSPOV           | SSPEN         | CKP    |                                   | SSPM        | <3:0>  |        | 244                 |  |

| SSP1CON3 | ACKTIM                                 | PCIE            | SCIE          | BOEN   | SDAHT                             | SBCDE       | AHEN   | DHEN   | 246                 |  |

| SSP2CON3 | ACKTIM                                 | PCIE            | SCIE          | BOEN   | SDAHT                             | SBCDE       | AHEN   | DHEN   | 246                 |  |

| SSP1STAT | SMP                                    | CKE             | D/A           | Р      | S                                 | R/W         | UA     | BF     | 242                 |  |

| SSP2STAT | SMP                                    | CKE             | D/Ā           | Р      | S                                 | S R/W UA BF |        | 242    |                     |  |

| TRISC    | TRISC7                                 | TRISC6          | TRISC5        | TRISC4 | TRISC3                            | TRISC2      | TRISC1 | TRISC0 | 120                 |  |

| TRISD    | TRISD7                                 | TRISD6          | TRISD5        | TRISD4 | TRISD3                            | TRISD2      | TRISD1 | TRISD0 | 123                 |  |

| TRISF    | TRISF7                                 | TRISF6          | TRISF5        | TRISF4 | TRISF3                            | TRISF2      | TRISF1 | TRISF0 | 129                 |  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSPx in SPI mode.

Page provides register information.

#### 21.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the 8th falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 21-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the 8th falling edge of the SCLx line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- Slave software reads ACKTIM bit of SSPxCON3 register, and R/W and D/A of the SSPxSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPxBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCLx.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

Note: <u>SSPxBUF</u> cannot be loaded until after the ACK.

13. Slave sets CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the 9th SCLx pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not  $\overline{ACK}$  the slave releases the bus allowing the master to send a Stop and end the communication.

Note: Master must send a not ACK on the last byte to ensure that the slave releases the SCLx line to receive a Stop.

| R/W-0             | R/W-0                                                                                 | R/W-0                                                                                                                                       | R/W-0          | R/W-0            | R-0                              | R-0             | R-x   |  |  |  |

|-------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|----------------------------------|-----------------|-------|--|--|--|

| SPEN              | RX9                                                                                   | SREN                                                                                                                                        | CREN           | ADDEN            | FERR                             | OERR            | RX9D  |  |  |  |

| bit 7             |                                                                                       |                                                                                                                                             |                | ·                | ·                                |                 | bit 0 |  |  |  |

|                   |                                                                                       |                                                                                                                                             |                |                  |                                  |                 |       |  |  |  |

| Legend:           |                                                                                       |                                                                                                                                             |                |                  |                                  |                 |       |  |  |  |

| R = Readable      | e bit                                                                                 | W = Writable                                                                                                                                | bit            | U = Unimpler     | mented bit, read                 | d as '0'        |       |  |  |  |

| -n = Value at POR |                                                                                       | '1' = Bit is set                                                                                                                            |                | '0' = Bit is cle | ared                             | x = Bit is unkr | nown  |  |  |  |

|                   |                                                                                       |                                                                                                                                             |                |                  |                                  |                 |       |  |  |  |

| bit 7             |                                                                                       | Port Enable bi                                                                                                                              | •              |                  |                                  |                 |       |  |  |  |

|                   | -                                                                                     | rt enabled (con<br>rt disabled (hel                                                                                                         | -              | DTx and TXx/C    | Kx pins as seria                 | al port pins)   |       |  |  |  |

| bit 6             |                                                                                       | ceive Enable b                                                                                                                              |                |                  |                                  |                 |       |  |  |  |

| DILO              | 1 = Selects 9                                                                         |                                                                                                                                             | 11             |                  |                                  |                 |       |  |  |  |

|                   | 0 = Selects 8                                                                         | •                                                                                                                                           |                |                  |                                  |                 |       |  |  |  |

| bit 5             | SREN: Single                                                                          | e Receive Enab                                                                                                                              | le bit         |                  |                                  |                 |       |  |  |  |

|                   | Asynchronou:                                                                          | <u>s mode</u> :                                                                                                                             |                |                  |                                  |                 |       |  |  |  |

|                   | Don't care                                                                            |                                                                                                                                             |                |                  |                                  |                 |       |  |  |  |

|                   | -                                                                                     | mode – Maste                                                                                                                                | <u>r</u> :     |                  |                                  |                 |       |  |  |  |

|                   |                                                                                       | single receive single receive                                                                                                               |                |                  |                                  |                 |       |  |  |  |

|                   |                                                                                       | ared after recep                                                                                                                            | otion is comp  | lete.            |                                  |                 |       |  |  |  |

|                   |                                                                                       | mode – Slave                                                                                                                                |                |                  |                                  |                 |       |  |  |  |

|                   | Don't care                                                                            |                                                                                                                                             |                |                  |                                  |                 |       |  |  |  |

| bit 4             |                                                                                       | nuous Receive                                                                                                                               | Enable bit     |                  |                                  |                 |       |  |  |  |

|                   | Asynchronous                                                                          |                                                                                                                                             |                |                  |                                  |                 |       |  |  |  |

|                   | 1 = Enables<br>0 = Disables                                                           |                                                                                                                                             |                |                  |                                  |                 |       |  |  |  |

|                   | Synchronous                                                                           |                                                                                                                                             |                |                  |                                  |                 |       |  |  |  |

|                   | 1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN) |                                                                                                                                             |                |                  |                                  |                 |       |  |  |  |

|                   | 0 = Disables                                                                          | continuous rec                                                                                                                              | eive           |                  |                                  |                 |       |  |  |  |

| bit 3             |                                                                                       | ress Detect En                                                                                                                              |                |                  |                                  |                 |       |  |  |  |

|                   |                                                                                       | s mode 9-bit (R                                                                                                                             |                |                  |                                  | "               |       |  |  |  |

|                   |                                                                                       |                                                                                                                                             |                |                  | d the receive bund ninth bit can |                 |       |  |  |  |

|                   |                                                                                       | s mode 8-bit (R                                                                                                                             | •              | are received a   |                                  |                 |       |  |  |  |

|                   | Don't care                                                                            | · ·                                                                                                                                         |                |                  |                                  |                 |       |  |  |  |

| bit 2             | FERR: Frami                                                                           | ng Error bit                                                                                                                                |                |                  |                                  |                 |       |  |  |  |

|                   | •                                                                                     | <ul> <li>1 = Framing error (can be updated by reading RCxREG register and receive next valid byte)</li> <li>0 = No framing error</li> </ul> |                |                  |                                  |                 |       |  |  |  |

| bit 1             | OERR: Overr                                                                           | -                                                                                                                                           |                |                  |                                  |                 |       |  |  |  |

|                   |                                                                                       |                                                                                                                                             | eared by clea  | aring bit CREN   | )                                |                 |       |  |  |  |

|                   | 0 = No overr                                                                          |                                                                                                                                             |                |                  |                                  |                 |       |  |  |  |

| bit 0             |                                                                                       | bit of Received                                                                                                                             |                |                  |                                  | _               |       |  |  |  |

|                   | This can be a                                                                         | ddress/data bit                                                                                                                             | or a parity bi | it and must be o | calculated by us                 | ser firmware.   |       |  |  |  |

# REGISTER 22-2: RCxSTA: RECEIVE STATUS AND CONTROL REGISTER

|        |                                   | SYNC = 0, BRGH = 1, BRG16 = 0 |       |                             |                |            |                             |                  |            |                             |      |     |

|--------|-----------------------------------|-------------------------------|-------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|------|-----|

| BAUD   | Fosc = 8.000 MHz Fosc = 4.000 MHz |                               | ) MHz | Fosc                        | : = 3.686      | 4 MHz      | Fos                         | Fosc = 1.000 MHz |            |                             |      |     |

| RATE   | Actual<br>Rate                    | al % value Actual %           |       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |      |     |

| 300    | _                                 | _                             | —     | _                           |                | _          |                             | _                | _          | 300                         | 0.16 | 207 |

| 1200   | —                                 | _                             | —     | 1202                        | 0.16           | 207        | 1200                        | 0.00             | 191        | 1202                        | 0.16 | 51  |

| 2400   | 2404                              | 0.16                          | 207   | 2404                        | 0.16           | 103        | 2400                        | 0.00             | 95         | 2404                        | 0.16 | 25  |

| 9600   | 9615                              | 0.16                          | 51    | 9615                        | 0.16           | 25         | 9600                        | 0.00             | 23         | —                           |      | —   |

| 10417  | 10417                             | 0.00                          | 47    | 10417                       | 0.00           | 23         | 10473                       | 0.53             | 21         | 10417                       | 0.00 | 5   |

| 19.2k  | 19231                             | 0.16                          | 25    | 19.23k                      | 0.16           | 12         | 19.2k                       | 0.00             | 11         | _                           | _    | _   |

| 57.6k  | 55556                             | -3.55                         | 8     | —                           | _              | _          | 57.60k                      | 0.00             | 3          | —                           | _    | _   |

| 115.2k | —                                 | _                             | _     | —                           | _              | _          | 115.2k                      | 0.00             | 1          | —                           | _    | —   |

# TABLE 22-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------|-------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz             |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 16.000 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                         | -0.01      | 4166                        | 300.0             | 0.00       | 3839                        | 300.03            | 0.01       | 3332                        | 300.0              | 0.00       | 2303                        |

| 1200   | 1200                          | -0.03      | 1041                        | 1200              | 0.00       | 959                         | 1200.5            | 0.04       | 832                         | 1200               | 0.00       | 575                         |

| 2400   | 2399                          | -0.03      | 520                         | 2400              | 0.00       | 479                         | 2398              | -0.08      | 416                         | 2400               | 0.00       | 287                         |

| 9600   | 9615                          | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9615              | 0.16       | 103                         | 9600               | 0.00       | 71                          |

| 10417  | 10417                         | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10417             | 0.00       | 95                          | 10473              | 0.53       | 65                          |

| 19.2k  | 19.23k                        | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.23k            | 0.16       | 51                          | 19.20k             | 0.00       | 35                          |

| 57.6k  | 56.818                        | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 58.82k            | 2.12       | 16                          | 57.60k             | 0.00       | 11                          |

| 115.2k | 113.636                       | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 111.11k           | -3.55      | 8                           | 115.2k             | 0.00       | 5                           |

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                  |            |                             |                |            |                             |                |            |                             |

|--------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            | Fosc = 3.6864 MHz           |                |            | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 299.9                         | -0.02      | 1666                        | 300.1            | 0.04       | 832                         | 300.0          | 0.00       | 767                         | 300.5          | 0.16       | 207                         |

| 1200   | 1199                          | -0.08      | 416                         | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202           | 0.16       | 51                          |

| 2400   | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404           | 0.16       | 25                          |

| 9600   | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | _              | _          | _                           |

| 10417  | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417          | 0.00       | 5                           |

| 19.2k  | 19.23k                        | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.20k         | 0.00       | 11                          | —              | _          | _                           |

| 57.6k  | 55556                         | -3.55      | 8                           | —                | _          | _                           | 57.60k         | 0.00       | 3                           | —              | _          | _                           |

| 115.2k | —                             | _          | _                           | —                | _          | _                           | 115.2k         | 0.00       | 1                           | —              | _          | _                           |

| RETFIE           | Return from Interrupt                                                                                                                                                                                              |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                     |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                               |  |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                            |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                               |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE<br>(INTCON<7>). This is a 2-cycle<br>instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                  |  |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                             |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                             |  |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                        |

| Operands:        | None                                                                                                                                                  |

| Operation:       | $TOS\toPC$                                                                                                                                            |

| Status Affected: | None                                                                                                                                                  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |

| RETLW                      | Return with literal in W                                                                                                                                                      | RLF                 | Rotate Left f through Carry                                                                                                                                                                                            |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                    | [ <i>label</i> ] RETLW k                                                                                                                                                      | Syntax:             | [ <i>label</i> ] RLF f,d                                                                                                                                                                                               |

| Operands:                  | $0 \le k \le 255$                                                                                                                                                             | Operands:           | $0 \le f \le 127$                                                                                                                                                                                                      |

| Operation:                 | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                  | Operation:          | $d \in [0,1]$<br>See description below                                                                                                                                                                                 |

| Status Affected:           | None                                                                                                                                                                          | Status Affected:    | С                                                                                                                                                                                                                      |

| Description:               | The W register is loaded with the 8-bit<br>literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. | Description:        | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'.      |

| Words:                     | 1                                                                                                                                                                             |                     | C Register f                                                                                                                                                                                                           |

| Cycles:<br><u>Example:</u> | 2<br>CALL TABLE;W contains table                                                                                                                                              | Words:              | 1                                                                                                                                                                                                                      |

|                            | <pre>;offset value ,W now has table value</pre>                                                                                                                               | Cycles:<br>Example: | 1<br>RLF REG1,0                                                                                                                                                                                                        |