Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 54                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 30x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1526-i-mr |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                    | LE 3-2: S              | SPECIAL I |                             | JN REG        | 191 EK 9     |               |       | NUED)    |          |                      |                                 |

|--------------------|------------------------|-----------|-----------------------------|---------------|--------------|---------------|-------|----------|----------|----------------------|---------------------------------|

| Addr               | Name                   | Bit 7     | Bit 6                       | Bit 5         | Bit 4        | Bit 3         | Bit 2 | Bit 1    | Bit 0    | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Bank               | 2                      |           |                             |               |              |               |       |          |          |                      |                                 |

| 10Ch               | LATA                   | PORTA Dat | a Latch                     |               |              |               |       |          |          | xxxx xxxx            | uuuu uuuu                       |

| 10Dh               | LATB                   | PORTB Da  | ta Latch                    |               |              |               |       |          |          | xxxx xxxx            | uuuu uuuu                       |

| 10Eh               | LATC                   | PORTC Da  | ta Latch                    |               |              |               |       |          |          | xxxx xxxx            | uuuu uuuu                       |

| 10Fh               | LATD                   | PORTD Da  | ta Latch                    |               |              |               |       |          |          | xxxx xxxx            | uuuu uuuu                       |

| 110h               | LATE                   | PORTE Da  | ta Latch                    |               |              |               |       |          |          | xxxx xxxx            | uuuu uuuu                       |

| 111h<br>to<br>115h | _                      | Unimpleme | nted                        |               |              |               |       |          |          | _                    | _                               |

| 116h               | BORCON                 | SBOREN    | BORFS                       | _             | —            | _             | _     | _        | BORRDY   | 10q                  | uuu                             |

| 117h               | FVRCON                 | FVREN     | FVRRDY                      | TSEN          | TSRNG        |               | _     | ADFV     | R<1:0>   | 0q00 0000            | 0q00 0000                       |

| 118h<br>to<br>11Ch | _                      | Unimpleme | nted                        |               |              |               |       |          |          | _                    | _                               |

| 11Dh               | APFCON                 |           | _                           | —             | —            |               |       | T3CKISEL | CCP2SEL  | 00                   | 00                              |

| 11Eh               | —                      | Unimpleme | nted                        |               |              |               |       |          |          | —                    | —                               |

| 11Fh               | —                      | Unimpleme | nted                        |               |              |               |       |          |          | _                    | _                               |

| Ban                | k 3                    |           |                             |               |              |               |       |          |          |                      |                                 |

| 18Ch               | ANSELA                 | _         | _                           | ANSA5         | —            | ANSA3         | ANSA2 | ANSA1    | ANSA0    | 1- 1111              | 1- 1111                         |

| 18Dh               | ANSELB                 | _         | _                           | ANSB5         | ANSB4        | ANSB3         | ANSB2 | ANSB1    | ANSB0    | 11 1111              | 11 1111                         |

| 18Eh               | ANSELC                 | Unimpleme | nted                        | •             |              |               |       |          |          | _                    | _                               |

| 18Fh               | ANSELD                 | _         | _                           | —             | _            | ANSD3         | ANSD2 | ANSD1    | ANSD0    | 1111                 | 1111                            |

| 190h               | ANSELE                 | _         | _                           | _             | _            |               | ANSE2 | ANSE1    | ANSE0    | 111                  | 111                             |

| 191h               | PMADRL                 | Program M | emory Addre                 | ess Register  | Low Byte     |               |       | •        |          | 0000 0000            | 0000 0000                       |

| 192h               | PMADRH                 | (2)       | Program Me                  | emory Addre   | ess Register | High Byte     |       |          |          | 1000 0000            | 1000 0000                       |

| 193h               | PMDATL                 | Program M | emory Data I                | Register Lov  | v Byte       |               |       |          |          | xxxx xxxx            | uuuu uuuu                       |

| 194h               | PMDATH                 | _         | —                           | Program M     | emory Data I | Register High | Byte  |          |          | xx xxxx              | uu uuuu                         |

| 195h               | PMCON1                 | (2)       | CFGS                        | LWLO          | FREE         | WRERR         | WREN  | WR       | RD       | 1000 x000            | 1000 q000                       |

| 196h               | PMCON2                 | Program M | emory contro                | ol register 2 |              |               |       | •        |          | 0000 0000            | 0000 0000                       |

| 197h               | VREGCON <sup>(1)</sup> | _         | —                           | —             | —            | —             | _     | VREGPM   | Reserved | 01                   | 01                              |

| 198h               | _                      | Unimpleme | nted                        |               |              |               |       |          |          | _                    | —                               |

| 199h               | RC1REG                 | USART Re  | USART Receive Data Register |               |              |               |       |          |          | 0000 0000            | 0000 0000                       |

| 19Ah               | TX1REG                 | USART Tra | nsmit Data F                | Register      |              |               |       |          |          | 0000 0000            | 0000 0000                       |

| 19Bh               | SP1BRG                 |           |                             |               | BRO          | G<7:0>        |       |          |          | 0000 0000            | 0000 0000                       |

| 19Ch               | SP1BRGH                |           |                             |               | BRG          | <15:8>        |       |          |          | 0000 0000            | 0000 0000                       |

| 19Dh               | RC1STA                 | SPEN      | RX9                         | SREN          | CREN         | ADDEN         | FERR  | OERR     | RX9D     | 0000 000x            | 0000 000x                       |

|                    | TX1STA                 | CSRC      | TX9                         | TXEN          | SYNC         | SENDB         | BRGH  | TRMT     | TX9D     | 0000 0010            | 0000 0010                       |

| 19Eh               | -                      |           |                             |               |              |               |       |          |          |                      |                                 |

TABLE 3-2: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: PIC16F1526/7 only.

2: Unimplemented, read as '1'.

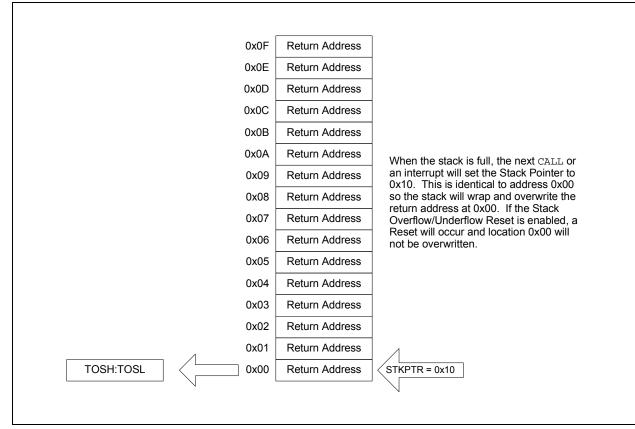

FIGURE 3-8: ACCESSING THE STACK EXAMPLE 4

# 3.7.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

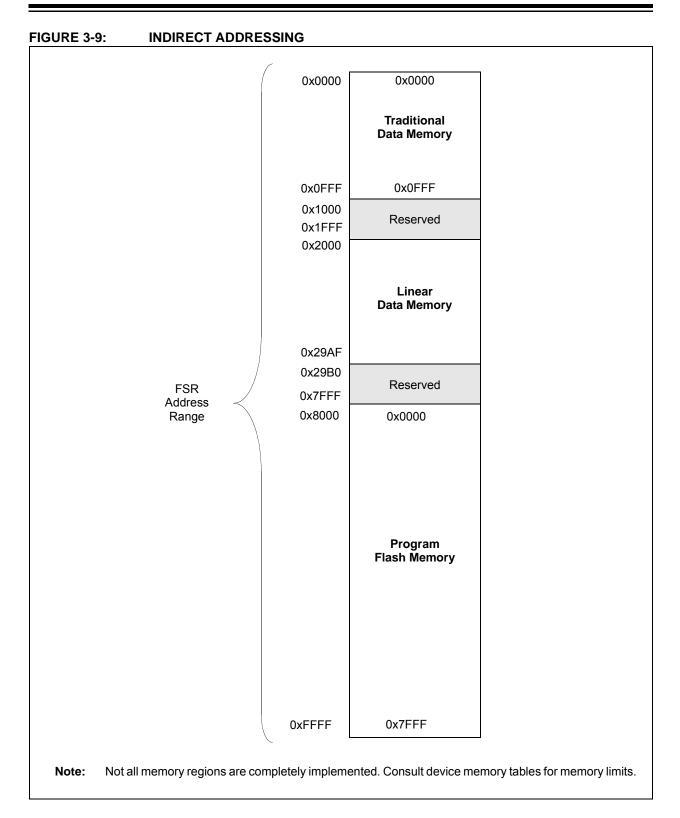

# 3.8 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- · Linear Data Memory

- Program Flash Memory

|                                                                                                                                                                                                   |                                                                                  |                                     | GUNATION                               |                          |                  |                                   |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------|----------------------------------------|--------------------------|------------------|-----------------------------------|-------|

|                                                                                                                                                                                                   |                                                                                  | R/P-1                               | R/P-1                                  | R/P-1                    | R/P-1            | R/P-1                             | U-1   |

|                                                                                                                                                                                                   |                                                                                  | LVP                                 | DEBUG                                  | LPBOR                    | BORV             | STVREN                            | —     |

|                                                                                                                                                                                                   |                                                                                  | bit 13                              |                                        |                          |                  |                                   | bit 8 |

| U-1                                                                                                                                                                                               | U-1                                                                              | U-1                                 | R/P-1                                  | U-1                      | U-1              | R/P-1                             | R/P-1 |

| 0-1                                                                                                                                                                                               | 0-1                                                                              | 0-1                                 | VCAPEN <sup>(1)</sup>                  | 0-1                      | 0-1              | WRT<                              |       |

| <br>bit 7                                                                                                                                                                                         | _                                                                                |                                     | VCAFEN                                 | _                        | _                |                                   | bit 0 |

|                                                                                                                                                                                                   |                                                                                  |                                     |                                        |                          |                  |                                   | DILU  |

| Legend:                                                                                                                                                                                           |                                                                                  |                                     |                                        |                          |                  |                                   |       |

| R = Readab                                                                                                                                                                                        | le bit                                                                           | P = Programr                        | nable bit                              | U = Unimplen             | nented bit, read | d as '1'                          |       |

| '0' = Bit is cl                                                                                                                                                                                   | eared                                                                            | '1' = Bit is set                    |                                        | •                        | en blank or aft  |                                   |       |

| 0 21010 01                                                                                                                                                                                        |                                                                                  |                                     |                                        |                          |                  |                                   |       |

| bit 13                                                                                                                                                                                            | LVP: Low-Vol                                                                     | ltage Programr                      | ning Enable bit                        |                          |                  |                                   |       |

|                                                                                                                                                                                                   | 1 = Low-volta                                                                    | ge programmir                       | ng enabled                             |                          |                  |                                   |       |

|                                                                                                                                                                                                   |                                                                                  | -                                   | nust be used fo                        | or programming           | 9                |                                   |       |

| bit 12                                                                                                                                                                                            |                                                                                  | ircuit Debugge                      |                                        |                          | F ara gaparal p  | urness I/O nins                   |       |

|                                                                                                                                                                                                   |                                                                                  |                                     |                                        |                          |                  | urpose I/O pins<br>to the debugge | r     |

| bit 11                                                                                                                                                                                            |                                                                                  | -Power BOR b                        |                                        |                          |                  |                                   |       |

| 1 = Low-Power BOR is disabled                                                                                                                                                                     |                                                                                  |                                     |                                        |                          |                  |                                   |       |

|                                                                                                                                                                                                   | 0 = Low-Power BOR is enabled                                                     |                                     |                                        |                          |                  |                                   |       |

| bit 10                                                                                                                                                                                            |                                                                                  |                                     | tage Selection                         |                          |                  |                                   |       |

|                                                                                                                                                                                                   |                                                                                  |                                     | e (Vbor), low tri<br>e (Vbor), high tr |                          |                  |                                   |       |

| bit 9                                                                                                                                                                                             |                                                                                  | -                                   | nderflow Reset                         |                          | eu.              |                                   |       |

| DIL 9                                                                                                                                                                                             |                                                                                  |                                     | flow will cause                        |                          |                  |                                   |       |

|                                                                                                                                                                                                   |                                                                                  |                                     | flow will not ca                       |                          |                  |                                   |       |

| bit 8-5                                                                                                                                                                                           | Unimplemen                                                                       | ted: Read as '                      | 1'                                     |                          |                  |                                   |       |

| bit 4                                                                                                                                                                                             | VCAPEN: Vol                                                                      | Itage Regulato                      | r Capacitor Ena                        | able bits <sup>(1)</sup> |                  |                                   |       |

|                                                                                                                                                                                                   |                                                                                  | 26/7 (regulator                     |                                        |                          |                  |                                   |       |

|                                                                                                                                                                                                   |                                                                                  | ts are ignored.<br>6/7 (regulator e | All VCAP pin fu                        | nctions are dis          | abled.           |                                   |       |

|                                                                                                                                                                                                   |                                                                                  |                                     | s enabled on R                         | E0                       |                  |                                   |       |

|                                                                                                                                                                                                   |                                                                                  | •                                   | ons are disabled                       |                          |                  |                                   |       |

| bit 3-2                                                                                                                                                                                           | Unimplemen                                                                       | ted: Read as '                      | 1'                                     |                          |                  |                                   |       |

| bit 1-0                                                                                                                                                                                           | WRT<1:0>: F                                                                      | lash Memory S                       | Self-Write Prote                       | ection bits              |                  |                                   |       |

|                                                                                                                                                                                                   |                                                                                  |                                     | ( <u>L)F1526 only)</u> :               |                          |                  |                                   |       |

|                                                                                                                                                                                                   |                                                                                  | ite protection o                    |                                        | NOb to 1EEEb m           | aav ha modifia   |                                   | ntrol |

| <ul> <li>10 = 000h to 1FFh write-protected, 200h to 1FFFh may be modified by PMCON control</li> <li>01 = 000h to FFFh write-protected, 1000h to 1FFFh may be modified by PMCON control</li> </ul> |                                                                                  |                                     |                                        |                          |                  |                                   |       |

|                                                                                                                                                                                                   | 00 = 000h to 1FFFh write-protected, no addresses may be modified by PMCON contro |                                     |                                        |                          |                  |                                   |       |

|                                                                                                                                                                                                   |                                                                                  |                                     | 6(L)F1527 only                         | <u>)</u> :               |                  |                                   |       |

|                                                                                                                                                                                                   |                                                                                  | ite protection o                    |                                        | 0h to 3EEEh m            | nav he modifier  | d by PMCON co                     | ntrol |

|                                                                                                                                                                                                   |                                                                                  |                                     |                                        |                          |                  | fied by PMCON                     |       |

|                                                                                                                                                                                                   |                                                                                  |                                     |                                        |                          |                  | d by PMCON co                     |       |

| Note 1: P                                                                                                                                                                                         | PIC16F1526/7 on                                                                  | nly.                                |                                        |                          |                  |                                   |       |

| <b>2:</b> S                                                                                                                                                                                       | See Vbor parame                                                                  | eter for specific                   | trip point voltag                      | ges.                     |                  |                                   |       |

|                                                                                                                                                                                                   |                                                                                  |                                     |                                        |                          |                  |                                   |       |

# REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2

# 12.5 PORTB Registers

### 12.5.1 DATA REGISTER

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 12-7). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 12-6) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

### 12.5.2 DIRECTION CONTROL

The TRISB register (Register 12-7) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

### 12.5.3 ANALOG CONTROL

The ANSELB register (Register 12-9) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

## 12.5.4 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority. Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in Table 12-5.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RB0      | RB0                              |

| RB1      | RB1                              |

| RB2      | RB2                              |

| RB3      | CCP2<br>RB3                      |

| RB4      | RB4                              |

| RB5      | RB5                              |

| RB6      | ICDCLK<br>RB6                    |

| RB7      | ICDDAT<br>RB7                    |

## TABLE 12-5: PORTB OUTPUT PRIORITY

**Note 1:** Priority listed from highest to lowest.

# 12.15 PORTG Registers

#### 12.15.1 DATA REGISTER

PORTG is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISG (Register 12-29). Setting a TRISG bit (= 1) will make the corresponding PORTG pin an input (i.e., disable the output driver). Clearing a TRISG bit (= 0) will make the corresponding PORTG pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RG5, which is input only and its TRIS bit will always read as '1'. Example 12-1 shows how to initialize an I/O port.

Reading the PORTG register (Register 12-28) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATG).

### 12.15.2 DIRECTION CONTROL

The TRISG register (Register 12-29) controls the PORTG pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISG register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

# 12.15.3 ANALOG CONTROL

The ANSELG register (Register 12-31) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELG bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELG bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELG bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

# 12.15.4 PORTG FUNCTIONS AND OUTPUT PRIORITIES

Each PORTG pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-16.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority list.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RG0      | CCP3<br>RG0                      |

| RG1      | CK2<br>TX2<br>RG1                |

| RG2      | DT2<br>RG2                       |

| RG3      | CCP4<br>RG3                      |

| RG4      | CCP5<br>RG4                      |

| RG5      | Input only pin                   |

#### TABLE 12-16: PORTG OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

# 12.16 Register Definitions: PORTG

#### REGISTER 12-28: PORTG: PORTG REGISTER

| U-0                  | U-0 | R-x/u              | R/W-x/u | R/W-x/u                                     | R/W-x/u          | R/W-x/u | R/W-x/u     |

|----------------------|-----|--------------------|---------|---------------------------------------------|------------------|---------|-------------|

| _                    | —   | RG5                | RG4     | RG3                                         | RG2              | RG1     | RG0         |

| bit 7                | •   | •                  |         |                                             |                  | •       | bit 0       |

|                      |     |                    |         |                                             |                  |         |             |

| Legend:              |     |                    |         |                                             |                  |         |             |

| R = Readable         | bit | W = Writable       | bit     | U = Unimpler                                | mented bit, read | as '0'  |             |

| u = Bit is unchanged |     | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all ot |                  |         | ther Resets |

| '1' = Bit is set     |     | '0' = Bit is clea  | ared    |                                             |                  |         |             |

bit 7-6

Unimplemented: Read as '0'

bit 5-0

RG<5:0>: PORTG I/O Pin bits<sup>(1)</sup>

1 = Port pin is > VIH

0 = Port pin is < VIL

**Note 1:** Writes to PORTG are actually written to corresponding LATG register. Reads from PORTG register is return of actual I/O pin values.

### REGISTER 12-29: TRISG: PORTG TRI-STATE REGISTER

| U-0   | U-0 | U-1 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | (1) | TRISG4 | TRISG3 | TRISG2 | TRISG1 | TRISG0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 Unimplemented: Read as ' | 0' |

|----------------------------------|----|

|----------------------------------|----|

bit 5 Unimplemented: Read as '1'

bit 4-0 **TRISG<4:0>:** RG<4:0> Tri-State Control bits<sup>(1)</sup> 1 = PORTG pin configured as an input (tri-stated) 0 = PORTG pin configured as an output

Note 1: Unimplemented, read as '1'.

### 17.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |

|-------|---------------------------------------|

|       | independent prescaler.                |

There are 8 prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

# 17.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

# 17.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 25.0** "**Electrical Specifications**".

# 17.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

| TABLE 20-5: | SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE |

|-------------|----------------------------------------------|

|-------------|----------------------------------------------|

| Bit 4                                                                     |                                    | Bit 0                                                  | Register on<br>Page                                              |  |  |

|---------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------|------------------------------------------------------------------|--|--|

| _                                                                         | CP2SEL 11                          | CCP2SEL                                                | 112                                                              |  |  |

| DC1B<1:0> CCP1M<3:0>                                                      |                                    |                                                        | 189                                                              |  |  |

| — — DC2B<1:0>                                                             |                                    |                                                        | 189                                                              |  |  |

| B<1:0>                                                                    | 18                                 |                                                        | 189                                                              |  |  |

| B<1:0>                                                                    | 18                                 |                                                        | 189                                                              |  |  |

| B<1:0>                                                                    | 18                                 |                                                        | 189                                                              |  |  |

| B<1:0>                                                                    | 18                                 |                                                        | 189                                                              |  |  |

| B<1:0>                                                                    | 18                                 |                                                        | 189                                                              |  |  |

| B<1:0>                                                                    | 18                                 |                                                        | 189                                                              |  |  |

| B<1:0>                                                                    | 18                                 |                                                        | 189                                                              |  |  |

| B<1:0>                                                                    | 18                                 |                                                        | 189                                                              |  |  |

| yte (LSB)                                                                 | 17                                 |                                                        | 176*                                                             |  |  |

| yte (LSB)                                                                 | 17                                 |                                                        | 176*                                                             |  |  |

| yte (LSB)                                                                 | 17                                 |                                                        | 176*                                                             |  |  |

| yte (LSB)                                                                 | 17                                 |                                                        | 176*                                                             |  |  |

| syte (LSB)                                                                | 17                                 |                                                        | 176*                                                             |  |  |

| syte (LSB)                                                                | 17                                 |                                                        | 176*                                                             |  |  |

| yte (LSB)                                                                 | 17                                 |                                                        | 176*                                                             |  |  |

| syte (LSB)                                                                | 17                                 |                                                        | 176*                                                             |  |  |

| syte (LSB)                                                                | 17                                 |                                                        | 176*                                                             |  |  |

| Byte (LSB)                                                                | 17                                 |                                                        | 176*                                                             |  |  |

| Capture/Compare/PWM Register 1 High Byte (MSB)                            |                                    |                                                        |                                                                  |  |  |

| Capture/Compare/PWM Register 2 High Byte (MSB)                            |                                    |                                                        |                                                                  |  |  |

| Capture/Compare/PWM Register 3 High Byte (MSB)                            |                                    |                                                        |                                                                  |  |  |

| Capture/Compare/PWM Register 4 High Byte (MSB)                            |                                    |                                                        |                                                                  |  |  |

| Capture/Compare/PWM Register 5 High Byte (MSB)                            |                                    |                                                        |                                                                  |  |  |

| Capture/Compare/PWM Register 6 High Byte (MSB)                            |                                    |                                                        |                                                                  |  |  |

| Capture/Compare/PWM Register 7 High Byte (MSB)                            |                                    |                                                        |                                                                  |  |  |

| Capture/Compare/PWM Register 8 High Byte (MSB)                            |                                    |                                                        |                                                                  |  |  |

| Capture/Compare/PWM Register 9 High Byte (MSB)                            |                                    |                                                        |                                                                  |  |  |

| Byte (MSB)                                                                |                                    |                                                        | 176*                                                             |  |  |

| INTE                                                                      |                                    | IOCIF                                                  | 176*                                                             |  |  |

| TX1IE                                                                     |                                    | TMR1IE                                                 | 76                                                               |  |  |

| TAIL                                                                      |                                    | CCP2IE                                                 | 77                                                               |  |  |

| CCP3IE                                                                    |                                    | TMR3IE                                                 | 78<br>79                                                         |  |  |

| TX2IE                                                                     |                                    | SSP2IE                                                 | -                                                                |  |  |

| TX1IF                                                                     |                                    | TMR1IF                                                 | 80                                                               |  |  |

|                                                                           |                                    | CCP2IF                                                 | 81                                                               |  |  |

| CCP3IF                                                                    |                                    | TMR3IF                                                 | 82                                                               |  |  |

| TX2IF                                                                     |                                    | SSP2IF                                                 | 83                                                               |  |  |

|                                                                           |                                    | TMR10N                                                 | 84                                                               |  |  |

| TMR1CS<1:0>         T1CKPS<1:0>           TMR3CS<1:0>         T3CKPS<1:0> |                                    |                                                        | 168                                                              |  |  |

| PS<1:0>                                                                   |                                    | TMR3ON<br>TMR5ON                                       | 168                                                              |  |  |

| 1                                                                         |                                    |                                                        | 168                                                              |  |  |

|                                                                           |                                    |                                                        | 169<br>169                                                       |  |  |

|                                                                           | TIGSPM TIGGO/DONE TIGVAL TIGSS<1:( | T1GSPMT1GGO/DONET1GVALT1GSST3GSPMT3GGO/DONET3GVALT3GSS | T1GSPMT1GGO/DONET1GVALT1GSS<1:0>T3GSPMT3GGO/DONET3GVALT3GSS<1:0> |  |  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Compare mode. \* Page provides register information.

| R/W-0/0          | R/W-0/0                                                                                                                                  | R/W-0/0                     | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|----------------|------------------|------------------|--------------|--|

| C4TSEL<1:0>      |                                                                                                                                          | C3TSE                       | L<1:0>          | C2TSE          | L<1:0>           | C1TSE            | L<1:0>       |  |

| bit 7            |                                                                                                                                          |                             |                 |                |                  |                  | bit          |  |

|                  |                                                                                                                                          |                             |                 |                |                  |                  |              |  |

| Legend:          |                                                                                                                                          |                             |                 |                |                  |                  |              |  |

| R = Readable     | bit                                                                                                                                      | W = Writable                | bit             | U = Unimplen   | nented bit, read | d as '0'         |              |  |

| u = Bit is unch  | nanged                                                                                                                                   | x = Bit is unkr             | nown            | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |

| '1' = Bit is set |                                                                                                                                          | '0' = Bit is cle            | ared            |                |                  |                  |              |  |

|                  |                                                                                                                                          |                             |                 |                |                  |                  |              |  |

| bit 7-6          | C4TSEL<1:0                                                                                                                               | D>: CCP4 Time               | Selection bits  | i              |                  |                  |              |  |

|                  | -                                                                                                                                        | oture/Compare               |                 |                |                  |                  |              |  |

|                  |                                                                                                                                          | s based off Tim             |                 |                |                  |                  |              |  |

|                  |                                                                                                                                          | s based off Time            | er1 in Capture  | Compare mode   | 9                |                  |              |  |

|                  | When in PW                                                                                                                               |                             |                 |                |                  |                  |              |  |

|                  | 11 = Reserve                                                                                                                             | eu<br>s based off Tim       | er6 in PWM m    | ode            |                  |                  |              |  |

|                  |                                                                                                                                          | s based off Time            |                 |                |                  |                  |              |  |

|                  | 00 <b>= CCP4 i</b>                                                                                                                       | s based off Time            | er2 in PWM m    | ode            |                  |                  |              |  |

| bit 5-4          |                                                                                                                                          | D>: CCP3 Time               |                 | i              |                  |                  |              |  |

|                  | When in Capture/Compare mode:                                                                                                            |                             |                 |                |                  |                  |              |  |

|                  | x1 = CCP3 is based off Timer3 in Capture/Compare mode                                                                                    |                             |                 |                |                  |                  |              |  |

|                  | x0 = CCP3 is based off Timer1 in Capture/Compare mode<br>When in PWM mode:                                                               |                             |                 |                |                  |                  |              |  |

|                  | 11 = Reserv                                                                                                                              |                             |                 |                |                  |                  |              |  |

|                  |                                                                                                                                          | s based off Tim             | er6 in PWM m    | ode            |                  |                  |              |  |

|                  |                                                                                                                                          | s based off Time            |                 |                |                  |                  |              |  |

|                  | 00 <b>= CCP3</b> is                                                                                                                      | s based off Time            | er2 in PWM m    | ode            |                  |                  |              |  |

| bit 3-2          |                                                                                                                                          | D>: CCP2 Time               |                 | i              |                  |                  |              |  |

| When in          |                                                                                                                                          | oture/Compare               |                 |                |                  |                  |              |  |

|                  | <ul> <li>x1 = CCP2 is based off Timer3 in Capture/Compare mode</li> <li>x0 = CCP2 is based off Timer1 in Capture/Compare mode</li> </ul> |                             |                 |                |                  |                  |              |  |

|                  | $x_0 = CCP2$ is<br>When in PW                                                                                                            |                             | er'i in Capture | Compare mode   | 9                |                  |              |  |

|                  | 11 = Reserv                                                                                                                              |                             |                 |                |                  |                  |              |  |

|                  |                                                                                                                                          | eu<br>s based off Tim       | er6 in PWM m    | ode            |                  |                  |              |  |

|                  | 01 = CCP2 is                                                                                                                             | s based off Time            | er4 in PWM m    | ode            |                  |                  |              |  |

|                  | 00 <b>= CCP2</b> i                                                                                                                       | s based off Time            | er2 in PWM m    | ode            |                  |                  |              |  |

| bit 1-0          |                                                                                                                                          | D>: CCP1 Time               |                 | ;              |                  |                  |              |  |

|                  | <u>When in Capture/Compare mode</u> :<br>x1 = CCP1 is based off Timer3 in Capture/Compare mode                                           |                             |                 |                |                  |                  |              |  |

|                  |                                                                                                                                          |                             |                 |                |                  |                  |              |  |

|                  | $x_0 = CCPT$                                                                                                                             | s based off Time<br>M mode: | er i in Capture | Compare mode   | 5                |                  |              |  |

|                  | 11 = Reserve                                                                                                                             |                             |                 |                |                  |                  |              |  |

|                  |                                                                                                                                          | s based off Tim             | er6 in PWM m    | ode            |                  |                  |              |  |

|                  |                                                                                                                                          | s based off Time            |                 |                |                  |                  |              |  |

|                  | 00 = CCP1 i                                                                                                                              |                             |                 |                |                  |                  |              |  |

# REGISTER 20-2: CCPTMRS0: CCP TIMER SELECTION CONTROL REGISTER 0

The  $\mathsf{I}^2\mathsf{C}$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- 7-bit and 10-bit addressing

- Start and Stop interrupts

- Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- Address masking

- Address Hold and Data Hold modes

- Selectable SDAx hold times

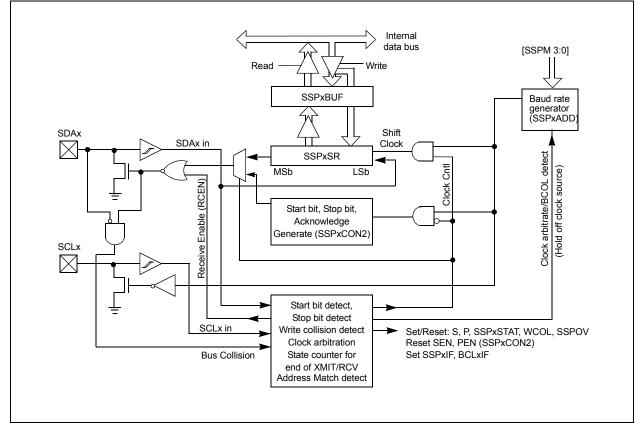

Figure 21-2 is a block diagram of the  $I^2C$  Interface module in Master mode. Figure 21-3 is a diagram of the  $I^2C$  interface module in Slave mode.

The PIC16F1527 has two MSSP modules, MSSP1 and MSSP2, each module operating independently from the other.

- Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSP1CON1 and SSP1CON2 registers control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

- 2: Throughout this section, generic references to an MSSP module in any of its operating modes may be interpreted as being equally applicable to MSSP1 or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

# FIGURE 21-2: MSSPX BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

© 2011-2015 Microchip Technology Inc.

# 21.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSPx interrupt is enabled).

# 21.6.11 EFFECTS OF A RESET

A Reset disables the MSSPx module and terminates the current transfer.

# 21.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSPx module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPxSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSPx interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDAx line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- Address Transfer

- · Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

## 21.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF and reset the I<sup>2</sup>C port to its Idle state (Figure 21-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

# FIGURE 24-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations 13 8 7 6                                       | 0        |

|---------------------------------------------------------------------------------------|----------|

| OPCODE d f(FILE                                                                       | -        |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |          |

| Bit-oriented file register operations 13 10 9 7 6                                     | 0        |

| OPCODE b (BIT #) f (FIL                                                               |          |

| b = 3-bit bit address<br>f = 7-bit file register address                              |          |

| Literal and control operations                                                        |          |

| General                                                                               |          |

| 13 8 7                                                                                | 0        |

| OPCODE k (liter                                                                       | al)      |

| k = 8-bit immediate value                                                             |          |

| CALL and GOTO instructions only                                                       |          |

|                                                                                       | 0        |

| OPCODE k (literal)                                                                    |          |

| k = 11-bit immediate value MOVLP instruction only                                     |          |

| 13 7 6                                                                                | 0        |

| OPCODE k (liter                                                                       | al)      |

| k = 7-bit immediate value                                                             |          |

| 13 5 4                                                                                | 0        |

| OPCODE k (lit                                                                         | teral)   |

| k = 5-bit immediate value                                                             |          |

| BRA instruction only<br>13 9 8                                                        | 0        |

| OPCODE k (liter                                                                       | al)      |

| k = 9-bit immediate value                                                             |          |

| FSR Offset instructions<br>13 7 6 5                                                   | 0        |

| OPCODE n k (lit                                                                       | teral)   |

| n = appropriate FSR<br>k = 6-bit immediate value                                      |          |

| FSR Increment instructions<br>13 3 2                                                  | 1 0      |

| OPCODE n I                                                                            | m (mode) |

| n = appropriate FSR<br>m = 2-bit mode value                                           |          |

| OPCODE only<br>13                                                                     | 0        |

| OPCODE                                                                                |          |

|                                                                                       |          |

| Mnemonic,<br>Operands |      | Description                                   | Cycles | 14-Bit Opcode |      |      |      | Status   | Notes |

|-----------------------|------|-----------------------------------------------|--------|---------------|------|------|------|----------|-------|

|                       |      | Description                                   | Cycles | MSb           |      |      | LSb  | Affected | Notes |

|                       |      | CONTROL OPERA                                 | TIONS  |               |      |      |      |          |       |

| BRA                   | k    | Relative Branch                               | 2      | 11            | 001k | kkkk | kkkk |          |       |

| BRW                   | _    | Relative Branch with W                        | 2      | 00            | 0000 | 0000 | 1011 |          |       |

| CALL                  | k    | Call Subroutine                               | 2      | 10            | 0kkk | kkkk | kkkk |          |       |

| CALLW                 | -    | Call Subroutine with W                        | 2      | 00            | 0000 | 0000 | 1010 |          |       |

| GOTO                  | k    | Go to address                                 | 2      | 10            | 1kkk | kkkk | kkkk |          |       |

| RETFIE                | k    | Return from interrupt                         | 2      | 00            | 0000 | 0000 | 1001 |          |       |