Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 54                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1.5К х 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 30x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1527-e-mr |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

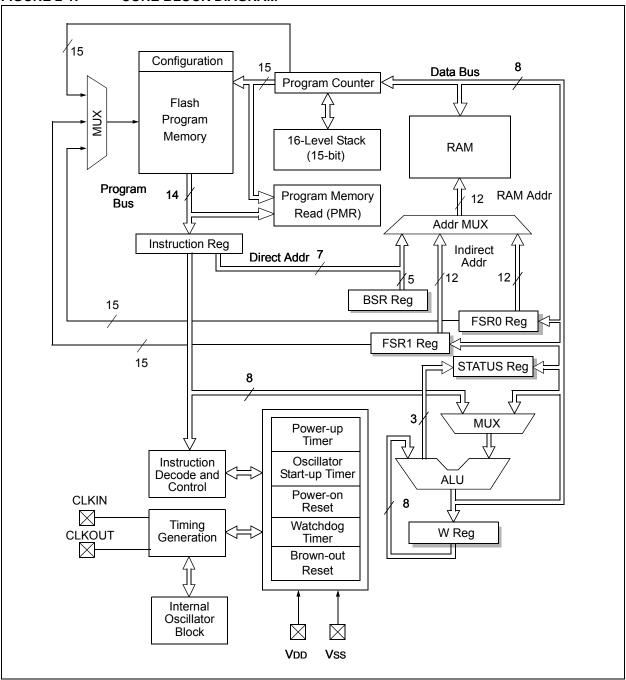

# 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative Addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

FIGURE 2-1: CORE BLOCK DIAGRAM

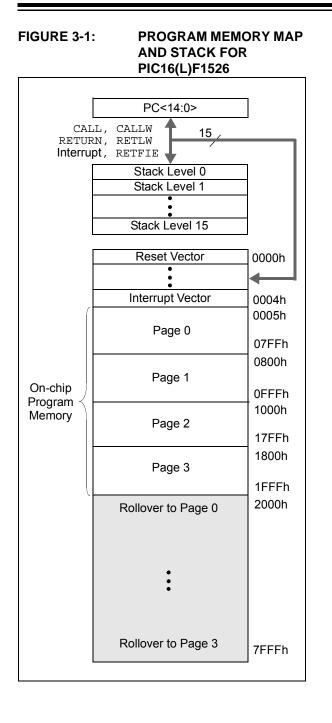

FIGURE 3-2: PROGRAM MEMORY MAP AND STACK FOR PIC16(L)F1527

# 3.5.4 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-4 can be addressed from any Bank.

| Addr                                                                                                                            | Name                      | Bit 7        | Bit 6                      | Bit 5         | Bit 4            | Bit 3        | Bit 2  | Bit 1 | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

|---------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------|----------------------------|---------------|------------------|--------------|--------|-------|-----------|----------------------|---------------------------|

| Bank                                                                                                                            | 0-31                      |              |                            |               |                  |              |        |       |           |                      |                           |

| x00h or<br>x80h INDF0 Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |                           |              |                            |               |                  |              |        |       | xxxx xxxx | uuuu uuuu            |                           |

| x01h or<br>x81h INDF1 Addressing this location uses contents of FSR1H/FSR1L to address data memory<br>(not a physical register) |                           |              |                            |               |                  |              |        |       | xxxx xxxx | uuuu uuuu            |                           |

| x02h or<br>x82h                                                                                                                 | PCL                       | Program Co   | ounter (PC) I              | Least Signifi | cant Byte        |              |        |       |           | 0000 0000            | 0000 0000                 |

| x03h or<br>x83h                                                                                                                 | STATUS                    | _            | <u>TO</u> <u>PD</u> Z DC C |               |                  |              |        |       | 1 1000    | q quuu               |                           |

| x04h or<br>x84h FSR0L Indirect Data Memory Address 0 Low Pointer                                                                |                           |              |                            |               |                  |              |        |       | 0000 0000 | uuuu uuuu            |                           |

| x05h or<br>x85h                                                                                                                 | FSR0H                     | Indirect Dat | ta Memory A                | ddress 0 Hig  | gh Pointer       |              |        |       |           | 0000 0000            | 0000 0000                 |

| x06h or<br>x86h                                                                                                                 | FSR1L                     | Indirect Dat | ta Memory A                | ddress 1 Lo   | w Pointer        |              |        |       |           | 0000 0000            | uuuu uuuu                 |

| x07h or<br>x87h                                                                                                                 | FSR1H                     | Indirect Dat | ta Memory A                | ddress 1 Hig  | gh Pointer       |              |        |       |           | 0000 0000            | 0000 0000                 |

| x08h or<br>x88h                                                                                                                 | BSR                       | _            | -                          | -             | BSR4             | BSR3         | BSR2   | BSR1  | BSR0      | 0 0000               | 0 0000                    |

| x09h or<br>x89h                                                                                                                 | IN/REC IN/orking Register |              |                            |               |                  |              |        |       |           | 0000 0000            | uuuu uuuu                 |

| x0Ahor<br>x8Ah                                                                                                                  | PCLATH                    | _            | Write Buffer               | for the uppe  | er 7 bits of the | e Program Co | ounter |       |           | -000 0000            | -000 0000                 |

| x0Bhor<br>x8Bh                                                                                                                  | INTCON                    | GIE          | PEIE                       | TMR0IE        | INTE             | IOCIE        | TMR0IF | INTF  | IOCIF     | 0000 0000            | 0000 0000                 |

# TABLE 3-4: CORE FUNCTION REGISTERS SUMMARY

| U-0              | R/W-0/0      | U-0                                | U-0            | R/W-0/0           | R/W-0/0          | R/W-0/0           | U-0        |

|------------------|--------------|------------------------------------|----------------|-------------------|------------------|-------------------|------------|

|                  | AD2IE        |                                    |                | BCL1IE            | BCL2IE           | TMR4IE            |            |

| bit 7            |              |                                    |                |                   |                  |                   | bit (      |

|                  |              |                                    |                |                   |                  |                   |            |

| Legend:          |              |                                    |                |                   |                  |                   |            |

| R = Readable     | bit          | W = Writable                       | bit            | U = Unimplen      | nented bit, read | l as '0'          |            |

| u = Bit is unch  | anged        | x = Bit is unkn                    | own            | -n/n = Value a    | at POR and BO    | R/Value at all ot | her Resets |

| '1' = Bit is set |              | '0' = Bit is clea                  | ared           |                   |                  |                   |            |

| L:4 7            |              | n ( a de Da a al a a fé            | .,             |                   |                  |                   |            |

| bit 7            | •            | nted: Read as '                    |                |                   | 1.1. 1.9         |                   |            |

| bit 6            |              | 0 0                                | ``             | C2) Interrupt Ena | adie dit         |                   |            |

|                  |              | the ADC interru<br>the ADC interru |                |                   |                  |                   |            |

| bit 5-4          |              | nted: Read as '                    |                |                   |                  |                   |            |

| bit 3            | BCL1IE: MS   | SP1 Bus Collisi                    | on Interrupt   | Enable bit        |                  |                   |            |

|                  | 1 = Enables  | the MSSP1 Bu                       | s Collision Ir | nterrupt          |                  |                   |            |

|                  | 0 = Disable  | s the MSSP1 Bu                     | s Collision I  | nterrupt          |                  |                   |            |

| bit 2            | BCL2IE: MS   | SP2 Bus Collisi                    | on Interrupt   | Enable bit        |                  |                   |            |

|                  |              | the MSSP2 Bus<br>the MSSP2 Bu      |                |                   |                  |                   |            |

| bit 1            |              | IR4 to PR4 Mate                    |                | •                 |                  |                   |            |

|                  |              | the Timer8 to Pl                   |                |                   |                  |                   |            |

|                  | 0 = Disables | the Timer8 to P                    | R4 match ir    | iterrupt          |                  |                   |            |

| bit 0            | Unimpleme    | nted: Read as 'd                   | )'             |                   |                  |                   |            |

|                  | ommpleme     |                                    | J              |                   |                  |                   |            |

|                  |              | NTCON register<br>peripheral inter |                |                   |                  |                   |            |

# REGISTER 7-3: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| U-0          | R/W-0/0                               | U-0                       | U-0             | R/W-0/0        | R/W-0/0          | R/W-0/0           | U-0        |

|--------------|---------------------------------------|---------------------------|-----------------|----------------|------------------|-------------------|------------|

| _            | AD2IF                                 | _                         | _               | BCL1IF         | BCL2IF           | TMR4IF            | _          |

| bit 7        |                                       |                           |                 |                |                  |                   | bit C      |

|              |                                       |                           |                 |                |                  |                   |            |

| Legend:      |                                       |                           |                 |                |                  |                   |            |

| R = Read     | able bit                              | W = Writable              | bit             | U = Unimpler   | nented bit, reac | l as '0'          |            |

| u = Bit is   | unchanged                             | x = Bit is unkr           | nown            | -n/n = Value a | at POR and BO    | R/Value at all ot | her Resets |

| '1' = Bit is | set                                   | '0' = Bit is cle          | ared            |                |                  |                   |            |

|              |                                       |                           |                 |                |                  |                   |            |

| bit 7        | Unimpleme                             | nted: Read as '           | 0'              |                |                  |                   |            |

| bit 6        |                                       | er5 Gate Interrup         | ot Flag bit     |                |                  |                   |            |

|              | 1 = Interrupt                         | is pending is not pending |                 |                |                  |                   |            |

| bit 5-4      |                                       | nted: Read as '           | 0'              |                |                  |                   |            |

| bit 3        | •                                     | SP1 Bus Collisi           |                 | -log bit       |                  |                   |            |

| DIL 3        | 1 = Interrupt                         |                           | on menupi       | lay bit        |                  |                   |            |

|              |                                       | is not pending            |                 |                |                  |                   |            |

| bit 2        | BCL2IF: MS                            | SP2 Bus Collisi           | on Interrupt F  | -lag bit       |                  |                   |            |

|              | 1 = Interrupt                         | is pending                |                 |                |                  |                   |            |

|              | •                                     | is not pending            |                 |                |                  |                   |            |

| bit 1        |                                       | ner4 to PR4 Inte          | errupt Flag bit | t              |                  |                   |            |

|              | 1 = Interrupt                         | is pending is not pending |                 |                |                  |                   |            |

| bit 0        |                                       | nted: Read as '           | 0'              |                |                  |                   |            |

| DILU         | Uninpienie                            | nieu. Reau as             | 0               |                |                  |                   |            |

|              |                                       |                           |                 |                |                  |                   |            |

| Note:        | Interrupt flag bits condition occurs, |                           |                 |                |                  |                   |            |

|              | its corresponding                     |                           |                 |                |                  |                   |            |

|              | Enable bit, GIE,                      | of the INTCON             | register.       |                |                  |                   |            |

|              | User software                         | should ensu               | ure the         |                |                  |                   |            |

# REGISTER 7-7: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

appropriate interrupt flag bits are clear prior

to enabling an interrupt.

| R/W-0/       | 0 R/W-0/0                         | R/W-0/0                                             | R/W-0/0                                | R/W-0/0      | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |  |

|--------------|-----------------------------------|-----------------------------------------------------|----------------------------------------|--------------|------------------|------------------|--------------|--|--|--|--|

| CCP6I        | F CCP5IF                          | CCP4IF                                              | CCP3IF                                 | TMR6IF       | TMR5IF           | TMR4IF           | TMR3IF       |  |  |  |  |

| bit 7        |                                   |                                                     |                                        |              |                  |                  | bit C        |  |  |  |  |

|              |                                   |                                                     |                                        |              |                  |                  |              |  |  |  |  |

| Legend:      |                                   |                                                     |                                        |              |                  |                  |              |  |  |  |  |

| R = Reada    | able bit                          | W = Writable                                        | bit                                    | •            | mented bit, read |                  |              |  |  |  |  |

| u = Bit is ι | inchanged                         | x = Bit is unki                                     | nown                                   | -n/n = Value | at POR and BO    | R/Value at all c | other Resets |  |  |  |  |

| '1' = Bit is | set                               | '0' = Bit is cle                                    | ared                                   |              |                  |                  |              |  |  |  |  |

| bit 7        | CCP6IF: CC                        | P6 Interrupt Fla                                    | a bit                                  |              |                  |                  |              |  |  |  |  |

|              | 1 = Interrupt                     |                                                     | 3                                      |              |                  |                  |              |  |  |  |  |

|              |                                   | is not pending                                      |                                        |              |                  |                  |              |  |  |  |  |

| bit 6        | CCP5IF: CC                        | P5 Interrupt Fla                                    | ig bit                                 |              |                  |                  |              |  |  |  |  |

|              | 1 = Interrupt                     | is pending                                          |                                        |              |                  |                  |              |  |  |  |  |

|              | •                                 | is not pending                                      |                                        |              |                  |                  |              |  |  |  |  |

| bit 5        | CCP4IF: CC                        | P4 Interrupt Fla                                    | ıg bit                                 |              |                  |                  |              |  |  |  |  |

|              | 1 = Interrupt                     |                                                     |                                        |              |                  |                  |              |  |  |  |  |

| 1.11.4       | •                                 | is not pending                                      |                                        |              |                  |                  |              |  |  |  |  |

| bit 4        |                                   | P3 Interrupt Fla                                    | ig dit                                 |              |                  |                  |              |  |  |  |  |

|              | 1 = Interrupt<br>0 = Interrupt    | is not pending                                      |                                        |              |                  |                  |              |  |  |  |  |

| bit 3        |                                   | <b>TMR6IF:</b> TMR6 to PR6 Match Interrupt Flag bit |                                        |              |                  |                  |              |  |  |  |  |

|              | 1 = Interrupt                     |                                                     | •••••••••••••••••••••••••••••••••••••• |              |                  |                  |              |  |  |  |  |

|              |                                   | is not pending                                      |                                        |              |                  |                  |              |  |  |  |  |

| bit 2        | TMR5IF: Tim                       | ner5 Overflow Ir                                    | nterrupt Flag b                        | it           |                  |                  |              |  |  |  |  |

|              | 1 = Interrupt                     |                                                     |                                        |              |                  |                  |              |  |  |  |  |

|              | -                                 | is not pending                                      |                                        |              |                  |                  |              |  |  |  |  |

| bit 1        |                                   | R4 to PR4 Mate                                      | ch Interrupt Fla                       | ag bit       |                  |                  |              |  |  |  |  |

|              | 1 = Interrupt                     |                                                     |                                        |              |                  |                  |              |  |  |  |  |

| hit 0        | •                                 | is not pending                                      | torrupt Flog b                         | :4           |                  |                  |              |  |  |  |  |

| bit 0        | 1 = Interrupt                     | er3 Overflow Ir                                     | iterrupt Flag b                        | IL           |                  |                  |              |  |  |  |  |

|              |                                   | is not pending                                      |                                        |              |                  |                  |              |  |  |  |  |

|              | • <b></b>                         | ie net penang                                       |                                        |              |                  |                  |              |  |  |  |  |

| Note:        | Interrupt flag bits a             | are set when an                                     | interrupt                              |              |                  |                  |              |  |  |  |  |

|              | condition occurs,                 |                                                     |                                        |              |                  |                  |              |  |  |  |  |

|              | its corresponding                 |                                                     |                                        |              |                  |                  |              |  |  |  |  |

|              | Enable bit, GIE,<br>User software | should ensi                                         |                                        |              |                  |                  |              |  |  |  |  |

|              | appropriate interru               |                                                     |                                        |              |                  |                  |              |  |  |  |  |

|              | to enabling an inte               |                                                     |                                        |              |                  |                  |              |  |  |  |  |

# REGISTER 7-8: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

# **10.1** Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 25.0 "Electrical Specifications"** for the LFINTOSC tolerances.

### **10.2 WDT Operating Modes**

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 10-1.

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |  |  |  |  |  |  |

|-----------|--------|----------------|-------------|--|--|--|--|--|--|

| 11        | Х      | х              | Active      |  |  |  |  |  |  |

| 10        |        | Awake          | Active      |  |  |  |  |  |  |

|           | X      | Sleep          | Disabled    |  |  |  |  |  |  |

| 0.1       | 1      | х              | Active      |  |  |  |  |  |  |

| 01        | 0      | х              | Disabled    |  |  |  |  |  |  |

| 00        | х      | Х              | Disabled    |  |  |  |  |  |  |

|           |        |                |             |  |  |  |  |  |  |

### TABLE 10-2: WDT CLEARING CONDITIONS

#### 10.3 Time-out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is 2 seconds.

# 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 10-2 for more information.

# 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 5.0** "Oscillator **Module (with Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See **Section 3.0** "Memory Organization" and The STATUS register (Register 3-1) for more information.

| WDT                          |  |  |  |  |  |  |  |

|------------------------------|--|--|--|--|--|--|--|

|                              |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |

| Cleared                      |  |  |  |  |  |  |  |

| Cleared                      |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |

| Cleared until the end of OST |  |  |  |  |  |  |  |

| Unaffected                   |  |  |  |  |  |  |  |

|                              |  |  |  |  |  |  |  |

# TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

| Name   | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0  | Register<br>on Page |

|--------|-------|-------|------------|-------|-------|-------|----------|--------|---------------------|

| OSCCON | —     |       | IRCF<3:0>  |       |       |       | SCS<1:0> |        | 61                  |

| STATUS | —     | —     | —          | TO    | PD    | Z     | DC       | С      | 21                  |

| WDTCON | —     | —     | WDTPS<4:0> |       |       |       |          | SWDTEN | 93                  |

# TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|------------|---------|---------|---------------------|

| CONFIG1 | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |         | —       | 40                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | =<1:0>   | FOSC<2:0>  |         |         | 43                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

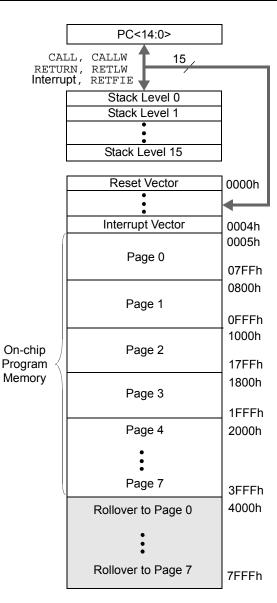

# 12.0 I/O PORTS

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

Each port has three standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- · LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

# TABLE 12-1:PORT AVAILABILITY PER<br/>DEVICE

| Device        | PORTA | PORTB | PORTC | PORTD | PORTE | PORTF | PORTG |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| PIC16(L)F1526 | ٠     | •     | •     | •     | •     | •     | •     |

| PIC16(L)F1527 | •     | ٠     | ٠     | ٠     | ٠     | ٠     | ٠     |

The Data Latch (LATA register) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATA register has the same effect as a write to the corresponding PORTA register. A read of the LATA register reads of the values held in the I/O PORT latches, while a read of the PORTA register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

### FIGURE 12-1: GENERIC I/O PORT OPERATION

# 13.0 INTERRUPT-ON-CHANGE

The PORTB pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTB pin, or combination of PORTB pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

# 13.1 Enabling the Module

To allow individual PORTB pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

# 13.2 Individual Pin Configuration

For each PORTB pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCBPx bit of the IOCBP register is set. To enable a pin to detect a falling edge, the associated IOCBNx bit of the IOCBN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCBPx bit and the IOCBNx bit of the IOCBP and IOCBN registers, respectively.

# 13.3 Interrupt Flags

The IOCBFx bits located in the IOCBF register are status flags that correspond to the Interrupt-on-change pins of PORTB. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCBFx bits.

# 13.4 Clearing Interrupt Flags

The individual status flags, (IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

# EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

# 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCBF register will be updated prior to the first instruction executed out of Sleep.

# REGISTER 16-5: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u          | R/W-x/u  | R/W-x/u |  |  |

|------------------|---------|-------------------|---------|-------------------------------------------------------|------------------|----------|---------|--|--|

| _                | —       | —                 | _       | _                                                     | _                | ADRE     | S<9:8>  |  |  |

| bit 7            |         | •                 |         |                                                       |                  |          | bit 0   |  |  |

|                  |         |                   |         |                                                       |                  |          |         |  |  |

| Legend:          |         |                   |         |                                                       |                  |          |         |  |  |

| R = Readable I   | bit     | W = Writable      | bit     | U = Unimplen                                          | nented bit, read | l as '0' |         |  |  |

| u = Bit is uncha | anged   | x = Bit is unkn   | iown    | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |  |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                                                       |                  |          |         |  |  |

bit 7-2 Reserved: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits Upper 2 bits of 10-bit conversion result

# **REGISTER 16-6:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADRES   | 6<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower 8 bits of 10-bit conversion result

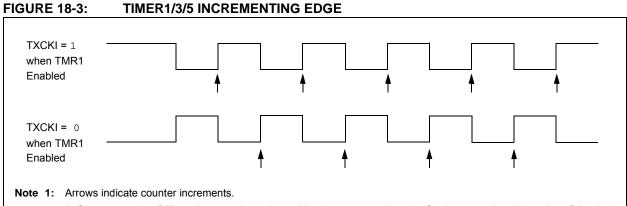

# 18.1 Timer1/3/5 Operation

The Timer1/3/5 module is a 16-bit incrementing counter which is accessed through the TMRxH:TMRxL register pair. Writes to TMRxH or TMRxL directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

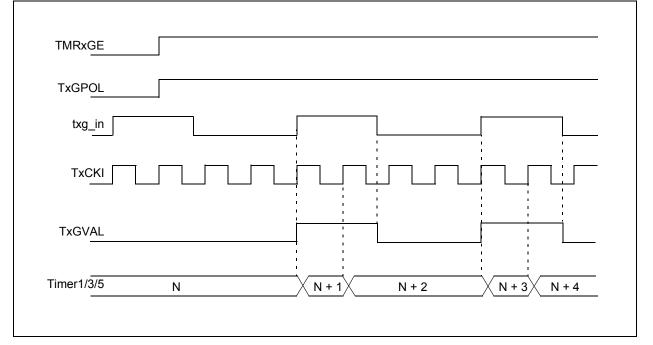

Timer1/3/5 is enabled by configuring the TMRxON and TMRxGE bits in the TxCON and TxGCON registers, respectively. Table 18-1 displays the Timer1/3/5 enable selections.

| TABLE 18-1: | TIMER1/3/5 ENABLE |

|-------------|-------------------|

|             | SELECTIONS        |

| TMRxON | TMRxGE | Timer1/3/5<br>Operation |  |

|--------|--------|-------------------------|--|

| 0      | 0      | Off                     |  |

| 0      | 1      | Off                     |  |

| 1      | 0      | Always On               |  |

| 1      | 1      | Count Enabled           |  |

# 18.2 Clock Source Selection

The TMRxCS<1:0> and SOSCEN bits of the TxCON register are used to select the clock source for Timer1/3/5. Table 18-2 displays the clock source selections.

#### 18.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMRxH:TMRxL register pair will increment on multiples of Fosc as determined by the Timer1/3/5 prescaler.

When the Fosc internal clock source is selected, the Timer1/3/5 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1/3/5 value. To utilize the full resolution of Timer1/3/5, an asynchronous input signal must be used to gate the Timer1/3/5 clock input.

The following asynchronous sources may be used:

• Asynchronous event on the TxG pin to Timer1/3/5 gate

#### 18.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1/3/5 module may work as a timer or a counter.

When enabled to count, Timer1/3/5 is incremented on the rising edge of the external clock input TxCKI. These external clock inputs (TxCKI) can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

•Timer1/3/5 enabled after POR

•Write to TMRxH or TMRxL

•Timer1/3/5 is disabled

•Timer1/3/5 is disabled (TMRxON = 0) when TxCKI is high then Timer1/3/5 is enabled (TMRxON = 1) when TxCKI is low.

| TMRxCS<1:0> | SOSCEN | Clock Source                                     |  |  |

|-------------|--------|--------------------------------------------------|--|--|

| 00          | х      | Instruction Clock (Fosc/4)                       |  |  |

| 01          | x      | System Clock (Fosc)                              |  |  |

| 1.0         | 0      | External Clocking on TxCKI Pin                   |  |  |

| 10          | 1      | Secondary Oscillator Circuit on SOSCI/SOSCO Pins |  |  |

| 11          | x      | LFINTOSC                                         |  |  |

#### TABLE 18-2: CLOCK SOURCE SELECTIONS

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

# FIGURE 18-4: TIMER1/3/5 GATE ENABLE MODE

| Name     | Bit 7                                                            | Bit 6                               | Bit 5                               | Bit 4  | Bit 3      | Bit 2      | Bit 1    | Bit 0  | Register<br>on Page |

|----------|------------------------------------------------------------------|-------------------------------------|-------------------------------------|--------|------------|------------|----------|--------|---------------------|

| CCP1CON  | —                                                                | _                                   | — DC1B<1:0>                         |        |            | CCP1M<3:0> |          |        |                     |

| CCP2CON  | _                                                                | _                                   | DC2B                                | <1:0>  | CCP2M<3:0> |            |          |        | 189                 |

| CCP3CON  | _                                                                | _                                   | DC3B                                | <1:0>  |            | CCP3       | V<3:0>   |        | 189                 |

| CCP4CON  | —                                                                | _                                   | DC4B                                | <1:0>  |            | CCP4M<3:0> |          |        |                     |

| CCP5CON  | —                                                                | _                                   | DC5B                                | <1:0>  | CCP5M<3:0> |            |          |        | 189                 |

| CCP6CON  | —                                                                | _                                   | DC6B                                | <1:0>  | CCP6M<3:0> |            |          |        | 189                 |

| CCP7CON  | —                                                                | _                                   | DC7B                                | <1:0>  | CCP7M<3:0> |            |          |        | 189                 |

| CCP8CON  | —                                                                | _                                   | DC8B                                | <1:0>  |            | CCP8       | √<3:0>   |        | 189                 |

| CCP9CON  | —                                                                | _                                   | DC9B                                | <1:0>  |            | CCP9       | √<3:0>   |        | 189                 |

| CCP10CON | —                                                                | _                                   | DC10                                | 3<1:0> |            | CCP10      | M<3:0>   |        | 189                 |

| INTCON   | GIE                                                              | PEIE                                | TMR0IE                              | INTE   | IOCIE      | TMR0IF     | INTF     | IOCIF  | 76                  |

| PIE1     | TMR1GIE                                                          | ADIE                                | RC1IE                               | TX1IE  | SSP1IE     | CCP1IE     | TMR2IE   | TMR1IE | 77                  |

| PIE2     | OSFIE                                                            | TMR5GIE                             | TMR3GIE                             | _      | BCL1IE     | TMR10IE    | TMR8IE   | CCP2IE | 78                  |

| PIE3     | CCP6IE                                                           | CCP5IE                              | CCP4IE                              | CCP3IE | TMR6IE     | TMR5IE     | TMR4IE   | TMR3IE | 79                  |

| PIR1     | TMR1GIF                                                          | ADIF                                | RC1IF                               | TX1IF  | SSP1IF     | CCP1IF     | TMR2IF   | TMR1IF | 81                  |

| PIR2     | OSFIF                                                            | TMR5GIF                             | TMR3GIF                             | _      | BCL1IF     | TMR10IF    | TMR8IF   | CCP2IF | 82                  |

| PIR3     | CCP6IF                                                           | CCP5IF                              | CCP4IF                              | CCP3IF | TMR6IF     | TMR5IF     | TMR4IF   | TMR3IF | 83                  |

| PR2      | Timer2 Module Period Register                                    |                                     |                                     |        |            |            | 213*     |        |                     |

| PR4      | Timer4 Module Period Register                                    |                                     |                                     |        |            | 213*       |          |        |                     |

| PR6      | Timer6 Module Period Register                                    |                                     |                                     |        |            | 213*       |          |        |                     |

| PR8      | Timer8 Module Period Register                                    |                                     |                                     |        |            | 213*       |          |        |                     |

| PR10     | Timer10 Mo                                                       | dule Period R                       | egister                             |        |            |            |          |        | 213*                |

| T2CON    | —                                                                |                                     | T2OUTPS<3:0> TMR2ON T2CKPS1 T2CKPS0 |        |            |            | 215      |        |                     |

| T4CON    | —                                                                | T4OUTPS<3:0> TMR4ON T4CKPS1 T       |                                     |        | T4CKPS0    | 215        |          |        |                     |

| T6CON    | —                                                                |                                     | T6OUTPS<3:0> TMR6ON T6CKPS1 T6CKPS0 |        |            |            | 215      |        |                     |

| T8CON    | _                                                                | T8OUTPS<3:0> TMR8ON T8CKPS1 T8CKPS0 |                                     |        |            | 215        |          |        |                     |

| T10CON   | _                                                                | T10OUTPS<3:0> TMR1                  |                                     |        | TMR100N    | T10CKPS1   | T10CKPS0 | 215    |                     |

| TMR2     | Holding Register for the 8-bit TMR2 Register                     |                                     |                                     |        |            | 213*       |          |        |                     |

| TMR4     | Holding Register for the 8-bit TMR4 Register <sup>(1)</sup>      |                                     |                                     |        |            | 213*       |          |        |                     |

| TMR6     | Holding Register for the 8-bit TMR6 Register <sup>(1)</sup>      |                                     |                                     |        |            | 213*       |          |        |                     |

| TMR8     | MR8 Holding Register for the 8-bit TMR8 Register <sup>(1)</sup>  |                                     |                                     |        |            | 213*       |          |        |                     |

| TMR10    | R10 Holding Register for the 8-bit TMR10 Register <sup>(1)</sup> |                                     |                                     |        |            | 213*       |          |        |                     |

# TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2/4/6/8/10

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2/4/6/8/10 module.

\* Page provides register information.

#### 21.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCLx pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDAx line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDAx line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPxCON3 register are clear.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the 8th falling edge of SCLx on the bus, the ACKTIM bit of the SSPx-CON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

# 21.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSPx Slave mode operates in one of four modes selected in the SSPM bits of SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operated the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 21.5.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 21-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSPx Mask register (Register 21-5) affects the address matching process. See **Section 21.5.9 "SSPx Mask Register"** for more information.

21.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

21.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCLx is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all 8 bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPxIF and UA are set, and SCLx is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

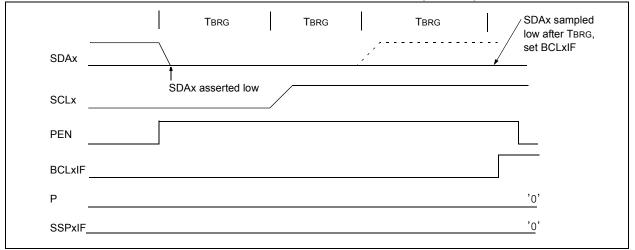

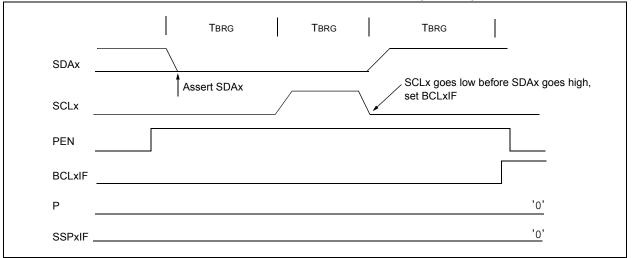

### 21.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out (Case 1).

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high (Case 2).

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to 0. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 21-38). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 21-39).

#### FIGURE 21-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 21-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

# 22.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a VOL space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is 8 bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 22-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 22.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 22-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

#### 22.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the TXx/CKx I/O pin as an output. If the TXx/CKx pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXxIF transmitter interrupt flag is set when the TXEN enable bit is set.

# 22.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

### 22.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity only in Asynchronous mode. In Synchronous mode the SCKP bit has a different function.

### 22.1.1.4 Transmit Interrupt Flag

The TXxIF interrupt flag bit of the PIR1/PIR4 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXxIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXxIF flag bit is not cleared immediately upon writing TXxREG. TXxIF becomes valid in the second instruction cycle following the write execution. Polling TXxIF immediately following the TXxREG write will return invalid results. The TXxIF bit is read-only, it cannot be set or cleared by software.

The TXxIF interrupt can be enabled by setting the TXxIE interrupt enable bit of the PIE1/PIE4 register. However, the TXxIF flag bit will be set whenever the TXxREG is empty, regardless of the state of TXxIE enable bit.

To use interrupts when transmitting data, set the TXxIE bit only when there is more data to send. Clear the TXxIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

# 22.1.2.3 Receive Interrupts

The RCxIF interrupt flag bit of the PIR1/PIR4 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCxIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCxIF interrupts are enabled by setting the following bits:

- RCxIE interrupt enable bit of the PIE1/PIE4 register

- PEIE peripheral interrupt enable bit of the INTCON register

- GIE global interrupt enable bit of the INTCON register

The RCxIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

### 22.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCxSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCxREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCxSTA register which resets the EUSART. Clearing the CREN bit of the RCxSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive |

|-------|------------------------------------------|

|       | FIFO have framing errors, repeated reads |

|       | of the RCxREG will not clear the FERR    |

|       | bit.                                     |

# 22.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCxSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCxSTA register or by resetting the EUSART by clearing the SPEN bit of the RCxSTA register.

# 22.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set, the EUSART will shift 9 bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the 8 Least Significant bits from the RCxREG.

### 22.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCxSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCxIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

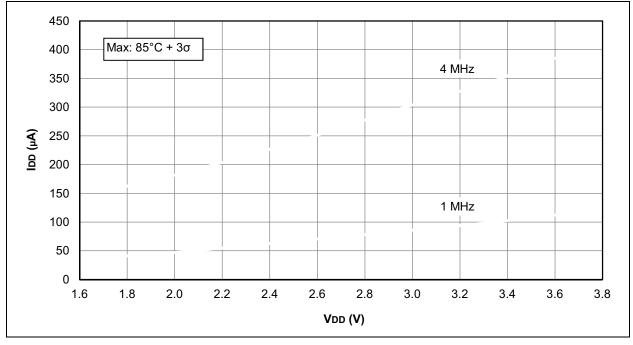

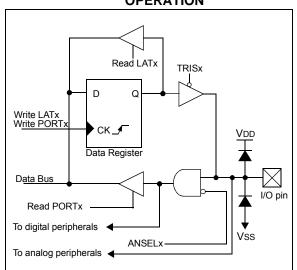

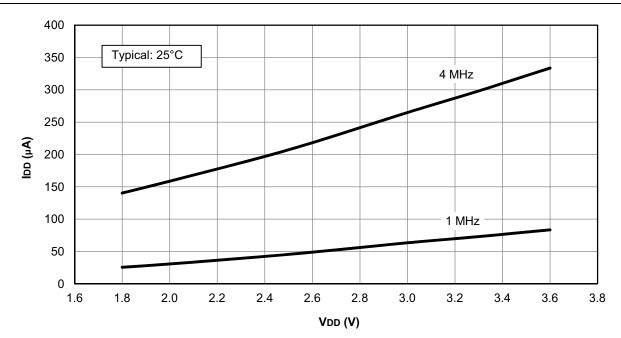

FIGURE 26-12: IDD MAXIMUM, EXTERNAL CLOCK (ECM), MEDIUM-POWER MODE, PIC16LF1526 ONLY