Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.5K x 8                                                                   |

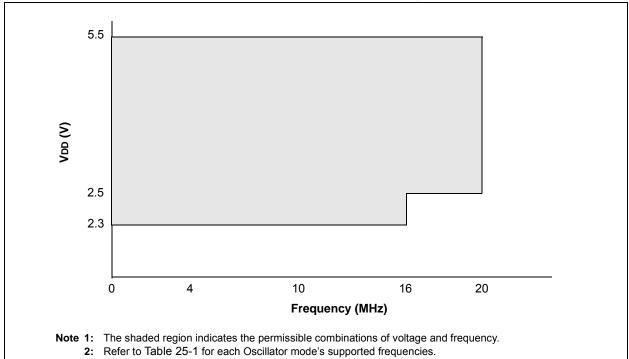

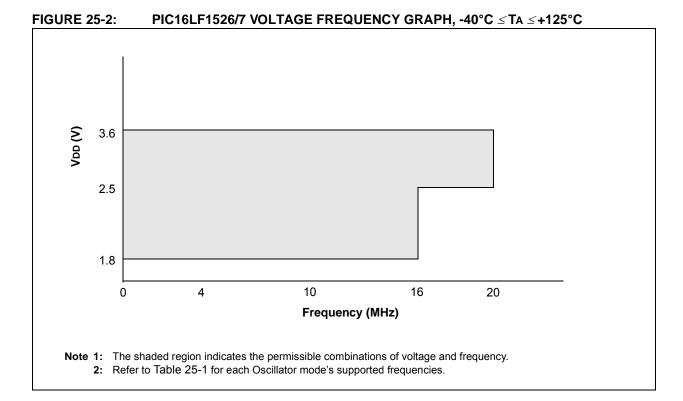

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 30x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1527t-i-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### PIC16(L)F151X/152X Family Types

|               |                  |                                 |                      | tes)                         |                      | AI          | C                |                      |        |                             |     |                      |     |

|---------------|------------------|---------------------------------|----------------------|------------------------------|----------------------|-------------|------------------|----------------------|--------|-----------------------------|-----|----------------------|-----|

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High-Endurance Flash (bytes) | I/O's <sup>(2)</sup> | 10-bit (ch) | Advanced Control | Timers<br>(8/16-bit) | EUSART | MSSP (I <sup>2</sup> C/SPI) | ССР | Debug <sup>(1)</sup> | XLP |

| PIC16(L)F1512 | (1)              | 2048                            | 128                  | 128                          | 25                   | 17          | Y                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1513 | (1)              | 4096                            | 256                  | 128                          | 25                   | 17          | Y                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1516 | (2)              | 8192                            | 512                  | 128                          | 25                   | 17          | N                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1517 | (2)              | 8192                            | 512                  | 128                          | 36                   | 28          | Ν                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1518 | (2)              | 16384                           | 1024                 | 128                          | 25                   | 17          | Ν                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1519 | (2)              | 16384                           | 1024                 | 128                          | 36                   | 28          | Ν                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1526 | (3)              | 8192                            | 768                  | 128                          | 54                   | 30          | N                | 6/3                  | 2      | 2                           | 10  | 1                    | Y   |

| PIC16(L)F1527 | (3)              | 16384                           | 1536                 | 128                          | 54                   | 30          | Ν                | 6/3                  | 2      | 2                           | 10  |                      | Y   |

Note 1: I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS41624 PIC16(L)F1512/13 Data Sheet, 28-Pin Flash, 8-bit Microcontrollers.

- **2:** DS41452 PIC16(L)F1516/7/8/9 Data Sheet, 28/40/44-Pin Flash, 8-bit MCUs.

- **3:** DS41458 PIC16(L)F1526/7 Data Sheet, 64-Pin Flash, 8-bit MCUs.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

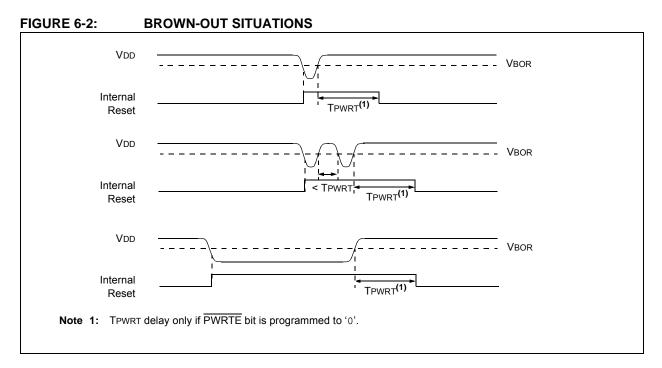

#### 6.3 Register Definitions: BOR Control

#### REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u     | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |  |  |

|-------------|---------|-----|-----|-----|-----|-----|--------|--|--|

| SBOREN      | BORFS   | —   | —   | —   | —   | —   | BORRDY |  |  |

| bit 7 bit 0 |         |     |     |     |     |     |        |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | <b>SBOREN:</b> Software Brown-out Reset Enable bit <sup>(1)</sup><br><u>If BOREN &lt;1:0&gt; <math>\neq</math> 01:<br/>SBOREN is read/write, but has no effect on the BOR.<br/><u>If BOREN &lt;1:0&gt; = 01</u>:<br/>1 = BOR Enabled<br/>0 = BOR Disabled</u>                                                                                                                                                                                                    |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 6   | <ul> <li>BORFS: Brown-out Reset Fast Start bit<sup>(1)</sup></li> <li>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</li> <li>BORFS is Read/Write, but has no effect.</li> <li>If BOREN&lt;1:0&gt; = 10 (Disabled in Sleep) or BOREN&lt;1:0&gt; = 01 (Under software control):</li> <li>1 = Band gap is forced on always (covers sleep/wake-up/operating cases)</li> <li>0 = Band gap operates normally, and may turn off</li> </ul> |  |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| bit 0   | <b>BORRDY:</b> Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                                                                                                              |  |

| Noto 1  | POPEN-1:0> hits are leasted in Configuration Words                                                                                                                                                                                                                                                                                                                                                                                                               |  |

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

| U-0          | R/W-0/0                               | U-0                       | U-0             | R/W-0/0        | R/W-0/0          | R/W-0/0           | U-0        |

|--------------|---------------------------------------|---------------------------|-----------------|----------------|------------------|-------------------|------------|

| _            | AD2IF                                 | _                         | _               | BCL1IF         | BCL2IF           | TMR4IF            | _          |

| bit 7        |                                       |                           |                 |                |                  |                   | bit C      |

|              |                                       |                           |                 |                |                  |                   |            |

| Legend:      |                                       |                           |                 |                |                  |                   |            |

| R = Read     | able bit                              | W = Writable              | bit             | U = Unimpler   | nented bit, reac | l as '0'          |            |

| u = Bit is   | unchanged                             | x = Bit is unkr           | nown            | -n/n = Value a | at POR and BO    | R/Value at all ot | her Resets |

| '1' = Bit is | set                                   | '0' = Bit is cle          | ared            |                |                  |                   |            |

|              |                                       |                           |                 |                |                  |                   |            |

| bit 7        | Unimpleme                             | nted: Read as '           | 0'              |                |                  |                   |            |

| bit 6        |                                       | er5 Gate Interrup         | ot Flag bit     |                |                  |                   |            |

|              | 1 = Interrupt                         | is pending is not pending |                 |                |                  |                   |            |

| bit 5-4      |                                       | nted: Read as '           | 0'              |                |                  |                   |            |

| bit 3        | •                                     | SP1 Bus Collisi           |                 | -log bit       |                  |                   |            |

| DIL 3        | 1 = Interrupt                         |                           | on menupi       | lay bit        |                  |                   |            |

|              |                                       | is not pending            |                 |                |                  |                   |            |

| bit 2        | BCL2IF: MS                            | SP2 Bus Collisi           | on Interrupt F  | =lag bit       |                  |                   |            |

|              | 1 = Interrupt                         | is pending                |                 |                |                  |                   |            |

|              | •                                     | is not pending            |                 |                |                  |                   |            |

| bit 1        |                                       | ner4 to PR4 Inte          | errupt Flag bit | t              |                  |                   |            |

|              | 1 = Interrupt                         | is pending is not pending |                 |                |                  |                   |            |

| bit 0        |                                       | nted: Read as '           | 0'              |                |                  |                   |            |

| DILU         | Uninpienie                            | nieu. Reau as             | 0               |                |                  |                   |            |

|              |                                       |                           |                 |                |                  |                   |            |

| Note:        | Interrupt flag bits condition occurs, |                           |                 |                |                  |                   |            |

|              | its corresponding                     |                           |                 |                |                  |                   |            |

|              | Enable bit, GIE,                      | of the INTCON             | register.       |                |                  |                   |            |

|              | User software                         | should ensu               | ure the         |                |                  |                   |            |

#### REGISTER 7-7: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

appropriate interrupt flag bits are clear prior

to enabling an interrupt.

| TABLE 11-1: | FLASH MEMORY           |

|-------------|------------------------|

|             | ORGANIZATION BY DEVICE |

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |  |

|---------------|----------------------|-----------------------------|--|

| PIC16(L)F1526 | 32                   | 32                          |  |

| PIC16(L)F1527 | 32                   | 52                          |  |

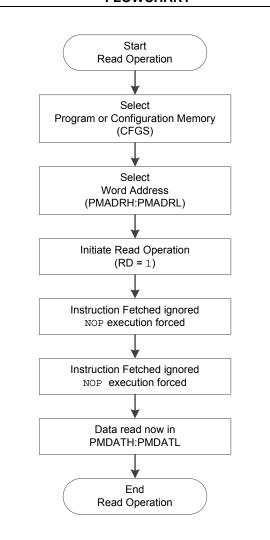

### 11.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

| Note: | The two instructions following a program |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | memory read are required to be NOPS.     |  |  |  |  |  |  |  |  |

|       | This prevents the user from executing a  |  |  |  |  |  |  |  |  |

|       | two-cycle instruction on the next        |  |  |  |  |  |  |  |  |

|       | instruction after the RD bit is set.     |  |  |  |  |  |  |  |  |

#### FIGURE 11-1: FLASH PROGRAM MEMORY READ FLOWCHART

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|

| ANSF7 | ANSF6 | ANSF5 | ANSF4 | ANSF3 | ANSF2 | ANSF1 |

| bit 7 |       |       |       |       |       |       |

#### REGISTER 12-27: ANSELF: PORTF ANALOG SELECT REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ANSF<7:0>**: Analog Select between Analog or Digital Function on pins RF<7:0>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled. 0 = Digital I/O. Pin is assigned to port or digital special function.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELF | ANSF7  | ANSF6  | ANSF5  | ANSF4  | ANSF3  | ANSF2  | ANSF1  | ANSF0  | 130                 |

| LATF   | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | 129                 |

| PORTF  | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | 129                 |

| TRISF  | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 129                 |

TABLE 12-14: SUMMARY OF REGISTERS ASSOCIATED WITH PORTF

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTF.

#### TABLE 12-15: SUMMARY OF CONFIGURATION WORD WITH PORTF

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4              | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------------------|----------|----------|---------|---------|---------------------|

|         | 13:8 | -       | _       | LVP      | DEBUG                 | LPBOR    | BORV     | STVREN  | _       | 45                  |

| CONFIG2 | 7:0  | _       | -       | —        | VCAPEN <sup>(1)</sup> | _        | _        | WRT     | <1:0>   | 45                  |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used by PORTF.

Note 1: PIC16F1526/7 only.

R/W-1 ANSF0

bit 0

#### 17.2 Register Definitions: Option Register

#### REGISTER 17-1: OPTION\_REG: OPTION REGISTER

| R/W-1/1          | R/W-1/1                             | R/W-1/1          | R/W-1/1         | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1     |

|------------------|-------------------------------------|------------------|-----------------|----------------|------------------|------------------|-------------|

| WPUEN            | INTEDG                              | TMR0CS           | TMR0SE          | PSA            |                  | PS<2:0>          |             |

| bit 7            |                                     |                  |                 |                |                  |                  | bit 0       |

|                  |                                     |                  |                 |                |                  |                  |             |

| Legend:          |                                     |                  |                 |                |                  |                  |             |

| R = Readable b   |                                     | W = Writable     | bit             | •              | mented bit, read |                  |             |

| u = Bit is uncha | inged                               | x = Bit is unkr  | nown            | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |                                     | '0' = Bit is cle | ared            |                |                  |                  |             |

|                  |                                     |                  |                 |                |                  |                  |             |

| bit 7            | WPUEN: Wea                          | •                |                 |                |                  |                  |             |

|                  | 1 = All weak p<br>0 = Weak pull-    |                  |                 |                |                  |                  |             |

| bit 6            | INTEDG: Inter                       | •                | -               |                | Valueo           |                  |             |

|                  | 1 = Interrupt o                     |                  |                 |                |                  |                  |             |

|                  | 0 = Interrupt o                     | n falling edge   | of INT pin      |                |                  |                  |             |

| bit 5            | TMR0CS: Tim                         |                  | irce Select bit |                |                  |                  |             |

|                  | 1 = Transition                      | •                |                 |                |                  |                  |             |

| L:4 4            | 0 = Internal in:                    | •                | •               | +)             |                  |                  |             |

| bit 4            | <b>TMR0SE:</b> Tim<br>1 = Increment |                  | •               |                |                  |                  |             |

|                  | 0 = Increment                       |                  |                 |                |                  |                  |             |

| bit 3            | PSA: Prescale                       | •                |                 |                |                  |                  |             |

|                  | 1 = Prescaler                       | is not assigne   | d to the Timer  | 0 module       |                  |                  |             |

|                  | 0 = Prescaler                       | is assigned to   | the Timer0 m    | odule          |                  |                  |             |

| bit 2-0          | PS<2:0>: Pres                       | scaler Rate Se   | elect bits      |                |                  |                  |             |

|                  | Bit V                               | /alue Timer0     | Rate            |                |                  |                  |             |

|                  |                                     | 00 1:2           |                 |                |                  |                  |             |

|                  |                                     | 01 1:4<br>10 1:8 |                 |                |                  |                  |             |

|                  |                                     | 11 1:1           | -               |                |                  |                  |             |

|                  |                                     | 00 1:3<br>01 1:6 |                 |                |                  |                  |             |

|                  | 11                                  | 10 1:1           |                 |                |                  |                  |             |

|                  | 11                                  | 11 <b>1</b> :2   | 56              |                |                  |                  |             |

|                  |                                     |                  |                 |                |                  |                  |             |

| TABLE 17-1:      | SUMMARY                             | OF REGIST        | ERS ASSO        | CIATED WIT     | H TIMER0         |                  |             |

| Name       | Bit 7     | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|-----------|------------|--------|--------|--------|--------|---------|--------|---------------------|

| INTCON     | GIE       | PEIE       | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF  | 76                  |

| OPTION_REG | WPUEN     | INTEDG     | TMR0CS | TMR0SE | PSA    |        | PS<2:0> |        | 158                 |

| TMR0       | Timer0 Mc | dule Regis | ter    |        |        |        |         |        | 156*                |

| TRISA      | TRISA7    | TRISA6     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 114                 |

**Legend:** — = Unimplemented locations, read as '0'. Shaded cells are not used by the Timer0 module.

\* Page provides register information.

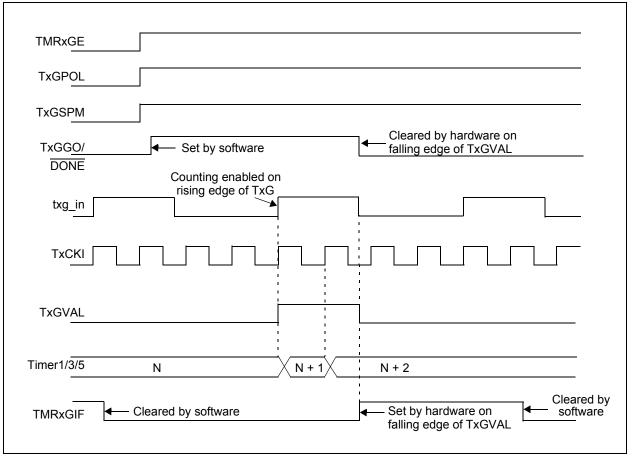

#### FIGURE 18-5: TIMER1/3/5 GATE TOGGLE MODE

| TMRxGE       |                         |                         |

|--------------|-------------------------|-------------------------|

| TxGPOL       |                         |                         |

| TxGTM        |                         |                         |

| txg_in       |                         |                         |

|              |                         |                         |

| TxGVAL       |                         |                         |

| Timer1/3/5 N | N + 1 N + 2 N + 3 N + 4 | N + 5 N + 6 N + 7 N + 8 |

|              |                         |                         |

#### FIGURE 18-6: TIMER1/3/5 GATE SINGLE-PULSE MODE

#### 18.12 Register Definitions: Timer1/3/5 Gate Control

#### REGISTER 18-2: TxGCON: TIMER1/3/5 GATE CONTROL REGISTER

| R/W-0/u          | R/W-0/u         | R/W-0/u                             | R/W-0/u         | R/W/HC-0/u                    | R-x/x             | R/W-0/u        | R/W-0/u      |

|------------------|-----------------|-------------------------------------|-----------------|-------------------------------|-------------------|----------------|--------------|

| TMRxGE           | TxGPOL          | TxGTM                               | TxGSPM          | TxGGO/<br>DONE                | TxGVAL            | TxGS           | S<1:0>       |

| bit 7            |                 |                                     |                 |                               |                   |                | bit 0        |

| Lovendi          |                 |                                     |                 |                               |                   |                |              |

| Legend:          | L :4            |                                     | L :4            |                               |                   |                |              |

| R = Readable     |                 | W = Writable                        |                 | U = Unimplem                  |                   |                |              |

| u = Bit is unch  | langed          | x = Bit is unki                     |                 |                               |                   | R/Value at all | other Resets |

| '1' = Bit is set |                 | '0' = Bit is cle                    | ared            | HC = Bit is cle               | eared by hardw    | vare           |              |

| bit 7            | TMRxGE: Ti      | mer1/3/5 Gate                       | Enable bit      |                               |                   |                |              |

|                  | If TMRxON =     | <u>= 0</u> :                        |                 |                               |                   |                |              |

|                  | This bit is igr |                                     |                 |                               |                   |                |              |

|                  | If TMRxON =     |                                     | optrolled by th | ne Timer1/3/5 ga              | ata function      |                |              |

|                  |                 |                                     |                 | r1/3/5 gate func              |                   |                |              |

| bit 6            |                 | mer1/3/5 Gate I                     |                 | <u> </u>                      |                   |                |              |

|                  |                 |                                     | •               | /3/5 counts whe               | en gate is high   | )              |              |

|                  |                 | •                                   | •               | 3/5 counts whe                | • •               | ,              |              |

| bit 5            | TxGTM: Tim      | er1/3/5 Gate To                     | ggle Mode bit   |                               |                   |                |              |

|                  |                 | 3/5 Gate Toggle                     |                 |                               |                   |                |              |

|                  |                 |                                     |                 | oled and toggle               | flip-flop is clea | red            |              |

| hit 4            | -               | ate flip-flop tog                   |                 |                               |                   |                |              |

| bit 4            |                 | mer1/3/5 Gate                       | •               | s enabled and is              | controlling Ti    | mer1/3/5 gate  |              |

|                  |                 | 3/5 Gate Single                     |                 |                               | s controlling Th  | nei 1/3/3 gate |              |

| bit 3            |                 | _                                   |                 | ulse Acquisition              | Status bit        |                |              |

|                  |                 |                                     | •               | on is ready, wai              |                   | е              |              |

|                  |                 |                                     |                 | on has complete               |                   |                |              |

| bit 2            | TxGVAL: Tir     | mer1/3/5 Gate (                     | Current State b | bit                           |                   |                |              |

|                  |                 | e current state o<br>y Timer1/3/5 G |                 | /5 gate that coul<br>//RxGE). | ld be provided    | to TMRxH:TM    | RxL.         |

| bit 1-0          | TxGSS<1:0>      | <b>-:</b> Timer1/3/5 G              | ate Source Se   | lect bits                     |                   |                |              |

|                  | -               | 0 match PR10                        |                 | (1)                           |                   |                |              |

|                  |                 | 2/4/6/8 match P                     |                 | PR8(1)                        |                   |                |              |

|                  |                 | ) overflow outpu<br>/3/5 gate pin   | it              |                               |                   |                |              |

| Note 1: Se       |                 | or Timer selection                  | n               |                               |                   |                |              |

|                  |                 |                                     |                 |                               |                   |                |              |

#### 21.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

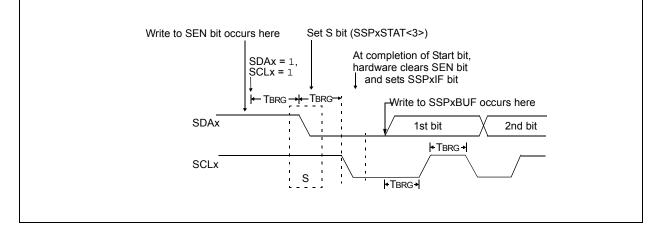

To initiate a Start condition (Figure 21-26), the user sets the Start Enable bit, SEN bit of the SSPxCON2 register. If the SDAx and SCLx pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCLx and SDAx are both sampled high when the Baud Rate Generator times out (TBRG), the SDAx pin is driven low. The action of the SDAx being driven low while SCLx is high is the Start condition and causes the S bit of the SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SDAx bit of the SSPxADD<7:0> and resumes its count. When the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared

FIGURE 21-26: FIRST START BIT TIMING

by hardware; the Baud Rate Generator is suspended, leaving the SDAx line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDAx and SCLx pins are already sampled low, or if during the Start condition, the SCLx line is sampled low before the SDAx line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- **2:** The Philips I<sup>2</sup>C Specification states that a bus collision cannot occur on a Start.

#### 21.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

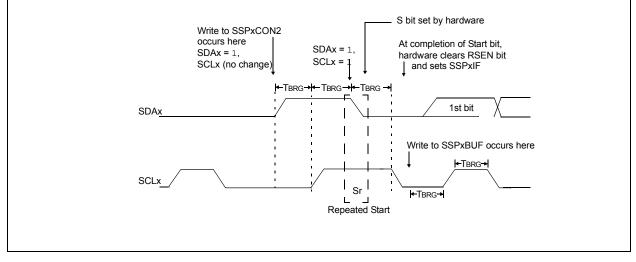

A Repeated Start condition occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. SCLx is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- 2: A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

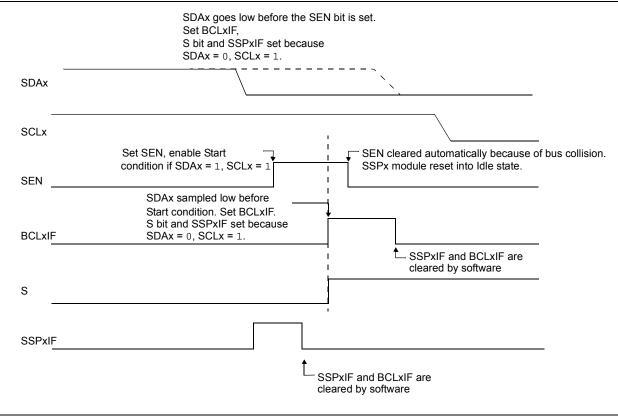

#### 21.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDAx or SCLx are sampled low at the beginning of the Start condition (Figure 21-33).

- b) SCLx is sampled low before SDAx is asserted low (Figure 21-34).

During a Start condition, both the SDAx and the SCLx pins are monitored.

If the SDAx pin is already low, or the SCLx pin is already low, then all of the following occur:

- · the Start condition is aborted,

- · the BCLxIF flag is set and

- the MSSPx module is reset to its Idle state (Figure 21-33).

The Start condition begins with the SDAx and SCLx pins deasserted. When the SDAx pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCLx pin is sampled low while SDAx is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDAx pin is sampled low during this count, the BRG is reset and the SDAx line is asserted early (Figure 21-35). If, however, a '1' is sampled on the

SDAx pin, the SDAx pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCLx pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCLx pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDAx before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion. Repeated Start or Stop conditions.

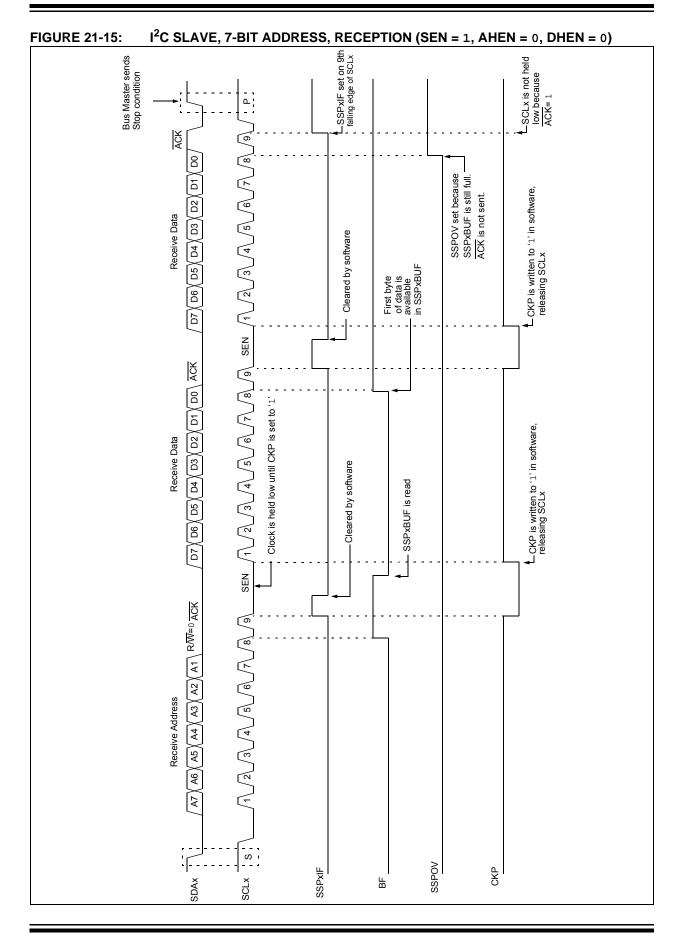

| R-0/0            | R/W-0/0                   | R/W-0/0                                | R/W-0/0                      | R/W-0/0                    | R/W-0/0                      | R/W-0/0          | R/W-0/0         |

|------------------|---------------------------|----------------------------------------|------------------------------|----------------------------|------------------------------|------------------|-----------------|

| ACKTIM           | PCIE                      | SCIE                                   | BOEN                         | SDAHT                      | SBCDE                        | AHEN             | DHEN            |

| bit 7            |                           | ·                                      |                              |                            |                              |                  | bit C           |

|                  |                           |                                        |                              |                            |                              |                  |                 |

| Legend:          |                           |                                        |                              |                            |                              |                  |                 |

| R = Readable     |                           | W = Writable                           |                              | •                          | mented bit, read             |                  |                 |

| u = Bit is uncl  | 0                         | x = Bit is unk                         | nown                         | -n/n = Value               | at POR and BO                | R/Value at all o | other Resets    |

| '1' = Bit is set |                           | '0' = Bit is cle                       | ared                         |                            |                              |                  |                 |

| bit 7            |                           | knowledge Tim                          | e Status bit (1 <sup>2</sup> | C mode only)               | 3)                           |                  |                 |

|                  |                           | •                                      |                              | • •                        | e, set on 8 <sup>™</sup> fal | ling edge of SC  | l x clock       |

|                  |                           |                                        |                              |                            | g edge of SCLx               |                  |                 |

| bit 6            | PCIE: Stop C              | Condition Interru                      | upt Enable bit (             | I <sup>2</sup> C mode only | /)                           |                  |                 |

|                  |                           | nterrupt on dete                       |                              |                            |                              |                  |                 |

|                  | •                         | ection interrupts                      |                              |                            |                              |                  |                 |

| bit 5            |                           | Condition Interro                      |                              | · -                        | , ,                          |                  |                 |

|                  |                           | nterrupt on deten<br>ection interrupts |                              |                            | ditions                      |                  |                 |

| bit 4            | BOEN: Buffe               | r Overwrite En                         | able bit                     |                            |                              |                  |                 |

|                  | In SPI Slave              | <u>mode:</u> (1)                       |                              |                            |                              |                  |                 |

|                  |                           |                                        |                              |                            | yte is shifted in            |                  |                 |

|                  |                           |                                        |                              |                            | STAT register a              | Iready set, SSI  | POV bit of the  |

|                  |                           | xCON1 registe<br>r mode and SP         |                              |                            | updated                      |                  |                 |

|                  |                           | s ignored.                             |                              | -                          |                              |                  |                 |

|                  | In I <sup>2</sup> C Slave |                                        |                              |                            |                              |                  |                 |

|                  |                           | of the SSPOV                           |                              |                            | r a received ad              | dress/data byte  | e, ignoring the |

|                  |                           | xBUF is only u                         |                              |                            | r                            |                  |                 |

| bit 3            |                           | Ax Hold Time S                         | -                            |                            |                              |                  |                 |

|                  | 1 = Minimum               | of 300 ns hold                         | time on SDAx                 | after the fallir           | ng edge of SCL               | x                |                 |

|                  |                           |                                        |                              |                            | ng edge of SCL               |                  |                 |

| bit 2            | SBCDE: Slav               | ve Mode Bus C                          | ollision Detect              | Enable bit (I <sup>2</sup> | C Slave mode c               | only)            |                 |

|                  |                           | ng edge of SCL<br>the PIR2 regis       |                              |                            | en the module i              | s outputting a l | high state, the |

|                  |                           | lave bus collisi                       |                              | lad                        |                              |                  |                 |

| L:1 1            |                           | s collision inter                      | -                            |                            |                              |                  |                 |

| bit 1            |                           | ess Hold Enabl                         | -                            | • •                        | hing received a              | addross byto: (  | YAD bit of the  |

|                  | SSPxCC                    | DN1 register wi                        | ll be cleared ar             |                            | -                            | iduless byle, C  |                 |

|                  |                           | holding is disal                       |                              |                            |                              |                  |                 |

| bit 0            |                           | Hold Enable bi                         |                              | • ·                        |                              |                  |                 |

|                  |                           |                                        |                              |                            | data byte; slave             | hardware clea    | irs the CKP bi  |

|                  |                           | SPxCON1 regis<br>ding is disabled      |                              |                            |                              |                  |                 |

| Note 1: Fo       | or daisy-chained          | -                                      |                              | r to ignore all b          | out the last recei           | ved byte. SSPC   | DV is still set |

| wh               | nen a new byte i          |                                        |                              |                            |                              | -                |                 |

|                  | :- h:+ h                  | ant in Clave me                        | alaa that Ctart              | and Chan age               | dition data ation            | : [! _ ! i ]     |                 |

#### REGISTER 21-4: SSPxCON3: SSPx CONTROL REGISTER 3

2: This bit has no effect in Slave modes that Start and Stop condition detection is explicitly listed as enabled.

**3:** The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

|          |         |        |         |           |             | _         |        |        |                     |

|----------|---------|--------|---------|-----------|-------------|-----------|--------|--------|---------------------|

| Name     | Bit 7   | Bit 6  | Bit 5   | Bit 4     | Bit 3       | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

| BAUD1CON | ABDOVF  | RCIDL  | —       | SCKP      | BRG16       | —         | WUE    | ABDEN  | 260                 |

| BAUD2CON | ABDOVF  | RCIDL  | —       | SCKP      | BRG16       | —         | WUE    | ABDEN  | 260                 |

| INTCON   | GIE     | PEIE   | TMR0IE  | INTE      | IOCIE       | TMR0IF    | INTF   | IOCIF  | 76                  |

| PIE1     | TMR1GIE | ADIE   | RC1IE   | TX1IE     | SSP1IE      | CCP1IE    | TMR2IE | TMR1IE | 77                  |

| PIE4     | CCP10IE | CCP9IE | RC2IE   | TX2IE     | CCP8IE      | CCP7IE    | BCL2IE | SSP2IE | 80                  |

| PIR1     | TMR1GIF | ADIF   | RC1IF   | TX1IF     | SSP1IF      | CCP1IF    | TMR2IF | TMR1IF | 81                  |

| PIR4     | CCP10IF | CCP9IF | RC2IF   | TX2IF     | CCP8IF      | CCP7IF    | BCL2IF | SSP2IF | 84                  |

| RC1STA   | SPEN    | RX9    | SREN    | CREN      | ADDEN       | FERR      | OERR   | RX9D   | 259                 |

| RC2STA   | SPEN    | RX9    | SREN    | CREN      | ADDEN       | FERR      | OERR   | RX9D   | 259                 |

| SP1BRGL  |         |        | EUSART1 | Baud Rate | Generator   | Low Byte  |        |        | 261*                |

| SP1BRGH  |         |        | EUSART1 | Baud Rate | Generator,  | High Byte |        |        | 261*                |

| SP2BRGL  |         |        | EUSART2 | Baud Rate | Generator   | Low Byte  |        |        | 261*                |

| SP2BRGH  |         |        | EUSART2 | Baud Rate | Generator,  | High Byte |        |        | 261*                |

| TRISC    | TRISC7  | TRISC6 | TRISC5  | TRISC4    | TRISC3      | TRISC2    | TRISC1 | TRISC0 | 120                 |

| TX1REG   |         |        | EU      | SART1 Tra | nsmit Regis | ster      |        |        | 250*                |

| TX1STA   | CSRC    | TX9    | TXEN    | SYNC      | SENDB       | BRGH      | TRMT   | TX9D   | 258                 |

| TX2REG   |         |        | EU      | SART2 Tra | nsmit Regis | ster      |        |        | 250*                |

| TX2STA   | CSRC    | TX9    | TXEN    | SYNC      | SENDB       | BRGH      | TRMT   | TX9D   | 258                 |

| 17221A   | LSKL    | 178    | IXEN    | STINC     | SENDB       | BRGH      | IRMI   | 1,73D  | 25                  |

### TABLE 22-9:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE<br/>TRANSMISSION

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for synchronous slave transmission.

\* Page provides register information.

#### 25.2 DC Characteristics: Supply Current (IDD)

| PIC16LF      | 1526/7                              |         | rd Operat<br>ng temper |      | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                                                              |                                               |  |  |

|--------------|-------------------------------------|---------|------------------------|------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------|--|--|

| PIC16F1      | 526/7                               |         | rd Operat<br>ng temper |      | -40°C ≤ 1                                                                                                                      | <b>erwise stated)</b><br>C for industrial<br>°C for extended |                                               |  |  |

| Param<br>No. | Device<br>Characteristics           | Min.    | Тур†                   | Max. | Units                                                                                                                          |                                                              | Conditions                                    |  |  |

| NO.          |                                     |         |                        |      |                                                                                                                                | Vdd                                                          | Note                                          |  |  |

|              | Supply Current (IDD) <sup>(1)</sup> | , 2, 3) |                        |      | •                                                                                                                              |                                                              | 1                                             |  |  |

| D009         | LDO Regulator                       | —       | 350                    | —    | μA                                                                                                                             |                                                              | Device operating at 8 MHz                     |  |  |

|              |                                     | —       | 13                     | —    | μA                                                                                                                             |                                                              | Sleep VREGPM = 0                              |  |  |

|              |                                     | —       | 0.3                    | —    | μA                                                                                                                             |                                                              | Sleep VREGPM = 1                              |  |  |

| D010         |                                     | —       | 10                     | 20   | μA                                                                                                                             | 1.8                                                          | Fosc = 32 kHz                                 |  |  |

|              |                                     | -       | 15                     | 35   | μA                                                                                                                             | 3.0                                                          | LP Oscillator<br>-40°C $\leq$ TA $\leq$ +85°C |  |  |

| D010         |                                     | —       | 20                     | 35   | μA                                                                                                                             | 2.3                                                          | Fosc = 32 kHz                                 |  |  |

|              |                                     |         | 30                     | 45   | μA                                                                                                                             | 3.0                                                          | LP Oscillator<br>-40°C $\leq$ TA $\leq$ +85°C |  |  |

|              |                                     |         | 40                     | 50   | μA                                                                                                                             | 5.0                                                          |                                               |  |  |

| D011         |                                     | —       | 70                     | 100  | μA                                                                                                                             | 1.8                                                          | Fosc = 1 MHz                                  |  |  |

|              |                                     | —       | 130                    | 200  | μΑ                                                                                                                             | 3.0                                                          | XT Oscillator                                 |  |  |

| D011         |                                     | —       | 120                    | 180  | μA                                                                                                                             | 2.3                                                          | Fosc = 1 MHz                                  |  |  |

|              |                                     | —       | 160                    | 240  | μA                                                                                                                             | 3.0                                                          | XT Oscillator                                 |  |  |

|              |                                     | —       | 240                    | 360  | μA                                                                                                                             | 5.0                                                          |                                               |  |  |

| D012         |                                     |         | 170                    | 245  | μA                                                                                                                             | 1.8                                                          | Fosc = 4 MHz                                  |  |  |

|              |                                     | _       | 300                    | 440  | μA                                                                                                                             | 3.0                                                          | XT Oscillator                                 |  |  |

| D012         |                                     |         | 290                    | 475  | μA                                                                                                                             | 2.3                                                          | Fosc = 4 MHz                                  |  |  |

|              |                                     | _       | 380                    | 525  | μA                                                                                                                             | 3.0                                                          | XT Oscillator                                 |  |  |

|              |                                     | —       | 460                    | 675  | μA                                                                                                                             | 5.0                                                          |                                               |  |  |

| D013         |                                     |         | 25                     | 35   | μA                                                                                                                             | 1.8                                                          | Fosc = 500 kHz                                |  |  |

|              |                                     | -       | 42                     | 60   | μA                                                                                                                             | 3.0                                                          | External Clock (ECL),<br>Low-Power mode       |  |  |

| D013         |                                     | —       | 50                     | 65   | μA                                                                                                                             | 2.3                                                          | Fosc = 500 kHz                                |  |  |

|              |                                     | _       | 60                     | 80   | μA                                                                                                                             | 3.0                                                          | External Clock (ECL),<br>Low-Power mode       |  |  |

|              |                                     |         | 70                     | 85   | μA                                                                                                                             | 5.0                                                          |                                               |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: 0.1 µF capacitor on VCAP pin (PIC16F1526/7).

4: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

\*

#### 27.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

#### 27.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 27.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 27.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

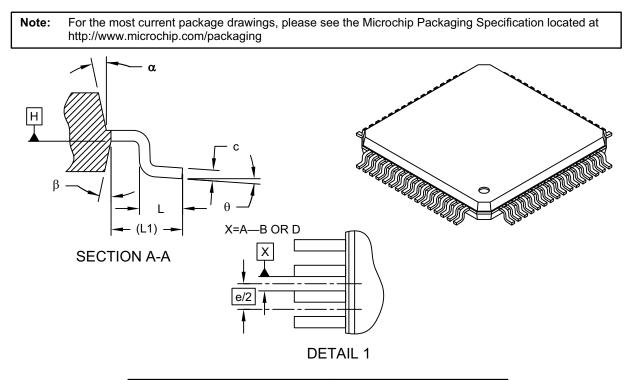

#### 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

|                          | N   | 1ILLIMETER: | S         |      |  |

|--------------------------|-----|-------------|-----------|------|--|

| Dimension                | MIN | NOM         | MAX       |      |  |

| Number of Leads          | Ν   |             | 64        |      |  |

| Lead Pitch               | е   |             | 0.50 BSC  |      |  |

| Overall Height           | Α   | -           | -         | 1.20 |  |

| Molded Package Thickness | A2  | 0.95        | 1.00      | 1.05 |  |

| Standoff                 | A1  | 0.05        | -         | 0.15 |  |

| Foot Length              | L   | 0.45        | 0.60      | 0.75 |  |

| Footprint                | L1  | 1.00 REF    |           |      |  |

| Foot Angle               | ¢   | 0°          | 3.5°      | 7°   |  |

| Overall Width            | E   |             | 12.00 BSC |      |  |

| Overall Length           | D   |             | 12.00 BSC |      |  |

| Molded Package Width     | E1  |             | 10.00 BSC |      |  |

| Molded Package Length    | D1  |             | 10.00 BSC |      |  |

| Lead Thickness           | С   | 0.09        | -         | 0.20 |  |

| Lead Width               | b   | 0.17        | 0.22      | 0.27 |  |

| Mold Draft Angle Top     | α   | 11° 12° 13° |           |      |  |

| Mold Draft Angle Bottom  | β   | 11°         | 12°       | 13°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085C Sheet 2 of 2

### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Ν      | <b>ILLIMETER</b> | S        |      |  |  |

|------------------------|--------|------------------|----------|------|--|--|

| Dimension              | Limits | MIN              | NOM      | MAX  |  |  |

| Number of Pins         | N      |                  | 64       |      |  |  |

| Pitch                  | е      |                  | 0.50 BSC |      |  |  |

| Overall Height         | A      | 0.80             | 0.90     | 1.00 |  |  |

| Standoff               | A1     | 0.00             | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3     | 0.20 REF         |          |      |  |  |

| Overall Width          | E      |                  | 9.00 BSC |      |  |  |

| Exposed Pad Width      | E2     | 5.30             | 5.40     | 5.50 |  |  |

| Overall Length         | D      | 9.00 BSC         |          |      |  |  |

| Exposed Pad Length     | D2     | 5.30             | 5.40     | 5.50 |  |  |

| Contact Width          | b      | 0.20             | 0.25     | 0.30 |  |  |

| Contact Length         | L      | 0.30             | 0.40     | 0.50 |  |  |

| Contact-to-Exposed Pad | К      | 0.20             | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2