Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 30x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-VQFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1526-i-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

## 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing a  $32K \times 14$  program memory space. Table 3-1 shows the memory sizes implemented for the PIC16(L)F1526/7 family. Accessing a location above these boundaries will cause a

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device                    | Program Memory<br>Space (Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |

|---------------------------|---------------------------------|--------------------------------|-------------------------------------------------------------|

| PIC16F1526<br>PIC16LF1526 | 8,192                           | 1FFFh                          | 1F80h-1FFFh                                                 |

| PIC16F1527<br>PIC16LF1527 | 16,384                          | 3FFFh                          | 3F80h-3FFFh                                                 |

Note 1: High-endurance Flash applies to the low byte of each address in the range.

wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1 and Figure 3-2).

## 3.2 High Endurance Flash

This device has a 128-byte section of high-endurance Program Flash Memory (PFM) in lieu of data EEPROM. This area is especially well suited for nonvolatile data storage that is expected to be updated frequently over the life of the end product. See **Section 11.2** "**Flash Program Memory Overview**" for more information on writing data to PFM. Refer to section **Section 3.2.1.2** "**Indirect Read with FSR**" for more information about using the FSR registers to read byte data stored in PFM.

|            |         | -      |        |        |        |        |         |        |                     |

|------------|---------|--------|--------|--------|--------|--------|---------|--------|---------------------|

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF  | 76                  |

| IOCBF      | IOCBF7  | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3 | IOCBF2 | IOCBF1  | IOCBF0 | 137                 |

| IOCBN      | IOCBN7  | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3 | IOCBN2 | IOCBN1  | IOCBN0 | 137                 |

| IOCBP      | IOCBP7  | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3 | IOCBP2 | IOCBP1  | IOCBP0 | 137                 |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    |        | PS<2:0> |        | 158                 |

| PIE1       | TMR1GIE | ADIE   | RC1IE  | TX1IE  | SSP1IE | SSP2IE | TMR2IE  | TMR1IE | 77                  |

| PIE2       | —       | AD2IE  | —      | —      | BCL1IE | BCL2IE | TMR4IE  | —      | 78                  |

| PIE3       | CCP6IE  | CCP5IE | CCP4IE | CCP3IE | TMR6IE | TMR5IE | TMR4IE  | TMR3IE | 79                  |

| PIE4       | CCP10IE | CCP9IE | RC2IE  | TX2IE  | CCP8IE | CCP7IE | BCL2IE  | SSP2IE | 80                  |

| PIR1       | TMR1GIF | AD1IF  | RCIF   | TXIF   | SSP1IF | SSP2IF | TMR2IF  | TMR1IF | 81                  |

| PIR2       | —       | AD2IF  | —      | —      | BCL1IF | BCL2IF | TMR4IF  | —      | 82                  |

| PIR3       | CCP6IF  | CCP5IF | CCP4IF | CCP3IF | TMR6IF | TMR5IF | TMR4IF  | TMR3IF | 83                  |

| PIR4       | CCP10IF | CCP9IF | RC2IF  | TX2IF  | CCP8IF | CCP7IF | BCL2IF  | SSP2IF | 84                  |

| TABLE 7-1: | SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS |

|------------|-------------------------------------------------|

|            |                                                 |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used by Interrupts.

# 10.6 Register Definitions: Watchdog Control

| U-0                          | U-0                          | R/W-0/0                                                          | R/W-1/1       | R/W-0/0          | R/W-1/1        | R/W-1/1  | R/W-0/0      |

|------------------------------|------------------------------|------------------------------------------------------------------|---------------|------------------|----------------|----------|--------------|

| —                            |                              |                                                                  |               | WDTPS<4:0>       |                |          | SWDTEN       |

| pit 7                        |                              |                                                                  |               |                  |                |          | bit (        |

| agandi                       |                              |                                                                  |               |                  |                |          |              |

| <b>₋egend:</b><br>R = Readat | ole bit                      | W = Writable                                                     | bit           | U = Unimplem     | ented bit, rea | d as '0' |              |

| u = Bit is ur                |                              | x = Bit is unkr                                                  |               | -m/n = Value a   |                |          | other Resets |

| 1' = Bit is s                | •                            | '0' = Bit is clea                                                |               |                  |                |          |              |

|                              | Unimplome                    | nted. Dood oo f                                                  | <u>,</u>      |                  |                |          |              |

| oit 7-6<br>oit 5-1           | -                            | nted: Read as '<br><b>)&gt;:</b> Watchdog Til                    |               | elect hits(1)    |                |          |              |

| <i>n</i> t 0-1               |                              | Prescale Rate                                                    |               | elect bits.      |                |          |              |

|                              |                              | eserved. Results                                                 | s in minimum  | interval (1:32)  |                |          |              |

|                              | •                            |                                                                  |               | intervar (1.52)  |                |          |              |

|                              | •                            |                                                                  |               |                  |                |          |              |

|                              | •                            |                                                                  |               |                  |                |          |              |

|                              | 10011 = R                    | eserved. Results                                                 | s in minimum  | interval (1:32)  |                |          |              |

|                              | 10010 = <b>1</b> :           | :8388608 (2 <sup>23</sup> ) (                                    | nterval 256s  | nominal)         |                |          |              |

|                              | 10001 = <b>1</b> :           | :4194304 (2 <sup>22</sup> ) (I                                   | nterval 128s  | nominal)         |                |          |              |

|                              | 10000 <b>= 1</b> :           | :2097152 (2 <sup>21</sup> ) (1                                   | nterval 64s r | iominal)         |                |          |              |

|                              | 01111 = 1:                   | 1048576 (2 <sup>20</sup> ) (1                                    | nterval 32s r | iominal)         |                |          |              |

|                              | 01110 = 1                    | :524288 (2 <sup>19</sup> ) (In<br>:262144 (2 <sup>18</sup> ) (In | terval 16s no | ninal)           |                |          |              |

|                              |                              | :131072 (2 <sup>17</sup> ) (In                                   |               |                  |                |          |              |

|                              |                              | 65536 (Interval                                                  |               |                  |                |          |              |

|                              |                              | 32768 (Interval                                                  |               | ,                |                |          |              |

|                              |                              | 16384 (Interval                                                  |               | ,                |                |          |              |

|                              |                              | 8192 (Interval 2                                                 |               |                  |                |          |              |

|                              |                              | :4096 (Interval 1)<br>:2048 (Interval 6                          |               | · ·              |                |          |              |

|                              |                              | :1024 (Interval 3                                                |               | ,                |                |          |              |

|                              |                              | 512 (Interval 16                                                 |               |                  |                |          |              |

|                              |                              | 256 (Interval 8 r                                                |               |                  |                |          |              |

|                              |                              | 128 (Interval 4 r                                                |               |                  |                |          |              |

|                              |                              | 64 (Interval 2 m                                                 |               |                  |                |          |              |

|                              |                              | 32 (Interval 1 m                                                 |               |                  |                |          |              |

| oit O                        |                              |                                                                  | Disable for V | Vatchdog Timer b | it             |          |              |

|                              | If WDTE<1:                   |                                                                  |               |                  |                |          |              |

|                              | This bit is ig<br>If WDTE<1: |                                                                  |               |                  |                |          |              |

|                              | 1 = WDT is                   |                                                                  |               |                  |                |          |              |

|                              | 0 = WDT is                   |                                                                  |               |                  |                |          |              |

|                              | <u>If WDTE&lt;1:</u>         | 0 > = 1 v                                                        |               |                  |                |          |              |

|                              | This bit is ig               |                                                                  |               |                  |                |          |              |

## REGISTER 10-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

Note 1: Times are approximate. WDT time is based on 31 kHz LFINTOSC.

| U-0                                     | R/W-1/1           | R/W-1/1                                                                            | R/W-1/1                                        | R/W-1/1                                                                                                                         | R/W-1/1                                                                                                                                                                                | R/W-1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------|-------------------|------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| —                                       | ANSB5             | ANSB4                                                                              | ANSB3                                          | ANSB2                                                                                                                           | ANSB1                                                                                                                                                                                  | ANSB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                   |                                                                                    |                                                |                                                                                                                                 |                                                                                                                                                                                        | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                   |                                                                                    |                                                |                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                         |                   |                                                                                    |                                                |                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| R = Readable bit W = Writable bit       |                   |                                                                                    | U = Unimplen                                   | nented bit, read                                                                                                                | l as '0'                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I = Bit is unchanged x = Bit is unknown |                   | nown                                                                               | -n/n = Value a                                 | at POR and BO                                                                                                                   | R/Value at all                                                                                                                                                                         | other Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                         | '0' = Bit is clea | ared                                                                               |                                                |                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                         |                   | ANSB5       —     ANSB5       bit     W = Writable       anged     x = Bit is unkr | ANSB5     ANSB4       bit     W = Writable bit | ANSB5     ANSB4     ANSB3       bit     W = Writable bit     U = Unimplen       anged     x = Bit is unknown     -n/n = Value a | ANSB5       ANSB4       ANSB3       ANSB2         bit       W = Writable bit       U = Unimplemented bit, read         anged       x = Bit is unknown       -n/n = Value at POR and BO | ANSB5ANSB4ANSB3ANSB2ANSB1bitW = Writable bitU = Unimplemented bit, read as '0'angedx = Bit is unknown-n/n = Value at POR and BOR/Value at all of the second s |

#### REGISTER 12-9: ANSELB: PORTB ANALOG SELECT REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **ANSB<5:0>**: Analog Select between Analog or Digital Function on pins RB<5:0>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled. 0 = Digital I/O. Pin is assigned to port or digital special function.

#### REGISTER 12-10: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

#### Legend:

| 0                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **WPUB<7:0>**: Weak Pull-up Register bits

1 = Pull-up enabled

0 = Pull-up disabled

- Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1    | Bit 0   | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|----------|---------|---------------------|

| APFCON | —      | —      | -      | -      | -      | —      | T3CKISEL | CCP2SEL | 118                 |

| ANSELB | —      | —      | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1    | ANSB0   | 118                 |

| LATB   | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1    | LATB0   | 117                 |

| PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1      | RB0     | 117                 |

| TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1   | TRISB0  | 117                 |

| WPUB   | WPUB7  | WPUB6  | WPUB5  | WPUB4  | WPUB3  | WPUB2  | WPUB1    | WPUB0   | 118                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

## 12.10 Register Definitions: PORTD

### REGISTER 12-14: PORTD: PORTD REGISTER

| R/W-x/u                                 | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                            | R/W-x/u        | R/W-x/u          | R/W-x/u     |  |  |

|-----------------------------------------|---------|-------------------|---------|------------------------------------|----------------|------------------|-------------|--|--|

| RD7                                     | RD6     | RD5               | RD4     | RD3                                | RD2            | RD1              | RD0         |  |  |

| bit 7                                   |         |                   |         |                                    |                |                  | bit 0       |  |  |

|                                         |         |                   |         |                                    |                |                  |             |  |  |

| Legend:                                 |         |                   |         |                                    |                |                  |             |  |  |

| R = Readable bit W = Writable bit       |         |                   |         | U = Unimplemented bit, read as '0' |                |                  |             |  |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | iown    | -n/n = Value a                     | at POR and BOI | R/Value at all o | ther Resets |  |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared    |                                    |                |                  |             |  |  |

bit 7-0 **RD<7:0>**: PORTD General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

#### REGISTER 12-15: TRISD: PORTD TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISD<7:0>: PORTD Tri-State Control bits

1 = PORTD pin configured as an input (tri-stated)

0 = PORTD pin configured as an output

## REGISTER 12-16: LATD: PORTD DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATD7   | LATD6   | LATD5   | LATD4   | LATD3   | LATD2   | LATD1   | LATD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 LATD<7:0>: PORTD Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTD are actually written to corresponding LATD register. Reads from PORTD register is return of actual I/O pin values.

## 12.16 Register Definitions: PORTG

#### REGISTER 12-28: PORTG: PORTG REGISTER

| U-0                                     | U-0 | R-x/u             | R/W-x/u        | R/W-x/u       | R/W-x/u          | R/W-x/u     | R/W-x/u |

|-----------------------------------------|-----|-------------------|----------------|---------------|------------------|-------------|---------|

| _                                       | —   | RG5               | RG4            | RG3           | RG2              | RG1         | RG0     |

| bit 7                                   | •   | •                 |                |               |                  | •           | bit 0   |

|                                         |     |                   |                |               |                  |             |         |

| Legend:                                 |     |                   |                |               |                  |             |         |

| R = Readable                            | bit | W = Writable      | bit            | U = Unimpler  | mented bit, read | as '0'      |         |

| u = Bit is unchanged x = Bit is unknown |     | nown              | -n/n = Value a | at POR and BO | R/Value at all o | ther Resets |         |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared           |               |                  |             |         |

bit 7-6

Unimplemented: Read as '0'

bit 5-0

RG<5:0>: PORTG I/O Pin bits<sup>(1)</sup>

1 = Port pin is > VIH

0 = Port pin is < VIL

**Note 1:** Writes to PORTG are actually written to corresponding LATG register. Reads from PORTG register is return of actual I/O pin values.

#### REGISTER 12-29: TRISG: PORTG TRI-STATE REGISTER

| U-0   | U-0 | U-1 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | (1) | TRISG4 | TRISG3 | TRISG2 | TRISG1 | TRISG0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 Unimplemented: Read as ' | 0' |

|----------------------------------|----|

|----------------------------------|----|

bit 5 Unimplemented: Read as '1'

bit 4-0 **TRISG<4:0>:** RG<4:0> Tri-State Control bits<sup>(1)</sup> 1 = PORTG pin configured as an input (tri-stated) 0 = PORTG pin configured as an output

Note 1: Unimplemented, read as '1'.

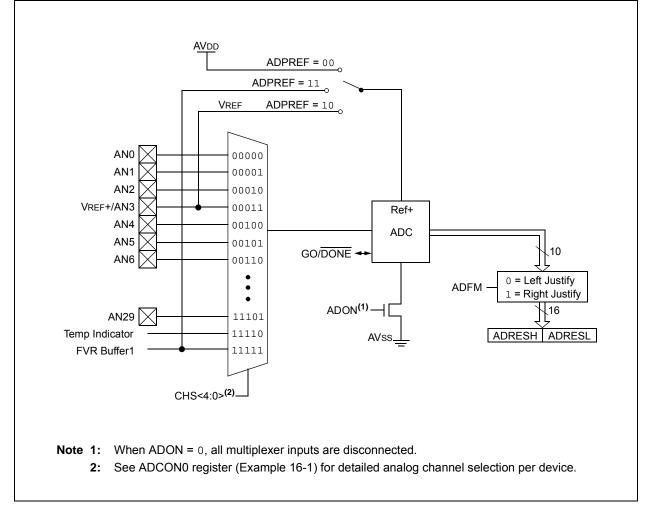

# 16.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 16-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

## FIGURE 16-1: ADC BLOCK DIAGRAM

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

## 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 16.2.6 "ADC Conver-     |

|       | sion Procedure".                         |

#### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

## 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device          | ССР   |

|-----------------|-------|

| PIC16(L)F1526/7 | CCP10 |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to **Section 20.0** "Capture/Compare/PWM **Modules**" for more information.

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | ADRE    | S<9:2>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable b    | oit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkno  | own     | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | red     |                |                  |                |              |

## **REGISTER 16-3:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

bit 7-0 ADRES<9:2>: ADC Result Register bits Upper 8 bits of 10-bit conversion result

#### **REGISTER 16-4:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | S<1:0>  | —       | —       | —       | —       | —       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 ADRES<1:0>: ADC Result Register bits Lower 2 bits of 10-bit conversion result bit 5-0 Reserved: Do not use.

© 2011-2015 Microchip Technology Inc.

#### 17.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|

|       | independent prescaler.                |  |  |  |  |

There are 8 prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

## 17.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |

|-------|-----------------------------------------|--|--|

|       | processor from Sleep since the timer is |  |  |

|       | frozen during Sleep.                    |  |  |

## 17.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 25.0** "**Electrical Specifications**".

## 17.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

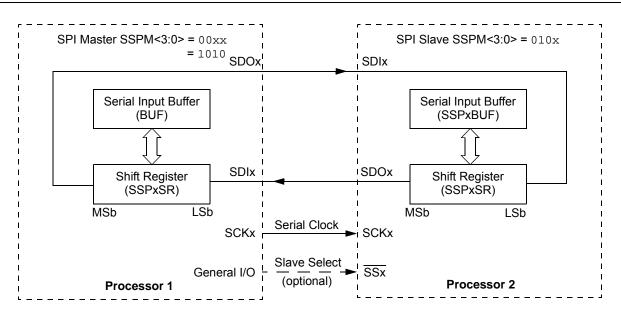

## 21.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- · Master mode (SCKx is the clock output)

- · Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSPx Enable bit, SSPEN of the SSPxCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPxCONx registers and then set the SSPEN bit. This configures the SDIx, SDOx, SCKx and SSx pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDIx must have corresponding TRIS bit set

- · SDOx must have corresponding TRIS bit cleared

- SCKx (Master mode) must have corresponding TRIS bit cleared

- SCKx (Slave mode) must have corresponding TRIS bit set

- SSx must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSPx consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write the **SSPxBUF** reaister to durina transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPxCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSPx interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

## FIGURE 21-5: SPI MASTER/SLAVE CONNECTION

#### 21.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCKx line. The master determines when the slave (Processor 2, Figure 21-5) is to broadcast data by the software protocol.

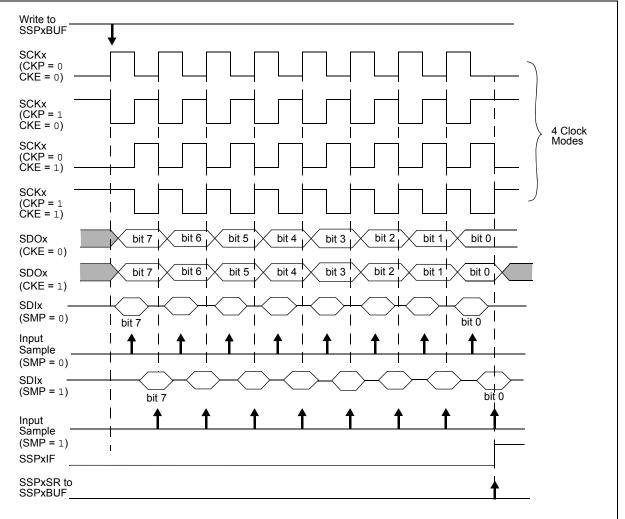

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDOx output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDIx pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPxCON1 register and the CKE bit of the SSPxSTAT register. This then, would give waveforms for SPI communication as shown in Figure 21-6, Figure 21-8, Figure 21-9 and Figure 21-10, where the MSb is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPxADD + 1))

Figure 21-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDOx data is valid before there is a clock edge on SCKx. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

FIGURE 21-6: SPI MODE WAVEFORM (MASTER MODE)

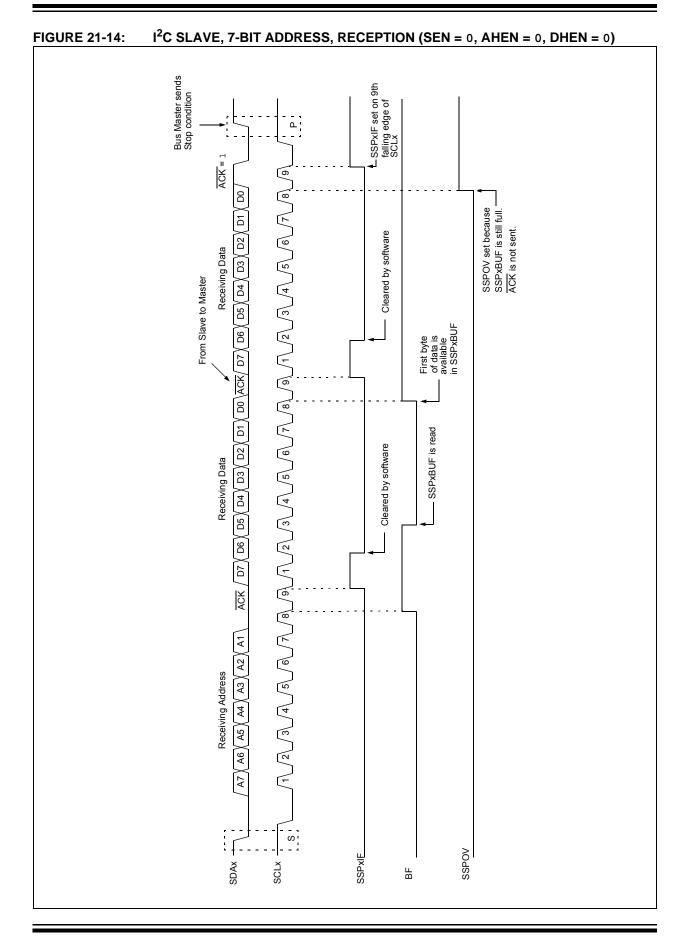

#### 21.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSPx module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 21-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with  $R/\overline{W}$  bit clear; UA bit of the SSPxSTAT register is set.

- 4. Slave sends ACK and SSPxIF is set.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. Slave loads low address into SSPxADD, releasing SCLx.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPxADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSPxIF is set.

**Note:** If the low address does not match, SSPxIF and UA are still set so that the slave software can set SSPxADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPxIF.

- 11. Slave reads the received matching address from SSPxBUF clearing BF.

- 12. Slave loads high address into SSPxADD.

- 13. Master clocks a data <u>byte</u> to the slave and clocks out the slaves ACK on the 9th SCLx pulse; SSPxIF is set.

- 14. If SEN bit of SSPxCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPxIF.

- 16. Slave reads the received byte from SSPxBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCLx.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

#### 21.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPxADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCLx line is held low are the same. Figure 21-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 21-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

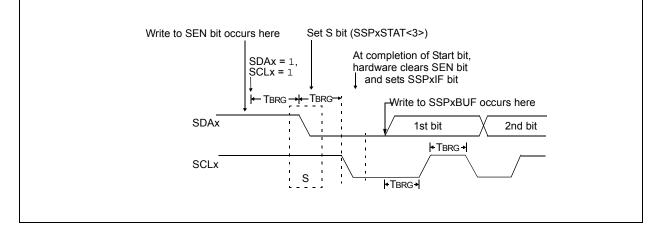

## 21.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 21-26), the user sets the Start Enable bit, SEN bit of the SSPxCON2 register. If the SDAx and SCLx pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCLx and SDAx are both sampled high when the Baud Rate Generator times out (TBRG), the SDAx pin is driven low. The action of the SDAx being driven low while SCLx is high is the Start condition and causes the S bit of the SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SDAx bit of the SSPxADD<7:0> and resumes its count. When the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared

FIGURE 21-26: FIRST START BIT TIMING

by hardware; the Baud Rate Generator is suspended, leaving the SDAx line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDAx and SCLx pins are already sampled low, or if during the Start condition, the SCLx line is sampled low before the SDAx line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- **2:** The Philips I<sup>2</sup>C Specification states that a bus collision cannot occur on a Start.

## 22.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 22.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXxSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART. If the RXx/DTx or TXx/CKx pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

The TRIS bits corresponding to the RXx/DTx and TXx/CKx pins should be set.

#### 22.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TXx/CKx line. The TXx/CKx pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

## 22.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDxCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock and is sampled on the rising edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock and is sampled on the falling edge of each clock.

#### 22.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RXx/DTx pin. The RXx/DTx and TXx/CKx pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXxREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXxREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXxREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

# 25.7 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| т                                          |                          |     |                |  |

|--------------------------------------------|--------------------------|-----|----------------|--|

| F                                          | Frequency                | Т   | Time           |  |

| Lowercase letters (pp) and their meanings: |                          |     |                |  |

| рр                                         |                          |     |                |  |

| сс                                         | CCP1                     | OSC | OSC1           |  |

| ck                                         | CLKOUT                   | rd  | RD             |  |

| CS                                         | CS                       | rw  | RD or WR       |  |

| di                                         | SDIx                     | sc  | SCKx           |  |

| do                                         | SDO                      | SS  | SS             |  |

| dt                                         | Data in                  | tO  | TOCKI          |  |

| io                                         | I/O PORT                 | t1  | T1CKI          |  |

| mc                                         | MCLR                     | wr  | WR             |  |

| Uppercase letters and their meanings:      |                          |     |                |  |

| S                                          |                          |     |                |  |

| F                                          | Fall                     | Р   | Period         |  |

| Н                                          | High                     | R   | Rise           |  |

| I                                          | Invalid (High-impedance) | V   | Valid          |  |

| L                                          | Low                      | Z   | High-impedance |  |

#### FIGURE 25-5: LOAD CONDITIONS