Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

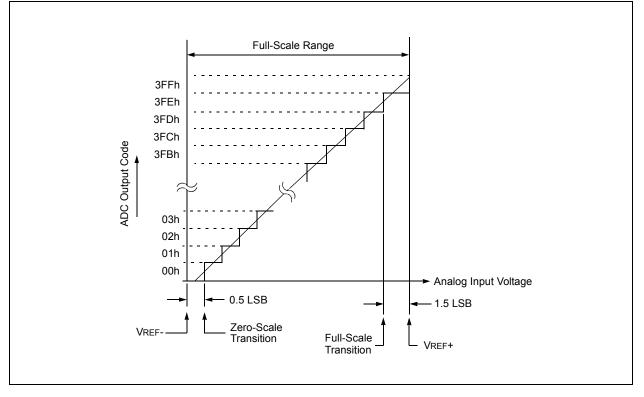

| Data Converters            | A/D 30x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-VQFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1527-e-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### PIC16(L)F151X/152X Family Types

|               |                  |                                 |                      | tes)                         |          | AI          | C                |                      |        |                             |     |                      |     |

|---------------|------------------|---------------------------------|----------------------|------------------------------|----------|-------------|------------------|----------------------|--------|-----------------------------|-----|----------------------|-----|

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High-Endurance Flash (bytes) | (Z)S,O/I | 10-bit (ch) | Advanced Control | Timers<br>(8/16-bit) | EUSART | MSSP (I <sup>2</sup> C/SPI) | ССР | Debug <sup>(1)</sup> | XLP |

| PIC16(L)F1512 | (1)              | 2048                            | 128                  | 128                          | 25       | 17          | Y                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1513 | (1)              | 4096                            | 256                  | 128                          | 25       | 17          | Y                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1516 | (2)              | 8192                            | 512                  | 128                          | 25       | 17          | N                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1517 | (2)              | 8192                            | 512                  | 128                          | 36       | 28          | Ν                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1518 | (2)              | 16384                           | 1024                 | 128                          | 25       | 17          | Ν                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1519 | (2)              | 16384                           | 1024                 | 128                          | 36       | 28          | Ν                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1526 | (3)              | 8192                            | 768                  | 128                          | 54       | 30          | N                | 6/3                  | 2      | 2                           | 10  |                      | Y   |

| PIC16(L)F1527 | (3)              | 16384                           | 1536                 | 128                          | 54       | 30          | Ν                | 6/3                  | 2      | 2                           | 10  |                      | Y   |

Note 1: I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS41624 PIC16(L)F1512/13 Data Sheet, 28-Pin Flash, 8-bit Microcontrollers.

- **2:** DS41452 PIC16(L)F1516/7/8/9 Data Sheet, 28/40/44-Pin Flash, 8-bit MCUs.

- **3:** DS41458 PIC16(L)F1526/7 Data Sheet, 64-Pin Flash, 8-bit MCUs.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

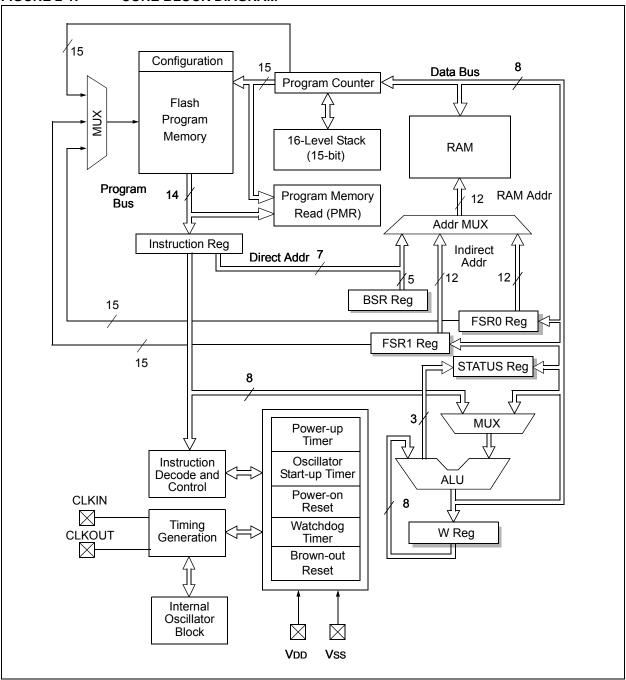

#### 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative Addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

FIGURE 2-1: CORE BLOCK DIAGRAM

#### TABLE 3-3: PIC16(L)F1526/7 MEMORY MAP

|              | BANK 0                                     |              | BANK 1                                     |              | BANK 2                                     |              | BANK 3                                     |              | BANK 4                                     |              | BANK 5                                     |              | BANK 6                                     |              | BANK 7                                     |

|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|--------------|--------------------------------------------|

| 000h         |                                            | 080h         |                                            | 100h         |                                            | 180h         |                                            | 200h         |                                            | 280h         |                                            | 300h         |                                            | 380h         |                                            |

|              | Core Registers<br>(Table 3-2)              |

| 00Bh         |                                            | 08Bh         |                                            | 10Bh         |                                            | 18Bh         |                                            | 20Bh         |                                            | 28Bh         |                                            | 30Bh         |                                            | 38Bh         |                                            |

| 00Ch         | PORTA                                      | 08Ch         | TRISA                                      | 10Ch         | LATA                                       | 18Ch         | ANSELA                                     | 20Ch         | —                                          | 28Ch         | PORTF                                      | 30Ch         | TRISF                                      | 38Ch         | LATF                                       |

| 00Dh         | PORTB                                      | 08Dh         | TRISB                                      | 10Dh         | LATB                                       | 18Dh         | ANSELB                                     | 20Dh         | WPUB                                       | 28Dh         | PORTG                                      | 30Dh         | TRISG                                      | 38Dh         | LATG                                       |

| 00Eh         | PORTC                                      | 08Eh         | TRISC                                      | 10Eh         | LATC                                       | 18Eh         | —                                          | 20Eh         | —                                          | 28Eh         | _                                          | 30Eh         | —                                          | 38Eh         | —                                          |

| 00Fh         | PORTD                                      | 08Fh         | TRISD                                      | 10Fh         | LATD                                       | 18Fh         | ANSELD                                     | 20Fh         | WPUD                                       | 28Fh         | -                                          | 30Fh         | —                                          | 38Fh         | —                                          |

| 010h         | PORTE                                      | 090h         | TRISE                                      | 110h         | LATE                                       | 190h         | ANSELE                                     | 210h         | WPUE                                       | 290h         | —                                          | 310h         | —                                          | 390h         | —                                          |

| 011h         | PIR1                                       | 091h         | PIE1                                       | 111h         | —                                          | 191h         | PMADRL                                     | 211h         | SSP1BUF                                    | 291h         | CCPR1L                                     | 311h         | CCPR3L                                     | 391h         | —                                          |

| 012h         | PIR2                                       | 092h         | PIE2                                       | 112h         | _                                          | 192h         | PMADRH                                     | 212h         | SSP1ADD                                    | 292h         | CCPR1H                                     | 312h         | CCPR3H                                     | 392h         | —                                          |

| 013h         | PIR3                                       | 093h         | PIE3                                       | 113h         | _                                          | 193h         | PMDATL                                     | 213h         | SSP1MSK                                    | 293h         | CCP1CON                                    | 313h         | CCP3CON                                    | 393h         | —                                          |

| 014h         | PIR4                                       | 094h         | PIE4                                       | 114h         | _                                          | 194h         | PMDATH                                     | 214h         | SSP1STAT                                   | 294h         | _                                          | 314h         | —                                          | 394h         | IOCBP                                      |

| 015h         | TMR0                                       | 095h         | OPTION_REG                                 | 115h         | _                                          | 195h         | PMCON1                                     | 215h         | SSP1CON1                                   | 295h         | —                                          | 315h         | —                                          | 395h         | IOCBN                                      |

| 016h         | TMR1L                                      | 096h         | PCON                                       | 116h         | BORCON                                     | 196h         | PMCON2                                     | 216h         | SSP1CON2                                   | 296h         | _                                          | 316h         | —                                          | 396h         | IOCBF                                      |

| 017h         | TMR1H                                      | 097h         | WDTCON                                     | 117h         | FVRCON                                     | 197h         | VREGCON <sup>(1)</sup>                     | 217h         | SSP1CON3                                   | 297h         |                                            | 317h         | _                                          | 397h         | —                                          |

| 018h         | T1CON                                      | 098h         | —                                          | 118h         | _                                          | 198h         | —                                          | 218h         | _                                          | 298h         | CCPR2L                                     | 318h         | CCPR4L                                     | 398h         | —                                          |

| 019h         | T1GCON                                     | 099h         | OSCCON                                     | 119h         | _                                          | 199h         | RC1REG                                     | 219h         | SSP2BUF                                    | 299h         | CCPR2H                                     | 319h         | CCPR4H                                     | 399h         | —                                          |

| 01Ah         | TMR2                                       | 09Ah         | OSCSTAT                                    | 11Ah         | —                                          | 19Ah         | TX1REG                                     | 21Ah         | SSP2ADD                                    | 29Ah         | CCP2CON                                    | 31Ah         | CCP4CON                                    | 39Ah         | —                                          |

| 01Bh         | PR2                                        | 09Bh         | ADRESL                                     | 11Bh         | —                                          | 19Bh         | SP1BRG                                     | 21Bh         | SSP2MSK                                    | 29Bh         | —                                          | 31Bh         | —                                          | 39Bh         | —                                          |

| 01Ch         | T2CON                                      | 09Ch         | ADRESH                                     | 11Ch         | —                                          | 19Ch         | SP1BRGH                                    | 21Ch         | SSP2STAT                                   | 29Ch         | _                                          | 31Ch         | CCPR5L                                     | 39Ch         | —                                          |

| 01Dh         | _                                          | 09Dh         | ADCON0                                     | 11Dh         | APFCON                                     | 19Dh         | RC1STA                                     | 21Dh         | SSP2CON1                                   | 29Dh         | CCPTMRS0                                   | 31Dh         | CCPR5H                                     | 39Dh         | —                                          |

| 01Eh         | _                                          | 09Eh         | ADCON1                                     | 11Eh         | _                                          | 19Eh         | TX1STA                                     | 21Eh         | SSP2CON2                                   | 29Eh         | CCPTMRS1                                   | 31Eh         | CCP5CON                                    | 39Eh         | —                                          |

| 01Fh         | —                                          | 09Fh         | _                                          | 11Fh         | —                                          | 19Fh         | BAUD1CON                                   | 21Fh         | SSP2CON3                                   | 29Fh         | CCPTMRS2                                   | 31Fh         | _                                          | 39Fh         | _                                          |

| 020h         |                                            | 0A0h         |                                            | 120h         |                                            | 1A0h         |                                            | 220h         |                                            | 2A0h         |                                            | 320h         |                                            | 3A0h         |                                            |

|              | General<br>Purpose<br>Register<br>80 Bytes |

| 06Fh         |                                            | 0EFh         |                                            | 16Fh         |                                            | 1EFh         |                                            | 26Fh         |                                            | 2EFh         |                                            | 36Fh         |                                            | 3EFh         |                                            |

| 070h<br>07Fh | Common RAM                                 | 0F0h<br>0FFh | Common RAM<br>(Accesses<br>70h – 7Fh)      | 170h<br>17Fh | Common RAM<br>(Accesses<br>70h – 7Fh)      | 1F0h<br>1FFh | Common RAM<br>(Accesses<br>70h – 7Fh)      | 270h<br>27Fh | Common RAM<br>(Accesses<br>70h – 7Fh)      | 2F0h<br>2FFh | Common RAM<br>(Accesses<br>70h – 7Fh)      | 370h<br>37Fh | Common RAM<br>(Accesses<br>70h – 7Fh)      | 3F0h<br>3FFh | Common RAM<br>(Accesses<br>70h – 7Fh)      |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: PIC16F1526/7 only.

## 3.5.4 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-4 can be addressed from any Bank.

| Addr            | Name   | Bit 7        | Bit 6                                                      | Bit 5         | Bit 4        | Bit 3       | Bit 2         | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on all other Resets |

|-----------------|--------|--------------|------------------------------------------------------------|---------------|--------------|-------------|---------------|--------|-------|----------------------|---------------------------|

| Bank            | 0-31   |              |                                                            |               |              |             |               |        |       |                      |                           |

| x00h or<br>x80h | INDF0  |              | this location<br>ical register)                            |               | xxxx xxxx    | uuuu uuuu   |               |        |       |                      |                           |

| x01h or<br>x81h | INDF1  |              | this location<br>ical register)                            |               | nts of FSR1H | /FSR1L to a | ddress data r | memory |       | xxxx xxxx            | uuuu uuuu                 |

| x02h or<br>x82h | PCL    | Program Co   | ounter (PC) I                                              | Least Signifi | cant Byte    |             |               |        |       | 0000 0000            | 0000 0000                 |

| x03h or<br>x83h | STATUS | _            | -                                                          | -             | TO           | PD          | Z             | DC     | С     | 1 1000               | q quuu                    |

| x04h or<br>x84h | FSR0L  | Indirect Dat | direct Data Memory Address 0 Low Pointer                   |               |              |             |               |        |       |                      | uuuu uuuu                 |

| x05h or<br>x85h | FSR0H  | Indirect Dat | ndirect Data Memory Address 0 High Pointer                 |               |              |             |               |        |       | 0000 0000            | 0000 0000                 |

| x06h or<br>x86h | FSR1L  | Indirect Dat | ta Memory A                                                | ddress 1 Lo   | w Pointer    |             |               |        |       | 0000 0000            | uuuu uuuu                 |

| x07h or<br>x87h | FSR1H  | Indirect Dat | ta Memory A                                                | ddress 1 Hig  | gh Pointer   |             |               |        |       | 0000 0000            | 0000 0000                 |

| x08h or<br>x88h | BSR    | _            | -                                                          | -             | BSR4         | BSR3        | BSR2          | BSR1   | BSR0  | 0 0000               | 0 0000                    |

| x09h or<br>x89h | WREG   | Working Re   | Working Register                                           |               |              |             |               |        |       | 0000 0000            | uuuu uuuu                 |

| x0Ahor<br>x8Ah  | PCLATH | _            | — Write Buffer for the upper 7 bits of the Program Counter |               |              |             |               |        |       | -000 0000            | -000 0000                 |

| x0Bhor<br>x8Bh  | INTCON | GIE          | PEIE                                                       | TMR0IE        | INTE         | IOCIE       | TMR0IF        | INTF   | IOCIF | 0000 0000            | 0000 0000                 |

#### TABLE 3-4: CORE FUNCTION REGISTERS SUMMARY

#### 4.6 Device ID and Revision ID

The memory location 8006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See **Section 11.5 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

#### REGISTER 4-3: DEVID: DEVICE ID REGISTER

|                |          | R      | R | R             | R                  | R   | R     |

|----------------|----------|--------|---|---------------|--------------------|-----|-------|

|                |          |        |   | DEV           | <8:3>              |     |       |

|                |          | bit 13 |   |               |                    |     | bit 8 |

|                |          |        |   |               |                    |     |       |

| R              | R        | R      | R | R             | R                  | R   | R     |

|                | DEV<2:0> |        |   |               | REV<4:0>           |     |       |

| bit 7          |          |        |   |               |                    |     | bit 0 |

|                |          |        |   |               |                    |     |       |

| Legend:        |          |        |   |               |                    |     |       |

| R = Readable b | bit      |        |   | U = Unimpleme | ented bit, read as | '1' |       |

-n/n = Value at POR and BOR/Value at all other Resets

#### bit 13-5 DEV<8:0>: Device ID bits

| Device      | DEVID<13:0> Values |          |  |  |  |  |  |  |  |

|-------------|--------------------|----------|--|--|--|--|--|--|--|

| Device      | DEV<8:0>           | REV<4:0> |  |  |  |  |  |  |  |

| PIC16F1526  | 01 0101 100        | x xxxx   |  |  |  |  |  |  |  |

| PIC16F1527  | 01 0101 101        | x xxxx   |  |  |  |  |  |  |  |

| PIC16LF1526 | 01 0101 110        | x xxxx   |  |  |  |  |  |  |  |

| PIC16LF1527 | 01 0101 111        | x xxxx   |  |  |  |  |  |  |  |

bit 4-0 REV<4:0>: Revision ID bits

These bits are used to identify the revision (see Table under DEV<8:0> above).

#### 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                          |

|--------|--------|------|-------|----|-----|-----|----|----|------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                     |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, TO is set on POR          |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, PD is set on POR          |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                    |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                          |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep             |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep       |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep            |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed         |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)  |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1) |

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

#### TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00-1 110x        |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu-u Ouuu        |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu-u Ouuu        |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu-0 uuuu        |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu-u uuuu        |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00-1 11u0        |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu-u uuuu        |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu-u u0uu        |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu-u uuuu        |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul-u uuuu        |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

| R/W-0/0          | R/W-0/0                        | R-0/0             | R-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0  | R/W-0/0     |

|------------------|--------------------------------|-------------------|-----------------|------------------|------------------|----------|-------------|

| CCP10IF          | CCP9IF                         | RC2IF             | TX2IF           | CCP8IF           | CCP7IF           | BCL2IF   | SSP2IF      |

| bit 7            |                                |                   |                 |                  |                  |          | bit         |

| Legend:          |                                |                   |                 |                  |                  |          |             |

| R = Readable     | e bit                          | W = Writable      | bit             | U = Unimpler     | mented bit, read | l as '0' |             |

| u = Bit is unc   |                                | x = Bit is unk    |                 | •                | at POR and BO    |          | ther Resets |

| '1' = Bit is set | t U                            | '0' = Bit is cle  | ared            |                  |                  |          |             |

| bit 7            | CCP10IF: C                     | CP10 Interrupt    | Flag bit        |                  |                  |          |             |

| Sit 7            | 1 = Interrupt                  | •                 | nag bit         |                  |                  |          |             |

|                  |                                | t is not pending  |                 |                  |                  |          |             |

| bit 6            | CCP9IF: CC                     | P9 Interrupt Fla  | ng bit          |                  |                  |          |             |

|                  | 1 = Interrupt                  |                   |                 |                  |                  |          |             |

|                  | 0 = Interrupt                  | t is not pending  |                 |                  |                  |          |             |

| bit 5            |                                | RT2 Receive In    | iterrupt Flag b | bit              |                  |          |             |

|                  | 1 = Interrupt                  |                   |                 |                  |                  |          |             |

|                  | •                              | t is not pending  |                 | .,               |                  |          |             |

| bit 4            |                                | RT2 Transmit Ir   | iterrupt Flag b | DIT              |                  |          |             |

|                  | 1 = Interrupt<br>0 = Interrupt | t is not pending  |                 |                  |                  |          |             |

| bit 3            |                                | CP8 Interrupt Fla | a bit           |                  |                  |          |             |

|                  | 1 = Interrupt                  | •                 | ig on           |                  |                  |          |             |

|                  |                                | t is not pending  |                 |                  |                  |          |             |

| bit 2            | CCP7IF: CC                     | P7 Interrupt Fla  | ng bit          |                  |                  |          |             |

|                  | 1 = Interrupt                  | 1 0               |                 |                  |                  |          |             |

|                  | 0 = Interrupt                  | t is not pending  |                 |                  |                  |          |             |

| bit 1            |                                | SSP2 Bus Collis   | ion Interrupt F | lag bit          |                  |          |             |

|                  | 1 = Interrupt                  |                   |                 |                  |                  |          |             |

| L:1 0            |                                | t is not pending  |                 |                  | h:t              |          |             |

| bit 0            |                                | nchronous Seria   | al Port (MSSP   | 2) Interrupt Fla | g bit            |          |             |

|                  | 1 = Interrupt<br>0 = Interrupt | t is not pending  |                 |                  |                  |          |             |

|                  | ·                              |                   |                 |                  |                  |          |             |

|                  |                                | are set when an   |                 |                  |                  |          |             |

|                  |                                | regardless of th  |                 |                  |                  |          |             |

| Its              |                                | enable bit or th  |                 |                  |                  |          |             |

#### REGISTER 7-9: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4

Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior

to enabling an interrupt.

| U-0   | R/W-1/1           | R/W-1/1                                                    | R/W-1/1                            | R/W-1/1                                                                                         | R/W-1/1                                                                                                                                            | R/W-1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-------------------|------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| —     | ANSB5             | ANSB4                                                      | ANSB3                              | ANSB2                                                                                           | ANSB1                                                                                                                                              | ANSB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                   |                                                            |                                    |                                                                                                 |                                                                                                                                                    | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                   |                                                            |                                    |                                                                                                 |                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                   |                                                            |                                    |                                                                                                 |                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit   | W = Writable      | bit                                                        | U = Unimplen                       | nented bit, read                                                                                | l as '0'                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| anged | x = Bit is unkr   | nown                                                       | -n/n = Value a                     | at POR and BO                                                                                   | R/Value at all                                                                                                                                     | other Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | '0' = Bit is clea | ared                                                       |                                    |                                                                                                 |                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                   | ANSB5   — ANSB5   bit W = Writable   anged x = Bit is unkr | ANSB5 ANSB4   bit W = Writable bit | ANSB5 ANSB4 ANSB3   bit W = Writable bit U = Unimplen   anged x = Bit is unknown -n/n = Value a | ANSB5   ANSB4   ANSB3   ANSB2     bit   W = Writable bit   U = Unimplemented bit, read     anged   x = Bit is unknown   -n/n = Value at POR and BO | ANSB5ANSB4ANSB3ANSB2ANSB1bitW = Writable bitU = Unimplemented bit, read as '0'angedx = Bit is unknown-n/n = Value at POR and BOR/Value at all of the second s |

#### REGISTER 12-9: ANSELB: PORTB ANALOG SELECT REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **ANSB<5:0>**: Analog Select between Analog or Digital Function on pins RB<5:0>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled. 0 = Digital I/O. Pin is assigned to port or digital special function.

#### REGISTER 12-10: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

#### Legend:

| 0                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **WPUB<7:0>**: Weak Pull-up Register bits

1 = Pull-up enabled

0 = Pull-up disabled

- Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1    | Bit 0   | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|----------|---------|---------------------|

| APFCON | —      | —      | -      | -      | -      | —      | T3CKISEL | CCP2SEL | 118                 |

| ANSELB | —      | —      | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1    | ANSB0   | 118                 |

| LATB   | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1    | LATB0   | 117                 |

| PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1      | RB0     | 117                 |

| TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1   | TRISB0  | 117                 |

| WPUB   | WPUB7  | WPUB6  | WPUB5  | WPUB4  | WPUB3  | WPUB2  | WPUB1    | WPUB0   | 118                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

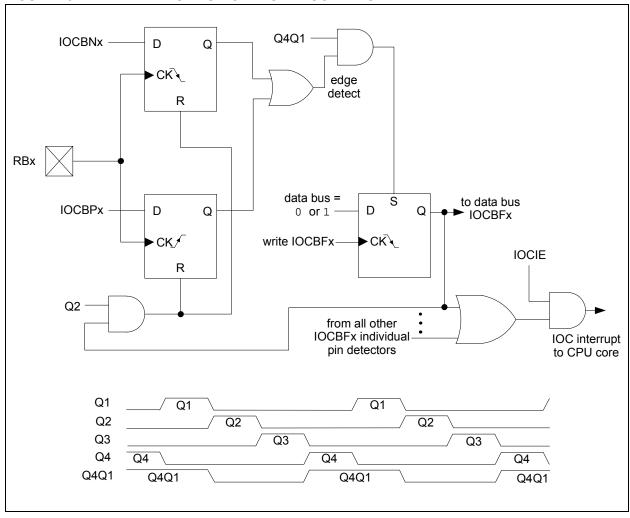

#### FIGURE 13-1: INTERRUPT-ON-CHANGE BLOCK DIAGRAM

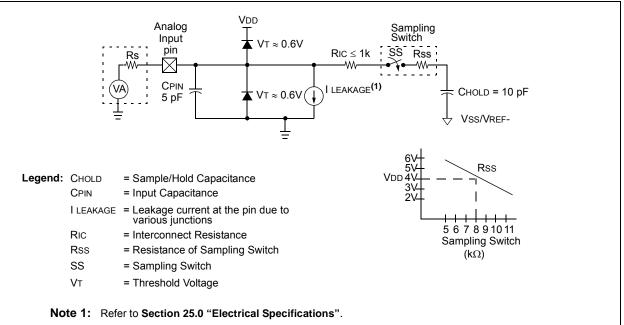

#### FIGURE 16-4: ANALOG INPUT MODEL

| Name     | Bit 7                                                       | Bit 6                                                       | Bit 5        | Bit 4                  | Bit 3  | Bit 2   | Bit 1    | Bit 0    | Register<br>on Page |  |

|----------|-------------------------------------------------------------|-------------------------------------------------------------|--------------|------------------------|--------|---------|----------|----------|---------------------|--|

| CCP1CON  | —                                                           | _                                                           | DC1B         | <1:0>                  |        | CCP1    | M<3:0>   |          | 189                 |  |

| CCP2CON  | _                                                           | _                                                           | DC2B         | <1:0>                  |        | CCP2    | V<3:0>   |          | 189                 |  |

| CCP3CON  | _                                                           | _                                                           | DC3B         | <1:0>                  |        | CCP3    | V<3:0>   |          | 189                 |  |

| CCP4CON  | —                                                           | _                                                           | DC4B         | <1:0>                  |        | CCP4    | √<3:0>   |          | 189                 |  |

| CCP5CON  | —                                                           | _                                                           | DC5B         | <1:0>                  |        | CCP5    | √<3:0>   |          | 189                 |  |

| CCP6CON  | —                                                           | _                                                           | DC6B         | <1:0>                  |        | CCP6    | V<3:0>   |          | 189                 |  |

| CCP7CON  | —                                                           | _                                                           | DC7B         | <1:0>                  |        | CCP7    | M<3:0>   |          | 189                 |  |

| CCP8CON  | —                                                           | _                                                           | DC8B         | <1:0>                  |        | CCP8    | √<3:0>   |          | 189                 |  |

| CCP9CON  | —                                                           | _                                                           | DC9B         | <1:0>                  |        | CCP9    | √<3:0>   |          | 189                 |  |

| CCP10CON | —                                                           | _                                                           | DC10         | 3<1:0>                 |        | CCP10   | M<3:0>   |          | 189                 |  |

| INTCON   | GIE                                                         | PEIE                                                        | TMR0IE       | INTE                   | IOCIE  | TMR0IF  | INTF     | IOCIF    | 76                  |  |

| PIE1     | TMR1GIE                                                     | ADIE                                                        | RC1IE        | TX1IE                  | SSP1IE | CCP1IE  | TMR2IE   | TMR1IE   | 77                  |  |

| PIE2     | OSFIE                                                       | TMR5GIE                                                     | TMR3GIE      | _                      | BCL1IE | TMR10IE | TMR8IE   | CCP2IE   | 78                  |  |

| PIE3     | CCP6IE                                                      | CCP5IE                                                      | CCP4IE       | CCP3IE                 | TMR6IE | TMR5IE  | TMR4IE   | TMR3IE   | 79                  |  |

| PIR1     | TMR1GIF                                                     | ADIF                                                        | RC1IF        | TX1IF                  | SSP1IF | CCP1IF  | TMR2IF   | TMR1IF   | 81                  |  |

| PIR2     | OSFIF                                                       | TMR5GIF                                                     | TMR3GIF      | _                      | BCL1IF | TMR10IF | TMR8IF   | CCP2IF   | 82                  |  |

| PIR3     | CCP6IF                                                      | CCP5IF                                                      | CCP4IF       | CCP3IF                 | TMR6IF | TMR5IF  | TMR4IF   | TMR3IF   | 83                  |  |

| PR2      | Timer2 Mod                                                  | ule Period Re                                               | gister       |                        |        |         |          |          | 213*                |  |

| PR4      | Timer4 Mod                                                  | ule Period Re                                               | gister       |                        |        |         |          |          | 213*                |  |

| PR6      | Timer6 Mode                                                 | ule Period Re                                               | gister       |                        |        |         |          |          | 213*                |  |

| PR8      | Timer8 Mode                                                 | ule Period Re                                               | gister       |                        |        |         |          |          | 213*                |  |

| PR10     | Timer10 Mo                                                  | dule Period R                                               | egister      |                        |        |         |          |          | 213*                |  |

| T2CON    | —                                                           |                                                             | T2OUT        | PS<3:0>                |        | TMR2ON  | T2CKPS1  | T2CKPS0  | 215                 |  |

| T4CON    | —                                                           |                                                             | T4OUT        | PS<3:0>                |        | TMR4ON  | T4CKPS1  | T4CKPS0  | 215                 |  |

| T6CON    | —                                                           |                                                             | T6OUT        | PS<3:0>                |        | TMR6ON  | T6CKPS1  | T6CKPS0  | 215                 |  |

| T8CON    | _                                                           |                                                             | T8OUT        | PS<3:0>                |        | TMR8ON  | T8CKPS1  | T8CKPS0  | 215                 |  |

| T10CON   | _                                                           |                                                             | T10OUT       | PS<3:0>                |        | TMR100N | T10CKPS1 | T10CKPS0 | 215                 |  |

| TMR2     | Holding Reg                                                 | olding Register for the 8-bit TMR2 Register                 |              |                        |        |         |          |          |                     |  |

| TMR4     | Holding Reg                                                 | Holding Register for the 8-bit TMR4 Register <sup>(1)</sup> |              |                        |        |         |          |          |                     |  |

| TMR6     | Holding Reg                                                 | lolding Register for the 8-bit TMR6 Register <sup>(1)</sup> |              |                        |        |         |          |          |                     |  |

| TMR8     | Holding Register for the 8-bit TMR8 Register <sup>(1)</sup> |                                                             |              |                        |        |         |          |          | 213*                |  |

| TMR10    | Holding Reg                                                 | ister for the 8                                             | -bit TMR10 R | egister <sup>(1)</sup> |        |         |          |          | 213*                |  |

#### TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2/4/6/8/10

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2/4/6/8/10 module.

\* Page provides register information.

|        |                   |            |                             |                   | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRC     | <b>G16 =</b> 0 |                             |                    |            |                             |

|--------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|----------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Foso           | : = 16.00      | 0 MHz                       | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                 | _          | _                           |                   |            | _                           |                | _              | _                           |                    | _          | _                           |

| 1200   | 1221              | 1.73       | 255                         | 1200              | 0.00       | 239                         | 1202           | 0.16           | 207                         | 1200               | 0.00       | 143                         |

| 2400   | 2404              | 0.16       | 129                         | 2400              | 0.00       | 119                         | 2404           | 0.16           | 103                         | 2400               | 0.00       | 71                          |

| 9600   | 9470              | -1.36      | 32                          | 9600              | 0.00       | 29                          | 9615           | 0.16           | 25                          | 9600               | 0.00       | 17                          |

| 10417  | 10417             | 0.00       | 29                          | 10286             | -1.26      | 27                          | 10417          | 0.00           | 23                          | 10165              | -2.42      | 16                          |

| 19.2k  | 19.53k            | 1.73       | 15                          | 19.20k            | 0.00       | 14                          | 19.23k         | 0.16           | 12                          | 19.20k             | 0.00       | 8                           |

| 57.6k  | —                 | _          | _                           | 57.60k            | 0.00       | 7                           | —              | _              | _                           | 57.60k             | 0.00       | 2                           |

| 115.2k | —                 | _          | —                           | _                 | _          | _                           | _              | _              | _                           | _                  | _          | —                           |

#### TABLE 22-5:BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  |            |                             |                  | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRG     | <b>616 =</b> 0 |                             |                |                  |                             |  |  |

|--------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------------|-----------------------------|--|--|

| BAUD   | Fosc = 8.000 MHz |            |                             | Fosc = 4.000 MHz |            |                             | Fosc           | : = 3.686      | 4 MHz                       | Fos            | Fosc = 1.000 MHz |                             |  |  |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |

| 300    | _                | _          | _                           | 300              | 0.16       | 207                         | 300            | 0.00           | 191                         | 300            | 0.16             | 51                          |  |  |

| 1200   | 1202             | 0.16       | 103                         | 1202             | 0.16       | 51                          | 1200           | 0.00           | 47                          | 1202           | 0.16             | 12                          |  |  |

| 2400   | 2404             | 0.16       | 51                          | 2404             | 0.16       | 25                          | 2400           | 0.00           | 23                          | _              | _                | —                           |  |  |

| 9600   | 9615             | 0.16       | 12                          | _                | _          | _                           | 9600           | 0.00           | 5                           | _              | _                | —                           |  |  |

| 10417  | 10417            | 0.00       | 11                          | 10417            | 0.00       | 5                           | _              | _              | _                           | _              | _                | _                           |  |  |

| 19.2k  | _                | _          | _                           | _                | _          | _                           | 19.20k         | 0.00           | 2                           | _              | _                | _                           |  |  |

| 57.6k  | —                | _          | _                           | —                | _          | _                           | 57.60k         | 0.00           | 0                           | —              | _                | _                           |  |  |

| 115.2k | —                | _          | —                           | —                | _          | —                           | —              | _              | —                           | —              | —                | —                           |  |  |

|        |                   |            |                             |                   | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRC     | <b>G16 =</b> 0 |                             |                |                    |                             |  |

|--------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Foso           | : = 16.00      | 0 MHz                       | Fosc           | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | _                 | _          | _                           |                   | _          | _                           |                | _              | _                           |                | _                  | _                           |  |

| 1200   | —                 | _          | _                           | _                 | _          | _                           | _              | _              | _                           | —              | _                  | _                           |  |

| 2400   | _                 | _          | _                           | _                 | _          | _                           | _              | _              | _                           | _              | _                  | _                           |  |

| 9600   | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9615           | 0.16           | 103                         | 9600           | 0.00               | 71                          |  |

| 10417  | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10417          | 0.00           | 95                          | 10473          | 0.53               | 65                          |  |

| 19.2k  | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.23k         | 0.16           | 51                          | 19.20k         | 0.00               | 35                          |  |

| 57.6k  | 56.82k            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 58.82k         | 2.12           | 16                          | 57.60k         | 0.00               | 11                          |  |

| 115.2k | 113.64k           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 111.1k         | -3.55          | 8                           | 115.2k         | 0.00               | 5                           |  |

# FIGURE 22-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

Serve 31 The EUSARY remembers to the while the WHI 13 is not.

Г

### FIGURE 22-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

|     |                 | Na farana sa         | okordozą    | 009040090     | 003924             | 03                                     | 2010       | oopaqoxo qo | 20090903030    | (303504)  | en louiseek                 | 20030060   | .304        |

|-----|-----------------|----------------------|-------------|---------------|--------------------|----------------------------------------|------------|-------------|----------------|-----------|-----------------------------|------------|-------------|