Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 30x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1527-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

# 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection is controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4** "Write **Protection**" for more information.

#### 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

## 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 11.5 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC16F/LF151X/152X Memory Programming Specification*" (DS41422).

# 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- · Secondary oscillator 32 kHz crystal

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

#### 5.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the secondary oscillator.

# 5.3.3 SECONDARY OSCILLATOR

The secondary oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator is enabled using the SOSCEN control bit in the TxCON register. See **Section 18.0** "**Timer1/3/5 Module with Gate Control**" for more information about the Timer1 peripheral.

#### 5.3.4 SECONDARY OSCILLATOR READY (SOSCR) BIT

The user must ensure that the secondary oscillator is ready to be used before it is selected as a system clock source. The Secondary Oscillator Ready (SOSCR) bit of the OSCSTAT register indicates whether the secondary oscillator is ready to be used. After the SOSCR bit is set, the SCS bits can be configured to select the secondary oscillator.

# 5.3.5 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock, prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the Sleep instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PLLR is cleared the switch from the 32 MHz operation to the selected internal clock is complete.

| R/W-0/       | 0 R/W-0/0                                | R-0/0                            | R-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|--------------|------------------------------------------|----------------------------------|-----------------|------------------|------------------|------------------|--------------|

| TMR1G        | IF ADIF                                  | RC1IF                            | TX1IF           | SSP1IF           | CCP1IF           | TMR2IF           | TMR1IF       |

| bit 7        |                                          | I.                               | 1               |                  |                  |                  | bit 0        |

|              |                                          |                                  |                 |                  |                  |                  |              |

| Legend:      |                                          |                                  |                 |                  |                  |                  |              |

| R = Reada    | able bit                                 | W = Writable                     | bit             | U = Unimple      | mented bit, read | l as '0'         |              |

| u = Bit is u | nchanged                                 | x = Bit is unk                   | nown            | -n/n = Value     | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is | set                                      | '0' = Bit is cle                 | ared            |                  |                  |                  |              |

|              |                                          |                                  |                 |                  |                  |                  |              |

| bit 7        |                                          | Timer1 Gate Inte                 | errupt Flag bit |                  |                  |                  |              |

|              | 1 = Interrup                             | t is pending<br>t is not pending |                 |                  |                  |                  |              |

| bit 6        |                                          | Converter Interr                 | unt Elan hit    |                  |                  |                  |              |

| bit 0        | 1 = Interrup                             |                                  | upt i lag bit   |                  |                  |                  |              |

|              |                                          | t is not pending                 |                 |                  |                  |                  |              |

| bit 5        | RC1IF: USA                               | ART1 Receive Ir                  | iterrupt Flag b | bit              |                  |                  |              |

|              | 1 = Interrup                             |                                  |                 |                  |                  |                  |              |

|              |                                          | t is not pending                 |                 |                  |                  |                  |              |

| bit 4        |                                          | RT1 Transmit Ir                  | nterrupt Flag b | bit              |                  |                  |              |

|              | 1 = Interrup<br>0 = Interrup             | t is penaing t is not pending    |                 |                  |                  |                  |              |

| bit 3        |                                          | nchronous Seria                  | al Port (MSSP   | 1) Interrupt Fla | a bit            |                  |              |

|              | 1 = Interrup                             |                                  | (               | ,                | 0                |                  |              |

|              |                                          | t is not pending                 |                 |                  |                  |                  |              |

| bit 2        |                                          | CP1 Interrupt Fla                | ag bit          |                  |                  |                  |              |

|              | 1 = Interrup                             |                                  |                 |                  |                  |                  |              |

| L:1 4        |                                          | t is not pending                 | www.wt.Elea.hit |                  |                  |                  |              |

| bit 1        | 1 = Interrup                             | mer2 to PR2 Inte                 | errupt Flag bit |                  |                  |                  |              |

|              |                                          | t is not pending                 |                 |                  |                  |                  |              |

| bit 0        | -                                        | mer1 Overflow I                  | nterrupt Flag I | oit              |                  |                  |              |

|              | 1 = Interrup                             | t is pending                     |                 |                  |                  |                  |              |

|              | 0 = Interrup                             | t is not pending                 |                 |                  |                  |                  |              |

|              |                                          |                                  |                 |                  |                  |                  |              |

| Note:        | Interrupt flag bits                      |                                  |                 |                  |                  |                  |              |

|              | condition occurs,<br>its corresponding   |                                  |                 |                  |                  |                  |              |

|              | Enable bit, GIE,                         |                                  |                 |                  |                  |                  |              |

|              | User software                            | should ens                       | ure the         |                  |                  |                  |              |

|              | appropriate interr<br>to enabling an inf |                                  | clear prior     |                  |                  |                  |              |

|              | to enability all litt                    | tenupt.                          |                 |                  |                  |                  |              |

# REGISTER 7-6: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0/       | 0 R/W-0/0                         | R/W-0/0          | R/W-0/0                                | R/W-0/0 | R/W-0/0          | R/W-0/0 | R/W-0/0 |  |  |

|--------------|-----------------------------------|------------------|----------------------------------------|---------|------------------|---------|---------|--|--|

| CCP6I        | F CCP5IF                          | CCP4IF           | CCP3IF                                 | TMR6IF  | TMR5IF           | TMR4IF  | TMR3IF  |  |  |

| bit 7        |                                   |                  |                                        |         |                  |         | bit C   |  |  |

|              |                                   |                  |                                        |         |                  |         |         |  |  |

| Legend:      |                                   |                  |                                        |         |                  |         |         |  |  |

| R = Reada    | able bit                          | W = Writable     | bit                                    | •       | mented bit, read |         |         |  |  |

| u = Bit is ι | inchanged                         | •                |                                        |         |                  |         |         |  |  |

| '1' = Bit is | set                               | '0' = Bit is cle | ared                                   |         |                  |         |         |  |  |

| bit 7        | CCP6IF: CC                        | P6 Interrupt Fla | a bit                                  |         |                  |         |         |  |  |

|              | 1 = Interrupt                     |                  | 3                                      |         |                  |         |         |  |  |

|              |                                   | is not pending   |                                        |         |                  |         |         |  |  |

| bit 6        | CCP5IF: CC                        | P5 Interrupt Fla | ig bit                                 |         |                  |         |         |  |  |

|              | 1 = Interrupt                     | is pending       |                                        |         |                  |         |         |  |  |

|              | •                                 | is not pending   |                                        |         |                  |         |         |  |  |

| bit 5        | CCP4IF: CC                        | P4 Interrupt Fla | ıg bit                                 |         |                  |         |         |  |  |

|              | 1 = Interrupt                     |                  |                                        |         |                  |         |         |  |  |

| 1.11.4       | •                                 | is not pending   |                                        |         |                  |         |         |  |  |

| bit 4        |                                   | P3 Interrupt Fla | ig dit                                 |         |                  |         |         |  |  |

|              | 1 = Interrupt<br>0 = Interrupt    | is not pending   |                                        |         |                  |         |         |  |  |

| bit 3        |                                   | R6 to PR6 Mat    | ch Interrupt Fla                       | aa bit  |                  |         |         |  |  |

|              | 1 = Interrupt                     |                  | •••••••••••••••••••••••••••••••••••••• |         |                  |         |         |  |  |

|              |                                   | is not pending   |                                        |         |                  |         |         |  |  |

| bit 2        | TMR5IF: Tim                       | ner5 Overflow Ir | nterrupt Flag b                        | it      |                  |         |         |  |  |

|              | 1 = Interrupt                     |                  |                                        |         |                  |         |         |  |  |

|              | -                                 | is not pending   |                                        |         |                  |         |         |  |  |

| bit 1        |                                   | R4 to PR4 Mate   | ch Interrupt Fla                       | ag bit  |                  |         |         |  |  |

|              | 1 = Interrupt                     |                  |                                        |         |                  |         |         |  |  |

| hit 0        | •                                 | is not pending   | torrupt Flog b                         | :4      |                  |         |         |  |  |

| bit 0        | 1 = Interrupt                     | er3 Overflow Ir  | iterrupt Flag b                        | п       |                  |         |         |  |  |

|              |                                   | is not pending   |                                        |         |                  |         |         |  |  |

|              | • <b></b>                         | ie net penang    |                                        |         |                  |         |         |  |  |

| Note:        | Interrupt flag bits a             | are set when an  | interrupt                              |         |                  |         |         |  |  |

|              | condition occurs,                 |                  |                                        |         |                  |         |         |  |  |

|              | its corresponding                 |                  |                                        |         |                  |         |         |  |  |

|              | Enable bit, GIE,<br>User software | should ensi      |                                        |         |                  |         |         |  |  |

|              | appropriate interru               |                  |                                        |         |                  |         |         |  |  |

|              | to enabling an inte               |                  |                                        |         |                  |         |         |  |  |

# REGISTER 7-8: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

# 12.4 Register Definitions: PORTA

# REGISTER 12-2: PORTA: PORTA REGISTER

| R/W-x/u           | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-x/u         | R/W-x/u            | R/W-x/u           | R/W-x/u |

|-------------------|---------|--------------------|---------|-----------------|--------------------|-------------------|---------|

| RA7               | RA6     | RA5                | RA4     | RA3             | RA2                | RA1               | RA0     |

| bit 7             | •       | •                  | •       |                 |                    | •                 | bit 0   |

|                   |         |                    |         |                 |                    |                   |         |

| Legend:           |         |                    |         |                 |                    |                   |         |

| R = Readable bi   | t       | W = Writable bi    | it      | U = Unimpleme   | ented bit, read as | '0'               |         |

| u = Bit is unchar | nged    | x = Bit is unkno   | wn      | -n/n = Value at | POR and BOR/V      | alue at all other | Resets  |

| '1' = Bit is set  |         | '0' = Bit is clear | ed      |                 |                    |                   |         |

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

## REGISTER 12-3: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         | •       |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISA<7:0>: PORTA Tri-State Control bits

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

## REGISTER 12-4: LATA: PORTA DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATA<7:0>: PORTA Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

Note 1: Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

# 12.14 Register Definitions: PORTF

### REGISTER 12-24: PORTF: PORTF REGISTER

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

| RF7              | RF6     | RF5               | RF4     | RF3            | RF2              | RF1              | RF0         |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable I   | bit     | W = Writable      | bit     | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is uncha | anged   | x = Bit is unkr   | iown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0 **RF<7:0>**: PORTF General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTF are actually written to corresponding LATF register. Reads from PORTF register is return of actual I/O pin values.

#### REGISTER 12-25: TRISF: PORTF TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISF7  | TRISF6  | TRISF5  | TRISF4  | TRISF3  | TRISF2  | TRISF1  | TRISF0  |

| bit 7   | •       |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISF<7:0>: PORTF Tri-State Control bits

1 = PORTF pin configured as an input (tri-stated)

0 = PORTF pin configured as an output

## REGISTER 12-26: LATF: PORTF DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATF7   | LATF6   | LATF5   | LATF4   | LATF3   | LATF2   | LATF1   | LATF0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATF<7:0>: PORTF Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTF are actually written to corresponding LATF register. Reads from PORTF register is return of actual I/O pin values.

## 13.6 Register Definitions: Interrupt-on-change Control

#### **REGISTER 13-1: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER**

| Legend:              |         |         |         |         |         |         |         |

|----------------------|---------|---------|---------|---------|---------|---------|---------|

| bit 7                |         |         |         |         |         |         | bit 0   |

| IOCBP7 IOCBP6 IOCBP5 |         | IOCBP5  | IOCBP4  | IOCBP3  | IOCBP2  | IOCBP1  | IOCBP0  |

| R/W-0/0              | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

IOCBP<7:0>: Interrupt-on-Change PORTB Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin

#### REGISTER 13-2: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER

| R/W-0/0              | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|----------------------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7 IOCBN6 IOCBN5 |         | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |         |

| bit 7                |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**IOCBN<7:0>:** Interrupt-on-Change PORTB Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin

#### REGISTER 13-3: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER

| R/W/HS-0/0    | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|---------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7 IOCBF6 |            | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7         |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

**IOCBF<7:0>:** Interrupt-on-Change PORTB Flag bits

- 1 = An enabled change was detected on the associated pin. Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

#### 16.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| he ADIF bit is set at the completion of                                       |

|-------------------------------------------------------------------------------|

| very conversion, regardless of whether<br>r not the ADC interrupt is enabled. |

|                                                                               |

**2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

#### 16.1.6 RESULT FORMATTING

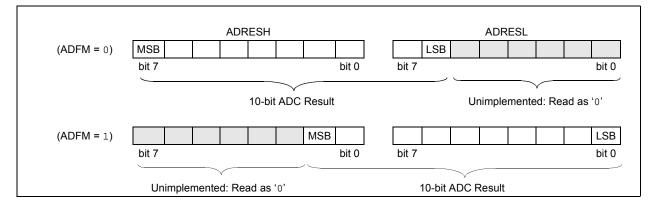

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 16-3 shows the two output formats.

## FIGURE 16-3: 10-BIT ADC CONVERSION RESULT FORMAT

# 16.2 ADC Operation

#### 16.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|

|       | same instruction that turns on the ADC   |  |  |  |  |  |  |  |

|       | Refer to Section 16.2.6 "ADC Conver      |  |  |  |  |  |  |  |

|       | sion Procedure".                         |  |  |  |  |  |  |  |

#### 16.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 16.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

## 16.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 16.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 16-2: SPECIAL EVENT TRIGGER

| Device          | ССР   |

|-----------------|-------|

| PIC16(L)F1526/7 | CCP10 |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to **Section 20.0** "Capture/Compare/PWM **Modules**" for more information.

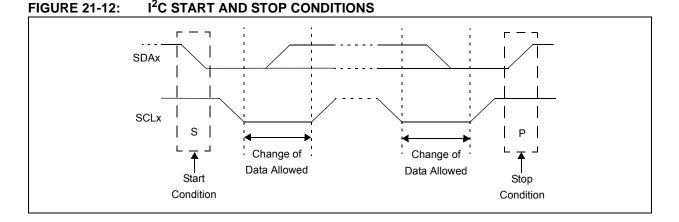

#### 21.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDAx from a high to a low state while SCLx line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 21-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDAx line low before asserting it low. This does not conform to the I<sup>2</sup>C Specification that states no bus collision can occur on a Start.

#### 21.4.6 STOP CONDITION

A Stop condition is a transition of the SDAx line from low-to-high state while the SCLx line is high.

**Note:** At least one SCLx low time must appear before a Stop is valid, therefore, if the SDAx line goes low then high again while the SCLx line stays high, only the Start condition is detected.

#### 21.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 21-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained. Until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

#### 21.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

# © 2011-2015 Microchip Technology Inc.

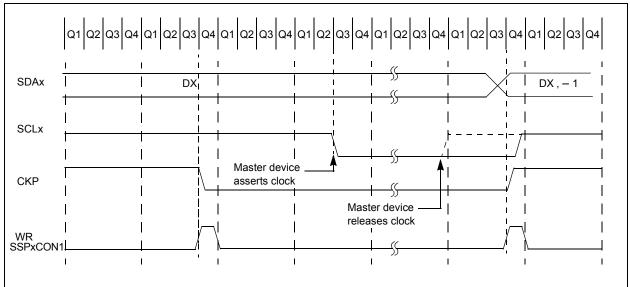

#### 21.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCLx line low effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCLx.

The CKP bit of the SSPxCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCLx line to go low and then hold it. Setting CKP will release SCLx and allow more communication.

#### 21.5.6.1 Normal Clock Stretching

Following an ACK if the R/W bit of SSPxSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPxBUF with data to transfer to the master. If the SEN bit of SSPxCON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPxBUF was read before the 9th falling edge of SCLx.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSPxBUF was loaded before the 9th falling edge of SCLx. It is now always cleared for read requests.

#### 21.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set, the clock is always stretched. This is the only time the SCLx is stretched without CKP being cleared. SCLx is released immediately after a write to SSPxADD.

| Note: | Previous versions of the module did not      |

|-------|----------------------------------------------|

|       | stretch the clock if the second address byte |

|       | did not match.                               |

#### 21.5.6.3 Byte NACKing

When AHEN bit of SSPxCON3 is set; CKP is cleared by hardware after the 8th falling edge of SCLx for a received matching address byte. When DHEN bit of SSPxCON3 is set; CKP is cleared after the 8th falling edge of SCLx for received data.

Stretching after the 8th falling edge of SCLx allows the slave to look at the received address or data and decide if it wants to ACK the received data.

#### 21.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCLx line to go low and then hold it. However, clearing the CKP bit will not assert the SCLx output low until the SCLx output is already sampled low. Therefore, the CKP bit will not assert the SCLx line until an external  $I^2C$  master device has already asserted the SCLx line. The SCLx output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCLx. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCLx (see Figure 21-23).

#### FIGURE 21-23: CLOCK SYNCHRONIZATION TIMING

| Name     | Bit 7                                  | Bit 6           | Bit 5          | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Reset<br>Values on<br>Page: |  |

|----------|----------------------------------------|-----------------|----------------|--------|--------|---------|--------|--------|-----------------------------|--|

| INTCON   | GIE                                    | PEIE            | TMR0IE         | INTE   | IOCIE  | TMR0IF  | INTF   | IOCIF  | 76                          |  |

| PIE1     | TMR1GIE                                | ADIE            | RC1IE          | TX1IE  | SSP1IE | CCP1IE  | TMR2IE | TMR1IE | 77                          |  |

| PIE2     | OSFIE                                  | TMR5GIE         | TMR3GIE        | _      | BCL1IE | TMR10IE | TMR8IE | CCP2IE | 78                          |  |

| PIE4     | CCP10IE                                | CCP9IE          | RC2IE          | TX2IE  | CCP8IE | CCP7IE  | BCL2IE | SSP2IE | 80                          |  |

| PIR1     | TMR1GIF                                | ADIF            | RC1IF          | TX1IF  | SSP1IF | CCP1IF  | TMR2IF | TMR1IF | 81                          |  |

| PIR2     | OSFIF                                  | TMR5GIF         | TMR3GIF        | _      | BCL1IF | TMR10IF | TMR8IF | CCP2IF | 82                          |  |

| PIR4     | CCP10IF                                | CCP9IF          | RC2IF          | TX2IF  | CCP8IF | CCP7IF  | BCL2IF | SSP2IF | 84                          |  |

| SSP1ADD  | ADD<7:0>                               |                 |                |        |        |         |        |        |                             |  |

| SSP2ADD  | ADD<7:0>                               |                 |                |        |        |         |        |        |                             |  |

| SSP1BUF  | MSSPx Receive Buffer/Transmit Register |                 |                |        |        |         |        |        |                             |  |

| SSP2BUF  | MSSPx Reco                             | eive Buffer/Tra | ansmit Registe | er     |        |         |        |        | 197*                        |  |

| SSP1CON1 | WCOL                                   | SSPOV           | SSPEN          | CKP    |        | SSPM    | <3:0>  |        | 244                         |  |

| SSP2CON1 | WCOL                                   | SSPOV           | SSPEN          | CKP    |        | SSPM    | <3:0>  |        | 244                         |  |

| SSP1CON2 | GCEN                                   | ACKSTAT         | ACKDT          | ACKEN  | RCEN   | PEN     | RSEN   | SEN    | 245                         |  |

| SSP2CON2 | GCEN                                   | ACKSTAT         | ACKDT          | ACKEN  | RCEN   | PEN     | RSEN   | SEN    | 245                         |  |

| SSP1CON3 | ACKTIM                                 | PCIE            | SCIE           | BOEN   | SDAHT  | SBCDE   | AHEN   | DHEN   | 246                         |  |

| SSP2CON3 | ACKTIM                                 | PCIE            | SCIE           | BOEN   | SDAHT  | SBCDE   | AHEN   | DHEN   | 246                         |  |

| SSP1MSK  |                                        |                 |                | MSK<   | <7:0>  |         |        |        | 247                         |  |

| SSP2MSK  |                                        |                 |                | MSK<   | <7:0>  |         |        |        | 247                         |  |

| SSP1STAT | SMP                                    | CKE             | D/A            | Р      | S      | R/W     | UA     | BF     | 242                         |  |

| SSP2STAT | SMP                                    | CKE             | D/Ā            | Р      | S      | R/W     | UA     | BF     | 242                         |  |

| TRISC    | TRISC7                                 | TRISC6          | TRISC5         | TRISC4 | TRISC3 | TRISC2  | TRISC1 | TRISC0 | 120                         |  |

| TRISD    | TRISD7                                 | TRISD6          | TRISD5         | TRISD4 | TRISD3 | TRISD2  | TRISD1 | TRISD0 | 123                         |  |

# TABLE 21-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in I<sup>2</sup>C mode.

\* Page provides register information.

**Note 1:** PIC16(L)F1527 only.

|        |                  | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                | _                             | —                           | _                |            | _                           |                   | _          | _                           | 300              | 0.16       | 207                         |

| 1200   | —                | _                             | —                           | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404             | 0.16                          | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615             | 0.16                          | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | —                |            | —                           |

| 10417  | 10417            | 0.00                          | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231            | 0.16                          | 25                          | 19.23k           | 0.16       | 12                          | 19.2k             | 0.00       | 11                          | _                | _          | _                           |

| 57.6k  | 55556            | -3.55                         | 8                           | —                | _          | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           |

| 115.2k | —                | _                             | —                           | _                |            | _                           | 115.2k            | 0.00       | 1                           | —                | _          | —                           |

# TABLE 22-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------|-------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz             |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 16.000 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                         | -0.01      | 4166                        | 300.0             | 0.00       | 3839                        | 300.03            | 0.01       | 3332                        | 300.0              | 0.00       | 2303                        |

| 1200   | 1200                          | -0.03      | 1041                        | 1200              | 0.00       | 959                         | 1200.5            | 0.04       | 832                         | 1200               | 0.00       | 575                         |

| 2400   | 2399                          | -0.03      | 520                         | 2400              | 0.00       | 479                         | 2398              | -0.08      | 416                         | 2400               | 0.00       | 287                         |

| 9600   | 9615                          | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9615              | 0.16       | 103                         | 9600               | 0.00       | 71                          |

| 10417  | 10417                         | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10417             | 0.00       | 95                          | 10473              | 0.53       | 65                          |

| 19.2k  | 19.23k                        | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.23k            | 0.16       | 51                          | 19.20k             | 0.00       | 35                          |

| 57.6k  | 56.818                        | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 58.82k            | 2.12       | 16                          | 57.60k             | 0.00       | 11                          |

| 115.2k | 113.636                       | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 111.11k           | -3.55      | 8                           | 115.2k             | 0.00       | 5                           |

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 299.9                         | -0.02      | 1666                        | 300.1            | 0.04       | 832                         | 300.0             | 0.00       | 767                         | 300.5            | 0.16       | 207                         |

| 1200   | 1199                          | -0.08      | 416                         | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | _                | _          | _                           |

| 10417  | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19.23k                        | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.20k            | 0.00       | 11                          | —                | _          | _                           |

| 57.6k  | 55556                         | -3.55      | 8                           | —                | _          | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           |

| 115.2k | _                             | _          | _                           | —                | _          | _                           | 115.2k            | 0.00       | 1                           | —                | _          | _                           |

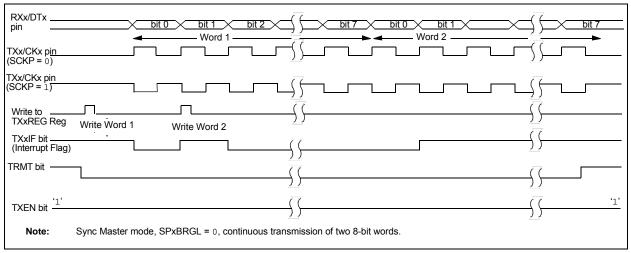

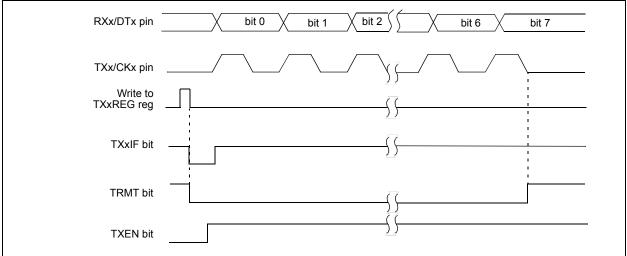

# 22.5.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 22.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC. Set the TRIS bits corresponding to the RXx/DTx and TXx/CKx I/O pins.

- 4. Disable Receive mode by clearing bits SREN and CREN.

- 5. Enable Transmit mode by setting the TXEN bit.

- 6. If 9-bit transmission is desired, set the TX9 bit.

- 7. If interrupts are desired, set the TXxIE, GIE and PEIE interrupt enable bits.

- 8. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 9. Start transmission by loading data to the TXx-REG register.

# FIGURE 22-10: SYNCHRONOUS TRANSMISSION

# FIGURE 22-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

| LSLF             | Logical Left Shift                                                                                                                                                                                                                  | MOVF             | Move f                                                                                                                                                                                                                                                                            |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ]LSLF f{,d}                                                                                                                                                                                                          | Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                                  | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                 |  |  |  |  |

| Operation:       | $(f < 7 >) \rightarrow C$                                                                                                                                                                                                           | Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                          |  |  |  |  |

|                  | $(f<6:0>) \rightarrow dest<7:1>$<br>0 $\rightarrow dest<0>$                                                                                                                                                                         | Status Affected: | Z                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Status Affected: | C, Z                                                                                                                                                                                                                                | Description:     | The contents of register f is moved to<br>a destination dependent upon the<br>status of d. If $d = 0$ , destination is W<br>register. If $d = 1$ , the destination is file<br>register f itself. $d = 1$ is useful to test a<br>file register since status flag Z is<br>affected. |  |  |  |  |

| Description:     | The contents of register 'f' are shifted<br>one bit to the left through the Carry flag.<br>A '0' is shifted into the LSb. If 'd' is '0',<br>the result is placed in W. If 'd' is '1', the<br>result is stored back in register 'f'. |                  |                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                  | C                                                                                                                                                                                                                                   | Words:           | 1                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                  |                                                                                                                                                                                                                                     | Cycles:          | 1                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                  |                                                                                                                                                                                                                                     | Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                       |  |  |  |  |

| LSRF             | Logical Right Shift                                                                                                                                                                                                                 |                  | After Instruction<br>W = value in FSR register                                                                                                                                                                                                                                    |  |  |  |  |

| Syntax:          | [ <i>label</i> ]LSRF f{,d}                                                                                                                                                                                                          |                  | Z = 1                                                                                                                                                                                                                                                                             |  |  |  |  |

| Syntax:          | [ <i>label</i> ]LSRF f{,d}                                                                                                                                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                    |

| Operation:       | 0 → dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                                                  |

| Status Affected: | C, Z                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. A '0' is shifted into the MSb. If 'd' is<br>'0', the result is placed in W. If 'd' is '1',<br>the result is stored back in register 'f'. |

|                  | 0 → register f → C                                                                                                                                                                                                                   |

# 27.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 27.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>